Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

Caricato da

Yadav RaviTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

Caricato da

Yadav RaviCopyright:

Formati disponibili

13. IEEE 1149.

1 (JTAG) Boundary-Scan

Testing in Stratix III Devices

SIII51013-1.9

This chapter discusses how to use the IEEE Std. 1149.1 boundary-scan test (BST)

circuitry in Stratix® III devices. The BST architecture offers the capability to test

efficiently components on PCBs with tight lead spacing. BST architecture tests pin

connections without using physical test probes and captures functional data while a

device is operating normally. Boundary-scan cells in a device can force signals onto

pins or capture data from pin or logic array signals. Forced test data is serially shifted

into the boundary-scan cells. Captured data is serially shifted out and externally

compared to expected results. Figure 13–1 shows the concept of BST.

Figure 13–1. IEEE Std. 1149.1 Boundary-Scan Testing

Boundary-Scan Cell

Serial Serial

Data In IC Pin Signal Data Out

Logic Logic

Array Array

Tested

Connection

JTAG Device 1 JTAG Device 2

In addition to BST, you can use the IEEE Std. 1149.1 controller for Stratix III device

in-circuit reconfiguration (ICR). However, this chapter only discusses the BST feature

of the IEEE Std. 1149.1 circuitry.

f For information about configuring Stratix III devices by using the IEEE Std. 1149.1

circuitry, refer to the Configuring Stratix III Devices, Hot Socketing and Power-On Reset in

Stratix III Devices, and the Remote System Upgrades with Stratix III Devices chapters.

IEEE Std. 1149.1 BST Architecture

A Stratix III device operating in IEEE Std. 1149.1 BST mode uses four required pins,

TDI, TDO, TMS, and TCK, and one optional pin, TRST. The TCK pin has an internal

weak pull-down resistor; the TDI, TMS, and TRST pins have weak internal pull-ups.

The TDO output pin and all of the JTAG input pins are powered by the

2.5-V/3.0-V/3.3-V VCCPD supply of I/O Bank 1A. All user I/O pins are tri-stated

during JTAG configuration.

f For recommendations about how to connect a JTAG chain with multiple voltages

across the devices in the chain, refer to “I/O Voltage Support in JTAG Chain” on

page 13–17.

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–2 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 BST Architecture

Table 13–1 summarizes the functions of each of these pins.

Table 13–1. IEEE Std. 1149.1 Pin Descriptions

Pin Description Function

Serial input pin for instructions as well as test and programming data. Signal applied

TDI Test data input to TDI is expected to change state at the falling edge of TCK. Data is shifted in on

the rising edge of TCK.

Serial data output pin for instructions as well as test and programming data. Data is

TDO Test data output shifted out on the falling edge of TCK. The pin is tri-stated if data is not being shifted

out of the device.

Input pin that provides the control signal to determine the transitions of the test

access port (TAP) controller state machine. Transitions within the state machine

TMS Test mode select occur at the rising edge of TCK. Therefore, you must set up TMS before the rising

edge of TCK. TMS is evaluated on the rising edge of TCK. During non-JTAG

operation, Altera recommends you drive TMS high.

The clock input to the BST circuitry. Some operations occur at the rising edge, while

TCK Test clock input

others occur at the falling edge.

Test reset input Active-low input to asynchronously reset the boundary-scan circuit. For non-JTAG

TRST (1)

(optional) users, you should permanently tie the pin to GND.

Note to Table 13–1:

(1) The minimum TRST pulse width to reset the JTAG TAP controller is 60 ns.

The IEEE Std. 1149.1 BST circuitry requires the following registers:

■ The instruction register determines the action to be performed and the data

register to be accessed.

■ The bypass register is a one-bit-long data register that provides a minimum-length

serial path between TDI and TDO.

■ The boundary-scan register is a shift register composed of all the boundary-scan

cells of the device.

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–3

IEEE Std. 1149.1 BST Architecture

Figure 13–2 shows a functional model of the IEEE Std. 1149.1 circuitry.

Figure 13–2. IEEE Std. 1149.1 Circuitry

Instruction Register (1)

TDI

TDO

UPDATEIR

CLOCKIR

SHIFTIR

Instruction Decode

TAP

TMS Controller

TCLK

UPDATEDR Data Registers

CLOCKDR Bypass Register

TRST SHIFTDR

Boundary-Scan Register (1)

Device ID Register

ICR Registers

Note to Figure 13–2:

(1) For register lengths, refer to the device datasheet in the Configuring Stratix III Devices chapter in volume 1 of the Stratix III Device Handbook.

IEEE Std. 1149.1 boundary-scan testing is controlled by a TAP controller. For more

information about the TAP controller, refer to “IEEE Std. 1149.1 BST Operation

Control” on page 13–7. The TMS and TCK pins operate the TAP controller. The TDI

and TDO pins provide the serial path for the data registers. The TDI pin also provides

data to the instruction register, which then generates control logic for the data

registers.

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–4 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 Boundary-Scan Register

IEEE Std. 1149.1 Boundary-Scan Register

The boundary-scan register is a large serial shift register that uses the TDI pin as an

input and the TDO pin as an output. The boundary-scan register consists of three-bit

peripheral elements that are associated with Stratix III I/O pins. You can use the

boundary-scan register to test external pin connections or to capture internal data.

f For the Stratix III family device boundary-scan register lengths, refer to the

Configuring Stratix III Devices chapter in volume 1 of the Stratix III Device Handbook.

Figure 13–3 shows how test data is serially shifted around the periphery of the IEEE

Std. 1149.1 device.

Figure 13–3. Boundary-Scan Register

Each peripheral

element is either an

I/O pin, dedicated

input pin, or

Internal Logic dedicated

configuration pin.

TAP Controller

TDI TMS TCK TRST TDO

Table 13–2 lists the boundary-scan register length for Stratix III devices.

Table 13–2. Stratix III Boundary-Scan Register Length

Device Boundary-Scan Register Length

EP3SL50 1506

EP3SL70 1506

EP3SL110 2274

EP3SL150ES 2274

EP3SL150 2274

EP3SL200 2970

EP3SL340 3402

EP3SE50 1506

EP3SE80 2274

EP3SE110 2274

EP3SE260 2970

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–5

IEEE Std. 1149.1 Boundary-Scan Register

Boundary-Scan Cells of a Stratix III Device I/O Pin

The Stratix III device three-bit boundary-scan cell (BSC) consists of a set of capture

registers and a set of update registers. The capture registers can connect to internal

device data through the OUTJ, OEJ, and PIN_IN signals, while the update registers

connect to external data through the PIN_OUT and PIN_OE signals.

The global control signals for the IEEE Std. 1149.1 BST registers (such as shift,

clock, and update) are generated internally by the TAP controller. The MODE signal

is generated by a decode of the instruction register. The HIGHZ signal is high when

executing the HIGHZ instruction. The data signal path for the boundary-scan register

runs from the serial data in (SDI) signal to the serial data out (SDO) signal. The scan

register begins at the TDI pin and ends at the TDO pin of the device.

Figure 13–4 shows the Stratix III device's user I/O boundary-scan cell.

Figure 13–4. Stratix III Device's User I/O BSC with IEEE Std. 1149.1 BST Circuitry

Capture Update

Registers Registers

SDO

INJ

PIN_IN

0

0

D Q D Q 1

1

INPUT INPUT

OEJ

To or From

0 0 PIN_OE

Device D Q D Q 0

I/O Cell 1 1

OE OE 1

Circuitry

and/or

Logic VCC

Array

OUTJ

0 PIN_OUT

0 Pin

D Q D Q 1

1

Output

OUTPUT OUTPUT

Buffer

SDI

Global

SHIFT CLOCK UPDATE HIGHZ MODE

Signals

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–6 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 Boundary-Scan Register

Table 13–3 lists the capture and update register capabilities of all boundary-scan cells

within Stratix III devices.

Table 13–3. Stratix III Device Boundary Scan Cell Descriptions (Note 1)

Captures Drives

Pin Type Output OE Input Output Input Comments

OE Update

Capture Capture Capture Update Update

Register

Register Register Register Register Register

User I/O pins OUTJ OEJ PIN_IN PIN_OUT PIN_OE INJ —

PIN_IN drives to

Dedicated clock

0 1 PIN_IN — — — clock network or

input

logic array

Dedicated input PIN_IN drives to

0 1 PIN_IN — — —

(2) control logic

Dedicated PIN_IN drives to

bi-directional 0 OEJ PIN_IN — — — configuration

(open drain) (3) control

PIN_IN drives to

configuration

Dedicated

OUTJ OEJ PIN_IN — — — control and OUTJ

bi-directional (4)

drives to output

buffer

Dedicated output OUTJ drives to

OUTJ 0 0 — — —

(5) output buffer

Notes to Table 13–3:

(1) TDI, TDO, TMS, TCK, TRST, all VCC and GND pin types, VREF, and TEMP_DIODE pins do not have BSCs.

(2) This includes pins PLL_ENA, nCONFIG, MSEL0, MSEL1, MSEL2, nCE, PORSEL, and nIO_PULLUP.

(3) This includes pins CONF_DONE and nSTATUS.

(4) This includes pin DCLK.

(5) This includes pin nCEO.

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–7

IEEE Std. 1149.1 BST Operation Control

IEEE Std. 1149.1 BST Operation Control

Stratix III devices support the IEEE Std. 1149.1 (JTAG) instructions listed in Table 13–4.

Table 13–4. Stratix III JTAG Instructions

Instruction

JTAG Instruction Description

Code

Allows a snapshot of signals at the device pins to be captured and examined

SAMPLE / PRELOAD 00 0000 0101 during normal device operation, and permits an initial data pattern to be output at

the device pins. Also used by the SignalTap® II embedded logic analyzer.

Allows the external circuitry and board-level interconnects to be tested by forcing

EXTEST (1) 00 0000 1111

a test pattern at the output pins and capturing test results at the input pins.

Places the 1-bit bypass register between the TDI and TDO pins, which allows

BYPASS 11 1111 1111 the BST data to pass synchronously through selected devices to adjacent devices

during normal device operation.

Places the 32-bit device identification register between TDI and TDO. The

USERCODE 00 0000 0111 USERCODE value are loaded into this Device ID register for shifting out through

TDO.

Selects the IDCODE register and places it between TDI and TDO, allowing the

IDCODE 00 0000 0110

IDCODE to be serially shifted out of TDO.

Places the 1-bit bypass register between the TDI and TDO pins, which allows

HIGHZ (1) 00 0000 1011 the BST data to pass synchronously through selected devices to adjacent devices

during normal device operation, while tri-stating all of the I/O pins.

Places the 1-bit bypass register between the TDI and TDO pins, which allows

the BST data to pass synchronously through selected devices to adjacent devices

CLAMP (1) 00 0000 1010

during normal device operation while holding I/O pins to a state defined by the

data in the boundary-scan register.

Used when configuring a Stratix III device through the JTAG port with a

USB-Blaster™, ByteBlaster™ II, MasterBlaster™ or ByteBlasterMV™ download

ICR instructions —

cable, or when using a Jam File or Jam Byte-Code (JBC) File through an

embedded processor.

Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though

PULSE_NCONFIG 00 0000 0001

the physical pin is unaffected.

Allows I/O reconfiguration through JTAG ports using the IOCSR for JTAG testing.

CONFIG_IO 00 0000 1101

Can be executed before, after, or during configurations.

Note to Table 13–4:

(1) Bus hold and weak pull-up resistor features override the high-impedance state of the HIGHZ, CLAMP, and EXTEST instructions.

The IEEE Std. 1149.1 TAP controller, a 16-state machine clocked on the rising edge of

TCK, uses the TMS pin to control IEEE Std. 1149.1 operation in the device. Figure 13–5

shows the TAP controller state machine.

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–8 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 BST Operation Control

Figure 13–5. IEEE Std. 1149.1 TAP Controller State Machine

TEST_LOGIC/

TMS = 1 RESET

TMS = 0 SELECT_DR_SCAN TMS = 1 SELECT_IR_SCAN

TMS = 1 TMS = 1

RUN_TEST/

TMS = 0 IDLE

TMS = 0 TMS = 0

TMS = 1 TMS = 1

CAPTURE_DR CAPTURE_IR

TMS = 0 TMS = 0

SHIFT_DR SHIFT_IR

TMS = 0 TMS = 0

TMS = 1 TMS = 1

TMS = 1 TMS = 1

EXIT1_DR EXIT1_IR

TMS = 0 TMS = 0

PAUSE_DR PAUSE_IR

TMS = 0 TMS = 0

TMS = 1 TMS = 1

TMS = 0 TMS = 0

EXIT2_DR EXIT2_IR

TMS = 1 TMS = 1

TMS = 1 TMS = 1

UPDATE_DR UPDATE_IR

TMS = 0 TMS = 0

When the TAP controller is in the TEST_LOGIC/RESET state, the BST circuitry is

disabled, the device is in normal operation, and the instruction register is initialized

with IDCODE as the initial instruction. At device power-up, the TAP controller starts

in this TEST_LOGIC/RESET state. In addition, forcing the TAP controller to the

TEST_LOGIC/RESET state is achieved by holding TMS high for five TCK clock cycles,

or by holding the TRST pin low. In the TEST_LOGIC/RESET state, the TAP controller

remains in this state as long as TMS is held high (while TCK is clocked) or TRST is held

low. Figure 13–6 shows the timing requirements for the IEEE Std. 1149.1 signals.

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–9

IEEE Std. 1149.1 BST Operation Control

Figure 13–6. IEEE Std. 1149.1 Timing Waveforms

TMS

TDI

tJCP

tJCH tJCL t JPSU tJPH

TCK

tJPZX tJPCO tJPXZ

TDO

To start IEEE Std. 1149.1 operation, select an instruction mode by advancing the TAP

controller to the shift instruction register (SHIFT_IR) state and shift in the

appropriate instruction code on the TDI pin. The waveform diagram in Figure 13–7

shows the entry of the instruction code into the instruction register. It also shows the

values of TCK, TMS, TDI, TDO, and the states of the TAP controller. From the RESET

state, TMS is clocked with the pattern 01100 to advance the TAP controller to

SHIFT_IR.

Figure 13–7. Selecting the Instruction Mode

TCK

TMS

TDI

TDO

TAP_STATE SHIFT_IR

RUN_TEST/IDLE SELECT_IR_SCAN

TEST_LOGIC/RESET SELECT_DR_SCAN CAPTURE_IR EXIT1_IR

The TDO pin is tri-stated in all states except in the SHIFT_IR and SHIFT_DR states.

The TDO pin is activated at the first falling edge of TCK after entering either of the shift

states and is tri-stated at the first falling edge of TCK after leaving either of the shift

states.

When the SHIFT_IR state is activated, TDO is no longer tri-stated, and the initial state

of the instruction register is shifted out on the falling edge of TCK. TDO continues to

shift out the contents of the instruction register as long as the SHIFT_IR state is

active. The TAP controller remains in the SHIFT_IR state as long as TMS remains low.

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–10 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 BST Operation Control

During the SHIFT_IR state, an instruction code is entered by shifting data on the TDI

pin on the rising edge of TCK. The last bit of the instruction code is clocked at the same

time that the next state, EXIT1_IR, is activated. Set TMS high to activate the

EXIT1_IR state. After the EXIT1_IR state is activated, TDO becomes tri-stated again.

TDO is always tri-stated except in the SHIFT_IR and SHIFT_DR states. After an

instruction code is entered correctly, the TAP controller advances to serially shift test

data in one of three modes.

The three serially shift test data instruction modes are discussed in the following

sections:

■ “SAMPLE/PRELOAD Instruction Mode” on page 13–11

■ “EXTEST Instruction Mode” on page 13–13

■ “BYPASS Instruction Mode” on page 13–15

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–11

IEEE Std. 1149.1 BST Operation Control

SAMPLE/PRELOAD Instruction Mode

The SAMPLE/PRELOAD instruction mode allows you to take a snapshot of device data

without interrupting normal device operation. However, this instruction is most often

used to preload the test data into the update registers prior to loading the EXTEST

instruction. Figure 13–8 shows the capture, shift, and update phases of the

SAMPLE/PRELOAD mode.

Figure 13–8. IEEE Std. 1149.1 BST SAMPLE/PRELOAD Mode

PIN_IN

Capture Phase

SDO

In the capture phase, the

signals at the pin, OEJ and

0

OUTJ, are loaded into the 0 INJ

capture registers. The CLOCK D Q D Q 1

1

signals are supplied by the TAP

controller's CLOCKDR output.

The data retained in these

registers consists of signals

from normal device operation. OEJ

0

0

D Q D Q 1

1

OUTJ

0

0

D Q D Q 1

1

Capture Update

Registers Registers

SDI SHIFT UPDATE MODE

CLOCK

PIN_IN

Shift and Update Phases SDO

In the shift phase, the

previously captured signals at 0

0 INJ

the pin, OEJ and OUTJ, are D Q D Q 1

1

shifted out of the boundary-scan

register through the TDO pin using

CLOCK. As data is shifted out,

the patterns for the next test

can be shifted in through the

OEJ

TDI pin. 0

0

D Q D Q 1

In the update phase, data is 1

transferred from the capture

registers to the update

registers using the UPDATE

clock. The data stored in the

OUTJ

update registers can be used 0

for the EXTEST instruction. 0

D Q D Q 1

1

Capture Update

Registers Registers

SDI SHIFT UPDATE MODE

CLOCK

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–12 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 BST Operation Control

During the capture phase, multiplexers preceding the capture registers select the

active device data signals. This data is then clocked into the capture registers. The

multiplexers at the outputs of the update registers also select active device data to

prevent functional interruptions to the device. During the shift phase, the

boundary-scan shift register is formed by clocking data through the capture registers

around the device periphery and then out of the TDO pin. The device can

simultaneously shift new test data into TDI and replace the contents of the capture

registers. During the update phase, data in the capture registers is transferred to the

update registers. You can then use this data in the EXTEST instruction mode. Refer to

“EXTEST Instruction Mode” on page 13–13 for more information.

Figure 13–9 shows the SAMPLE/PRELOAD waveforms. The SAMPLE/PRELOAD

instruction code is shifted in through the TDI pin. The TAP controller advances to the

CAPTURE_DR state and then to the SHIFT_DR state, where it remains if TMS is held

low. The data that was present in the capture registers after the capture phase is

shifted out of the TDO pin. New test data shifted into the TDI pin appears at the TDO

pin after being clocked through the entire boundary-scan register. If TMS is held high

on two consecutive TCK clock cycles, the TAP controller advances to the UPDATE_DR

state for the update phase.

Figure 13–9. SAMPLE/PRELOAD Shift Data Register Waveforms

TCK

TMS

TDI

TDO

SHIFT_IR SHIFT_DR

TAP_STATE

EXIT1_IR SELECT_DR (1) (2) EXIT1_DR

Instruction Code UPDATE_IR CAPTURE_DR UPDATE_DR

Note to Figure 13–9:

(1) Data stored in boundary-scan register is shifted out of TDO.

(2) After boundary-scan register data has been shifted out, data entered into TDI will shift out of TDO.

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–13

IEEE Std. 1149.1 BST Operation Control

EXTEST Instruction Mode

Use the EXTEST instruction mode primarily to check external pin connections

between devices. Unlike the SAMPLE/PRELOAD mode, EXTEST allows test data to be

forced onto the pin signals. By forcing known logic high and low levels on output

pins, you can detect opens and shorts at pins of any device in the scan chain.

Figure 13–10 shows the capture, shift, and update phases of the EXTEST mode.

Figure 13–10. IEEE Std. 1149.1 BST EXTEST Mode

PIN_IN

Capture Phase

SDO

In the capture phase, the

signals at the pin, OEJ and 0

OUTJ, are loaded into the 0 INJ

D Q D Q 1

capture registers. The CLOCK 1

signals are supplied by the TAP

controller's CLOCKDR output.

Previously retained data in the

update registers drive the

PIN_OUT, INJ, and allows the OEJ

0

I/O pin to tri-state or drive a 0

signal out. D Q D Q 1

1

A "1" in the OEJ update

register tri-states the output

buffer.

OUTJ

0

0

D Q D Q 1

1

Capture Update

Registers Registers

SDI SHIFT UPDATE MODE

CLOCK

PIN_IN

Shift and Update Phases SDO

In the shift phase, the

previously captured signals at 0

0 INJ

the pin, OEJ and OUTJ, are D Q D Q 1

1

shifted out of the boundary-scan

register through the TDO pin using

CLOCK. As data is shifted out,

the patterns for the next test

can be shifted in through the

OEJ

TDI pin. 0

0

D Q D Q 1

In the update phase, data is 1

transferred from the capture

registers to the update

registers using the UPDATE

clock. The update registers

OUTJ

then drive the PIN_OUT, INJ, 0

and allow the I/O pin to 0

D Q D Q 1

tri-state or drive a signal out. 1

Capture Update

Registers Registers

SDI SHIFT UPDATE MODE

CLOCK

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–14 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 BST Operation Control

EXTEST mode selects data differently than SAMPLE/PRELOAD mode. EXTEST chooses

data from the update registers as the source of the output and output-enable signals.

After the EXTEST instruction code is entered, the multiplexers select the update

register data. Therefore, data stored in these registers from a previous EXTEST or

SAMPLE/PRELOAD test cycle can be forced onto the pin signals. In the capture phase,

the results of this test data are stored in the capture registers and then shifted out of

TDO during the shift phase. You can then store new test data in the update registers

during the update phase.

The EXTEST waveform diagram in Figure 13–11 resembles the SAMPLE/PRELOAD

waveform diagram, except for the instruction code. The data shifted out of TDO

consists of the data that was present in the capture registers after the capture phase.

New test data shifted into the TDI pin appears at the TDO pin after being clocked

through the entire boundary-scan register.

Figure 13–11. EXTEST Shift Data Register Waveforms

TCK

TMS

TDI

TDO

SHIFT_IR SHIFT_DR

TAP_STATE

EXIT1_IR SELECT_DR (1) (2) EXIT1_DR

Instruction Code UPDATE_IR CAPTURE_DR UPDATE_DR

Note to Figure 13–11:

(1) Data stored in the boundary-scan register is shifted out of TDO.

(2) After boundary-scan register data has been shifted out, data entered into TDI will shift out of TDO.

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–15

IEEE Std. 1149.1 BST Operation Control

BYPASS Instruction Mode

The BYPASS mode is activated when an instruction code of all ones is loaded in the

instruction register. This mode allows the boundary scan data to pass the selected

device synchronously to adjacent devices when no test operation of the device is

needed at the board level. The waveforms in Figure 13–12 show how scan data passes

through a device after the TAP controller is in the SHIFT_DR state. In this state, data

signals are clocked into the bypass register from TDI on the rising edge of TCK and

out of TDO on the falling edge of the same clock pulse.

Figure 13–12. BYPASS Shift Data Register Waveforms

TCK

TMS

TDI Bit 1 Bit 2 Bit 3

TDO Bit 1 Bit 2 Bit 4

SHIFT_IR SHIFT_DR

TAP_STATE EXIT1_IR SELECT_DR_SCAN EXIT1_DR

(1)

Instruction Code UPDATE_IR CAPTURE_DR UPDATE_DR

Note to Figure 13–12:

(1) Data shifted into TDI on the rising edge of TCK is shifted out of TDO on the falling edge of the same TCK pulse.

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–16 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 BST Operation Control

IDCODE Instruction Mode

Use the IDCODE instruction mode to identify the devices in an IEEE Std. 1149.1 chain.

When IDCODE is selected, the device identification register is loaded with the 32-bit

vendor-defined identification code. The device ID register is connected between the

TDI and TDO ports, and the device IDCODE is shifted out. Table 13–5 lists the IDCODE

information for Stratix III devices.

Table 13–5. 32-Bit Stratix III Device IDCODE

IDCODE (32 Bits) (1)

Device LSB

Version (4 Bits) Part Number (16 Bits) Manufacturer Identity (11 Bits)

(1 Bit) (2)

EP3SL50 0000 0010 0001 0000 1000 000 0110 1110 1

EP3SL70 0000 0010 0001 0000 0001 000 0110 1110 1

EP3SL110 0001 0010 0001 0000 1001 000 0110 1110 1

EP3SL150ES 0000 0010 0001 0000 0010 000 0110 1110 1

EP3SL150 0001 0010 0001 0000 0010 000 0110 1110 1

EP3SL200 0000 0010 0001 0000 0011 000 0110 1110 1

EP3SL340 0000 0010 0001 0000 0101 000 0110 1110 1

EP3SE50 0000 0010 0001 0000 0110 000 0110 1110 1

EP3SE80 0000 0010 0001 0000 1010 000 0110 1110 1

EP3SE110 0000 0010 0001 0000 0111 000 0110 1110 1

EP3SE260 0000 0010 0001 0000 0100 000 0110 1110 1

Notes to Table 13–5:

(1) The most significant bit (MSB) is on the left.

(2) The IDCODE’s least significant bit (LSB) is always 1.

USERCODE Instruction Mode

Use the USERCODE instruction mode to examine the user electronic signature (UES)

within the devices along an IEEE Std. 1149.1 chain. When you select this instruction,

the device identification register is connected between the TDI and TDO ports. The

user-defined UES is shifted into the device ID register in parallel from the 32-bit

USERCODE register. The UES is then shifted out through the device ID register.

1 The UES value is not user defined until after the device is configured. This value is

stored in the programmer object file (.pof) and only loaded to the device during

configuration. Before configuration, the UES value is set to the default value.

CLAMP Instruction Mode

Use the CLAMP instruction mode to allow the state of the signals driven from the pins

to be determined from the boundary-scan register while the bypass register is selected

as the serial path between the TDI and TDO ports. The states of all signals driven from

the pins are completely defined by the data held in the boundary-scan register.

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–17

I/O Voltage Support in JTAG Chain

HIGHZ Instruction Mode

The HIGHZ instruction mode sets all of the user I/O pins to an inactive drive state.

These pins are tri-stated until a new JTAG instruction is executed. When this

instruction is loaded into the instruction register, the bypass register is connected

between the TDI and TDO ports.

I/O Voltage Support in JTAG Chain

The JTAG chain supports several devices. However, you should use caution if the

chain contains devices that have different VCCIO levels. The output voltage level of the

TDO pin must meet the specifications of the TDI pin it drives. The TDI and TDO pins of

Stratix III device are powered by the VCCPD (2.5 V / 3.0 V / 3.3 V) of I/O Bank 1A. You

should connect VCCPD according to the I/O standard used in the same bank. For 3.3-V

I/O standards, you should connect VCCPD to 3.3 V. For 3.0-V I/O standards, you should

connect VCCPD to 3.0 V; for 2.5-V and below I/O standards, you should connect VCCPD to

2.5 V. Table 13–6 lists board design recommendations to ensure proper JTAG chain

operation.

Table 13–6. Supported TDO/TDI Voltage Combinations

Stratix III TDO VCCPD

Device TDI Input Buffer Power

VCCPD = 3.3 V (1) VCCPD = 3.0 V (1) VCCPD = 2.5 V (2)

VCCPD = 3.3V v v v

Stratix III VCCPD = 3.0V v v v

VCCPD = 2.5V v v v

VCC = 3.3 V v (3) v (4) v (5)

VCC = 2.5 V v (3) v (4) v (5)

Non-Stratix III

VCC = 1.8 V v (3) v (4) v (5)

VCC = 1.5 V v (3) v (4) v (5)

Notes to Table 13–6:

(1) The TDO output buffer meets VOH (MIN) = 2.4 V.

(2) The TDO output buffer meets VOH (MIN) = 2.0 V.

(3) Input buffer must be 3.3-V tolerant.

(4) Input buffer must be 3.0-V tolerant.

(5) Input buffer must be 2.5-V tolerant.

You can interface the TDI and TDO lines of the devices that have different VCCIO levels

by inserting a level shifter between the devices. If possible, you should build the JTAG

chain in such a way that a device with a higher VCCIO level drives to a device with an

equal or lower VCCIO level. This way, a level shifter is used only to shift the TDO level to

a level acceptable to the JTAG tester. Figure 13–13 shows the JTAG chain of mixed

voltages and how a level shifter is inserted in the chain.

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–18 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

IEEE Std. 1149.1 BST Circuitry

Figure 13–13. JTAG Chain of Mixed Voltages

Must be 3.3-V tolerant.

TDI 3.3-V 2.5-V

VCCIO VCCIO

Tester

TDO Level 1.5-V 1.8-V

Shifter VCCIO VCCIO

Shift TDO to Must be Must be

level accepted 1.8-V tolerant. 2.5-V tolerant.

by tester if

necessary.

IEEE Std. 1149.1 BST Circuitry

Stratix III devices have dedicated JTAG pins and the IEEE Std. 1149.1 BST circuitry is

enabled upon device power-up. You can perform BST on Stratix III FPGAs before,

during, and after configuration. Stratix III FPGAs support the BYPASS, IDCODE, and

SAMPLE instructions during configuration without interrupting configuration. To

send all other JTAG instructions, you must interrupt configuration using the

CONFIG_IO instruction.

The CONFIG_IO instruction allows you to configure I/O buffers through the JTAG

port, and when issued, interrupts configuration. This instruction allows you to

perform board-level testing prior to configuring the Stratix III FPGA or you can wait

for the configuration device to complete configuration. After configuration is

interrupted and JTAG BST is complete, you must reconfigure the part through JTAG

(PULSE_CONFIG instruction) or by pulsing nCONFIG low.

1 When you perform JTAG boundary-scan testing before configuration, the nCONFIG

pin must be held low.

The chip-wide reset (DEV_CLRn) and chip-wide output enable (DEV_OE) pins on

Stratix III devices do not affect JTAG boundary-scan or configuration operations.

Toggling these pins does not disrupt BST operation (other than the expected BST

behavior).

When you design a board for JTAG configuration of Stratix III devices, you must

consider the connections for the dedicated configuration pins.

f For more information about using the IEEE Std.1149.1 circuitry for device

configuration, refer to the Configuring Stratix III Devices chapter in volume 1 of the

Stratix III Device Handbook.

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–19

IEEE Std. 1149.1 BST Circuitry (Disabling)

IEEE Std. 1149.1 BST Circuitry (Disabling)

The IEEE Std. 1149.1 BST circuitry for Stratix III devices is enabled upon device

power-up. Because the IEEE Std. 1149.1 BST circuitry is used for BST or in-circuit

reconfiguration, you must enable the circuitry only at specific times as mentioned in,

“IEEE Std. 1149.1 BST Circuitry” on page 13–18.

1 If you are not using the IEEE Std. 1149.1 circuitry in Stratix III, you should

permanently disable the circuitry to ensure that you do not inadvertently enable it

when it is not required.

Table 13–7 lists the pin connections necessary for disabling the IEEE Std. 1149.1

circuitry in Stratix III devices.

Table 13–7. Disabling IEEE Std. 1149.1 Circuitry

JTAG Pins (1) Connection for Disabling

TMS VCCPD supply of Bank 1A

TCK GND

TDI VCCPD supply of Bank 1A

TDO Leave open

TRST GND

Note to Table 13–7:

(1) There is no software option to disable JTAG in Stratix III devices. The JTAG pins are dedicated.

IEEE Std. 1149.1 BST Guidelines

Use the following guidelines when performing boundary-scan testing with IEEE Std.

1149.1 devices:

■ If the “10...” pattern does not shift out of the instruction register through the TDO

pin during the first clock cycle of the SHIFT_IR state, the TAP controller did not

reach the proper state. To solve this problem, try one of the following procedures:

■ Verify that the TAP controller has reached the SHIFT_IR state correctly. To

advance the TAP controller to the SHIFT_IR state, return to the RESET state

and send the code 01100 to the TMS pin.

■ Check the connections to the VCC, GND, JTAG, and dedicated configuration

pins on the device.

Do NOT use the following private instructions as they may render the device

inoperable:

11 0001 0000

00 1100 1001

11 0001 0011

11 0001 0111

You should take precautions to avoid invoking these instructions at any time.

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–20 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

Boundary-Scan Description Language (BSDL) Support

■ Perform a SAMPLE/PRELOAD test cycle prior to the first EXTEST test cycle to

ensure that known data is present at the device pins when you enter the EXTEST

mode. If the OEJ update register contains a 0, the data in the OUTJ update register

is driven out. The state must be known and correct to avoid contention with other

devices in the system.

■ Do not perform EXTEST testing during ICR. This instruction is supported before

or after ICR, but not during ICR. Use the CONFIG_IO instruction to interrupt

configuration and then perform testing, or wait for configuration to complete.

■ If performing testing before configuration, hold the nCONFIG pin low.

f For more information about boundary scan testing, contact Altera® Application at

www.altera.com.

Boundary-Scan Description Language (BSDL) Support

The Boundary-Scan Description Language (BSDL), a subset of VHDL, provides a

syntax that allows you to describe the features of an IEEE Std. 1149.1 BST-capable

device that can be tested. Test software development systems then use the BSDL files

for test generation, analysis, and failure diagnostics.

f For more information about BSDL files for IEEE Std. 1149.1-compliant Stratix III

devices, refer to the Stratix III BSDL Files page on the Altera website.

To perform BST on a configured device, you will require a post configuration BSDL

file that is customized to your design. This file can be generated with the BSDL

Customizer script.

f For more information about the BSDL Customizer, refer to the Altera BSDL Support

page on the Altera website.

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices 13–21

Chapter Revision History

Chapter Revision History

Table 13–8 lists the revision history for this chapter.

Table 13–8. Chapter Revision History

Date Version Changes Made

July 2010 1.9 Updated Table 13–1.

Updated for the Quartus II software version 9.1 SP2 release:

March 2010 1.8 ■ Removed “IEEE Std. 1149.1 BST for Configured Devices” and “Conclusion” section.

■ Updated Table 13–5.

■ Updated Table 13–1.

May 2009 1.7 ■ Updated “I/O Voltage Support in JTAG Chain” and “IEEE Std. 1149.1 BST Circuitry”

sections.

February 2009 1.6 Removed “Referenced Documents” section.

■ Updated Table 13–4.

October 2008 1.5

■ Updated New Document Format.

■ Updated Table 13–2 and Table 13–5 with EP3SL150ES information.

May 2008 1.4 ■ Updated Table 13–6.

■ Updated Figure 13–6.

November 2007 1.3 Updated Table 13–2.

■ Added new section “Referenced Documents”.

October 2007 1.2

■ Added live links for references.

■ Updated Note 3 to Table 13–3. Updated Figure 13–6.

■ Added Table 13–2, Table 13–4, Table 13–5, and Table 13–7.

May 2007 1.1 ■ Removed opening paragraph and footnote for “IEEE Std. 1149.1 BST Operation

Control” on page 13–9.

■ Added warning on page 13-22.

November 2006 1.0 Initial Release.

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 1

13–22 Chapter 13: IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices

Chapter Revision History

Stratix III Device Handbook, Volume 1 © July 2010 Altera Corporation

Potrebbero piacerti anche

- IEEE 1149.1 (JTAG) Boundary-Scan Testing For Cyclone II DevicesDocumento20 pagineIEEE 1149.1 (JTAG) Boundary-Scan Testing For Cyclone II DevicesKesavaram ChallapalliNessuna valutazione finora

- 8 JTAG Unit 8Documento19 pagine8 JTAG Unit 8nareshNessuna valutazione finora

- Boundary Scan: Joint Test Action Group (Jtag)Documento10 pagineBoundary Scan: Joint Test Action Group (Jtag)anuNessuna valutazione finora

- JTAG TAP ControllerDocumento5 pagineJTAG TAP ControllerTanmayKabra100% (1)

- Vinay Sharma: Director, Ni2designsDocumento6 pagineVinay Sharma: Director, Ni2designspranithpreethNessuna valutazione finora

- Boundary Scan TesterDocumento5 pagineBoundary Scan Testerrohitsingh2909Nessuna valutazione finora

- Design of Ieee 1149.1 Tap Controller Ip CoreDocumento12 pagineDesign of Ieee 1149.1 Tap Controller Ip CoreCS & ITNessuna valutazione finora

- Jtag PresentationDocumento21 pagineJtag PresentationNivaz ChockkalingamNessuna valutazione finora

- An Introduction To JTAG Boundary Scan From Sun MicroelectronicsDocumento10 pagineAn Introduction To JTAG Boundary Scan From Sun MicroelectronicsJoemill Veloso FlordelisNessuna valutazione finora

- 5 JtagDocumento64 pagine5 Jtagsharad2208Nessuna valutazione finora

- JTAG Principles and InterfaceDocumento27 pagineJTAG Principles and InterfaceMotamarri AravindNessuna valutazione finora

- Jtag System: With Openocd ExplanationDocumento17 pagineJtag System: With Openocd ExplanationMohammed Publications100% (1)

- Jtag 1Documento12 pagineJtag 1lavanyaNessuna valutazione finora

- Boundary Scan, JTAG, IEEE 1149.1 TutorialDocumento6 pagineBoundary Scan, JTAG, IEEE 1149.1 Tutorialmelvin45Nessuna valutazione finora

- App Arm JtagDocumento33 pagineApp Arm Jtagcarver_uaNessuna valutazione finora

- Xapp 017Documento17 pagineXapp 017JavierPariNessuna valutazione finora

- Using In-System Programming in Boundary-Scan Systems: TAP TimingDocumento8 pagineUsing In-System Programming in Boundary-Scan Systems: TAP TimingNandhini IlangovanNessuna valutazione finora

- JTAG TutorialDocumento6 pagineJTAG Tutorialmrunal1729Nessuna valutazione finora

- JTAG TutorialDocumento8 pagineJTAG TutorialVinay KrNessuna valutazione finora

- WWW DFT Co UkDocumento28 pagineWWW DFT Co UkHaryo BhirowoNessuna valutazione finora

- Boundary ScanDocumento12 pagineBoundary ScanMukul TanwarNessuna valutazione finora

- Scan and JTAG Principles: Advanced RISC MachinesDocumento22 pagineScan and JTAG Principles: Advanced RISC MachinesmivaepaoNessuna valutazione finora

- Boundary Scan: Boundary Scan Is A Method For Testing Interconnects (Wire Lines) OnDocumento5 pagineBoundary Scan: Boundary Scan Is A Method For Testing Interconnects (Wire Lines) OnParthepan SkyriderNessuna valutazione finora

- Boundary ScanDocumento61 pagineBoundary ScanGéza HorváthNessuna valutazione finora

- Timing and Control Signal Generator in RadarDocumento6 pagineTiming and Control Signal Generator in RadarsmsarmadNessuna valutazione finora

- Cyc c51013 33-37Documento5 pagineCyc c51013 33-37Huascar Anavi loayzaNessuna valutazione finora

- PW01Documento12 paginePW01HugoNessuna valutazione finora

- Jtag - AN IEEE 1149.1 STDDocumento42 pagineJtag - AN IEEE 1149.1 STDkanchanstiwariNessuna valutazione finora

- An 095Documento11 pagineAn 095tazzo2Nessuna valutazione finora

- Computer and Interfacing Chapter Six Pin and Clock GeneratorDocumento78 pagineComputer and Interfacing Chapter Six Pin and Clock GeneratormigadNessuna valutazione finora

- Max 6901 EtatDocumento18 pagineMax 6901 Etatrt23.kysliuk.artemNessuna valutazione finora

- Tc-Io-1.21 RCP Data SheetDocumento2 pagineTc-Io-1.21 RCP Data Sheetfahmi1987Nessuna valutazione finora

- Jtag 2 PDFDocumento21 pagineJtag 2 PDFravisguptajiNessuna valutazione finora

- CPLD JtagDocumento20 pagineCPLD Jtagjustinvil1103Nessuna valutazione finora

- STL4N10F7Documento15 pagineSTL4N10F7angel uriel silvaNessuna valutazione finora

- Slvs 038 IDocumento28 pagineSlvs 038 Igabriel6276Nessuna valutazione finora

- Tlx84X Current-Mode PWM Controllers: 1 Features 3 DescriptionDocumento26 pagineTlx84X Current-Mode PWM Controllers: 1 Features 3 DescriptionAnonymous t9tLb3WgNessuna valutazione finora

- Et-Arm7 Start Kit v1 ManualDocumento5 pagineEt-Arm7 Start Kit v1 Manualstunner08Nessuna valutazione finora

- DataSMART 656Documento2 pagineDataSMART 656bakh777196Nessuna valutazione finora

- IEEE 1149.1 Test Access PortDocumento17 pagineIEEE 1149.1 Test Access PortChinmay100% (1)

- Accurate and Low Jitter Time-Interval Generators Based On Phase Shifting MethodDocumento5 pagineAccurate and Low Jitter Time-Interval Generators Based On Phase Shifting MethodnorbertscribdNessuna valutazione finora

- Study of Temperature Sensor (TMP139) Based On I3C InterfaceDocumento5 pagineStudy of Temperature Sensor (TMP139) Based On I3C InterfaceIJRASETPublicationsNessuna valutazione finora

- V3i3 Ijertv3is031737Documento3 pagineV3i3 Ijertv3is031737takaca40Nessuna valutazione finora

- Service Center Repairs We Buy Used Equipment: InstraDocumento9 pagineService Center Repairs We Buy Used Equipment: InstradikastaloneNessuna valutazione finora

- Jitter-Wander Measurements GuideDocumento30 pagineJitter-Wander Measurements GuidegercruNessuna valutazione finora

- Relay Idt8n 87Documento56 pagineRelay Idt8n 87Dan Storytime RodriguezNessuna valutazione finora

- Lecture08 PDFDocumento52 pagineLecture08 PDFNik F. RafiqNessuna valutazione finora

- XP-Series ASTM Communication Specifications en Ver.1.0 (R312006)Documento18 pagineXP-Series ASTM Communication Specifications en Ver.1.0 (R312006)Aron Raymond0% (1)

- Debugging With JTAGDocumento43 pagineDebugging With JTAGGlen MonetteNessuna valutazione finora

- Uart Core Ug v3.6Documento18 pagineUart Core Ug v3.6haniamani37Nessuna valutazione finora

- CFG cf52004-1299428Documento27 pagineCFG cf52004-1299428Abner FrancoNessuna valutazione finora

- 09 - I2C Serial CommunicationsmDocumento10 pagine09 - I2C Serial CommunicationsmSorabh DungNessuna valutazione finora

- Ijtag Embedded Instrument ADC Xilinx SYSMONDocumento11 pagineIjtag Embedded Instrument ADC Xilinx SYSMONMoni QueNessuna valutazione finora

- IEC 61850-9-2LE IEC 61869-9: Our SolutionDocumento3 pagineIEC 61850-9-2LE IEC 61869-9: Our SolutionPavan Kumar A GNessuna valutazione finora

- 1 Introduction To Boundary-ScanDocumento60 pagine1 Introduction To Boundary-ScanHassine OueslatiNessuna valutazione finora

- Practical Data Acquisition for Instrumentation and Control SystemsDa EverandPractical Data Acquisition for Instrumentation and Control SystemsNessuna valutazione finora

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipDa EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNessuna valutazione finora

- TVLSI Assignment2 RaviYadav 2019HT80073Documento6 pagineTVLSI Assignment2 RaviYadav 2019HT80073Yadav RaviNessuna valutazione finora

- HWSW Assignment2 RaviYadav 2019HT80073Documento16 pagineHWSW Assignment2 RaviYadav 2019HT80073Yadav RaviNessuna valutazione finora

- Smart Cards: A Plastic Card With An Intelligent Brain Embedded!!Documento17 pagineSmart Cards: A Plastic Card With An Intelligent Brain Embedded!!Yadav RaviNessuna valutazione finora

- Solutions To Problems From Essentials of Electronic TestingDocumento215 pagineSolutions To Problems From Essentials of Electronic TestingPradeep Chandra82% (28)

- Temperation Sensitive Read AssistDocumento2 pagineTemperation Sensitive Read AssistYadav RaviNessuna valutazione finora

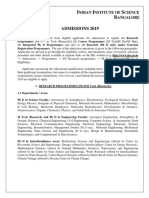

- I I S B: Admissions 2019Documento5 pagineI I S B: Admissions 2019Saurabh KumarNessuna valutazione finora

- Routing and Switching Technology Entry Lab Guide V2.2Documento143 pagineRouting and Switching Technology Entry Lab Guide V2.2Akhmad Arief Syah'bandikaNessuna valutazione finora

- Cnmaestro 3.1.0 Release NotesDocumento16 pagineCnmaestro 3.1.0 Release NotesVenite SoporteNessuna valutazione finora

- Audio CheckerDocumento2 pagineAudio CheckerKhristos ZuluNessuna valutazione finora

- CloudEngine 6800&5800 V100R001C00 Configuration Guide - Device Management 04 PDFDocumento146 pagineCloudEngine 6800&5800 V100R001C00 Configuration Guide - Device Management 04 PDFMenganoFulanoNessuna valutazione finora

- Profibus FMS CommunicationDocumento5 pagineProfibus FMS CommunicationMhd Samer AlHamwiNessuna valutazione finora

- Designer Profile For Jonathan IveDocumento6 pagineDesigner Profile For Jonathan IveJaneNessuna valutazione finora

- JBoss Drools Business RulesDocumento13 pagineJBoss Drools Business RulesSrinivas KadiyalaNessuna valutazione finora

- Konica Minolta Bizhub 362 Copier BrochureDocumento12 pagineKonica Minolta Bizhub 362 Copier BrochurepurjanjipurNessuna valutazione finora

- NEC IPasolink EX BrochureDocumento2 pagineNEC IPasolink EX BrochureIbrahim MaihoubNessuna valutazione finora

- S7plcsim Advanced Readme en-US en-USDocumento5 pagineS7plcsim Advanced Readme en-US en-USNhat Tan MaiNessuna valutazione finora

- DVD R120 SamsungDocumento95 pagineDVD R120 SamsungPerla Guadalupe Jara JimenezNessuna valutazione finora

- ATM Interface TAFJ Installation GuideDocumento26 pagineATM Interface TAFJ Installation GuideTsomondo Kudakwashe100% (1)

- MagicINFO DataLink and DataModule - DATASHEET - 20151005Documento5 pagineMagicINFO DataLink and DataModule - DATASHEET - 20151005Omar Hero MadridNessuna valutazione finora

- XCP ProDocumento366 pagineXCP ProCharitha Ranwala100% (1)

- WR Firewall Programmers Guide 1.1 PDFDocumento133 pagineWR Firewall Programmers Guide 1.1 PDFNitesh SinghNessuna valutazione finora

- Bypass FirewallDocumento8 pagineBypass Firewallamitk402Nessuna valutazione finora

- File Structures An ObjectOriented Approach With CDocumento749 pagineFile Structures An ObjectOriented Approach With CLuis Jose Castillo100% (3)

- Ds PIC30 F4013Documento5 pagineDs PIC30 F4013RaulsoftNessuna valutazione finora

- Huawei AirEngine 8760R-X1 & AirEngine 8760R-X1E Access Points Datasheet PDFDocumento14 pagineHuawei AirEngine 8760R-X1 & AirEngine 8760R-X1E Access Points Datasheet PDFnew signNessuna valutazione finora

- Convert Your Blog Into A PDF: ExportDocumento4 pagineConvert Your Blog Into A PDF: ExportJm MedinaNessuna valutazione finora

- LAB 8 - Web ProxyDocumento14 pagineLAB 8 - Web ProxyJuan PerezNessuna valutazione finora

- Network Security FundamentalsDocumento41 pagineNetwork Security FundamentalsMarco Lopez ReinosoNessuna valutazione finora

- ECEN 449 749: Microprocessor System Design Department of Electrical and Computer Engineering Texas A&M UniversityDocumento4 pagineECEN 449 749: Microprocessor System Design Department of Electrical and Computer Engineering Texas A&M Universityroby nkwamoNessuna valutazione finora

- Ashida Scada BrochureDocumento8 pagineAshida Scada Brochurerahulyadav2121545Nessuna valutazione finora

- OptiX OSN 550+-10.21.156Documento115 pagineOptiX OSN 550+-10.21.156Raja SolaimalaiNessuna valutazione finora

- Nprobe User GuideDocumento60 pagineNprobe User GuideAnonymous UjgMWXNessuna valutazione finora

- For Butter or Worse Smoothing Out Performance in Android UisDocumento135 pagineFor Butter or Worse Smoothing Out Performance in Android UisSteinerOkNessuna valutazione finora

- FITEL Telecom Projects For Regions of PeruDocumento43 pagineFITEL Telecom Projects For Regions of PeruFitel Fondo DE InversionNessuna valutazione finora

- Unit - II Microprocessors-and-Microcontrollers - CompressedDocumento22 pagineUnit - II Microprocessors-and-Microcontrollers - CompressedVishalNessuna valutazione finora

- Acrwfoguide - en Integration GuideDocumento28 pagineAcrwfoguide - en Integration GuideDanish ShaikhNessuna valutazione finora