Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

VLSI Problems of Chapter 3

Caricato da

Ahsan MoinTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

VLSI Problems of Chapter 3

Caricato da

Ahsan MoinCopyright:

Formati disponibili

Assignment#3

Submission date: April, 2012

Problems of chapter 3

Q 1. Given the data in Table 1 for a short channel NMOS transistor with VDSAT = 0.6 V and k

′=100 μA/V2, calculate VT0, γ, λ, 2|φf|, and W / L:

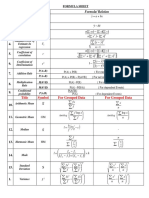

Table1. Measured NMOS transistor data

Q 2. Given Table 2 ,the goal is to derive the important device parameters from

these data points. As the measured transistor is processed in a deep-submicron technology, the

‘unified model’ holds. From the material constants, we also could determine that the saturation

voltage VDSAT equals -1V. You may also assume that -2ΦF = -0.6V.

a. Is the measured transistor a PMOS or an NMOS device? Explain your answer.

b. Determine the value of VT0.

c. Determine γ.

d. Determine λ.

e. Given the obtained answers, determine for each of the measurements the operation region

of the transistor (choose from cutoff, resistive, saturated, and velocity saturated). Annotate

your finding in the right-most column of the above.

Table 2. Measurements taken from the MOS device, at different terminal voltages.

Q 3. An NMOS device is plugged into the test configuration shown below in Figure

1. The input Vin =2V. The current source draws a constant current of 50 μA. R is a variable

resistor that can assume values between 10kΩ and 30 kΩ. Transistor M1 experiences

short channel effects and has following transistor parameters: k’ = 110x10-6 V/A2, VT = 0.4 ,

and VDSAT = 0.6V. The transistor has a W/L = 2.5μ/0.25μ. For simplicity body effect and

channel length modulation can be neglected. i.e λ=0, γ=0. .

Figure 1. Test configuration for the NMOS device.

a. When R =10kΩ find the operation region, VD and VS.

b. When R= 30kΩ again determine the operation region VD, VS

c. For the case of R = 10kΩ, would VS increase or decrease if λ ≠ 0. Explain qualitatively

Q 4. Consider the circuit configuration of Figure 2.

a. Write down the equations (and only those) which are needed to determine the voltage at

node X. Do NOT plug in any values yet. Neglect short channel effects and assume that λp

= 0.

b. Determine the required width of the transistor (for L = 0.25μm) such that X equals 1.5 V.

Figure 2. MOS circuit.

Q 5. The circuit of Figure 3 is known as a source-follower configuration. It

achieves a DC level shift between the input and output. The value of this shift is determined

by the current I0. Assume γ = 0.4, 2|φf| = 0.6 V, VT0 = 0.43 V, k′ = 115 μA/V2, and λ = 0. The

NMOS device has W/L = 5.4μ/1.2μ such that the short channel effects are not observed.

a. Derive an expression giving Vi as a function of Vo and VT(Vo). If we neglect body effect,

what is the nominal value of the level shift performed by this circuit.

b. The NMOS transistor experiences a shift in VT due to the body effect. Find VT as a function

of Vo for Vo ranging from 0 to 1.5V with 0.25 V intervals. Plot VT vs. Vo.

c. Plot Vo vs. Vi as Vo varies from 0 to 1.5 V with 0.25 V intervals. Plot two curves: one

neglecting the body effect and one accounting for it. How does the body effect influence

the operation of the level converter? At Vo (body effect) = 1.5 V, find Vo (ideal) and, thus,

determine the maximum error introduced by body effect.

Figure 3. Source-follower level converter.

Q 6. Short-channel effects:

a. Use the fact that current can be expressed as the product of the carrier charge per unit

length and the velocity of carriers (IDS = Qv) to derive IDS as a function of W, Cox, VGS – VT,

and carrier velocity v.

b. For a long-channel device, the carrier velocity is the mobility times the applied electric

field. The electrical field, which has dimensions of V/m, is simply (VGS – VT) / 2L. Derive

IDS for a long-channel device.

c. From the equation derived in a, find IDS for a short-channel device in terms of the maximum

carrier velocity, vmax.

Based on the results of b and c describe the most important differences between shortchannel

and long-channel devices.

Q 7. Another equation, which models the velocity-saturated drain current of an

MOS transistor is given by

Using this equation it is possible to see that velocity saturation can be modeled by a MOS

device with a source-degeneration resistor (see Figure 4).

a. Find the value of RS such that IDSAT(VGS, VDS) for the composite transistor in the figure

matches the above velocity-saturated drain current equation. Hint: the voltage drop across

RS is typically small.

b. Given Esat = 1.5 V/μm and k′ = μ0Cox = 20 μA/V2, what value of RS is required to model

velocity saturation. How does this value depend on W and L?

Figure 4. Source-degeneration model of velocity saturation.

Q 8. Compute the gate and diffusion capacitances for transistor M1 of Figure5.

Assume that drain and source areas are rectangular, and are 1 μm wide and 0.5 μm long. Use

the parameters of table 3.5(in book) to determine the capacitance values. Assume mj = 0.5 and

mjsw = 0.44. Also compute the total charge stored at node In, for the following initial conditions:

a. Vin = 2.5 V, Vout = 2.5 V, 0.5 V, and 0 V.

b. Vin = 0 V, Vout = 2.5 V, 0.5 V, and 0 V.

Figure 5.

Q 9. Consider an NMOS transistor with the following parameters: tox=6nm, L=0.24μm,

W=0.36μm, LD = LS=0.625μm, CO =3X10-10 F/m2, and Cjsw0=2.75x10-10F/m. Determine the zero

bias value of all relevant capacitances.

Potrebbero piacerti anche

- 6th Central Pay Commission Salary CalculatorDocumento15 pagine6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- XBOX 360 Back up and Burn ToolKit GuideDocumento103 pagineXBOX 360 Back up and Burn ToolKit GuideLeeann TaverasNessuna valutazione finora

- MOS Transistor IV Modeling and Regions of OperationDocumento47 pagineMOS Transistor IV Modeling and Regions of OperationRaga LasyaNessuna valutazione finora

- Solns - 1 CmosDocumento15 pagineSolns - 1 Cmosramprakash_rampelliNessuna valutazione finora

- MOSFET circuit analysis and design techniquesDocumento85 pagineMOSFET circuit analysis and design techniquesTaís LaurindoNessuna valutazione finora

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Documento34 pagineDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaNessuna valutazione finora

- CBORDocumento3 pagineCBORsweeti sahNessuna valutazione finora

- Vision Guided Robotics Maximizes Flexibility, Quality and Cost SavingsDocumento24 pagineVision Guided Robotics Maximizes Flexibility, Quality and Cost SavingsPedro SolNessuna valutazione finora

- MOSFET Electronics Devices AssignmentDocumento5 pagineMOSFET Electronics Devices AssignmentShaheer ShahzadNessuna valutazione finora

- Sheet 3 - SolutionDocumento10 pagineSheet 3 - SolutionMajid HelmyNessuna valutazione finora

- ESDynamic Logic CircuitsDocumento61 pagineESDynamic Logic CircuitsMandovi BorthakurNessuna valutazione finora

- Dynamic Logic CktsDocumento16 pagineDynamic Logic CktsaashishscribdNessuna valutazione finora

- Mos Transistor TheoryDocumento144 pagineMos Transistor TheorymailtolokiNessuna valutazione finora

- ELEC ENG 2EI5 Microelectronics Final ExamDocumento4 pagineELEC ENG 2EI5 Microelectronics Final ExamFilip ZubacNessuna valutazione finora

- 10 Metal-Semiconductor JunctionsDocumento56 pagine10 Metal-Semiconductor JunctionsKamalesh DebnathNessuna valutazione finora

- Mosfet 1Documento33 pagineMosfet 1Palash SwarnakarNessuna valutazione finora

- Resistance CapacitanceDocumento24 pagineResistance Capacitancemayurp90100% (1)

- Flash ADC MidsemDocumento9 pagineFlash ADC MidsemBikashKumarMoharanaNessuna valutazione finora

- EE 174 Fall 2019: Operational AmplifiersDocumento36 pagineEE 174 Fall 2019: Operational AmplifiersKavyashreeMNessuna valutazione finora

- ECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEDocumento6 pagineECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEAnwar Zainuddin100% (2)

- Clocked CmosDocumento24 pagineClocked CmosAnil KumarNessuna valutazione finora

- MOSFETDocumento13 pagineMOSFETMarkCabalunaNessuna valutazione finora

- VLSI Lab CompendiumDocumento52 pagineVLSI Lab CompendiumSaad Ali Khan SherwaniNessuna valutazione finora

- DelayDocumento31 pagineDelayvarun186Nessuna valutazione finora

- Elmore Delay in RC Networks: September 16, 2010Documento3 pagineElmore Delay in RC Networks: September 16, 2010Siddharth SabharwalNessuna valutazione finora

- Aulas15 16Documento16 pagineAulas15 16Pramod Reddy RNessuna valutazione finora

- PROJECT1 S 2013 v2 PDFDocumento4 paginePROJECT1 S 2013 v2 PDFHarshal SinghNessuna valutazione finora

- Design of Variable Resolution Flash ADC Using TIQDocumento30 pagineDesign of Variable Resolution Flash ADC Using TIQJoHnson TaYeNessuna valutazione finora

- Assignment 1Documento9 pagineAssignment 1Taslima Rahman MiliNessuna valutazione finora

- Digital Circuits: CMOS Dynamic Operation and Load CapacitanceDocumento32 pagineDigital Circuits: CMOS Dynamic Operation and Load CapacitanceShwetaGautamNessuna valutazione finora

- Metal-Semiconductor Junctions PDFDocumento22 pagineMetal-Semiconductor Junctions PDFTuncay YeşilkaynakNessuna valutazione finora

- Dynamic Logic Circuits: A. MarzukiDocumento25 pagineDynamic Logic Circuits: A. Marzukisreekanthreddy peramNessuna valutazione finora

- Lecture 8 - Circuits Design Issues and Layout FormationDocumento18 pagineLecture 8 - Circuits Design Issues and Layout FormationevildoctorbluetoothNessuna valutazione finora

- CMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETDocumento16 pagineCMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETNIET14Nessuna valutazione finora

- DC Operating Point at Cadence PDFDocumento3 pagineDC Operating Point at Cadence PDFAhmed Edris100% (1)

- ZhengchenDocumento139 pagineZhengchenAnh PhanNessuna valutazione finora

- HSPICE TutorialDocumento7 pagineHSPICE TutorialSreyas MohanNessuna valutazione finora

- SPICE ParametersDocumento4 pagineSPICE ParametersKaran KeherNessuna valutazione finora

- Lec3 Single Stage PDFDocumento24 pagineLec3 Single Stage PDFRavinder KumarNessuna valutazione finora

- Format of HSPICE NetlistDocumento2 pagineFormat of HSPICE NetlistJinesh PatelNessuna valutazione finora

- 33 7 LM V1 S1 Delay ModelingDocumento39 pagine33 7 LM V1 S1 Delay ModelingPriyanka AshishNessuna valutazione finora

- Fiduccia-Mattheyses Algorithm: Perform FM Algorithm On The Following CircuitDocumento12 pagineFiduccia-Mattheyses Algorithm: Perform FM Algorithm On The Following CircuitiiitsainiNessuna valutazione finora

- VLSIDocumento12 pagineVLSIPeer MohamedNessuna valutazione finora

- Active Loads and IC MOS AmplifiersDocumento41 pagineActive Loads and IC MOS AmplifiersKamlaNessuna valutazione finora

- Laplace Transform GuideDocumento10 pagineLaplace Transform Guideariana_kardiamouNessuna valutazione finora

- Electrical Network Analysis Lab Course Lab Course: Prepared By: Husan AliDocumento34 pagineElectrical Network Analysis Lab Course Lab Course: Prepared By: Husan AliengrhusanNessuna valutazione finora

- Tutorial 5 SolutionsDocumento11 pagineTutorial 5 SolutionsbarneyNessuna valutazione finora

- TriennaleDocumento129 pagineTriennaleJesus UrrestiNessuna valutazione finora

- Dynamic Logic CircuitsDocumento38 pagineDynamic Logic Circuitssreekanthreddy peramNessuna valutazione finora

- ETIN25 - Analogue IC Design Laboratory Manual - Lab 2: Jonas Lindstrand Martin Liliebladh Markus Törmänen September 2011Documento14 pagineETIN25 - Analogue IC Design Laboratory Manual - Lab 2: Jonas Lindstrand Martin Liliebladh Markus Törmänen September 2011Western777Nessuna valutazione finora

- Design of Analog Integrated Circuits and SystemsDocumento10 pagineDesign of Analog Integrated Circuits and Systemsecedeptt0% (1)

- iNVERTER aSSIGN6 1Documento6 pagineiNVERTER aSSIGN6 1Rohan ChopraNessuna valutazione finora

- Chapter03 ExDocumento10 pagineChapter03 ExKarthikeya VemparalaNessuna valutazione finora

- MOS Transistor Analysis and Circuit DesignDocumento4 pagineMOS Transistor Analysis and Circuit DesignAnh KhoaNessuna valutazione finora

- Ec3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopDocumento2 pagineEc3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopGamer AnonymousNessuna valutazione finora

- Sheet 1Documento4 pagineSheet 1MohamedAlyNessuna valutazione finora

- Mosfet Lab 1Documento11 pagineMosfet Lab 1Pramod SnkrNessuna valutazione finora

- Vlsi Questions-2Documento8 pagineVlsi Questions-2Chinu SoodNessuna valutazione finora

- Chapter 5 Problems CMOS INVERTERDocumento8 pagineChapter 5 Problems CMOS INVERTERShykh SheharyarNessuna valutazione finora

- SheetDocumento3 pagineSheetb5fc94cdd3Nessuna valutazione finora

- ExcersisesDocumento19 pagineExcersisesLÊ QUANG BÁ LĨNHNessuna valutazione finora

- Vlsi Question Paper 2Documento3 pagineVlsi Question Paper 2Chinu SoodNessuna valutazione finora

- Ranna Munna PDFDocumento5 pagineRanna Munna PDFrakshithNessuna valutazione finora

- ARF Current MirrorDocumento11 pagineARF Current MirrorJk WorldNessuna valutazione finora

- Solid State Physics MCQsDocumento7 pagineSolid State Physics MCQsAhsan MoinNessuna valutazione finora

- Assignment No. 01 Solid State PhysicsDocumento1 paginaAssignment No. 01 Solid State PhysicsAhsan MoinNessuna valutazione finora

- Transmission Lines and Waveguides QuestionsDocumento18 pagineTransmission Lines and Waveguides QuestionsPolaiah GerikiNessuna valutazione finora

- Perception of Fine Dining in ResturantDocumento28 paginePerception of Fine Dining in ResturantAhsan MoinNessuna valutazione finora

- List of ContentsDocumento7 pagineList of ContentsAhsan MoinNessuna valutazione finora

- Signal Flow GraphDocumento29 pagineSignal Flow GraphAhsan MoinNessuna valutazione finora

- YALDocumento23 pagineYALAhsan MoinNessuna valutazione finora

- Lab 1Documento1 paginaLab 1Ahsan MoinNessuna valutazione finora

- Adidas Mission and VisionDocumento17 pagineAdidas Mission and VisionAhsan MoinNessuna valutazione finora

- DwatsonDocumento1 paginaDwatsonAhsan MoinNessuna valutazione finora

- Development - Phase 4 of NPDDocumento16 pagineDevelopment - Phase 4 of NPDAhsan MoinNessuna valutazione finora

- Bloch TheoremDocumento12 pagineBloch TheoremAhsan MoinNessuna valutazione finora

- Mobile Comm. PrinciplesDocumento23 pagineMobile Comm. Principlesn2hj2nNessuna valutazione finora

- Crystal Structure FundamentalsDocumento26 pagineCrystal Structure FundamentalsAhsan MoinNessuna valutazione finora

- CMBA Exam Sample QuestionsDocumento6 pagineCMBA Exam Sample QuestionsAhsan MoinNessuna valutazione finora

- IELTS Handbook 2007 PDFDocumento22 pagineIELTS Handbook 2007 PDFAhsan MoinNessuna valutazione finora

- Formulas for ANOVA, Chi Square, T-Test, Z-Test & Coefficient of VarianceDocumento1 paginaFormulas for ANOVA, Chi Square, T-Test, Z-Test & Coefficient of VarianceAhsan MoinNessuna valutazione finora

- Stats Formula Sheet 1Documento1 paginaStats Formula Sheet 1Ahsan MoinNessuna valutazione finora

- Training and DevelopmentDocumento6 pagineTraining and DevelopmentAhsan MoinNessuna valutazione finora

- Break BreadDocumento35 pagineBreak BreadAhsan MoinNessuna valutazione finora

- Break BreadDocumento33 pagineBreak BreadAhsan MoinNessuna valutazione finora

- Troubleshooting Guide Omnipcx EnterpriseDocumento16 pagineTroubleshooting Guide Omnipcx EnterpriseHumberto Ochoa MendezNessuna valutazione finora

- Mks Ct150 Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocumento2 pagineMks Ct150 Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNessuna valutazione finora

- Result - VAS - B Tech S5 (R& S) Dec 2019 PDFDocumento49 pagineResult - VAS - B Tech S5 (R& S) Dec 2019 PDFGjNessuna valutazione finora

- Ibrahiem Abd Elrahman MohammedDocumento2 pagineIbrahiem Abd Elrahman MohammedHema AbdoNessuna valutazione finora

- System Verilog Quick View 4pagesDocumento9 pagineSystem Verilog Quick View 4pagesMani KumarNessuna valutazione finora

- Assignment Guide For ProgrammingDocumento8 pagineAssignment Guide For ProgrammingPrajik ShresthaNessuna valutazione finora

- PDFTron PDF2Text User ManualDocumento21 paginePDFTron PDF2Text User ManualTuấn MinhNessuna valutazione finora

- Spring Boot ReferenceDocumento692 pagineSpring Boot ReferencechivasNessuna valutazione finora

- Cacti Instalando CentOSDocumento9 pagineCacti Instalando CentOSleandroNessuna valutazione finora

- Forticlient v5.0.9 Windows Release NotesDocumento18 pagineForticlient v5.0.9 Windows Release NotesMiodrag BanacNessuna valutazione finora

- Cisco VPN Error CodesDocumento15 pagineCisco VPN Error CodesbossfnNessuna valutazione finora

- Procedure ICOMM CPE Firmware UpgradeDocumento14 pagineProcedure ICOMM CPE Firmware UpgradeAngad KumarNessuna valutazione finora

- An X2 DHP UserManualDocumento44 pagineAn X2 DHP UserManualAlejandro PerezNessuna valutazione finora

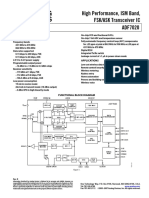

- High Performance, ISM Band, FSK/ASK Transceiver IC ADF7020: FeaturesDocumento48 pagineHigh Performance, ISM Band, FSK/ASK Transceiver IC ADF7020: FeaturesDNessuna valutazione finora

- GPS BTS-110 - User - ManualDocumento17 pagineGPS BTS-110 - User - ManualJulioneNessuna valutazione finora

- Systemverilog OVM UVM 3day TrainingDocumento10 pagineSystemverilog OVM UVM 3day TrainingTC SurendharNessuna valutazione finora

- Readme Win10 x64 5in1 Oct2015Documento2 pagineReadme Win10 x64 5in1 Oct2015Frumuzache FlorinNessuna valutazione finora

- DN304 - CCXXXX Development Tool - Texas Instruments, IncorporatedDocumento32 pagineDN304 - CCXXXX Development Tool - Texas Instruments, IncorporatedRaul RiveroNessuna valutazione finora

- IBM TotalStorage Virtual Tape Server Implementation and PlanningDocumento344 pagineIBM TotalStorage Virtual Tape Server Implementation and PlanningsenrameshNessuna valutazione finora

- Sy Ej Sem IV Dcs 22428 QP Model AnswersDocumento53 pagineSy Ej Sem IV Dcs 22428 QP Model Answersrohitsule0011Nessuna valutazione finora

- System Requirements Ansys 11Documento4 pagineSystem Requirements Ansys 11usacovadongafgNessuna valutazione finora

- Service Manual: HCD-GTX777/GTX787/GTX888Documento108 pagineService Manual: HCD-GTX777/GTX787/GTX888sixtoNessuna valutazione finora

- 9 - Object Oriented Programming Using PythonDocumento27 pagine9 - Object Oriented Programming Using PythonUmoora MinhajiNessuna valutazione finora

- BSNL GPON A/T ScheduleDocumento8 pagineBSNL GPON A/T Scheduleman_i_acNessuna valutazione finora

- Vivo Gallery Log ErrorsDocumento6 pagineVivo Gallery Log ErrorsHaniagaNessuna valutazione finora

- Sun Tracking System (Rahul Raj)Documento22 pagineSun Tracking System (Rahul Raj)Rahul Raj88% (8)

- Bangalore University: Computer Science and EngineeringDocumento25 pagineBangalore University: Computer Science and EngineeringBethel LalrotluangaNessuna valutazione finora