Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Rajiv Gandhi College of Engineering and Technology

Caricato da

Kannan Alagumuthiah0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

13 visualizzazioni2 pagineDigital Circuits Lesson Plan

Titolo originale

DC - LessonPlan

Copyright

© © All Rights Reserved

Formati disponibili

DOC, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoDigital Circuits Lesson Plan

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOC, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

13 visualizzazioni2 pagineRajiv Gandhi College of Engineering and Technology

Caricato da

Kannan AlagumuthiahDigital Circuits Lesson Plan

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOC, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 2

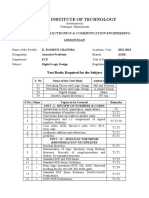

RAJIV GANDHI COLLEGE OF ENGINEERING AND TECHNOLOGY

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

LESSON PLAN

SUBJECT : DIGITAL CIRCUIT SUB CODE: EC T45

Staff In-charge : A.Kannan, Mr.B.Shanmugham

CUMULATIVE TOPICS COVERED BOOKS

PERIOD REFERRED

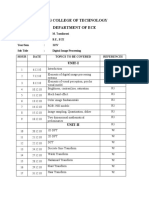

UNIT I - Number System

Binary Number Representations – Signed

0 T2

Numbers and Complements

Unsigned, Fixed point, and Floating point

1 T2

numbers

2 Addition T2, R2, R3

3 subtraction with 1’s and 2’s complements T2, R2, R3

4 Binary code for decimal numbers T2, R2, R3

5 Gray code T2, R2, R3

Codes for detecting and correcting errors:

7 T2, R2, R3

Even parity codes

Codes for detecting and correcting errors: Odd

9 T2, R2, R3

parity codes

Codes for detecting and correcting errors:

11 T2, R2, R3

Hamming Codes

Codes for detecting and correcting errors:

12 T2, R2, R3

Checksum codes

13 m-out–of-n-codes T2, R2, R3

UNIT II - Boolean Algebra

14 Basic theorems- Postulates T2

15 Duality T2

Boolean Function- Canonical form-Standard

16 T2

form

Simplification of Boolean

18 T2, R2, R3

Function:Karnaugh map method

20 Quine-McCluskey method T2, R2, R3

22 Incompletely specified functions T2, R2, R3

Realization of logic functions - NAND gate

23 T2, R2, R3

realization

Realization of logic functions - NOR gate

24 T2, R2, R3

realization

25 Multilevel synthesis T2, R2, R3

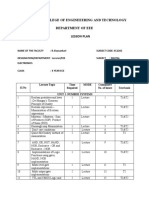

UNIT III - Combinational Logic Design

26 Half adder, Full adder T2, R2, R3

27 Parallel Adder, Carry Look Ahead Adder T2, R2, R3

28 BCD Adder T2, R2, R3

29 Magnitude Comparator T2, R2, R3

30 Encoders and Decoders T2, R2, R3

31 Multiplexers T2, R2, R3

32 Code converters T2, R2, R3

33 Parity generator, Parity checker T2, R2, R3

Combinational circuit implementation using

34 T2, R2, R3

multiplexers

Combinational circuit implementation using

35 T2, R2, R3

decoders

36 Programmable Logic Devices: PROM – T2, R2, R3

EPROM – EEPROM

37 Programmable Logic Array (PLA) T2, R2, R3

38 Programmable Array Logic (PAL) T2, R2, R3

Realization of combinational circuits using

39 T2, R2, R3

PROM,PLA and PAL

UNIT IV - Sequential Circuits

42 General model of sequential circuits T2, R2, R3

43 latches – Master-slave Configuration T2, R2, R3

44 Flip-Flops T2, R2, R3

45 Concept of State – State diagram – State Table T2, R2, R3

Synchronous Sequential Circuits – Binary

48 T2, R2, R3

ripple counters

50 Design of Synchronous counters T2, R2, R3

52 Binary counters T2, R2, R3

54 Arbitrary sequence counter T2, R2, R3

55 BCD counter T2, R2, R3

56 Shift Registers T2, R2, R3

57 Ring Counter T2, R2, R3

58 Johnson Counter T2, R2, R3

59 Timing diagram T2, R2, R3

60 Serial Adder T2, R2, R3

61 PN sequence generator T2, R2, R3

Sequential PLDs – Block diagrams of CPLD

62 T2, R2, R3

and Field programmable Gate Array (FPGA)

UNIT V – Memory

64 Classification of Memories T2, R2, R3

65 RAM Organization T2, R2, R3

66 Write Operation – Read Operation T2, R2, R3

67 Memory Cycle T2, R2, R3

68 Timing Waveforms T2, R2, R3

69 Memory Decoding T2, R2, R3

70 Memory Expansion T2, R2, R3

71 Static RAM Cell T2, R2, R3

72 Dynamic RAM Cell T2, R2, R3

Text Books:

1. John F. Wakerly, “Digital Design Principles and Practices”, PHI Private Ltd., New Delhi,

Fourth Edition, 2006

2. Morris Mano, “Digital design”, PHI Learning, Fourth Edition, 2008.

Reference Books:

1. Donald P Leach, Albert Paul Malvino and GoutamSaha, “Digital Principles and Applications,”

6 edition, Tata McGraw Hill Publishing Company Ltd.,New Delhi,2008.

th

2. Thomas L. Floyd, “Digital Fundamentals,” Dorling Kindersley (India) Pvt. Limited, 8th ed.,

2008.

3. Tocci R J, “Digital systems: Principles and Applications”, PHI learning, New Delhi, Tenth

Edition 2006.

Web References:

1. www.technologystudent.com

2. www.facstaff.bucknell.edu

3. www.chegg.com

Staff In-Charge

Potrebbero piacerti anche

- DLD LPDocumento2 pagineDLD LPRameshchandra K ECENessuna valutazione finora

- STLD (EEE) Teaching MethodologyDocumento3 pagineSTLD (EEE) Teaching MethodologyRahil HussainNessuna valutazione finora

- Compiler BlowupnDocumento1 paginaCompiler Blowupnapi-3812391Nessuna valutazione finora

- Pointers STEAM Robotic EASE 1Documento9 paginePointers STEAM Robotic EASE 1zkn 86Nessuna valutazione finora

- Lab Manual Advanced MicrocontrollerDocumento79 pagineLab Manual Advanced MicrocontrollertrippinNessuna valutazione finora

- ARM Slides Part3Documento33 pagineARM Slides Part3Asmitha G ee22b030Nessuna valutazione finora

- Channel Codes, Decoders and Implementation Architecture: Saikat MajumderDocumento18 pagineChannel Codes, Decoders and Implementation Architecture: Saikat MajumderSaikat MajumderNessuna valutazione finora

- Mini Ref AssemblerDocumento9 pagineMini Ref AssemblerVaibhavPatilNessuna valutazione finora

- Solution: Answer All Questions in The Provided Space. All Questions Are Based On AVR Architecture. 18 November 2020Documento4 pagineSolution: Answer All Questions in The Provided Space. All Questions Are Based On AVR Architecture. 18 November 2020BAHARUDIN BURAHNessuna valutazione finora

- Belimo Modbus RegisterDocumento13 pagineBelimo Modbus RegisterJonny GloverNessuna valutazione finora

- Technical Overview: Functions Ea Ea MFD-... CP8/CP10... Counter FunctionsDocumento1 paginaTechnical Overview: Functions Ea Ea MFD-... CP8/CP10... Counter FunctionsVirgil DamianNessuna valutazione finora

- Digital System (Full PDFDocumento150 pagineDigital System (Full PDFAmit RajputNessuna valutazione finora

- BI Technologies R2R Resistor Ladder NetworksDocumento6 pagineBI Technologies R2R Resistor Ladder NetworksRianKunNessuna valutazione finora

- Up & Uc - LessonPlanDocumento2 pagineUp & Uc - LessonPlanKannan AlagumuthiahNessuna valutazione finora

- HR200 User GuideDocumento118 pagineHR200 User GuideAkhmad Briamawan WakhidNessuna valutazione finora

- Cap 11 - RISC-V - Parte IDocumento22 pagineCap 11 - RISC-V - Parte IGuidoNessuna valutazione finora

- Computer Network Lesson PlanDocumento3 pagineComputer Network Lesson PlanJoshua eedaNessuna valutazione finora

- CH 01Documento31 pagineCH 01陳品涵Nessuna valutazione finora

- On The Analysis and Application of LDPC Codes: Olgica Milenkovic University of Colorado, BoulderDocumento51 pagineOn The Analysis and Application of LDPC Codes: Olgica Milenkovic University of Colorado, BouldersushanthsrkrNessuna valutazione finora

- Sensor Modbus-Register: 22DTH-..5.. 22UTH-..50X 22DTM-..5 22ADP-..5.Documento9 pagineSensor Modbus-Register: 22DTH-..5.. 22UTH-..50X 22DTM-..5 22ADP-..5.manzoor ansariNessuna valutazione finora

- Logic Contents All Chapters Except 5Documento198 pagineLogic Contents All Chapters Except 5Josealberto HernandezNessuna valutazione finora

- Basic PLCDocumento45 pagineBasic PLCisilpii4Nessuna valutazione finora

- 2 Introduction To Assembly v21Documento42 pagine2 Introduction To Assembly v21vokhacnam2k1Nessuna valutazione finora

- Vlsi Implementation of Turbo Decoder: Seminar OnDocumento22 pagineVlsi Implementation of Turbo Decoder: Seminar OnabizerattaryNessuna valutazione finora

- BaanERP Tools - Programming Features PDFDocumento228 pagineBaanERP Tools - Programming Features PDFSujatha Putra SudheerNessuna valutazione finora

- RS232 Serial Cable LayoutDocumento40 pagineRS232 Serial Cable Layoutjafarkhan1989100% (1)

- Lesson Plan - DipDocumento3 pagineLesson Plan - DiprajeshprpNessuna valutazione finora

- CH 08Documento82 pagineCH 08Luis Eduardo García QuesadaNessuna valutazione finora

- AVR ArchitectureDocumento25 pagineAVR Architectureநட்ராஜ் நாதன்Nessuna valutazione finora

- project5 謝博亦Documento28 pagineproject5 謝博亦Po PoNessuna valutazione finora

- Matlab Based Autonomous Ball Searching Robot Using Image ProcessingDocumento24 pagineMatlab Based Autonomous Ball Searching Robot Using Image Processingnikhil3298Nessuna valutazione finora

- Design of NHR1100 Single Loop Digital Display Parameter Indicator Based OnDocumento4 pagineDesign of NHR1100 Single Loop Digital Display Parameter Indicator Based OnRicardoAgredaNessuna valutazione finora

- L-3 Instruction ArchitectureDocumento41 pagineL-3 Instruction ArchitectureImran KhanNessuna valutazione finora

- MES LABORATORY Manual 2020Documento38 pagineMES LABORATORY Manual 2020Deepthi KNessuna valutazione finora

- An Instructional Processor Design Using VHDL and An FpgaDocumento10 pagineAn Instructional Processor Design Using VHDL and An FpgaRezwan KhanNessuna valutazione finora

- St. Peter'Scollege of Engineeering and Technology Department of Eee Lesson PlanDocumento11 pagineSt. Peter'Scollege of Engineeering and Technology Department of Eee Lesson PlanRaj Bharath Raju100% (1)

- DLD Assignment 2Documento3 pagineDLD Assignment 2siddharthsrathor04Nessuna valutazione finora

- AQA Assembly Language Questions and MSDocumento9 pagineAQA Assembly Language Questions and MSBen DaffadaNessuna valutazione finora

- AppendixD Assembly ArmDocumento53 pagineAppendixD Assembly ArmBilelAmerNessuna valutazione finora

- SERIES 2000: Modbus and Ei-Bisynch Digital Communications HandbookDocumento156 pagineSERIES 2000: Modbus and Ei-Bisynch Digital Communications HandbookKhaled El-BeheryNessuna valutazione finora

- Digital Weight Transmitter USER MANUALDocumento64 pagineDigital Weight Transmitter USER MANUALherlinanoviantyNessuna valutazione finora

- The 48 Laws of Power - 2Documento47 pagineThe 48 Laws of Power - 2probiggy007Nessuna valutazione finora

- Introduction To Arm AssemblyDocumento42 pagineIntroduction To Arm AssemblySureshNessuna valutazione finora

- 2.20RO2001 - DE & MicroprocessorsDocumento5 pagine2.20RO2001 - DE & MicroprocessorsRaj PNessuna valutazione finora

- Modified Python Lesson PlanDocumento3 pagineModified Python Lesson PlanValavala SrinivasuNessuna valutazione finora

- LDPC ConstrDocumento51 pagineLDPC Constrsravan padalaNessuna valutazione finora

- Co 1Documento43 pagineCo 1Akula Lakshmi SreenivasuluNessuna valutazione finora

- VL7101 VLSI Signal Processing Lesson PlanDocumento3 pagineVL7101 VLSI Signal Processing Lesson Planamlu menakaNessuna valutazione finora

- KickC Reference ManualDocumento51 pagineKickC Reference ManualSergio RicardoNessuna valutazione finora

- Signal Processsing ElementDocumento40 pagineSignal Processsing Elementkibrom atsbhaNessuna valutazione finora

- Answer ALL Questions.: (15 Marks)Documento8 pagineAnswer ALL Questions.: (15 Marks)Kenny MakNessuna valutazione finora

- Comm Manual Eng (Modicon Modbus+ (Rev.a) )Documento5 pagineComm Manual Eng (Modicon Modbus+ (Rev.a) )Tùng DTNessuna valutazione finora

- ARM Processor ProgramsDocumento11 pagineARM Processor Programsmonsan_83100% (1)

- Eceg3202 - Computer Architecture and OrganizationDocumento41 pagineEceg3202 - Computer Architecture and OrganizationAnonymous AFFiZnNessuna valutazione finora

- PLC ProgrammingDocumento53 paginePLC ProgrammingSnehilNessuna valutazione finora

- Manual ModbusDocumento45 pagineManual ModbusMaximiliano SanchezNessuna valutazione finora

- PR Communication ManualDocumento35 paginePR Communication ManualAbdul Moeez AliNessuna valutazione finora

- RN2483 Low Power Long Range LoRa Technology Transceiver Module DS50002346FDocumento24 pagineRN2483 Low Power Long Range LoRa Technology Transceiver Module DS50002346FВіталій ПузакNessuna valutazione finora

- Ge8151 LsDocumento2 pagineGe8151 LsGanesh KumarNessuna valutazione finora

- Part A 2marks - EsDocumento27 paginePart A 2marks - EsKannan AlagumuthiahNessuna valutazione finora

- FDP Workshop Brochure CompressedDocumento2 pagineFDP Workshop Brochure CompressedKannan AlagumuthiahNessuna valutazione finora

- I Internal UpDocumento2 pagineI Internal UpKannan AlagumuthiahNessuna valutazione finora

- Verilog Lab SolutionsDocumento15 pagineVerilog Lab Solutionsraja_ramalingam07Nessuna valutazione finora

- Ii Internal CTDocumento3 pagineIi Internal CTKannan AlagumuthiahNessuna valutazione finora

- Up & Uc - LessonPlanDocumento2 pagineUp & Uc - LessonPlanKannan AlagumuthiahNessuna valutazione finora

- Code Converters ExperimentDocumento12 pagineCode Converters ExperimentKannan Alagumuthiah0% (1)

- DEC Assignment 3Documento10 pagineDEC Assignment 3Kannan AlagumuthiahNessuna valutazione finora

- Electronic Circuits I Lab RecordDocumento2 pagineElectronic Circuits I Lab RecordKannan AlagumuthiahNessuna valutazione finora

- The Examination Shall Consist of The Following Two PartsDocumento5 pagineThe Examination Shall Consist of The Following Two PartsKannan AlagumuthiahNessuna valutazione finora

- Arithmetic InstructionsDocumento2 pagineArithmetic InstructionsKannan AlagumuthiahNessuna valutazione finora

- Transistor TestingDocumento2 pagineTransistor TestingKannan AlagumuthiahNessuna valutazione finora

- Security of Internet of ThingsDocumento4 pagineSecurity of Internet of ThingsKannan AlagumuthiahNessuna valutazione finora

- About Amateur RadioDocumento43 pagineAbout Amateur RadioShantha Kumar100% (1)

- Digital ThermometerDocumento5 pagineDigital ThermometerKannan AlagumuthiahNessuna valutazione finora

- Block Diagram of Fiber Optic Communiction SystemDocumento5 pagineBlock Diagram of Fiber Optic Communiction SystemKannan Alagumuthiah50% (2)

- Datasheet - CI 7493 PDFDocumento10 pagineDatasheet - CI 7493 PDFFreddy KruguerNessuna valutazione finora

- Unit I To Uiibeddud System: ObjectiveDocumento24 pagineUnit I To Uiibeddud System: ObjectiveAadithya AadithyaaNessuna valutazione finora

- SolutionDocumento6 pagineSolutionKannan AlagumuthiahNessuna valutazione finora

- RegistersDocumento18 pagineRegistersKannan AlagumuthiahNessuna valutazione finora

- MRDocumento14 pagineMRKannan AlagumuthiahNessuna valutazione finora

- Transistor TypesDocumento6 pagineTransistor TypesKannan AlagumuthiahNessuna valutazione finora

- B.Tech CSEDocumento112 pagineB.Tech CSESou Su BeNessuna valutazione finora

- Rajalakshmi Engineering College, Thandalam Department of Ece Question BankDocumento6 pagineRajalakshmi Engineering College, Thandalam Department of Ece Question BankAnne MathewNessuna valutazione finora

- Diodes and TransistorsDocumento27 pagineDiodes and TransistorsKannan AlagumuthiahNessuna valutazione finora

- Active and Passive DevicesDocumento1 paginaActive and Passive DevicesKannan AlagumuthiahNessuna valutazione finora

- Zener Diode TestingDocumento1 paginaZener Diode TestingKannan AlagumuthiahNessuna valutazione finora

- Transistor TestingDocumento2 pagineTransistor TestingKannan AlagumuthiahNessuna valutazione finora

- Testing Silicon DiodeDocumento1 paginaTesting Silicon DiodeKannan AlagumuthiahNessuna valutazione finora

- S3 U4 MiniTestDocumento3 pagineS3 U4 MiniTestĐinh Thị Thu HàNessuna valutazione finora

- VERGARA - RPH Reflection PaperDocumento2 pagineVERGARA - RPH Reflection PaperNezer Byl P. VergaraNessuna valutazione finora

- PedagogicalDocumento94 paginePedagogicalEdson MorenoNessuna valutazione finora

- Unit 3: Theories and Principles in The Use and Design of Technology Driven Learning LessonsDocumento5 pagineUnit 3: Theories and Principles in The Use and Design of Technology Driven Learning Lessons서재배Nessuna valutazione finora

- EDAG0007Documento5 pagineEDAG0007krunalNessuna valutazione finora

- Cella Di Carico Sartorius MP77 eDocumento3 pagineCella Di Carico Sartorius MP77 eNCNessuna valutazione finora

- Macros and DirectiveDocumento7 pagineMacros and DirectiveAbdul MoeedNessuna valutazione finora

- Ferroelectric RamDocumento20 pagineFerroelectric RamRijy LoranceNessuna valutazione finora

- DC Generator - Construction, Working Principle, Types, and Applications PDFDocumento1 paginaDC Generator - Construction, Working Principle, Types, and Applications PDFGokul GokulNessuna valutazione finora

- Charles Zastrow, Karen K. Kirst-Ashman-Understanding Human Behavior and The Social Environment-Thomson Brooks - Cole (2007)Documento441 pagineCharles Zastrow, Karen K. Kirst-Ashman-Understanding Human Behavior and The Social Environment-Thomson Brooks - Cole (2007)joan82% (17)

- Bhavesh ProjectDocumento14 pagineBhavesh ProjectRahul LimbaniNessuna valutazione finora

- (Ebook - Antroposofia - EnG) - Rudolf Steiner - Fundamentals of TheraphyDocumento58 pagine(Ebook - Antroposofia - EnG) - Rudolf Steiner - Fundamentals of Theraphyblueyes247Nessuna valutazione finora

- Unit 1 Building A Professional Relationship Across CulturesDocumento16 pagineUnit 1 Building A Professional Relationship Across CulturesAlex0% (1)

- HPSC HCS Exam 2021: Important DatesDocumento6 pagineHPSC HCS Exam 2021: Important DatesTejaswi SaxenaNessuna valutazione finora

- Aex-Kissan KeralaDocumento25 pagineAex-Kissan Keralabsh08070Nessuna valutazione finora

- UserProvisioningLabKit 200330 093526Documento10 pagineUserProvisioningLabKit 200330 093526Vivian BiryomumaishoNessuna valutazione finora

- 12 Logarithm Approximate FloatingDocumento6 pagine12 Logarithm Approximate FloatingPhilippe Englert VelhaNessuna valutazione finora

- Jy992d66901 CDocumento6 pagineJy992d66901 CMaitry ShahNessuna valutazione finora

- Mossbauer SpectrosDocumento7 pagineMossbauer SpectroscyrimathewNessuna valutazione finora

- Details Philippine Qualifications FrameworkDocumento6 pagineDetails Philippine Qualifications FrameworkCeline Pascual-RamosNessuna valutazione finora

- UpdateJul2007 3julDocumento10 pagineUpdateJul2007 3julAnshul SinghNessuna valutazione finora

- 1 AlarmvalveDocumento9 pagine1 AlarmvalveAnandNessuna valutazione finora

- VTB Datasheet PDFDocumento24 pagineVTB Datasheet PDFNikola DulgiarovNessuna valutazione finora

- STW 44 3 2 Model Course Leadership and Teamwork SecretariatDocumento49 pagineSTW 44 3 2 Model Course Leadership and Teamwork Secretariatwaranchai83% (6)

- Penelitian Tindakan Kelas - Alberta Asti Intan Sherliana 20220049Documento25 paginePenelitian Tindakan Kelas - Alberta Asti Intan Sherliana 20220049Asti SherlyanaNessuna valutazione finora

- Performance Task 2Documento3 paginePerformance Task 2Edrose WycocoNessuna valutazione finora

- Group Members: - Muhamad Sahli B Muda - Nurul Hana Balqis Baharom - Napsiah Abdul RahmanDocumento18 pagineGroup Members: - Muhamad Sahli B Muda - Nurul Hana Balqis Baharom - Napsiah Abdul RahmanNurul Hana BalqisNessuna valutazione finora

- The Limits of The Sectarian Narrative in YemenDocumento19 pagineThe Limits of The Sectarian Narrative in Yemenهادي قبيسيNessuna valutazione finora

- Book Chapter 11 SubmissionDocumento18 pagineBook Chapter 11 Submissioncristine_2006_g5590Nessuna valutazione finora

- Teaching PowerPoint Slides - Chapter 5Documento19 pagineTeaching PowerPoint Slides - Chapter 5Azril ShazwanNessuna valutazione finora