Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

N-Channel Powertrench Mosfet 150V, 21A, 66M: September 2002

Caricato da

curzTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

N-Channel Powertrench Mosfet 150V, 21A, 66M: September 2002

Caricato da

curzCopyright:

Formati disponibili

FDD2582

September 2002

FDD2582

N-Channel PowerTrench® MOSFET

150V, 21A, 66mΩ

Features Applications

• r DS(ON) = 58mΩ (Typ.), VGS = 10V, ID = 7A • DC/DC converters and Off-Line UPS

• Qg(tot) = 19nC (Typ.), VGS = 10V • Distributed Power Architectures and VRMs

• Low Miller Charge

• Primary Switch for 24V and 48V Systems

• Low QRR Body Diode

• High Voltage Synchronous Rectifier

• UIS Capability (Single Pulse and Repetitive Pulse)

• Qualified to AEC Q101 • Direct Injection / Diesel Injection System

Formerly developmental type 82855 • 42V Automotive Load Control

• Electronic Valve Train System

DRAIN

(FLANGE) D

GATE

G

SOURCE

TO-252AA

S

FDD SERIES

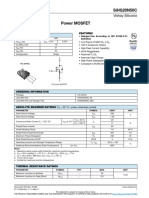

MOSFET Maximum Ratings TC = 25°C unless otherwise noted

Symbol Parameter Ratings Units

VDSS Drain to Source Voltage 150 V

VGS Gate to Source Voltage ±20 V

Drain Current

Continuous (TC = 25 oC, VGS = 10V) 21 A

ID

Continuous (TC = 100 oC, VGS = 10V) 15

Continuous (Tamb = 25oC, VGS = 10V, R θJA = 52oC/W) 3.7 A

Pulsed Figure 4 A

E AS Single Pulse Avalanche Energy (Note 1) 59 mJ

Power dissipation 95 W

PD

Derate above 25oC 0.63 W/oC

oC

TJ, TSTG Operating and Storage Temperature -55 to 175

Thermal Characteristics

o

RθJC Thermal Resistance Junction to Case TO-252 1.58 C/W

o

RθJA Thermal Resistance Junction to Ambient TO-252 100 C/W

2 o

RθJA Thermal Resistance Junction to Ambient TO-252, 1in copper pad area 52 C/W

This product has been designed to meet the extreme test conditions and environment demanded by the automotive industry. For a

copy of the requirements, see AEC Q101 at: http://www.aecouncil.com/

Reliability data can be found at: http://www.fairchildsemi.com/products/discrete/reliability/index.html.

All Fairchild Semiconductor products are manufactured, assembled and tested under ISO9000 and QS9000 quality systems

certification.

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

FDD2582 FDD2582 TO-252AA 330mm 16mm 2500 units

Electrical Characteristics TC = 25°C unless otherwise noted

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BVDSS Drain to Source Breakdown Voltage ID = 250µA, VGS = 0V 150 - - V

VDS = 120V - - 1

IDSS Zero Gate Voltage Drain Current µA

VGS = 0V TC = 150oC - - 250

IGSS Gate to Source Leakage Current VGS = ±20V - - ±100 nA

On Characteristics

VGS(TH) Gate to Source Threshold Voltage V GS = VDS, ID = 250µA 2 - 4 V

ID = 7A, VGS = 10V - 0.058 0.066

ID = 4A, VGS = 6V, - 0.066 0.099

rDS(ON) Drain to Source On Resistance Ω

ID = 7A, VGS = 10V,

- 0.151 0.172

TC = 175oC

Dynamic Characteristics

CISS Input Capacitance - 1295 - pF

VDS = 25V, VGS = 0V,

COSS Output Capacitance - 145 - pF

f = 1MHz

CRSS Reverse Transfer Capacitance - 30 - pF

Qg(TOT) Total Gate Charge at 10V VGS = 0V to 10V - 19 25 nC

Qg(TH) Threshold Gate Charge VGS = 0V to 2V VDD = 75V - 2.4 3.2 nC

Qgs Gate to Source Gate Charge ID = 7A - 6.2 - nC

Qgs2 Gate Charge Threshold to Plateau Ig = 1.0mA - 3.8 - nC

Qgd Gate to Drain “Miller” Charge - 4.2 - nC

Resistive Switching Characteristics (VGS = 10V)

tON Turn-On Time - - 41 ns

td(ON) Turn-On Delay Time - 8 - ns

tr Rise Time VDD = 75V, ID = 7A - 19 - ns

td(OFF) Turn-Off Delay Time VGS = 10V, RGS = 16Ω - 32 - ns

tf Fall Time - 19 - ns

tOFF Turn-Off Time - - 77 ns

Drain-Source Diode Characteristics

ISD = 7A - - 1.25 V

VSD Source to Drain Diode Voltage

ISD = 4A - - 1.0 V

trr Reverse Recovery Time ISD = 7A, dISD/dt = 100A/µs - - 67 ns

QRR Reverse Recovered Charge ISD = 7A, dISD/dt = 100A/µs - - 134 nC

Notes:

1: Starting TJ = 25°C, L = 1.17 mH, IAS = 10A.

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

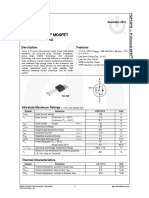

Typical Characteristics TC = 25°C unless otherwise noted

1.2 25

VGS = 10V

1.0

POWER DISSIPATION MULTIPLIER

20

ID, DRAIN CURRENT (A)

0.8

15

0.6

10

0.4

0.2 5

0 0

0 25 50 75 100 125 150 175

25 50 75 100 125 150 175

TC , CASE TEMPERATURE (oC) TC, CASE TEMPERATURE (oC)

Figure 1. Normalized Power Dissipation vs Figure 2. Maximum Continuous Drain Current vs

Ambient Temperature Case Temperature

2

DUTY CYCLE - DESCENDING ORDER

1 0.5

0.2

0.1

THERMAL IMPEDANCE

0.05

ZθJC, NORMALIZED

0.02

0.01

PDM

0.1

t1

t2

NOTES:

SINGLE PULSE DUTY FACTOR: D = t1/t2

PEAK TJ = PDM x ZθJC x R θJC + TC

0.01

10-5 10-4 10-3 10-2 10-1 100 101

t, RECTANGULAR PULSE DURATION (s)

Figure 3. Normalized Maximum Transient Thermal Impedance

300

TC = 25oC

TRANSCONDUCTANCE

MAY LIMIT CURRENT FOR TEMPERATURES

IN THIS REGION ABOVE 25oC DERATE PEAK

IDM, PEAK CURRENT (A)

CURRENT AS FOLLOWS:

I = I25 175 - TC

100

150

VGS = 10V

20

10 -5 10-4 10-3 10-2 10-1 100 101

t , PULSE WIDTH (s)

Figure 4. Peak Current Capability

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

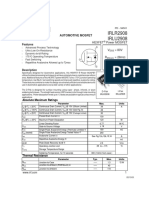

Typical Characteristics TC = 25°C unless otherwise noted

200 100

10µs If R = 0

100 tAV = (L)(IAS)/(1.3*RATED BVDSS - VDD)

If R ≠ 0

IAS, AVALANCHE CURRENT (A)

100µs tAV = (L/R)ln[(IAS*R)/(1.3*RATED BVDSS - VDD) +1]

ID, DRAIN CURRENT (A)

10 1ms

10 STARTING TJ = 25 oC

OPERATION IN THIS 10ms

AREA MAY BE

LIMITED BY rDS(ON)

1

SINGLE PULSE DC

TJ = MAX RATED STARTING TJ = 150oC

TC = 25oC

0.1 1

1 10 100 300 0.001 0.01 0.1 1 10

VDS, DRAIN TO SOURCE VOLTAGE (V) tAV, TIME IN AVALANCHE (ms)

Figure 5. Forward Bias Safe Operating Area NOTE: Refer to Fairchild Application Notes AN7514 and AN7515

Figure 6. Unclamped Inductive Switching

Capability

50 50

PULSE DURATION = 80µs VGS = 10V

DUTY CYCLE = 0.5% MAX

40 VDD = 15V 40 PULSE DURATION = 80µs VGS = 7V

ID , DRAIN CURRENT (A)

ID, DRAIN CURRENT (A)

DUTY CYCLE = 0.5% MAX

TC = 25 oC

30 30

TJ = 175oC VGS = 6V

20 20

TJ = 25oC TJ = -55oC

VGS = 5V

10 10

0 0

3.5 4.0 4.5 5.0 5.5 6.0 6.5 7.0 0 1 2 3 4 5

VGS , GATE TO SOURCE VOLTAGE (V) VDS , DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Transfer Characteristics Figure 8. Saturation Characteristics

90 3.0

DRAIN TO SOURCE ON RESISTANCE (m Ω)

PULSE DURATION = 80µs

PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX

NORMALIZED DRAIN TO SOURCE

DUTY CYCLE = 0.5% MAX

2.5

80

ON RESISTANCE

VGS = 6V

2.0

70

1.5

60 VGS = 10V

1.0

VGS = 10V, ID = 21A

50 0.5

0 5 10 15 20 25 -80 -40 0 40 80 120 160 200

ID, DRAIN CURRENT (A) TJ, JUNCTION TEMPERATURE (oC)

Figure 9. Drain to Source On Resistance vs Drain Figure 10. Normalized Drain to Source On

Current Resistance vs Junction Temperature

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

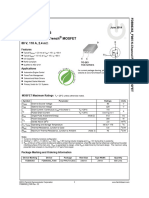

Typical Characteristics TC = 25°C unless otherwise noted

1.2 1.2

VGS = VDS, ID = 250µA ID = 250µA

NORMALIZED DRAIN TO SOURCE

BREAKDOWN VOLTAGE

THRESHOLD VOLTAGE

1.0

NORMALIZED GATE

1.1

0.8

1.0

0.6

0.4 0.9

-80 -40 0 40 80 120 160 200 -80 -40 0 40 80 120 160 200

TJ, JUNCTION TEMPERATURE (oC) TJ , JUNCTION TEMPERATURE (oC)

Figure 11. Normalized Gate Threshold Voltage vs Figure 12. Normalized Drain to Source

Junction Temperature Breakdown Voltage vs Junction Temperature

2000 10

VDD = 75V

VGS , GATE TO SOURCE VOLTAGE (V)

1000

CISS = CGS + CGD 8

C, CAPACITANCE (pF)

COSS ≅ CDS + CGD

CRSS = CGD

100

4

WAVEFORMS IN

2 DESCENDING ORDER:

ID = 21A

VGS = 0V, f = 1MHz ID = 7A

10 0

0.1 1 10 150 0 5 10 15 20

VDS , DRAIN TO SOURCE VOLTAGE (V) Qg, GATE CHARGE (nC)

Figure 13. Capacitance vs Drain to Source Figure 14. Gate Charge Waveforms for Constant

Voltage Gate Currents

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

Test Circuits and Waveforms

VDS BVDSS

tP

VDS

L

IAS

VARY tP TO OBTAIN VDD

+

REQUIRED PEAK IAS RG

VDD

VGS -

DUT

tP

0V IAS 0

0.01Ω

tAV

Figure 15. Unclamped Energy Test Circuit Figure 16. Unclamped Energy Waveforms

VDS

VDD Qg(TOT)

VDS

L

VGS = 10V

VGS

+

VDD VGS

-

DUT VGS = 2V

0 Qgs2

Ig(REF)

Qg(TH)

Qgs Qgd

Ig(REF)

0

Figure 17. Gate Charge Test Circuit Figure 18. Gate Charge Waveforms

VDS tON tOFF

td(ON) td(OFF)

RL tr tf

VDS

90% 90%

+

VGS

VDD

10% 10%

- 0

DUT 90%

RGS

VGS 50% 50%

PULSE WIDTH

VGS 10%

0

Figure 19. Switching Time Test Circuit Figure 20. Switching Time Waveforms

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

Thermal Resistance vs. Mounting Pad Area

The maximum rated junction temperature, TJM , and the 125

thermal resistance of the heat dissipating path determines RθJA = 33.32+ 23.84/(0.268+Area) EQ.2

the maximum allowable device power dissipation, PDM , in an

application. Therefore the application’s ambient RθJA = 33.32+ 154/(1.73+Area) EQ.3

100

temperature, TA (oC), and thermal resistance RθJA (oC/W)

must be reviewed to ensure that TJM is never exceeded.

RθJA (oC/W)

Equation 1 mathematically represents the relationship and

75

serves as the basis for establishing the rating of the part.

(T –T )

JM A (EQ. 1)

P D M = ----------------------------- 50

R θ JA

In using surface mount devices such as the TO-252 25

package, the environment in which it is applied will have a 0.01 0.1 1 10

significant influence on the part’s current and maximum (0.0645) (0.645) (6.45) (64.5)

power dissipation ratings. Precise determination of P DM is

complex and influenced by many factors: AREA, TOP COPPER AREA in2 (cm 2)

Figure 21. Thermal Resistance vs Mounting

1. Mounting pad area onto which the device is attached and Pad Area

whether there is copper on one side or both sides of the

board.

2. The number of copper layers and the thickness of the

board.

3. The use of external heat sinks.

4. The use of thermal vias.

5. Air flow and board orientation.

6. For non steady state applications, the pulse width, the

duty cycle and the transient thermal response of the part,

the board and the environment they are in.

Fairchild provides thermal information to assist the

designer’s preliminary application evaluation. Figure 21

defines the RθJA for the device as a function of the top

copper (component side) area. This is for a horizontally

positioned FR-4 board with 1oz copper after 1000 seconds

of steady state power with no air flow. This graph provides

the necessary information for calculation of the steady state

junction temperature or power dissipation. Pulse

applications can be evaluated using the Fairchild device

Spice thermal model or manually utilizing the normalized

maximum transient thermal impedance curve.

Thermal resistances corresponding to other copper areas

can be obtained from Figure 21 or by calculation using

Equation 2 or 3. Equation 2 is used for copper area defined

in inches square and equation 3 is for area in centimeters

square. The area, in square inches or square centimeters is

the top copper area including the gate and source pads.

23.84

R = 33.32 + ------------------------------------- (EQ. 2)

θ JA ( 0.268 + Area )

Area in Inches Squared

154

R = 33.32 + ---------------------------------- (EQ. 3)

θ JA ( 1.73 + Area )

Area in Centimeters Squared

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

PSPICE Electrical Model

.SUBCKT FDD2582 2 1 3 ; rev July 2002

Ca 12 8 4e-10

Cb 15 14 4.6e-10 LDRAIN

Cin 6 8 1.24e-9 DPLCAP 5 DRAIN

2

10

Dbody 7 5 DbodyMOD RLDRAIN

Dbreak 5 11 DbreakMOD RSLC1

51 DBREAK

Dplcap 10 5 DplcapMOD +

RSLC2

5

ESLC 11

Ebreak 11 7 17 18 160.4 51

-

Eds 14 8 5 8 1 50 +

Egs 13 8 6 8 1 -

RDRAIN 17 DBODY

6

Esg 6 10 6 8 1 ESG 8

EBREAK 18

Evthres 6 21 19 8 1 EVTHRES -

+ 16

Evtemp 20 6 18 22 1 + 19 - 21

LGATE EVTEMP MWEAK

8

GATE RGATE + 6

It 8 17 1 18 -

1 22 MMED

9 20

RLGATE MSTRO

Lgate 1 9 4.88e-9

LSOURCE

Ldrain 2 5 1.0e-9 CIN

8 SOURCE

7 3

Lsource 3 7 2.24e-9

RSOURCE

RLSOURCE

RLgate 1 9 48.8

S1A S2A

RLdrain 2 5 10 12 RBREAK

13 14 15

RLsource 3 7 22.4 8 13

17 18

S1B S2B RVTEMP

Mmed 16 6 8 8 MmedMOD

13 CB 19

Mstro 16 6 8 8 MstroMOD CA IT

+ + 14 -

Mweak 16 21 8 8 MweakMOD

6 5 VBAT

EGS EDS +

8 8

Rbreak 17 18 RbreakMOD 1 - - 8

Rdrain 50 16 RdrainMOD 37e-3 22

Rgate 9 20 1.8 RVTHRES

RSLC1 5 51 RSLCMOD 1.0e-6

RSLC2 5 50 1.0e3

Rsource 8 7 RsourceMOD 11.9e-3

Rvthres 22 8 RvthresMOD 1

Rvtemp 18 19 RvtempMOD 1

S1a 6 12 13 8 S1AMOD

S1b 13 12 13 8 S1BMOD

S2a 6 15 14 13 S2AMOD

S2b 13 15 14 13 S2BMOD

Vbat 22 19 DC 1

ESLC 51 50 VALUE={(V(5,51)/ABS(V(5,51)))*(PWR(V(5,51)/(1e-6*42),2.5))}

.MODEL DbodyMOD D (IS=2.3E-12 RS=5.3e-3 TRS1=2.2e-3 TRS2=4.5e-7

+ CJO=8.8e-10 M=0.64 TT=3.8e-8 XTI=4.2)

.MODEL DbreakMOD D (RS=0.4 TRS1=1.4e-3 TRS2=-5e-5)

.MODEL DplcapMOD D (CJO=2.75e-10 IS=1.0e-30 N=10 M=0.67)

.MODEL MmedMOD NMOS (VTO=3.76 KP=2.7 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=1.64)

.MODEL MstroMOD NMOS (VTO=4.25 KP=30 IS=1e-30 N=10 TOX=1 L=1u W=1u)

.MODEL MweakMOD NMOS (VTO=3.2 KP=0.068 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=16.4 RS=0.1)

.MODEL RbreakMOD RES (TC1=1.1e-3 TC2=-1.1e-8)

.MODEL RdrainMOD RES (TC1=1.0e-2 TC2=2.6e-5)

.MODEL RSLCMOD RES (TC1=2.7e-3 TC2=2.0e-6)

.MODEL RsourceMOD RES (TC1=1.0e-3 TC2=1.0e-6)

.MODEL RvthresMOD RES (TC1=-3.9e-3 TC2=-1.7e-5)

.MODEL RvtempMOD RES (TC1=-3.7e-3 TC2=1.9e-6)

.MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-5.0 VOFF=-2.0)

.MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-2.0 VOFF=-5.0)

.MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-0.4 VOFF=0.3)

.MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=0.3 VOFF=-0.4)

.ENDS

Note: For further discussion of the PSPICE model, consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global

Temperature Options; IEEE Power Electronics Specialist Conference Records, 1991, written by William J. Hepp and C. Frank

Wheatley.

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

SABER Electrical Model

REV July 2002

ttemplate FDD2582 n2,n1,n3

electrical n2,n1,n3

{

var i iscl

dp..model dbodymod = (isl=2.3e-12,rs=5.3e-3,trs1=2.2e-3,trs2=4.5e-7,cjo=8.8e-10,m=0.64,tt=3.8e-8,xti=4.2)

dp..model dbreakmod = (rs=0.4,trs1=1.4e-3,trs2=-5.0e-5)

dp..model dplcapmod = (cjo=2.75e-10,isl=10.0e-30,nl=10,m=0.67)

m..model mmedmod = (type=_n,vto=3.76,kp=2.7,is=1e-30, tox=1)

m..model mstrongmod = (type=_n,vto=4.25,kp=30,is=1e-30, tox=1)

m..model mweakmod = (type=_n,vto=3.2,kp=0.068,is=1e-30, tox=1,rs=0.1)

sw_vcsp..model s1amod = (ron=1e-5,roff=0.1,von=-5.0,voff=-2.0)

LDRAIN

sw_vcsp..model s1bmod = (ron=1e-5,roff=0.1,von=-2.0,voff=-5.0) DPLCAP 5 DRAIN

sw_vcsp..model s2amod = (ron=1e-5,roff=0.1,von=-0.4,voff=0.3) 2

sw_vcsp..model s2bmod = (ron=1e-5,roff=0.1,von=0.3,voff=-0.4) 10

RLDRAIN

c.ca n12 n8 = 4e-10 RSLC1

c.cb n15 n14 = 4.6e-10 51

c.cin n6 n8 = 1.24e-9 RSLC2

ISCL

dp.dbody n7 n5 = model=dbodymod 50 DBREAK

dp.dbreak n5 n11 = model=dbreakmod -

dp.dplcap n10 n5 = model=dplcapmod 6 RDRAIN

ESG 8 11

EVTHRES DBODY

+ 16

spe.ebreak n11 n7 n17 n18 = 160.4 + 19 - 21

LGATE EVTEMP MWEAK

spe.eds n14 n8 n5 n8 = 1 8

GATE RGATE + 6

spe.egs n13 n8 n6 n8 = 1 18 - EBREAK

1 22 MMED

9 +

spe.esg n6 n10 n6 n8 = 1 20

MSTRO

RLGATE 17

spe.evthres n6 n21 n19 n8 = 1 18 LSOURCE

spe.evtemp n20 n6 n18 n22 = 1 CIN - SOURCE

8 7 3

i.it n8 n17 = 1 RSOURCE

RLSOURCE

l.lgate n1 n9 = 4.88e-9 S1A S2A

12 RBREAK

l.ldrain n2 n5 = 1.0e-9 13 14 15

17 18

8 13

l.lsource n3 n7 = 2.24e-9

S1B S2B RVTEMP

res.rlgate n1 n9 = 48.8 13 CB 19

CA IT

res.rldrain n2 n5 = 10 + + 14 -

res.rlsource n3 n7 = 22.4 6 5 VBAT

EGS EDS +

8 8

- - 8

m.mmed n16 n6 n8 n8 = model=mmedmod, l=1u, w=1u 22

m.mstrong n16 n6 n8 n8 = model=mstrongmod, l=1u, w=1u RVTHRES

m.mweak n16 n21 n8 n8 = model=mweakmod, l=1u, w=1u

res.rbreak n17 n18 = 1, tc1=1.1e-3,tc2=-1.1e-8

res.rdrain n50 n16 = 37e-3, tc1=1.0e-2,tc2=2.6e-5

res.rgate n9 n20 = 1.8

res.rslc1 n5 n51 = 1.0e-6, tc1=2.7e-3,tc2=2.0e-6

res.rslc2 n5 n50 = 1.0e3

res.rsource n8 n7 = 11.9e-3, tc1=1.0e-3,tc2=1.0e-6

res.rvthres n22 n8 = 1, tc1=-3.9e-3,tc2=-1.7e-5

res.rvtemp n18 n19 = 1, tc1=-3.7e-3,tc2=1.9e-6

sw_vcsp.s1a n6 n12 n13 n8 = model=s1amod

sw_vcsp.s1b n13 n12 n13 n8 = model=s1bmod

sw_vcsp.s2a n6 n15 n14 n13 = model=s2amod

sw_vcsp.s2b n13 n15 n14 n13 = model=s2bmod

v.vbat n22 n19 = dc=1

equations {

i (n51->n50) +=iscl

iscl: v(n51,n50) = ((v(n5,n51)/(1e-9+abs(v(n5,n51))))*((abs(v(n5,n51)*1e6/42))** 2.5))

}

}

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

FDD2582

SPICE Thermal Model JUNCTION

th

REV 19 July 2002

FDD2582

CTHERM1 TH 6 1.6e-3

CTHERM2 6 5 4.5e-3

CTHERM3 5 4 5.0e-3 RTHERM1 CTHERM1

CTHERM4 4 3 8.0e-3

CTHERM5 3 2 8.2e-3

CTHERM6 2 TL 4.7e-2

6

RTHERM1 TH 6 3.3e-2

RTHERM2 6 5 7.9e-2

RTHERM3 5 4 9.5e-2

RTHERM2 CTHERM2

RTHERM4 4 3 1.4e-1

RTHERM5 3 2 2.9e-1

RTHERM6 2 TL 6.7e-1

5

SABER Thermal Model

SABER thermal model FDD2582

template thermal_model th tl RTHERM3 CTHERM3

thermal_c th, tl

{

ctherm.ctherm1 th 6 =1.6e-3

4

ctherm.ctherm2 6 5 =4.5e-3

ctherm.ctherm3 5 4 =5.0e-3

ctherm.ctherm4 4 3 =8.0e-3

ctherm.ctherm5 3 2 =8.2e-3 RTHERM4 CTHERM4

ctherm.ctherm6 2 tl =4.7e-2

rrtherm.rtherm1 th 6 =3.3e-2

rtherm.rtherm2 6 5 =7.9e-2 3

rtherm.rtherm3 5 4 =9.5e-2

rtherm.rtherm4 4 3 =1.4e-1

rtherm.rtherm5 3 2 =2.9e-1

RTHERM5 CTHERM5

rtherm.rtherm6 2 tl =6.7e-1

}

RTHERM6 CTHERM6

tl CASE

©2002 Fairchild Semiconductor Corporation FDD2582 Rev. B

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx FACT ImpliedDisconnect PACMAN SPM

ActiveArray FACT Quiet Series ISOPLANAR POP Stealth

Bottomless FASTâ LittleFET Power247 SuperSOT-3

CoolFET FASTr MicroFET PowerTrenchâ SuperSOT-6

CROSSVOLT FRFET MicroPak QFET SuperSOT-8

DOME GlobalOptoisolator MICROWIRE QS SyncFET

EcoSPARK GTO MSX QT Optoelectronics TinyLogic

E2CMOSTM HiSeC MSXPro Quiet Series TruTranslation

EnSignaTM I2C OCX RapidConfigure UHC

Across the board. Around the world. OCXPro RapidConnect UltraFETâ

The Power Franchise OPTOLOGICâ SILENT SWITCHERâ VCX

Programmable Active Droop OPTOPLANAR SMART START

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER

NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD

DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT

OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT

RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant into support device or system whose failure to perform can

the body, or (b) support or sustain life, or (c) whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can be effectiveness.

reasonably expected to result in significant injury to the

user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or This datasheet contains the design specifications for

In Design product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

Rev. I1

Potrebbero piacerti anche

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Fdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MDocumento11 pagineFdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MSukandar TeaNessuna valutazione finora

- Fdd9407L - F085: N-Channel Logic Level Powertrench MosfetDocumento7 pagineFdd9407L - F085: N-Channel Logic Level Powertrench Mosfetonis1 onis1Nessuna valutazione finora

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MDocumento11 pagineFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7Mfuad64Nessuna valutazione finora

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDa EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsValutazione: 3.5 su 5 stelle3.5/5 (6)

- Fdp3652 / Fdb3652: N-Channel Powertrench MosfetDocumento14 pagineFdp3652 / Fdb3652: N-Channel Powertrench Mosfethalil ibrahim soysalNessuna valutazione finora

- 72T02GH AdvancedPowerElectronicsDocumento6 pagine72T02GH AdvancedPowerElectronicsjose jesus arteaga gomezNessuna valutazione finora

- Is Now Part ofDocumento15 pagineIs Now Part ofSaikumarNessuna valutazione finora

- 161 5 003187 FDD6685Documento6 pagine161 5 003187 FDD6685Marcos Paulo FariaNessuna valutazione finora

- Advanced Power Electronics Corp.: AP72T02GH/JDocumento6 pagineAdvanced Power Electronics Corp.: AP72T02GH/JFrancisco MataNessuna valutazione finora

- 100N10 EtcDocumento5 pagine100N10 EtcJm TechNessuna valutazione finora

- FDD8880Documento11 pagineFDD8880DannyNessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento13 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataEdson CostaNessuna valutazione finora

- FDP 5800Documento8 pagineFDP 5800Khalid JakirNessuna valutazione finora

- FDPA Programing1231Documento10 pagineFDPA Programing1231Engr. Syed Ghulam Mustafa ShahNessuna valutazione finora

- 20N50EDocumento8 pagine20N50EFernando SimãoNessuna valutazione finora

- APM2558NU: Pin Description FeaturesDocumento10 pagineAPM2558NU: Pin Description FeaturesLuciano LucasNessuna valutazione finora

- FDH44N50Documento6 pagineFDH44N50loc nguyen dacNessuna valutazione finora

- IRLR2905Z IRLU2905Z: Automotive MosfetDocumento11 pagineIRLR2905Z IRLU2905Z: Automotive MosfetnaughtybigboyNessuna valutazione finora

- 75V, 80A Heatsink Planar N-Channel Power Mosfets: PB Free Plating ProductDocumento5 pagine75V, 80A Heatsink Planar N-Channel Power Mosfets: PB Free Plating ProductARESJAVIERNessuna valutazione finora

- DatasheetDocumento8 pagineDatasheetRegisk8 OliveiraNessuna valutazione finora

- Datasheet 520Documento11 pagineDatasheet 520IvanNessuna valutazione finora

- Irlz44Z Irlz44Zs Irlz44Zl: Automotive MosfetDocumento13 pagineIrlz44Z Irlz44Zs Irlz44Zl: Automotive MosfetrickiaqpNessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento6 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DatavetchboyNessuna valutazione finora

- P06VDocumento7 pagineP06VMauro BusciglioNessuna valutazione finora

- Data Sheet Mosfet Taladro de ManoDocumento5 pagineData Sheet Mosfet Taladro de ManosmoscatelloNessuna valutazione finora

- Irf530 DDocumento8 pagineIrf530 DnooneezNessuna valutazione finora

- N-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDDocumento9 pagineN-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDAnonymous p1ig0zX6p0Nessuna valutazione finora

- STP40NF10 STB40NF10 - STB40NF10-1Documento12 pagineSTP40NF10 STB40NF10 - STB40NF10-1Anca SterianNessuna valutazione finora

- Stp80Nf55-06 - Stp80Nf55-06Fp Stb80Nf55-06-1: N-Channel 55V - 0.005 - 80A To-220/To-220Fp/I Pak Stripfet Power MosfetDocumento10 pagineStp80Nf55-06 - Stp80Nf55-06Fp Stb80Nf55-06-1: N-Channel 55V - 0.005 - 80A To-220/To-220Fp/I Pak Stripfet Power MosfetCelso SáNessuna valutazione finora

- Huf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetDocumento7 pagineHuf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetJose cuelloNessuna valutazione finora

- Irf 634 BDocumento8 pagineIrf 634 BAhmed ShagidullinNessuna valutazione finora

- SW2N60DC: N-Channel Enhanced Mode TO-252/TO-251 MOSFETDocumento6 pagineSW2N60DC: N-Channel Enhanced Mode TO-252/TO-251 MOSFETdanielNessuna valutazione finora

- FDP 150 N 10Documento8 pagineFDP 150 N 10Luka BaracNessuna valutazione finora

- SW3205 Samwin: FeaturesDocumento7 pagineSW3205 Samwin: FeaturesYousef KassimNessuna valutazione finora

- Data SheetDocumento8 pagineData SheetSuyash SuyashNessuna valutazione finora

- HY27UF084G2B HynixSemiconductorDocumento7 pagineHY27UF084G2B HynixSemiconductorDrew AlbaneseNessuna valutazione finora

- FQB55N10: N-Channel QFET MosfetDocumento8 pagineFQB55N10: N-Channel QFET MosfetcurzNessuna valutazione finora

- Sihg20N50C: Vishay SiliconixDocumento8 pagineSihg20N50C: Vishay Siliconixалексей ЛфNessuna valutazione finora

- FQP12P10: P-Channel QFET MosfetDocumento8 pagineFQP12P10: P-Channel QFET MosfetCrdz LouisNessuna valutazione finora

- Is Now Part ofDocumento14 pagineIs Now Part ofSaadNessuna valutazione finora

- AP9T15GHDocumento4 pagineAP9T15GHJose M PeresNessuna valutazione finora

- FETek-FKD3006 C2758594Documento4 pagineFETek-FKD3006 C2758594Fraf ZeppNessuna valutazione finora

- IRLR2908 IRLU2908: Automotive MosfetDocumento11 pagineIRLR2908 IRLU2908: Automotive MosfetAnhVũNessuna valutazione finora

- NGTB25N120FL2WAG IGBT - Field Stop II / 4 Lead: 25 A, 1200 V V 2.0 V E 0.99 MJDocumento12 pagineNGTB25N120FL2WAG IGBT - Field Stop II / 4 Lead: 25 A, 1200 V V 2.0 V E 0.99 MJJuan Carlos SrafanNessuna valutazione finora

- FDP8443Documento7 pagineFDP8443Semut criminalsNessuna valutazione finora

- D5T40PDocumento12 pagineD5T40Pmarco kantutaNessuna valutazione finora

- Datasheet PDFDocumento10 pagineDatasheet PDFShikamaru MendozaNessuna valutazione finora

- APM2518NU AnpecElectronicsCoroprationDocumento10 pagineAPM2518NU AnpecElectronicsCoroprationpapainoelmorreuNessuna valutazione finora

- MTP3055V Power MOSFET 12 Amps, 60 Volts: N Channel TO 220Documento7 pagineMTP3055V Power MOSFET 12 Amps, 60 Volts: N Channel TO 220Hectór DavidNessuna valutazione finora

- Fdd390N15Alz: N-Channel Powertrench MosfetDocumento9 pagineFdd390N15Alz: N-Channel Powertrench Mosfetserrano.flia.coNessuna valutazione finora

- Fdb20an06a0 1305401Documento14 pagineFdb20an06a0 1305401Moi CanoNessuna valutazione finora

- Fdb86363 - F085: N-Channel Powertrench MosfetDocumento6 pagineFdb86363 - F085: N-Channel Powertrench MosfetNobreak ServiceNessuna valutazione finora

- APM2556NU AnpecElectronicsCoroprationDocumento11 pagineAPM2556NU AnpecElectronicsCoroprationEvelin RibeiroNessuna valutazione finora

- N-Channel Power Trench Mosfet: Features General DescriptionDocumento8 pagineN-Channel Power Trench Mosfet: Features General DescriptionRicardo VieiraNessuna valutazione finora

- 15 N 03 HDocumento6 pagine15 N 03 HJose M PeresNessuna valutazione finora

- Data SheetDocumento6 pagineData SheetAlberto IsmaelNessuna valutazione finora

- Presto enDocumento100 paginePresto encurzNessuna valutazione finora

- Manual Do ProdutoDocumento26 pagineManual Do ProdutocurzNessuna valutazione finora

- (At Command) Usr Tcp232 E2 at Command Set - v1.0.0Documento22 pagine(At Command) Usr Tcp232 E2 at Command Set - v1.0.0curzNessuna valutazione finora

- Manual Do ProdutoDocumento26 pagineManual Do ProdutocurzNessuna valutazione finora

- Horizon Compact Plus Loss of Management After 208 Days - TN-000041-01-En-02Documento5 pagineHorizon Compact Plus Loss of Management After 208 Days - TN-000041-01-En-02curzNessuna valutazione finora

- Cambium PTP 650 Series User Guide: System Release 650-01-00Documento196 pagineCambium PTP 650 Series User Guide: System Release 650-01-00curzNessuna valutazione finora

- Resumen SW NewDocumento20 pagineResumen SW NewcurzNessuna valutazione finora

- Customer Release Notes 07 01 83 7 1 Phase I - RGMDocumento18 pagineCustomer Release Notes 07 01 83 7 1 Phase I - RGMcurzNessuna valutazione finora

- LTC 4252Documento37 pagineLTC 4252curzNessuna valutazione finora

- Manual Do ProdutoDocumento26 pagineManual Do ProdutocurzNessuna valutazione finora

- 50650.installation Guide 2061303Documento39 pagine50650.installation Guide 2061303curzNessuna valutazione finora

- TS922, TS922A: Rail-To-Rail, High Output Current Dual Operational AmplifierDocumento24 pagineTS922, TS922A: Rail-To-Rail, High Output Current Dual Operational AmplifiercurzNessuna valutazione finora

- Rtcclient Tool Quick Guide: Date Jan. 25, 2011Documento3 pagineRtcclient Tool Quick Guide: Date Jan. 25, 2011curzNessuna valutazione finora

- UPC2762TB: Bipolar Analog Integrated CircuitDocumento6 pagineUPC2762TB: Bipolar Analog Integrated CircuitcurzNessuna valutazione finora

- Important Notice: Kind RegardsDocumento15 pagineImportant Notice: Kind RegardscurzNessuna valutazione finora

- Sofix Power Cable AssembliesDocumento2 pagineSofix Power Cable AssembliescurzNessuna valutazione finora

- HA178L00 Series: 3-Terminal Fixed Voltage RegulatorsDocumento22 pagineHA178L00 Series: 3-Terminal Fixed Voltage RegulatorscurzNessuna valutazione finora

- Customer Release Notes 07 01 83 7 1 Phase I - RGMDocumento17 pagineCustomer Release Notes 07 01 83 7 1 Phase I - RGMcurzNessuna valutazione finora

- VI-200 / VI-J00 Family: Design Guide & Applications ManualDocumento97 pagineVI-200 / VI-J00 Family: Design Guide & Applications ManualcurzNessuna valutazione finora

- 2.5-6.0/5.0-12.0 GHZ Gaas Mmic Active Doubler: Features Chip Device Layout X1002-BdDocumento5 pagine2.5-6.0/5.0-12.0 GHZ Gaas Mmic Active Doubler: Features Chip Device Layout X1002-BdcurzNessuna valutazione finora

- Key Features: Bias: VD 5 V & 7 V, Idq 1.05 ADocumento18 pagineKey Features: Bias: VD 5 V & 7 V, Idq 1.05 AcurzNessuna valutazione finora

- Credenziali ARIADocumento1 paginaCredenziali ARIAcurzNessuna valutazione finora

- Europe Power Cord Specs PDFDocumento9 pagineEurope Power Cord Specs PDFcurzNessuna valutazione finora

- Value Added Course - 2020-21 BatchDocumento2 pagineValue Added Course - 2020-21 BatchSUPRIYA PRAJAPATINessuna valutazione finora

- E32-TTL-100 Datasheet EN v1.0Documento14 pagineE32-TTL-100 Datasheet EN v1.0TKNgảiNessuna valutazione finora

- WorldShop CatalougeDocumento200 pagineWorldShop Catalougee2ashNessuna valutazione finora

- Ic Emc Application Note L4949 v4Documento9 pagineIc Emc Application Note L4949 v4Avs ElectronNessuna valutazione finora

- Ipd1 MeDocumento52 pagineIpd1 MeKopi143Nessuna valutazione finora

- Brkucc 2735Documento106 pagineBrkucc 2735silvano_lilianNessuna valutazione finora

- Wispy Manager: A Software Design For Avoiding Interference in A Wi-Fi (802.11) Mesh NetworkDocumento13 pagineWispy Manager: A Software Design For Avoiding Interference in A Wi-Fi (802.11) Mesh NetworkumailraghuNessuna valutazione finora

- Power Electronics TutorialDocumento147 paginePower Electronics Tutorialdongyu.li1992Nessuna valutazione finora

- Higher - O-O-O-Emf - O-O-O - Past Paper Questions 2000 - 2010Documento10 pagineHigher - O-O-O-Emf - O-O-O - Past Paper Questions 2000 - 2010Murray PhysicsNessuna valutazione finora

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - NotesDocumento214 pagineEce-V-fundamentals of Cmos Vlsi (10ec56) - NotesNithindev Guttikonda0% (1)

- DC and Ac Analysis of Input Stage, Second Stage and Output StageDocumento21 pagineDC and Ac Analysis of Input Stage, Second Stage and Output StageNarayan Mishra MishraNessuna valutazione finora

- User Manual ACS80 GBDocumento23 pagineUser Manual ACS80 GBJosef VacikNessuna valutazione finora

- Lic Syllabus 4th SemDocumento4 pagineLic Syllabus 4th SemYo Yo AnandNessuna valutazione finora

- SAD Unit 4 Real Time Systems1Documento20 pagineSAD Unit 4 Real Time Systems1onesnoneNessuna valutazione finora

- Lab Exercise #1: Introduction To The Cypress Fm4 Board and Fm4 Starter KitDocumento12 pagineLab Exercise #1: Introduction To The Cypress Fm4 Board and Fm4 Starter KitAhmed HamoudaNessuna valutazione finora

- 820B enDocumento12 pagine820B enSaif Ali100% (1)

- TOE-7402-7404 LeafletDocumento1 paginaTOE-7402-7404 LeafletenergiculNessuna valutazione finora

- Power Factor Correction & PFC ConvertersDocumento19 paginePower Factor Correction & PFC ConvertersSandeep Guha Niyogi100% (1)

- DMX Operator Ii PDFDocumento48 pagineDMX Operator Ii PDFcoxc5511Nessuna valutazione finora

- Controls Shimadzu Lc10 20systemsDocumento78 pagineControls Shimadzu Lc10 20systemsMiroslava González MontielNessuna valutazione finora

- 2n6661 MosfetDocumento10 pagine2n6661 MosfetCarlos DuranNessuna valutazione finora

- Intro To Industrial Process Control SystemsDocumento24 pagineIntro To Industrial Process Control Systemsmuhammad izzulNessuna valutazione finora

- Personal Radios To Keep You in Touch With Your World!Documento2 paginePersonal Radios To Keep You in Touch With Your World!Topcom Toki-VokiNessuna valutazione finora

- Electronics - and - Telecommunications - Noise, F R CONNOR PDFDocumento143 pagineElectronics - and - Telecommunications - Noise, F R CONNOR PDFAjay VarmaNessuna valutazione finora

- 06 Analog Input Modules PDFDocumento38 pagine06 Analog Input Modules PDFKelly Perez LopezNessuna valutazione finora

- Pertemuan 13 - Design Filter IirDocumento20 paginePertemuan 13 - Design Filter IirIca Khoerunnisa Allysa BalqisNessuna valutazione finora

- SLD QMT 8djh R-R-T (15kv)Documento3 pagineSLD QMT 8djh R-R-T (15kv)Manuel MassidiNessuna valutazione finora

- 6.012 DP: CMOS Integrated Differential Amplifier: Tony Hyun KimDocumento9 pagine6.012 DP: CMOS Integrated Differential Amplifier: Tony Hyun Kimanil kumarNessuna valutazione finora

- 1-PGNiG Kickoff MOM Rev1.0Documento4 pagine1-PGNiG Kickoff MOM Rev1.0zeeshansuboorNessuna valutazione finora

- Phoenix Contact - Relay Module - Rif-0-Rpt-24dc - 1 - 2903361Documento5 paginePhoenix Contact - Relay Module - Rif-0-Rpt-24dc - 1 - 2903361alexender2kNessuna valutazione finora