Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

01177a PDF

Caricato da

VitaliyGTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

01177a PDF

Caricato da

VitaliyGCopyright:

Formati disponibili

AN1177

Op Amp Precision Design: DC Errors

Author: Kumen Blake DC SPECIFICATIONS

Microchip Technology Inc. There are a small number of DC specifications that

describe errors at the input of an op amp. This section

INTRODUCTION organizes these specifications into those related to the

input offset and the others related to input bias

Engineers that use op amps in their circuits; especially currents.

those new to analog or op amp circuit design. Also

intended for engineers that want to understand op amp Ideal Op Amp

DC specifications.

Figure 1 shows the ideal, DC model for op amps (the

Description external circuitry is not shown). All error sources are

ignored and the open-loop gain (AOL) is infinite. The

This application note covers the essential background output voltage is related to the input voltages as shown

information and design theory needed to design a in Equation 1.

precision DC circuit using op amps. Topics include:

• Op Amp DC Specifications VN

• Circuit Analysis

VOUT

• Circuit Optimization AOL

VI

• Advanced Topics

• References FIGURE 1: Ideal, DC Op Amp Model.

This application note is limited to voltage feedback

(traditional) op amps. Those interested in current feed- EQUATION 1:

back op amps will benefit from the information here; the

DC specifications and op amp DC model have many V OUT = A OL ( V N – V I )

similarities.

For those that are interested, a simple circuit for When negative feedback is applied, the ideal op amp’s

measuring input offset voltage has been included in infinite gain forces VN and VI to be exactly equal; this is

Appendix A: “Input Offset Measurement Circuit”. the virtual short that some authors talk about. [ 1, 2]

When positive feedback is applied (e.g., when used as

a comparator), VOUT swings as far negative or positive

as it can (to the rails), depending on the sign of the dif-

ference (VN – VI).

Op Amp Model with DC Errors

Figure 2 shows a physically based, DC model for op

amps. VPLUS and VMINUS are the external input volt-

ages, while VN and VI are the internal input voltages.

VOST represents the total input offset voltage error. The

non-inverting bias current (IBN) and inverting bias cur-

rent (IBI) represent the physical currents seen at each

of the two input pins. AOL is the finite DC open-loop

gain.

© 2008 Microchip Technology Inc. DS01177A-page 1

AN1177

It is important to understand the units for these

VDD specifications. An engineer not used to op amp data

sheets may be confused by the units shown. The

following list should clear up the confusion.

VOST

VN • VOS units are: mV or µV

VPLUS • AOL units do not usually report the relationship

VOUT

VMINUS AOL shown above:

VI

- µV/V for 1/AOL = ΔVOST/ΔVOUT

- dB for 20log(AOL)

IBN IBI • CMRR units are similar to the AOL units:

- µV/V for 1/CMRR = ΔVOST/ΔVCM

- dB for 20log(CMRR)

VSS

• PSRR units are similar to the AOL units:

FIGURE 2: Physically Biased, DC Op - µV/V for 1/PSRR = ΔVOST/Δ(VDD – VSS)

Amp Model. - dB for 20log(PSRR)

Input Offset Related Specifications ΔVOS/ΔTA units are: µV/°C or nV/°C

A positive VOST creates a positive shift in the output Note: Notice that the gains AOL, CMRR and

voltage (VOUT). The DC voltages are: PSRR, when reported in µV/V, are actually

their reciprocals. This form of the gains is

EQUATION 2: best for statistical analyses; the values

tend to have a Gaussian distribution.

V N = V PLUS + V OST

V I = V MINUS Sometimes PSRR is split in two pieces: PSRR+ that is

related to changes in VDD (ΔVDD) and PSRR– that is

V OUT = A OL ( V N – V I )

related to changes in VSS (ΔVSS).

= A OL ( ( V PLUS – V MINUS ) + V OST )

These quantities are lumped together in the following

equation, where the changes in bias voltages are from

The total input offset voltage (VOST) collects the those specified for VOS (all units are converted to either

following specifications into one, easy to use V or V/V):

parameter:

• Input Offset Voltage (VOS): EQUATION 3:

- Specified offset ΔV OUT ΔV CM ΔV

DD ΔV SS Δ V OS

- Describes VOST at a specific bias point V OST = V OS + -------------------- + ----------------- + ----------------- + --------------- + Δ T A ⋅ ----------------

A

OL

CMRR PSRR PSRR Δ TA

• DC Open-Loop Gain (AOL):

- AOL = ΔVOUT/ΔVOST Notice that all of the specifications will give a positive

• Common Mode Rejection Ratio (CMRR): change in VOST when the corresponding changes are

positive.

- CMRR = ΔVCM/ΔVOST

- VCM is the common mode input voltage

(average of VPLUS and VMINUS)

Input Current Related Specifications

• Power Supply Rejection Ratio (PSRR): The input bias currents (IBN and IBI) create voltage

- PSRR = Δ(VDD – VSS)/ΔVOST drops across external resistances, which cause VOUT

• Input Offset Drift with Temperature (ΔVOS/ΔTA): to shift. By convention, the currents going into the pins

VPLUS and VMINUS are positive.

- Describes how VOST changes with TA;

actually ΔVOST/ΔTA Traditionally, these physically based currents have

- TA is the ambient temperature been mathematically transformed into the equivalent

pair of currents IB (input bias current) and IOS (input off-

set current). These are the average of IBN and IBI, and

their difference, respectively:

EQUATION 4:

( I BN + I BI )

I B = --------------------------

2

I OS = I BN – I BI

DS01177A-page 2 © 2008 Microchip Technology Inc.

AN1177

This model makes sense for traditional op amps that CIRCUIT ANALYSIS

have IBN and IBI nearly equal. This means that, in this

case, IB is much larger than IOS. This happens because Using a few simple techniques, it is easy to analyze the

these currents are caused by similar physically DC error performance of op amp circuits. Several

phenomena (e.g., matched transistor pair with similar common circuits illustrate these techniques.

input bias currents). Figure 2 shows how these

specified currents are modeled in a circuit. Resistance Seen by the Non-inverting

Input

VDD

Figure 4 is a simple circuit with a source and several

impedances attached to the non-inverting input. The

VOST process of calculating the equivalent resistance seen

VN

VPLUS by the non-inverting input will be described using this

VOUT circuit as the starting point.

VMINUS AOL

VI

R1 L1

U1

IB + IOS/2 IB – IOS/2 VOUT

V1 C1 R2

VSS

FIGURE 3: Equivalent DC Model for FIGURE 4: Simple Circuit.

Traditional Op Amps. The first step is to replace all external components with

Some newer op amp architectures have IOS near to the their DC equivalent for a Thevenin analysis:

same magnitude as IB. This happens because the • Voltage sources become 0V (short circuit)

physical causes of IBN and IBI are not physically related • Current sources become 0A (open circuit)

(they are independent or uncorrelated). Most data

• Resistors are left as is

sheets still use IB and IOS as the specifications.

• Capacitors become ∞Ω (open circuit)

The input currents depend strongly on architecture,

• Inductors become 0Ω (short circuit)

type of input transistors, and temperature. As

discussed before, traditional parts have IB >> IOS. Figure 5 shows the resulting circuit when this is done to

Some of the newer architectures have IOS and IB of those components attached to the non-inverting input

about the same size. of the op amp in Figure 4. A test source (VX) has been

added to help in the Thevenin analysis.

Most op amps have ESD diodes at the inputs. PN

junction ESD diodes tend to have small reverse

leakage at room temperature. These leakage currents IX

R1

increase by a factor of 2 for each 10°C increase in

VX

temperature. Since the ESD diodes tend to match well,

the differences between leakage currents tend to be R2

small. These leakage currents are a part of the input

bias currents. When an input goes outside the supply

voltage(s) the ESD diodes are tied to, the forward FIGURE 5: Equivalent DC Circuit for

current can grow to be very large. Non-inverting Input.

CMOS inputs transistors have very small input bias The equivalent resistance seen by the non-inverting

currents. Most of these op amps use ESD diodes at the input, for this example, is:

input for protection; the reverse leakage currents of

these ESD diodes are the dominant input bias currents.

EQUATION 5:

Electrometer grade op amps minimize input currents.

They typically use FET transistors at the input that give V

R NEQ = -----X-

currents in the femto-ampere (1015A) range. IX

Bipolar inputs have larger input bias currents. They are = R 1 || R 2

the input differential pair’s base currents, which do not

change much with supply voltage. They will change

This resistance is used in the error calculations for the

significantly with temperature (e.g., a 4 × range

non-inverting bias current (IBN) source. Figure 6 shows

between -40°C and +125°C). These op amps usually

how this is accomplished; the error at the op amp input

use ESD diodes, which increase the bias currents;

is calculated at this point of the process.

especially at high temperatures.

© 2008 Microchip Technology Inc. DS01177A-page 3

AN1177

IBN U1 IX

VX

VIBN VOUT

RNEQ R3

R2

VIBN = -IBN RNEQ

FIGURE 6: Application to Non-inverting FIGURE 9: Equivalent DC Circuit for the

Bias Current Error Calculations. Inverting Input.

The error voltage (VIBN) shown in Figure 6 can be The equivalent resistance seen by the inverting input,

placed in an equivalent circuit diagram that does not for this example, is:

explicitly show the current IBN. This will make the

analysis easier, and more consistent, in later steps.

EQUATION 6:

This new equivalent circuit is shown in Figure 7 (IBN is

already included in VIBN). The VIBN source, when it is V

R IEQ = -----X-

positive, will produce a positive change in VOUT. IX

= R 2 || R 3

0 U1

This resistance is used in the error calculations for the

VOUT inverting bias current (IBI) source. Figure 10 shows

R1 L1 VIBN

how this is done for the error at the op amp output,

referred to the input.

V1 C1 R2

U1

VIBN = -IBN RNEQ

VOUT

FIGURE 7: Application to Non-inverting

Bias Current Error Calculations.

IBI

This equivalent circuit has the same connections as the

original one (Figure 4) to simplify the analysis; this will RIEQ

be useful later on as we combine all of the error terms.

VIBI VIBI = IBI RIEQ

Resistance Seen by the Inverting Input

Figure 8 is a non-inverting gain amplifier. The process FIGURE 10: Application to Inverting Bias

discussed in the last section will be used here to Current Error Calculations.

calculate the resistance seen by the inverting input.

Note: Since the op amp’s inverting input voltage

U1 must equal its non-inverting input voltage,

VOUT VIBI is shown as a change in VOUT referred

V1 to the input.

The error voltage (VIB) shown in Figure 10 is placed in

R3 an equivalent circuit diagram that does not explicitly

R2

show the current IBI; see Figure 11 (IBI is already

included in VIBI). The VIBI source, when it is positive,

will produce a positive change in VOUT.

FIGURE 8: Non-inverting Gain Circuit.

The same process of generating a Thevenin equivalent

applies here, with one short cut:

• The op amp’s output (VOUT) is treated as a

voltage source

- It becomes a short to ground

Figure 9 shows the resulting circuit at the inverting

input, with the test source (VX).

DS01177A-page 4 © 2008 Microchip Technology Inc.

AN1177

The following examples will show how this concept is

U1 applied in common op amp circuits.

VOUT

Note: The concept of noise gain is central to

understanding op amp behavior. For

0

instance, it simplifies op amp bandwidth,

VIBI noise and stability analyses.

R3 Output DC Error

R2

VIBI = IBI RIEQ Now we can quickly calculate the output error of the op

amp (VOE) using the information we have developed.

FIGURE 11: Application to Inverting Bias The principle of superposition gives:

Current Error Calculations.

EQUATION 9:

The resistors R2 and R3 are shown with the same

connections as the original circuit (Figure 8) to simplify V OE = G N V IE

the analysis; this will be explained in the next section. = G N ( V OST + V IBN + V IBI )

Combined Input Voltage Errors and Noise

Gain Examples

All of the DC errors at an op amp’s input (VOST, VIBN UNITY GAIN BUFFER

and VIBI) can be combined into one equivalent voltage

Figure 13 shows a unity gain buffer using an op amp.

source (VIE) at the non-inverting input pin (see

The op amp’s DC model is shown inside the dashed

Figure 12):

box.

EQUATION 7:

IBN VOST

V IE = V OST + V IBN + V IBI

U1

VIN

VOUT

VIE IBI

Feedback U1

and VOUT

VINk

n Signal Path

FIGURE 13: Unity Gain Buffer.

Circuitry

Because the resistances seen by the op amp inputs are

zero and GN = 1 V/V, the output voltage is simply:

FIGURE 12: Circuit Diagram Illustrating

the Concept of Noise Gain. EQUATION 10:

Noise gain (GN) is the DC gain from VIE (at the non- V OUT = V IN + V OST

inverting input pin) to VOUT when the op amp operates

in a closed-loop condition, when all other (external) Let’s use Microchip’s MCP601 op amp to illustrate this

energy sources are zero. GN is positive for stable feed- design. We’ll assume that VCM, VDD and VOUT vary

back loops. This gain can be obtained with any reason- across their complete ranges. We’ll use an arbitrary

able circuit analysis method. In equation form, we estimate of the worst-case value for ΔVOS/ΔTA (see the

have: data sheet for the official specifications). R1 and R3 will

be 0.1% resistors.

EQUATION 8:

Note: Since the MCP601’s common mode input

V OUT

G N = ------------- voltage range (VCMR), at +25°C, is limited

V IE to the range -0.3V and VDD – 1.2V, there

Where: will be large output errors when VCM

VINk = 0V approaches VDD.

k = 1 to n

© 2008 Microchip Technology Inc. DS01177A-page 5

AN1177

EXAMPLE 1: EXAMPLE 2:

Maximum VOE = VOST: Maximum VOST = ±3.8 mV

VOS < ±2.00 mV Selected Resistors (see Figure 14):

ΔVOUT/AOL ≤ (2.65V)/(100 kV/V) R3 = 20.0 kΩ

≤ 0.03 mV R2 = 2.21 kΩ

ΔVDD/PSRR ≤ (1.40V)/(10.0 kV/V) R1 = 2.00 kΩ

≤ 0.14 mV

GN = 10.05 V/V

ΔVCM/CMRR ≤ (4.3V – (-0.3V))/(5.62 kV/V)

≤ 0.82 mV = ±0.41 mV Maximum VIBN:

ΔTA(ΔVOS/ΔTA) ≤ (100°C) (±12 µV/°C) RNEQ = 2.00 kΩ

≤ ±1.20 mV VIBN ≥ -(5 nA + 0.5 nA)(2.00 kΩ) = -11 µV

VOST ≤ ±3.8 mV

Maximum VIBN:

RIEQ = 1.99 kΩ

NON-INVERTING AMPLIFIER

VIBN ≤ (5 nA – 0.5 nA)(1.99 kΩ) = 9 µV

Figure 14 shows a non-inverting gain amplifier with an

LC low-pass filter at the input. The op amp’s DC model Maximum VOE:

is shown inside the dashed box. VOE ≤ ±38 mV

R1 L1 C1 INVERTING AMPLIFIER

VIN

Figure 15 shows an inverting gain amplifier. The op

amp’s DC model is shown inside the dashed box.

IBN VOST

U1 IBN VOST

R1 VOUT U1

VOUT

IBI R1

IBI

R2 R3 VIN

R2 R3

FIGURE 14: Non-inverting Gain Amplifier.

The output voltage with error is: FIGURE 15: Inverting Gain Amplifier.

The output voltage with error is:

EQUATION 11:

EQUATION 12:

V OE = G N ( V OST + V IBN + V IBI )

V OE = G N ( V OST + V IBN + V IBI )

V OUT = G N V IN + V OE

V OUT = – ( G N – 1 ) V IN + V OE

Where:

Where:

GN = 1 + R3/R2

GN = 1 + R3/R2

RNEQ = R1

RNEQ = R1

RIEQ = R2||R3

RIEQ = R2||R3

VIBN = –IBNRNEQ

VIBN = –IBNRNEQ

VIBI = IBIRIEQ

VIBI = IBIRIEQ

The MCP601 VOST calculations in Example 1 can be

used for a gain of +10 V/V example: Notice that Example 2 is easily modified for an inverting

gain of -9 V/V; the resistors and VOE are the same (only

the signal gain is changed).

DS01177A-page 6 © 2008 Microchip Technology Inc.

AN1177

DIFFERENCE AMPLIFIER CIRCUIT OPTIMIZATION

Figure 16 shows a difference amplifier. The op amp’s There are a few, simple design techniques that can

DC model is shown inside the dashed box. Notice that quickly help a designer reach an acceptable accuracy.

this circuit can be analyzed quickly using superposition.

Gain Selection

R1 R2

Set any amplifier next to a signal source (e.g., temper-

VP VREF

ature sensor) to the highest reasonable gain. This will

cause any later gains to be small; typically they will be

IBN VOST

at a gain of 1 V/V.

U1

This design technique minimizes the impact most of the

VOUT

analog signal processing components have on the

overall error. It also allows the designer to reduce cost

IBI

by specifying more precise components only where

VM they are needed.

R3 R4

Minimizing Bias Current Errors

FIGURE 16: Difference Amplifier. For the examples shown in Figure 13 through

The output voltage with error is: Figure 16, it is instructive to convert the bias current

error voltages to the equivalent form using the specified

EQUATION 13: currents:

V OE = G N ( V IE + V IBN + V IBI )

EQUATION 14:

V OUT = ( G N – 1 ) ( V P – V M ) + V REF + V OE V IBN + V IBI = – I BN R NEQ + I BI R IEQ

Where: R IEQ + R NEQ

= I B ( R IEQ – R NEQ ) – I OS ⎛ ---------------------------------⎞

⎝ 2 ⎠

R2 = R1

R4 = R3 Minimizing the resistances helps minimize these errors

GN = 1 + R2/R1 = 1+R4/R3 for all op amps.

RNEQ = R1||R2 Many op amps’ bias current (IB) have a much larger

RIEQ = R3||R4 maximum specification than their offset current (IOS). In

VIBN = –IBNRNEQ that case, set RN_EQ = RI_EQ for the best performance.

When IOS is much smaller than IB, the resistor toler-

VIBI = IBIRIEQ ance (RTOL) needs to be good enough to prevent IB

from becoming a significant contributor to the error:

Using the MCP601 in a differential amplifier with gain

10 V/V gives (similar to Example 2): EQUATION 15:

I OS

EXAMPLE 3: RTOL << 4 --------

IB

Maximum VOST = ±3.8 mV

Selected Resistors (see Figure 16): Large input resistances can also cause a significant

shift in the input common mode voltage (VCM). In some

R1 = R3 = 2.00 kΩ

cases, this can significantly reduce the input common

R2 = R4 = 20.0 kΩ mode voltage range (VCMR):

GN = 11.00 V/V

(GN–1) = 10.00 V/V, the differential gain EQUATION 16:

R +R

Maximum Error Voltages: Δ V CM = – I B ⎛⎝ --------------------------------

IEQ NEQ⎞

-

⎠

2

VIBN ≥ -(5 nA + 0.5 nA)(1.82 kΩ) = -10 µV

VIBN ≤ (5 nA – 0.5 nA)(1.82 kΩ) = 8 µV V CMR_EQ = V CMR + Δ V CM

VOE ≤ ±42 mV

© 2008 Microchip Technology Inc. DS01177A-page 7

AN1177

Op Amp Selection ADVANCED TOPICS

The op amp needs to support the level of DC precision

required by the design. Table 1 shows four general op PCB Layout

amp architectures that give trade-offs between Printed Circuit Board (PCB) layout can have a signifi-

performance, cost and design complexity. cant effect on DC precision. Effects that need to be

considered include:

TABLE 1: OP AMP CAPABILITIES(1)

• Ground Loops – Poor grounding techniques and

Performance for Each Architecture inattention to current return paths can cause

Parameter General Auto- Auto-

significant shifts in DC voltages

Trimmed • Crosstalk – Other signals on a PCB can find

Purpose calibrated zeroed

sneak paths through the ground, power supplies

VOS 1 2 3 4

and traces

ΔVOS/ΔTA 1 1 3 4

VOS Aging 1 1 3 4

Input Common Mode Voltage Range

AOL 2 2 3 4

CMRR 1 1 1 4

A commonly overlooked error source is allowing the

signal to go outside the input voltage range. This most

PSRR 1 1 1 4

commonly occurs when using a non-rail-to-rail input op

IB 2 2 1 3 amp in unity gain; the input will cause an output error

IOS 2 2 2 2 when the VCMR is exceeded; this error grows quickly.

Note 1: The performance numbers signify: 1 = okay,

2 = good, 3 = better and 4 = best. Output Voltage Range

There will be a significant error, that grows very quick,

Process and Environmental Variations

when the output voltage range is exceeded. The VOL

Methods to evaluate a design’s variation in and VOH specifications usually shown in op amp data

performance are commonly understood in the industry. sheets describe non-linear behavior (i.e., when used as

Examples include worst case analysis (all tolerances at a comparator). When the output approaches either

minimum or maximum) and RSS (Root Sum of limit, VOST can increase significantly before reaching

Squares – a statistical approach). the hard limits. For the most stringent designs, keep

VOUT within the range that the data sheet shows for the

The following list gives important op amp behaviors to

AOL specification.

include when evaluating process and environmental

changes (almost all have a Gaussian distribution):

Noise

• VOS

- All VOS values for duals and quads are The data sheet’s input noise density specifications can

statistically independent (zero correlation) be used to calculate an op amp’s integrated output

• 1/AOL, 1/CMRR and 1/PSRR (in units of µV/V) noise (random variation in output voltage). This helps

determine the range of expected errors at any point in

• ΔVOS/ΔTA

time; it also can significantly reduce the output range

• Offset Aging when there is a very high gain.

- Increases with time

- Only specified on auto-zeroed op amp data Non-linear Distortion

sheets

Non-linear distortion converts a sinewave at one

• IB and IOS

frequency into a Fourier series of tones; the undesired

- CMOS inputs (with ESD diodes) have an tone frequencies are the harmonic distortion products.

exponential relationship with temperature One of these undesired tones is at zero frequency

(double every 10°C increase) (DC); non-linear distortion can produce DC shifts.

- Bipolar inputs typically double at -40°C and

For example, a simple sinewave that is processed by

are halved at +125°C

an amplifier with a quadratic (polynomial) response will

- Are typically uncorrelated produce:

DS01177A-page 8 © 2008 Microchip Technology Inc.

AN1177

EQUATION 17: Oscillations

V IN = V M sin ( 2πft ) We sometimes see an op amp circuit that is unstable

2

V OUT = A 0 + A 1 V IN + A 2 V IN enough to oscillate. When this does happen, many

2 puzzling symptoms appear. The supply current

= A 0 + A 1 V M sin ( 2 π ft ) + A 2 ( V M sin ( 2 π ft ) ) increases, the DC voltages in a circuit can shift,

= B 0 + B 1 sin ( 2 π ft ) + B 2 cos ( 4 π ft ) voltages can wander and intermittent glitches can be

Where: seen.

2 To find this problem, use a fast oscilloscope and

A2 VM

B 0 = A 0 + -------------

- change the time scale; it may be necessary to gain up

2 a signal to see oscillations much smaller than 0.1V.

B1 = A1 VM To verify the source of oscillation (unstable behavior),

2 modify component values (e.g., place a capacitor in

–A2 VM parallel) in different feedback loops. A change in

B 2 = -----------------

2 oscillation frequency usually indicates that the unstable

loop has been affected.

All other even order harmonic distortion terms cause a Note: Op amps, by themselves, cannot be either

shift in DC bias too. The quadratic term, however, stable or unstable. The feedback loop

usually dominates. design (interaction of op amp and passive

Using mildly non-linear components in the signal path components) sets the stability.

can cause this effect. The cure is to select higher

quality components.

SUMMARY

More commonly, higher frequency signals will be re-

routed through a non-linear element. A common This application note has covered the topic of precision

example is discussed in detail in the next section. design using (voltage feedback) op amps in some

detail. It shows how all of the DC errors can be referred

to the input; they appear as an additional change in

EMI

input offset voltage. It gives results for the most

Electro-magnetic Interference (EMI) at high frequen- common op amp circuits: unity gain buffer, non-invert-

cies (i.e., near and above the op amp’s Gain Bandwidth ing gain amplifier, inverting gain amplifier and

Product) easily couples to the inputs of any component difference amplifier. Tips on optimizing performance

on a PCB; op amps are no exception to this rule. and coverage of advanced topics help the designer

Because the op amp has little control over this energy, with more difficult designs. The references give

and the ESD diodes are very fast, the latter will rectify additional information on related topics.

high frequency EMI.

The rectification of the EMI energy produces both high REFERENCES

frequency energy and a significant DC shift at the op

amp inputs. This appears as an unexpectedly large Textbook on Circuit Level Design

VOST on many measurement boxes; they average out

the high frequency component. To see if this is an issue [1] Paul R. Gray and Robert G. Meyer, “Analysis

with your design, use a fast oscilloscope at short time and Design of Analog Integrated Circuits,” 2nd

scales. Ed., John Wiley & Sons, 1984.

The most effective cures for EMI problems are handled

at the PCB design level. The coupling paths include Textbook on Transistor Level Design

power supply lines, magnetic loops and capacitive [2] Paul R. Gray and Robert G. Meyer, “Analysis

metal areas. and Design of Analog Integrated Circuits, 2nd

It is possible to improve performance with high Ed., John Wiley & Sons, 1984.

frequency filters at the op amp inputs. Usually, how-

ever, the improvements are small. Also, the filters may

affect the feedback network’s stability, causing

unexpected behaviors.

© 2008 Microchip Technology Inc. DS01177A-page 9

AN1177

APPENDIX A: INPUT OFFSET A.1.1 CIRCUIT DESIGN

MEASUREMENT The goal is to make GN reasonably large and the error

CIRCUIT terms (with VOST, IBN and IBI) as small as possible. The

following design choices will give good results (since

This appendix shows a simple test circuit that can be GNVOST is chosen to be so large):

used on the bench to evaluate most op amps’ input

offset voltage and bias current performance. A simpler EQUATION A-2:

circuit is discussed first, which only measures VOST. It

( 25mV )

is then expanded to include IBN and IBI measurements. G N ≈ -------------------------------

The limitations of these circuit are also discussed. ( max V OST )

R 3 ≈ typical load resistance

A.1 Basic Input Offset Test Circuit R3

R 2 = --------------- -

GN – 2

The circuit shown in Figure A-1 supports quick op amp R

VOST measurements (VOS, AOL, CMRR, PSRR and R 1 = ------3-

ΔVOS/ΔTA). VP sets the op amp’s VCM. VM sets the GN

nominal VOUT value. R1 isolates U1’s input from VP and

is used to cancel IB induced errors. The two resistors The 25 mV used to estimate GN gives VOUT a reason-

R3 set an inverting gain of -1 V/V for VM. R2 increases able output range. For instance, the MCP601’s AOL

the noise gain, but does not affect the gains seen by VP specification requires VOUT to be 0.1V from the rails;

and VM. VDD and VSS are the supply voltages, which the GNVOST term will make this 0.05V to 0.15V from the

can be varied for PSRR measurements. rails.

Solving for VOST, and assuming that the bias current

VDD errors are negligible, gives:

R1

VP U1

VOUT EQUATION A-3:

R2 V OUT#1 – ( 2V P – V M )

VSS V OST ≈ ----------------------------------------------------

GN

VM

R3 R3 Let’s use Microchip’s MCP601 op amp to illustrate this

design (similar to Example 2 on page 6). R3 is reduced

FIGURE A-1: Offset Test Circuit.

to minimize the impact of IBN and IBI.

The common mode input voltage and output voltage

are: EXAMPLE A-1:

VOST ≤ ±3.8 mV

EQUATION A-1:

Design Selections:

V OST

V CM = V P + ⎛ ---------------⎞ – I BN R 1 ≈

⎝ 2 ⎠ GN (25 mV)/(3.8 mV)

V OST = 6.6 V/V → 5 V/V

= V P + ⎛ ---------------⎞ – ( I B + I OS )R 1

⎝ 2 ⎠ R3 = 100 kΩ → 20.0 kΩ

V OUT = 2V P – V M + V OST G N – I BN G N R 1 + I BI R 3

R2 = 6.65 kΩ

= 2V P – V M + V OST G N + I B ( R 3 – G N R 1 )

R1 = 4.02 kΩ

R3 + GN R1

– I OS ⎛⎝ ---------------------------⎞⎠ Impact on VCM and VOUT accuracy:

2

Where: VCM = VP ± 1.9 mV

GN = 2 + R3/R2 VOUT = 2VP – VM + VOSTGN ± 0.01 mV

The error in VCM, divided by CMRR (5.62 kV/V),

Note: VCM contains a VOST/2 term because it is produces a ±0.3 µV error in VOUT. It also reduces the

the average of the two input voltages (one input common mode voltage range by 2.0 mV, which is

with VOST and the other without). Usually, negligible for most purposes. Thus, the estimated VOUT

this makes only a small difference. has errors, dominated by the bias currents, of about

±0.04%.

DS01177A-page 10 © 2008 Microchip Technology Inc.

AN1177

A.1.2 MEASUREMENT STRATEGY The common mode input voltage and output voltage

are:

Now that we have a circuit, it pays to have a strategy to

measure those points needed. Let’s assume the goal is

to double check the MCP601’s data sheet specifica- EQUATION A-4:

tions at +25°C. V OST

V CM = V P + ⎛ ------------⎞ – I BN R NEQ

⎝ 2 ⎠

TABLE A-1: MEASUREMENT POINTS V OST

= V P + ⎛⎝ ------------⎞⎠ – ( I B + I OS )R NEQ

Nominal Bias 2

Target Parameters V OUT = 2V P – V M + G N ( V OST – I BN R NEQ + I BI R IEQ )

Meas. Point

No. V = 2V P – V M + G N V OST + I B G N ( R IEQ – R NEQ )

DD VCM VOUT V R IEQ + R NEQ

OS AOL CMRR PSRR

(V) (V) (V) + I OS G N ⎛ --------------------------------⎞

⎝ 2 ⎠

1 2.7 1.35 1.35 X — — X Where:

2 1.35 0.1 — X — — GN = 2 + R3/R2

3 1.35 2.6 — X — — RNEQ = R1, SW4 = short

4 5.0 -0.3 2.5 — — X — = R1+R4, SW4 = open

5 3.8 2.5 — — X — RIEQ = R3/GN, SW5 = short

6 5.5 2.75 2.75 X — — X = (R3/GN)+R5, SW5 = open

7 2.75 0.1 — X — —

A.2.1 CIRCUIT DESIGN

8 2.75 5.4 — X — —

We now add to the design equations estimates of R4,

See Section “Input Offset Related Specifications” R5, C4 and C5. The capacitors are much larger than

on page 2 for the equations relating these measure- most op amps’ common mode input capacitance (for

ments and the specifications. stability, noise and speed).

A.2 Complete Input Offset Test Circuit EQUATION A-5:

The circuit in Figure A-2 functions like Figure A-1, plus Select GN, R3, R2 and R1 as before

it has R4 and R5 to measure IBN and IBI. SW4 and SW5

R4 = (25 mV) / (GN max |IBN|)

short R4 and R5 for all VOST related measurements. C4

and C5 help maintain stability and reduce noise. R5 = (25 mV) / (GN max |IBI|)

C4 = C5 = 100 pF

SW4

The practical way to use this circuit is as follows.

Measure all of the VOST related parameters with SW4

C4

R1 and SW5 shorted; the circuit behaves exactly as

VP VDD described in A.1 “Basic Input Offset Test Circuit”.

R4

U1 To measure IBN and IBI, take three measurements at a

R2 VOUT single bias point with different switch selections:

R5

VSS TABLE A-2: SWITCH SELECTIONS

C5 Switches

Meas.

Emphasize

R3 R3 No. SW1 SW2

SW5

VM 1 short short VOST

FIGURE A-2: Offset Test Circuit with Bias 2 open short VOST and IBNR4

Current Capabilities. 3 short open VOST and IBIR5

Note 1: The change in VCM caused by R4, in Meas. No.

2, can be substantial.

© 2008 Microchip Technology Inc. DS01177A-page 11

AN1177

Subtracting these measurements gives the following A.2.2 MEASUREMENT STRATEGY

simple results:

Let’s double check the MCP601’s data sheet bias

current specifications, for one temperature, at

EQUATION A-6: VDD = 2.7V and 5.5V.

– ( V OUT#2 – V OUT#1 )

I BN = ------------------------------------------------- -

R4 TABLE A-3: BIAS CURRENT

V OUT#3 – V OUT#1 MEASUREMENT POINTS

I BI = ------------------------------------------ -

R5 Nominal Bias Switch

V OUT#1 – ( 2V P – V M ) R3 Meas. Point Settings Target

V OST = --------------------------------------------------- - + I BN R 1 – I BI ⋅ ------

GN G No. V Parameter

DD VCM VOUT SW

V OUT#1 – ( 2V P – V M ) (V) (V) (V) 4 SW5

≈ ---------------------------------------------------

-

GN

1 2.7 1.35 1.35 short short VOST

( I BN + I BI )

I B = -------------------------- - 2 open short IBN

2

I OS = I BN – I BI 3 short open IBI

4 5.5 2.75 2.75 short short VOST

Let’s continue Example A-1, which uses the MCP601, 5 open short IBN

for measurements up to +85°C: 6 short open IBI

EXAMPLE A-2: See Equation A-6 for the parameter extraction

VOST ≤ ±3.8 mV equations.

TA ≤ +85°C

A.3 Limitations of These Test Circuits

Additional Design Selections:

Some of the more important limitations are:

R4 = R5 = (25 mV) / ((5 V/V) (60 pA))

• VCM is not accurately controlled (especially for

= 83.3 MΩ → 20.0 MΩ CMRR)

GNR4 = GNR5 = 100 MΩ • The common mode input range may be exceeded

C4 = C5 = 100 pF when IBNR4 is very large

Example Output Values: • The VOST resolution is not better than10 µV to

20 µV

IBNGNR4 = 0.10 mV, IBN = 1 pA • Temperature gradients on the PCB cause thermo-

= 6.0 mV, IBN = 60 pA junction voltages

• VOUT needs to be measured accurately in order to

The 20 MΩ is comprised of two, easy to obtain, 10 MΩ maintain reasonable accuracy on the extracted

resistors in series. Using a 18-bit ADC to measure parameters. For instance, with VDD = 5.5V and a

VOUT should be adequate. Let’s continue Example A-2 maximum VOSTGN of 0.1V, an ADC at VOUT

at +125°C by using a different value for R4 and R5: would need at least 16 bits in order to resolve

VOST to 0.1%

EXAMPLE A-3: • Measurements can be slower than with other

VOST < ±3.8 mV solutions

TA = +125°C

Additional Design Selections:

R4 = R5 = (25 mV) / ((5 V/V) (5 nA))

= 1 MΩ

GNR4 = GNR5 = 5 MΩ

C4 = C5 = 100 pF

Example Output Values:

IBNGNR4 = 0.25 mV, IBN = 50 pA

= 25 mV, IBN = 5 nA

This means that a 16-bit ADC is sufficient for this

temperature.

DS01177A-page 12 © 2008 Microchip Technology Inc.

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device Trademarks

applications and the like is provided only for your convenience The Microchip name and logo, the Microchip logo, Accuron,

and may be superseded by updates. It is your responsibility to

dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro,

ensure that your application meets with your specifications.

PICSTART, PRO MATE, rfPIC and SmartShunt are registered

MICROCHIP MAKES NO REPRESENTATIONS OR trademarks of Microchip Technology Incorporated in the

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

U.S.A. and other countries.

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION, FilterLab, Linear Active Thermistor, MXDEV, MXLAB,

INCLUDING BUT NOT LIMITED TO ITS CONDITION, SEEVAL, SmartSensor and The Embedded Control Solutions

QUALITY, PERFORMANCE, MERCHANTABILITY OR Company are registered trademarks of Microchip Technology

FITNESS FOR PURPOSE. Microchip disclaims all liability Incorporated in the U.S.A.

arising from this information and its use. Use of Microchip Analog-for-the-Digital Age, Application Maestro, CodeGuard,

devices in life support and/or safety applications is entirely at dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

the buyer’s risk, and the buyer agrees to defend, indemnify and ECONOMONITOR, FanSense, In-Circuit Serial

hold harmless Microchip from any and all damages, claims, Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB

suits, or expenses resulting from such use. No licenses are Certified logo, MPLIB, MPLINK, mTouch, PICkit, PICDEM,

conveyed, implicitly or otherwise, under any Microchip PICDEM.net, PICtail, PIC32 logo, PowerCal, PowerInfo,

intellectual property rights. PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total

Endurance, UNI/O, WiperLock and ZENA are trademarks of

Microchip Technology Incorporated in the U.S.A. and other

countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2008, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

© 2008 Microchip Technology Inc. DS01177A-page 13

WORLDWIDE SALES AND SERVICE

AMERICAS ASIA/PACIFIC ASIA/PACIFIC EUROPE

Corporate Office Asia Pacific Office India - Bangalore Austria - Wels

2355 West Chandler Blvd. Suites 3707-14, 37th Floor Tel: 91-80-4182-8400 Tel: 43-7242-2244-39

Chandler, AZ 85224-6199 Tower 6, The Gateway Fax: 91-80-4182-8422 Fax: 43-7242-2244-393

Tel: 480-792-7200 Harbour City, Kowloon India - New Delhi Denmark - Copenhagen

Fax: 480-792-7277 Hong Kong Tel: 45-4450-2828

Tel: 91-11-4160-8631

Technical Support: Tel: 852-2401-1200 Fax: 45-4485-2829

Fax: 91-11-4160-8632

http://support.microchip.com

Fax: 852-2401-3431 France - Paris

Web Address: India - Pune

Australia - Sydney Tel: 91-20-2566-1512 Tel: 33-1-69-53-63-20

www.microchip.com

Tel: 61-2-9868-6733 Fax: 91-20-2566-1513 Fax: 33-1-69-30-90-79

Atlanta Fax: 61-2-9868-6755

Duluth, GA Japan - Yokohama Germany - Munich

China - Beijing Tel: 81-45-471- 6166 Tel: 49-89-627-144-0

Tel: 678-957-9614

Tel: 86-10-8528-2100 Fax: 49-89-627-144-44

Fax: 678-957-1455 Fax: 81-45-471-6122

Fax: 86-10-8528-2104 Italy - Milan

Boston Korea - Daegu

China - Chengdu Tel: 39-0331-742611

Westborough, MA Tel: 82-53-744-4301

Tel: 86-28-8665-5511 Fax: 82-53-744-4302 Fax: 39-0331-466781

Tel: 774-760-0087

Fax: 86-28-8665-7889 Netherlands - Drunen

Fax: 774-760-0088 Korea - Seoul

China - Hong Kong SAR Tel: 82-2-554-7200 Tel: 31-416-690399

Chicago

Itasca, IL Tel: 852-2401-1200 Fax: 82-2-558-5932 or Fax: 31-416-690340

Tel: 630-285-0071 Fax: 852-2401-3431 82-2-558-5934 Spain - Madrid

Fax: 630-285-0075 China - Nanjing Tel: 34-91-708-08-90

Malaysia - Kuala Lumpur

Tel: 86-25-8473-2460 Fax: 34-91-708-08-91

Dallas Tel: 60-3-6201-9857

Addison, TX Fax: 86-25-8473-2470 Fax: 60-3-6201-9859 UK - Wokingham

Tel: 972-818-7423 China - Qingdao Tel: 44-118-921-5869

Malaysia - Penang

Fax: 972-818-2924 Tel: 86-532-8502-7355 Fax: 44-118-921-5820

Tel: 60-4-227-8870

Detroit Fax: 86-532-8502-7205 Fax: 60-4-227-4068

Farmington Hills, MI China - Shanghai Philippines - Manila

Tel: 248-538-2250 Tel: 86-21-5407-5533 Tel: 63-2-634-9065

Fax: 248-538-2260 Fax: 86-21-5407-5066 Fax: 63-2-634-9069

Kokomo China - Shenyang Singapore

Kokomo, IN Tel: 86-24-2334-2829 Tel: 65-6334-8870

Tel: 765-864-8360 Fax: 86-24-2334-2393 Fax: 65-6334-8850

Fax: 765-864-8387

China - Shenzhen Taiwan - Hsin Chu

Los Angeles Tel: 86-755-8203-2660 Tel: 886-3-572-9526

Mission Viejo, CA Fax: 86-755-8203-1760 Fax: 886-3-572-6459

Tel: 949-462-9523

China - Wuhan Taiwan - Kaohsiung

Fax: 949-462-9608

Tel: 86-27-5980-5300 Tel: 886-7-536-4818

Santa Clara Fax: 86-27-5980-5118 Fax: 886-7-536-4803

Santa Clara, CA

China - Xiamen Taiwan - Taipei

Tel: 408-961-6444

Tel: 86-592-2388138 Tel: 886-2-2500-6610

Fax: 408-961-6445

Fax: 86-592-2388130 Fax: 886-2-2508-0102

Toronto

China - Xian Thailand - Bangkok

Mississauga, Ontario,

Tel: 86-29-8833-7252 Tel: 66-2-694-1351

Canada

Tel: 905-673-0699 Fax: 86-29-8833-7256 Fax: 66-2-694-1350

Fax: 905-673-6509 China - Zhuhai

Tel: 86-756-3210040

Fax: 86-756-3210049

01/02/08

DS01177A-page 14 © 2008 Microchip Technology Inc.

Potrebbero piacerti anche

- Op Amp Precision Design-DC ErrorsDocumento14 pagineOp Amp Precision Design-DC ErrorsSougata DasNessuna valutazione finora

- Ch-1 - Opertional Amplifier Fundamentals byDocumento12 pagineCh-1 - Opertional Amplifier Fundamentals byyeasirarafat941Nessuna valutazione finora

- Philips On OpampsDocumento10 paginePhilips On OpampsSpun_GNessuna valutazione finora

- VI-200 / VI-J00 Family: Design Guide & Applications ManualDocumento97 pagineVI-200 / VI-J00 Family: Design Guide & Applications ManualcurzNessuna valutazione finora

- How The Voltage Reference Affects ADC Design Part 2 PDFDocumento6 pagineHow The Voltage Reference Affects ADC Design Part 2 PDFThanos van RamNessuna valutazione finora

- Ext Comp Op Amps Dec 10Documento12 pagineExt Comp Op Amps Dec 10Alvin RymashNessuna valutazione finora

- Operational AmplifiersDocumento15 pagineOperational AmplifiersPhu GNessuna valutazione finora

- Lab 2 Basic CMOS AmplifiersDocumento5 pagineLab 2 Basic CMOS AmplifiersJatinKumarNessuna valutazione finora

- Two Stage CMOS Op Amp - Seid PDFDocumento79 pagineTwo Stage CMOS Op Amp - Seid PDFTayachew BerhanNessuna valutazione finora

- Company Profile: LCR Bridge, Conductivity Bridge Etc. However, During Last Nearly 46 Years The Product MixDocumento58 pagineCompany Profile: LCR Bridge, Conductivity Bridge Etc. However, During Last Nearly 46 Years The Product Mixuatulkar100% (1)

- Principles and Applications of The ICL7660 CMOS Voltage Converter PDFDocumento10 paginePrinciples and Applications of The ICL7660 CMOS Voltage Converter PDFPeter JordanNessuna valutazione finora

- Lec 05Documento62 pagineLec 05fedirasagaNessuna valutazione finora

- Chapter 6 - Cmos Operational AmplifiersDocumento79 pagineChapter 6 - Cmos Operational AmplifierssanjayorcaNessuna valutazione finora

- April 2003 Ray Marston - Understanding and Using OTA Op-AmpsDocumento5 pagineApril 2003 Ray Marston - Understanding and Using OTA Op-AmpsMeatheadMerlin100% (1)

- "Rules of The Road" For High-Speed Differential ADC DriversDocumento11 pagine"Rules of The Road" For High-Speed Differential ADC Driversi512113143348Nessuna valutazione finora

- Chapter 6 - Cmos Operational AmplifiersDocumento79 pagineChapter 6 - Cmos Operational AmplifiersAngelino PimentelNessuna valutazione finora

- SAM - Unit VDocumento18 pagineSAM - Unit VMukund VahinipathiNessuna valutazione finora

- A Reliable Single-Phase Bipolar Buck-Boost Direct PWM AC-AC Converter With Continuous Input/ Output CurrentsDocumento12 pagineA Reliable Single-Phase Bipolar Buck-Boost Direct PWM AC-AC Converter With Continuous Input/ Output CurrentsDar JahangeerNessuna valutazione finora

- Operational Transconductance Amplifier: OperationDocumento12 pagineOperational Transconductance Amplifier: OperationRAJESH REDDY KAKARLANessuna valutazione finora

- RepoDocumento18 pagineRepoAaditya BaidNessuna valutazione finora

- Chapter06-2UP (4 23 02)Documento79 pagineChapter06-2UP (4 23 02)Nelor Jane Robles LagunaNessuna valutazione finora

- A New Circuit Design of Two-Switch Buck-Boost ConvDocumento10 pagineA New Circuit Design of Two-Switch Buck-Boost ConvBinh NguyenNessuna valutazione finora

- EDC Lab ManualDocumento63 pagineEDC Lab Manualranjitha gavniNessuna valutazione finora

- Design With Linear Integrated Circuits Experiment No: 1Documento11 pagineDesign With Linear Integrated Circuits Experiment No: 1Nilesh SinghNessuna valutazione finora

- Op-Amp Basic Stages: Adama UniversityDocumento18 pagineOp-Amp Basic Stages: Adama Universitygebretsadkan abrhaNessuna valutazione finora

- Linear Power Supplies Data Sheet: FeaturesDocumento9 pagineLinear Power Supplies Data Sheet: FeaturesDiego GrisalesNessuna valutazione finora

- Operational Amplifiers NewDocumento20 pagineOperational Amplifiers NewLester Garcia100% (1)

- Activity 6. BJT Current MirrorDocumento6 pagineActivity 6. BJT Current MirrorGiap LuongNessuna valutazione finora

- FOMSASDocumento169 pagineFOMSASBaekhyunNessuna valutazione finora

- Q4: Differential AmplifierDocumento5 pagineQ4: Differential Amplifiersrikanthpatel132Nessuna valutazione finora

- Sinusoidal AmplifierDocumento25 pagineSinusoidal AmplifierVandhana PramodhanNessuna valutazione finora

- Slyt157 PDFDocumento7 pagineSlyt157 PDFrmNessuna valutazione finora

- Chapter 3Documento47 pagineChapter 3yasinNessuna valutazione finora

- Linear & Digital Ic Applications: Course FileDocumento200 pagineLinear & Digital Ic Applications: Course FileDhanush 413Nessuna valutazione finora

- Co-3 MaterialDocumento35 pagineCo-3 MaterialMLM TELUGU GAMERSNessuna valutazione finora

- ClassDocumento35 pagineClassSrikkanth RamachandranNessuna valutazione finora

- 765 - AMC1200Interfacing A Differential OutputDocumento3 pagine765 - AMC1200Interfacing A Differential Outputachsanul khabibNessuna valutazione finora

- The Instrumentation Amplifier - Operational Amplifiers - Electronics TextbookDocumento4 pagineThe Instrumentation Amplifier - Operational Amplifiers - Electronics TextbookriponkumarNessuna valutazione finora

- Exp. 8 - Operational AmplifiersDocumento13 pagineExp. 8 - Operational AmplifiersHilmiNessuna valutazione finora

- AN-581 Application Note: Biasing and Decoupling Op Amps in Single Supply ApplicationsDocumento8 pagineAN-581 Application Note: Biasing and Decoupling Op Amps in Single Supply Applicationsaravind babuNessuna valutazione finora

- DocumentationDocumento8 pagineDocumentationmmNessuna valutazione finora

- EEE111 - Lab ManualDocumento28 pagineEEE111 - Lab ManualAnindita MishiNessuna valutazione finora

- Chap04 (12 21 06) PDFDocumento66 pagineChap04 (12 21 06) PDFHassan FarssiNessuna valutazione finora

- (A) - Amplification of A Difference: in This LectureDocumento3 pagine(A) - Amplification of A Difference: in This LectureHassan FarssiNessuna valutazione finora

- Service Manual: Orap) - Ig Eoi - AtizerDocumento14 pagineService Manual: Orap) - Ig Eoi - AtizerCarlos CuetoNessuna valutazione finora

- Sony Sa Wd200Documento16 pagineSony Sa Wd200kcorebusNessuna valutazione finora

- Operational AmplifierDocumento26 pagineOperational AmplifierAbhiraj DNessuna valutazione finora

- DC Characteristics of Op-AmpDocumento7 pagineDC Characteristics of Op-AmpVENKATESWARLU MUVVA (PA2111004040011)Nessuna valutazione finora

- Operational AmplifierDocumento24 pagineOperational AmplifierSead ArifagićNessuna valutazione finora

- AN-H51 Designing A Boost-Buck (Ĉuk) Converter With The HV9930 / AT9933Documento15 pagineAN-H51 Designing A Boost-Buck (Ĉuk) Converter With The HV9930 / AT9933JohnNessuna valutazione finora

- Operational Amplifier-IVDocumento40 pagineOperational Amplifier-IVBhalchandra ChandakkarNessuna valutazione finora

- MTE 3105 - Lecture-01Documento46 pagineMTE 3105 - Lecture-01shafin2031010Nessuna valutazione finora

- Chapter 8 - Comparators (1.3MB) - Analog ICDocumento42 pagineChapter 8 - Comparators (1.3MB) - Analog ICvenu sNessuna valutazione finora

- Chap08 (8 7 06) PDFDocumento42 pagineChap08 (8 7 06) PDFSebastian OrdoñezNessuna valutazione finora

- Ss-Isolated Ps OptocouplerDocumento9 pagineSs-Isolated Ps Optocouplerishrat.jamal1191Nessuna valutazione finora

- All BXE Experiments ManualDocumento21 pagineAll BXE Experiments ManualSahil PatelNessuna valutazione finora

- Applied Electronics CH3Documento17 pagineApplied Electronics CH3mesfin snowNessuna valutazione finora

- 110 Integrated Circuit Projects for the Home ConstructorDa Everand110 Integrated Circuit Projects for the Home ConstructorValutazione: 4.5 su 5 stelle4.5/5 (2)

- ENG DS 1-1773870-7 Filter-Connector 0616Documento74 pagineENG DS 1-1773870-7 Filter-Connector 0616VitaliyGNessuna valutazione finora

- Schematic Half-Bridge ModuleDocumento1 paginaSchematic Half-Bridge ModuleVitaliyGNessuna valutazione finora

- Application Note AN-1214: LED Buck Converter Design Using The IRS2505LDocumento16 pagineApplication Note AN-1214: LED Buck Converter Design Using The IRS2505LVitaliyGNessuna valutazione finora

- MC13783 Buck and Boost Inductor Sizing: Application NoteDocumento8 pagineMC13783 Buck and Boost Inductor Sizing: Application NoteVitaliyGNessuna valutazione finora

- Sciencedirect: A B C A B CDocumento9 pagineSciencedirect: A B C A B CVitaliyGNessuna valutazione finora

- A 1 V Low-Noise CMOS Amplifier Using Autozeroing and Chopper Stabilization TechniqueDocumento6 pagineA 1 V Low-Noise CMOS Amplifier Using Autozeroing and Chopper Stabilization TechniqueVitaliyGNessuna valutazione finora

- A Low Power Low Noise Chopper-Stabilized Tow-Stage Operational Amplifier For Portable Bio-Potential Acquisition Systems Using 90 NM TechnologyDocumento18 pagineA Low Power Low Noise Chopper-Stabilized Tow-Stage Operational Amplifier For Portable Bio-Potential Acquisition Systems Using 90 NM TechnologyVitaliyGNessuna valutazione finora

- A Different Approach On Pythagorean Triangle, Which SatisfiesDocumento4 pagineA Different Approach On Pythagorean Triangle, Which SatisfiesVitaliyGNessuna valutazione finora

- 003 PDFDocumento37 pagine003 PDFVitaliyGNessuna valutazione finora

- GNU/Linux and FPGA in Real-Time Control Applications: Pavel Pisa Pisa@cmp - Felk.cvut - CZ CC By-SaDocumento44 pagineGNU/Linux and FPGA in Real-Time Control Applications: Pavel Pisa Pisa@cmp - Felk.cvut - CZ CC By-SaVitaliyGNessuna valutazione finora

- Simosec Cataloge HA 41 21 enDocumento48 pagineSimosec Cataloge HA 41 21 enEddie FogartyNessuna valutazione finora

- Incremental Conductance MPPT With Direct Control MethodDocumento8 pagineIncremental Conductance MPPT With Direct Control MethodArchana Diwakar Ranjish100% (1)

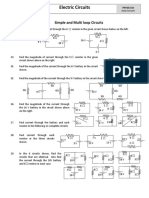

- STD 12 Electric Circuits Worksheets Part 2 (Simple and Multi Loop Circuits) - 1587984854220 - 86LHQ PDFDocumento2 pagineSTD 12 Electric Circuits Worksheets Part 2 (Simple and Multi Loop Circuits) - 1587984854220 - 86LHQ PDFSrihari SrikanthNessuna valutazione finora

- Anpara Thermal Power StationDocumento26 pagineAnpara Thermal Power StationManju Tripathi100% (1)

- Table D Flanges Bs10Documento235 pagineTable D Flanges Bs10Satender VermaNessuna valutazione finora

- Boylestad - Formula SheetDocumento2 pagineBoylestad - Formula SheetZain AliNessuna valutazione finora

- Heat Tracing CalculationDocumento22 pagineHeat Tracing CalculationflyzalNessuna valutazione finora

- 6931 PracticalExperience FH 20191021 WebDocumento13 pagine6931 PracticalExperience FH 20191021 WebLuisEspinozaNessuna valutazione finora

- SIEMENS 04 Modelling The Use of Selective Main Miniature Circuit-BreakersDocumento9 pagineSIEMENS 04 Modelling The Use of Selective Main Miniature Circuit-BreakersShailesh ChettyNessuna valutazione finora

- ws2 8-4lvuDocumento8 paginews2 8-4lvuCarlos MolinaNessuna valutazione finora

- Lect 5 Sub-Transmission LinesDocumento33 pagineLect 5 Sub-Transmission LinesMohammad Haseeb ButtNessuna valutazione finora

- 参量混频双光梳信道化接收机Documento9 pagine参量混频双光梳信道化接收机Gosoviet XINGNessuna valutazione finora

- Datasheet Kf2 RDocumento2 pagineDatasheet Kf2 RjohnzepolNessuna valutazione finora

- Owner's Manual: JL AUDIO 250/1Documento11 pagineOwner's Manual: JL AUDIO 250/1kaiser_shaikh1Nessuna valutazione finora

- Current Carrying Capacity CABLES - BVDocumento3 pagineCurrent Carrying Capacity CABLES - BVStefanita100% (1)

- Temperature Controlled DC FanDocumento5 pagineTemperature Controlled DC FanMuhammad MansoorNessuna valutazione finora

- NG125 MCBDocumento9 pagineNG125 MCBSaswita SaktiNessuna valutazione finora

- Power Generation Course OutlineDocumento3 paginePower Generation Course OutlineRao Umar100% (1)

- ModulanteDocumento23 pagineModulanteVBPNessuna valutazione finora

- Pulse Current Electrodeposition of Manganese Metal From Sulfate SolutionDocumento7 paginePulse Current Electrodeposition of Manganese Metal From Sulfate SolutionrichardNessuna valutazione finora

- Txtopper List of MaterialsDocumento1 paginaTxtopper List of Materialsfox7878Nessuna valutazione finora

- TriBand Trisector - SSC-760220020 - 2.2m AntennaDocumento7 pagineTriBand Trisector - SSC-760220020 - 2.2m AntennaborisNessuna valutazione finora

- PowerFactory 2021 Product SpecificationDocumento14 paginePowerFactory 2021 Product SpecificationGianfranco Pasqua IndianoNessuna valutazione finora

- An-F1 Specifications: 24/7 Asset Monitoring Solution EnergyDocumento4 pagineAn-F1 Specifications: 24/7 Asset Monitoring Solution EnergyJatupol PongsirisartNessuna valutazione finora

- DX-1710-2690-65-19.5i-M: Electrical PropertiesDocumento2 pagineDX-1710-2690-65-19.5i-M: Electrical PropertiesАлександрNessuna valutazione finora

- Packaged Air Conditioner Rooftop B Series: Technical ManualDocumento93 paginePackaged Air Conditioner Rooftop B Series: Technical ManualJf OngNessuna valutazione finora

- List of Lines For Up Gradation of Green Transmission CorridorDocumento138 pagineList of Lines For Up Gradation of Green Transmission CorridorDakshay BhardwajNessuna valutazione finora

- 522 Op ManualDocumento20 pagine522 Op ManualAhmed Abdullah100% (1)

- FQP10N60-FQPF10N60: General Description Product SummaryDocumento7 pagineFQP10N60-FQPF10N60: General Description Product SummaryVuksanov ZarkoNessuna valutazione finora

- EME PresentationDocumento31 pagineEME PresentationNicholas FrederickNessuna valutazione finora