Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Set-Reset (SR) Latch: Asynchronous Level Sensitive Cross-Coupled Nor Gates Active High Inputs (Only One Can Be Active)

Caricato da

Ravi ShastriDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Set-Reset (SR) Latch: Asynchronous Level Sensitive Cross-Coupled Nor Gates Active High Inputs (Only One Can Be Active)

Caricato da

Ravi ShastriCopyright:

Formati disponibili

Anatomy of a Flip-Flop

ELEC 4200

Set-Reset (SR) Latch

Asynchronous

Level sensitive

cross-coupled Nor gates

active high inputs (only one can be active)

S Q S R Q+ Q+ Function

0 0 Q Q Storage State

0 1 0 1 Reset

Q 1 0 1 0 Set

R

1 1 0-? 0-? Indeterminate

State

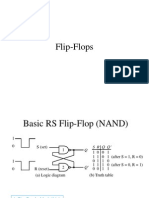

cross-coupled Nand gates

active low inputs (only one can be active)

S Q S R Q+ Q+ Function

0 0 1-? 1-? Indeterminate

State

0 1 1 0 Set

Q

R 1 0 0 1 Reset

1 1 Q Q Storage State

C. E. Stroud, Dept. of ECE, Auburn Univ.

8/06

Anatomy of a Flip-Flop

ELEC 4200

Enabled Set-Reset (SR) Latch

Asynchronous

Level sensitive

cross-coupled Nor gates

active high inputs (S & R cannot be active)

S E S R Q+ Q+ Function

Q 0 x x Q Q Storage State

E 1 0 0 Q Q Storage State

1 0 1 0 1 Reset

Q

1 1 0 1 0 Set

R

1 1 1 0-? 0-? Indeterminate

State

cross-coupled Nand gates

active low inputs (S & R cannot be active)

E S R Q+ Q+ Function

S

Q 0 0 0 1-? 1-? Indeterminate

State

0 0 1 1 0 Set

E

0 1 0 0 1 Reset

Q 0 1 1 Storage State

Q Q

R 1 x x Storage State

Q Q

C. E. Stroud, Dept. of ECE, Auburn Univ.

8/06

Anatomy of a Flip-Flop

ELEC 4200

Transparent D Latch

Asynchronous

Level sensitive

cross-coupled Nor gates

active high enable (E)

D

Q

E D Q+ Function

E 0 x Storage State

Q

Q 1 0 0 Transparent Mode

1 1 1 Transparent Mode

cross-coupled Nand gates

active low enable (E)

D

Q

E D Q+ Function

E 1 x Storage State

Q

Q 0 0 0 Transparent Mode

0 1 1 Transparent Mode

C. E. Stroud, Dept. of ECE, Auburn Univ.

8/06

Anatomy of a Flip-Flop

ELEC 4200

D Flip-Flop

Synchronous (also know as Master-Slave FF)

Edge Triggered (data moves on clock transition)

one latch transparent - the other in storage

active low latch followed by active high latch

positive edge triggered (rising edge of CK)

D

Q

CK

Master Section Slave Section

active low latch active high latch

active high latch followed by active low latch

negative edge triggered (falling edge of CK)

D

Q

CK

Master Section Slave Section

active high latch active low latch

C. E. Stroud, Dept. of ECE, Auburn Univ.

8/06

Anatomy of a Flip-Flop

ELEC 4200

Timing Considerations

Set-up time (tsu)= minimum time input data

must be valid before active edge of clock

Hold time (th)= minimum time input data must

be held valid after active edge of clock

Clock-to-output delay (tco)= maximum time

before output data is valid with respect to

active edge of clock

D

tsu th

CK

tco

Q

Set-up or Hold Time violation => metastability

(Q & Q go to intermediate voltage values which

are eventually resolved to an unknown state)

Set-up & Hold Time violations in a vector set

referred to as clock-data races

C. E. Stroud, Dept. of ECE, Auburn Univ.

8/06

Anatomy of a Flip-Flop

ELEC 4200

Timing Considerations

To verify that a sequential logic circuit will

work at the specified clock frequency, fclk,

we must consider the clock period, Tp, the

propagation delay, Pdel, of the worst case

path through the combinational logic, as

well as tsu and tco of the flip-flops such

that the following relationship holds:

For paths from flip-flop outputs to flip-flop

inputs:

1 ⁄ f clk = T p ≥ P del + t co + t su

For paths from primary inputs to flip-flop

inputs:

1 ⁄ f clk = T p ≥ P del + t su

For paths from flip-flop outputs to primary

outputs:

1 ⁄ f clk = T p ≥ P del + t co

For paths from primary inputs to primary

outputs:

1 ⁄ f clk = T p ≥ P del

Timing analysis and timing simulation CAD

tools are typically used for this verification.

C. E. Stroud, Dept. of ECE, Auburn Univ.

8/06

Anatomy of a Flip-Flop

ELEC 4200

Good Design Practices

Use single clock, single edge synchronous

design techniques as much as possible

Asynchronous interfaces lead to metastability

(minimize the async interface & double clock

data to reduce probability of metastability)

Avoid asynchronous presets & clears on FFs

(use sync presets & clears whenever possible)

DO NOT construct a FF from two level

sensitive latches of the same type with an

inverter on the clock input to one latch

D Q

D active Q D active Q

low low

CK latch latch Q

E Q E Q

BAD Design

DO NOT gate clocks!!!

Create clock enabled FFs via a MUX to feed

back current data

D Q 0 Q

D

1

CEN CEN

Q Q

CK CK

BAD Design GOOD Design

Active high clock enable (CEN)

C. E. Stroud, Dept. of ECE, Auburn Univ.

8/06

Potrebbero piacerti anche

- The Spectral Theory of Toeplitz Operators. (AM-99), Volume 99Da EverandThe Spectral Theory of Toeplitz Operators. (AM-99), Volume 99Nessuna valutazione finora

- Lecture #32 Registers, Counters EtcDocumento21 pagineLecture #32 Registers, Counters EtcRajan GoyalNessuna valutazione finora

- Power Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlDa EverandPower Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlValutazione: 5 su 5 stelle5/5 (1)

- Sequential Logic - Flip-Flops: 6.1 SR LatchDocumento5 pagineSequential Logic - Flip-Flops: 6.1 SR Latchanon020202Nessuna valutazione finora

- Two-Degree-of-Freedom Control Systems: The Youla Parameterization ApproachDa EverandTwo-Degree-of-Freedom Control Systems: The Youla Parameterization ApproachNessuna valutazione finora

- Latch and Flip-FlopDocumento58 pagineLatch and Flip-FlopDalila Nadia RazaliNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Latches and Flip Flops CharacteristicsDocumento13 pagineLatches and Flip Flops CharacteristicsWeaam RaedNessuna valutazione finora

- TTTTT Eeee AsDocumento20 pagineTTTTT Eeee AsEric GongNessuna valutazione finora

- Flip-Flops & Latches: Digital ElectronicsDocumento20 pagineFlip-Flops & Latches: Digital ElectronicsGowtham PalanirajanNessuna valutazione finora

- Computer Architecture 1Documento39 pagineComputer Architecture 1ARAFAT GaamanNessuna valutazione finora

- Sequential LogicDocumento139 pagineSequential Logicmdhuq1Nessuna valutazione finora

- 23 Quick SortDocumento53 pagine23 Quick SortSun77789Nessuna valutazione finora

- Computer Science 141 C I D Computing HardwareDocumento34 pagineComputer Science 141 C I D Computing HardwareVrinda GuptaNessuna valutazione finora

- CH 7Documento69 pagineCH 7katral-jamerson-9379Nessuna valutazione finora

- Unit 9 Latches and Flip-Flops: Dept. of Electrical and Computer Eng., NCTUDocumento33 pagineUnit 9 Latches and Flip-Flops: Dept. of Electrical and Computer Eng., NCTUGevorg PetrosyanNessuna valutazione finora

- 10 - Sequential CircuitDocumento32 pagine10 - Sequential CircuitJose Mari Emmanuel MedinaNessuna valutazione finora

- UntitledDocumento8 pagineUntitledlalita chauhanNessuna valutazione finora

- Flip FlopsDocumento60 pagineFlip FlopsA10-14Rajat KumarNessuna valutazione finora

- FlipflopsDocumento80 pagineFlipflopsvikramkolanuNessuna valutazione finora

- STA FinalDocumento66 pagineSTA FinalgauravkshriNessuna valutazione finora

- Lacthes and FlipflopsDocumento30 pagineLacthes and FlipflopsNaveen KumarNessuna valutazione finora

- 05 SeqDocumento46 pagine05 SeqRenju TjNessuna valutazione finora

- Presentation 1Documento33 paginePresentation 1Satyajit GantayatNessuna valutazione finora

- 6 111 l4 Seqntl BlocksDocumento24 pagine6 111 l4 Seqntl BlocksysakeunNessuna valutazione finora

- Chp1 - Latches and Flip-FlopsDocumento44 pagineChp1 - Latches and Flip-FlopsAbnen OngNessuna valutazione finora

- Sequential Circuit AnalysisDocumento13 pagineSequential Circuit AnalysismankindaNessuna valutazione finora

- Logic Circuits and Switching Theory: Engr. Kresil Joy P. Jimenez, ECE, MSEEDocumento28 pagineLogic Circuits and Switching Theory: Engr. Kresil Joy P. Jimenez, ECE, MSEEAutumnNessuna valutazione finora

- Sequential CircuitsDocumento22 pagineSequential CircuitsBaeNessuna valutazione finora

- Chapter 6: Sequential Logics: IntroductionDocumento49 pagineChapter 6: Sequential Logics: IntroductionAffo AlexNessuna valutazione finora

- Enel3de IntrosequentialcircuitsDocumento49 pagineEnel3de IntrosequentialcircuitsZamani MhlongoNessuna valutazione finora

- Notes 326 Set8Documento16 pagineNotes 326 Set8Bakshi AmitNessuna valutazione finora

- Chapter5 Synchronous Sequential LogicDocumento24 pagineChapter5 Synchronous Sequential Logicz45eNessuna valutazione finora

- CS1104 - Computer Organization: Aaron Tan Tuck ChoyDocumento30 pagineCS1104 - Computer Organization: Aaron Tan Tuck ChoyTaye ToluNessuna valutazione finora

- CB 2 CleDocumento4 pagineCB 2 CleJosé Antonio Montanares ZambranoNessuna valutazione finora

- Static Timing Analysis-1Documento58 pagineStatic Timing Analysis-1Pooja selvamNessuna valutazione finora

- cs1104 11Documento30 paginecs1104 11sansureNessuna valutazione finora

- Sequential Circuits: Presented By: Group 3Documento30 pagineSequential Circuits: Presented By: Group 3Jalaj SrivastavaNessuna valutazione finora

- Timing Issues in Digital ASIC DesignDocumento101 pagineTiming Issues in Digital ASIC Designnsai_vs1513Nessuna valutazione finora

- ECE465 Lecture Notes # 11 Clocking Methodologies: Shantanu Dutt UICDocumento21 pagineECE465 Lecture Notes # 11 Clocking Methodologies: Shantanu Dutt UICMohammed El-AdawyNessuna valutazione finora

- Chaptor 06Documento65 pagineChaptor 06Kaustav DasNessuna valutazione finora

- Cpe358/Cs381 Switching Theory and Logical Design Class 13Documento53 pagineCpe358/Cs381 Switching Theory and Logical Design Class 13Santhi SriNessuna valutazione finora

- ECEG3101-LC-Lec - 10 - Latches Flip Flops-1Documento31 pagineECEG3101-LC-Lec - 10 - Latches Flip Flops-1Tsinat WondimuNessuna valutazione finora

- Synchronous Sequential LogicDocumento69 pagineSynchronous Sequential Logic魏延任Nessuna valutazione finora

- Module 3: Flip FlopsDocumento34 pagineModule 3: Flip FlopsDevika UNessuna valutazione finora

- EET206 M4 Ktunotes - inDocumento195 pagineEET206 M4 Ktunotes - inKhaled AlshurmanNessuna valutazione finora

- Sequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos TatasDocumento22 pagineSequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos Tatasvikramkolanu100% (2)

- VLSI Testing - DFT and ScanDocumento35 pagineVLSI Testing - DFT and ScanAbdul RasheedNessuna valutazione finora

- Cse477-17 StaticseqDocumento33 pagineCse477-17 StaticseqHitesh GahlawatNessuna valutazione finora

- MD. Shybur Rahaman - 1811099 - EEE232L - Lab - Report - 5Documento17 pagineMD. Shybur Rahaman - 1811099 - EEE232L - Lab - Report - 5shyburrahaman120Nessuna valutazione finora

- cs302 Short Notes and Subjetive Paper For MidtermDocumento52 paginecs302 Short Notes and Subjetive Paper For MidtermchashmanmuneerNessuna valutazione finora

- Lab Session # 7 Flip-Flops: Figure 1: Block Diagram of A Sequential CircuitDocumento9 pagineLab Session # 7 Flip-Flops: Figure 1: Block Diagram of A Sequential CircuitAhmad M. HammadNessuna valutazione finora

- Static Timing Analysis: - RoshanDocumento60 pagineStatic Timing Analysis: - Roshanmani krishna yakkatiNessuna valutazione finora

- FF and LDocumento30 pagineFF and LRaja BenitaNessuna valutazione finora

- Flip FlopsDocumento25 pagineFlip FlopsNagul MeeraNessuna valutazione finora

- Report 1 (D2, Digital)Documento10 pagineReport 1 (D2, Digital)Kian YingNessuna valutazione finora

- Basic Electronics Flop FlopsDocumento9 pagineBasic Electronics Flop FlopsMegha SaranNessuna valutazione finora

- Latches and Flip-Flops: Experiment E10Documento9 pagineLatches and Flip-Flops: Experiment E10Resy ApolinarioNessuna valutazione finora

- Unit-1 - Digital ElectronicsDocumento50 pagineUnit-1 - Digital ElectronicsVignesh VigneshNessuna valutazione finora

- MemorendumDocumento1 paginaMemorendumAb Imo Pectore EvanNessuna valutazione finora

- DraftDocumento10 pagineDraftAb Imo Pectore EvanNessuna valutazione finora

- Reality Doesnt Exist UnlessDocumento26 pagineReality Doesnt Exist UnlessAb Imo Pectore EvanNessuna valutazione finora

- Nectario - Juan Colon Alias Cristobal Colon Alias Christopher Columbus Was A Spanish Jew (1971) PDFDocumento27 pagineNectario - Juan Colon Alias Cristobal Colon Alias Christopher Columbus Was A Spanish Jew (1971) PDFwroueaweNessuna valutazione finora

- SDFSFDocumento2 pagineSDFSFAb Imo Pectore EvanNessuna valutazione finora

- Script 1Documento3 pagineScript 1Ab Imo Pectore EvanNessuna valutazione finora

- Was Sich Aus Dem Streit Der Gegensätze Ergab: How Revivalist Preachers WorkDocumento4 pagineWas Sich Aus Dem Streit Der Gegensätze Ergab: How Revivalist Preachers WorkAb Imo Pectore EvanNessuna valutazione finora

- Lysergic Acid DiethylamideDocumento1 paginaLysergic Acid DiethylamideAb Imo Pectore EvanNessuna valutazione finora

- Nokia 3Documento1 paginaNokia 3Ab Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- Your More Than Your Genes You're Your ConnectomeDocumento1 paginaYour More Than Your Genes You're Your ConnectomeAb Imo Pectore EvanNessuna valutazione finora

- Nokia 3Documento1 paginaNokia 3Ab Imo Pectore EvanNessuna valutazione finora

- Nokia 3Documento1 paginaNokia 3Ab Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- It Is It NowDocumento2 pagineIt Is It NowAb Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- Bring em UpDocumento1 paginaBring em UpAb Imo Pectore EvanNessuna valutazione finora

- Tasjil ErkamDocumento4 pagineTasjil ErkamAb Imo Pectore EvanNessuna valutazione finora

- Clear This OutDocumento1 paginaClear This OutAb Imo Pectore EvanNessuna valutazione finora

- Pod Slurping An Easy Technique For Stealing DataDocumento7 paginePod Slurping An Easy Technique For Stealing DataAb Imo Pectore EvanNessuna valutazione finora

- 2007islamforum - Israel Hezb WarDocumento35 pagine2007islamforum - Israel Hezb WarAb Imo Pectore EvanNessuna valutazione finora

- It Is It NowDocumento2 pagineIt Is It NowAb Imo Pectore EvanNessuna valutazione finora

- Flick It OnDocumento1 paginaFlick It OnAb Imo Pectore EvanNessuna valutazione finora

- NPR StationsDocumento4 pagineNPR StationsGeorge DumitruNessuna valutazione finora

- De KalbDocumento1 paginaDe KalbAb Imo Pectore EvanNessuna valutazione finora