Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

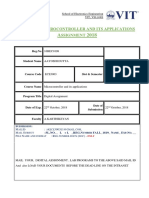

CMOS Inverter and Gates Layout in Microwind

Caricato da

nagarjun3802Descrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

CMOS Inverter and Gates Layout in Microwind

Caricato da

nagarjun3802Copyright:

Formati disponibili

Table of Contents

2. CMOS 90n micron Technology Inverter Characteristics and Layout in Microwind

3 . Layout of Basic Gates and a Complex Gate using CMOS 90n micron Technology in

Microwind.

4 . Layout of XOR and XNOR Gates using CMOS 90n micron Technology in Microwind.

7. Design and implementation of Layout of 1-Bit Full Adder using CMOS 90n micron

Technology in Microwind.

8. Design and implementation of Layout of D Latch in CMOS 90n micron Technology in

Microwind.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

EXPERIMENT-2

“CMOS Inverter Characteristics and Layout in Micro wind”

1. Objective

In this lab students will design and implement a CMOS Inverter. Different design Parameter’s

effects like transistor sizing, supply voltages etc well be analyzed and delay, area, power and currents

will be observed. This lab assumed that students are familiar with MicroWind and Lambda based

design rules. The tool used in this lab is MicroWind. The goals for this Lab are:

• Design of CMOS Inverter and transistor sizing.

• Layout Design using the tool.

• Gate delay, area, power and current analysis and the effects of transistor sizing on these parameters.

2. Theory

2.1 MOSFET

The Metal Oxide Semiconductor Field Effect Transistor is very important part of Digital Integrated

Circuits. It is mostly used as switch in digital design. MOSFET is a four terminal device. The voltage

applied to the gate terminal determine the current flow between drain and source terminals. The

body/substrate of the transistor is the fourth terminal. Mostly the fourth terminal (body/substrate) of

the device is connected to dc supply that is identical for all devices of the same type (GND fro nMOS

and Vdd for pMOS). Usually this terminal is not shown on the schematics

2.2 nMOS

The nMOS transistor consists of n+ drain and source diffusion regions, which are embedded in a p-

type substrate. The electrons in the channel beneath the gate between source and drain terminal are

responsible for the current flow.

2.3 pMOS

The pMOS transistor consists of p+ drain and source diffusion regions, which are embedded in an n-

type substrate. The holes in the channel beneath the gate between source and drain terminal are

responsible for the current flow.

2.4 CMOS

CMOS Inverter/NOT gate is considered to be the heart of VLSI circuits, based on the understanding

of NOT gate we can extend it easily to NAND and NOR gates which are VLSI Design the basic

building blocks of more complex circuits e.g. multipliers and microprocessors. As per discussion and

design on white board in the Lab, a NOT gate can be implemented using two FETs i.e. a pFET and

an nFET both connected in series, in which Vdd is supplied to pFET and nFET is grounded, input x

is applied to the gate terminals of both and the output is obtained at node y.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

3. Design/ Diagram/Circuit :

Symbol, Truth Table and CMOS circuit of NOT Gate:

4. Lab Instructions :

a. Open MicroWind and select the foundry cmos90n.

b. Save the design as “Save as” as “file name”, and save the design frequently during the lab session.

c. Draw the layout of nMOS using MOS Generator

d. Draw the layout of pMOS using MOS Generator by setting the appropriate width of pMOS

e. Connect the two transistors using Metal 1as per diagram.

f. Draw the rails of Vdd and Gnd above and below.

g. Connect the n well with Vdd.

h. Add input and output to your design.

i. Save the layout.

j. Apply design rule checker.

k. Simulate the design using run Command.

l. Analyze configuration delay, gate delay, current, power, and midpoint voltage.

m. Repeat the design for different values .

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

Inverter symbol in microwind Layout

Running simulation 1

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

Running Simulation 2

Running Simulation 3

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

EXPERIMENT-3

“Layout of Universal Gates using 0.25 micron Technology in Microwind”

1. Objective:

In this lab students will design and implement the layouts of different CMOS gates, which includes

NAND, NOR. The tool used in this lab is Microwind. The goals for this Lab are:

1. Design of CMOS NAND and NOR Gate.

2. Layout Design using the tool.

3.Gate delay, area, power and current analysis and the effects of transistor sizing on these parameters.

2. Theory :

2.1 NAND Gate

As per discussion and design on white board in the Lab, a NAND gate can be implemented using

four FETS i.e. two pFETs and two nFETs as the inputs of the gate is two. pFETs are connected in

parallel while nFETs are connected in series, Vdd is supplied to the parallel combination of pFETs

while the series combination of nFETs is grounded. Inputs a & b are applied to the gate terminals of

all FETs, and the output f is obtained from the common junction of these series and parallel

combinations as illustrated in NAND circuit under the heading of Design Diagram / Circuit.

2.2 NOR Gate

As per discussion and design on white board in the Lab, A NOR Gate can be implemented using

fours FETS i.e two pFETs and two nFETs as the inputs of the gate is two. pFETs are connected in

series while nFETs are connected in parallel, Vdd is supplied to the series combination of pFETs

while the parallel combination of nFETs is grounded. Inputs a & b are applied to the gate terminals

of all FETs, and the output f is obtained from the common junction of these parallel and series

combinations as

3. Design /Diagram/Circuit:

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

4. Lab Instructions

1. Open Microwind and select the foundry cmos90n

2. Save the design as “Save as” as “Lab05”, and save the design frequently during the lab

session.

3. Draw the layout of nMOS using MOS Generator.

4. Draw the layout of pMOS using MOS Generator by setting the appropriate width of pMOS

5. Connect the transistors using Metal 1 as per design.

6. Draw the rails of and ground rails above and below. DD V

7. Connect the nWell to DD V

8. Check the design using DRC for any design rule violation and correct the design in case of

error, again run the DRC and check for errors. Or run the DRC after each change in the layout.

9. Check for Electrical connections to be valid.

10. Add inputs and outputs to the design; also add virtual capacitance at the output in your

design.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

11. Simulate the Design. Observe the values of configuration delay, gate delay, power, current,

VTC, and area.

12. Repeat the design using for different values of transistor’s dimensions, supply voltages. And

observe the changes in configuration delay, gate delay, power, current, VTC, and area carefully.

NAND Gate using Metal 3 for inputs, Metal 2 for Vdd and Gnd, and Metal 1 for diffusion

interconnection and CMOS90n micron process .

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

Simulating the NOR gate

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

EXPERIMENT-4

“XOR and XNOR Gates using CMOS micron Technology in Microwind”

1.Objective: Layout of XOR and XNOR Gates using CMOS 0.25 micron Technology in

Microwind.In this lab students will design and implement the layouts of XOR and XNOR

GateS. The tool used in this lab is Microwind. The tasks given in the lab include,

• Design of XOR and XNOR Gates.

• Layout Design using the tool.

• Gate delay, area, power and current analysis and the effects of transistor sizing on these

parameters.

2.Theory:

Schematic for CMOS Xor Gate

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

EXPERIMENT-5

“Design and Implementation of Full Adder at Layout Level in Microwind”

1. Objective:

In this lab students will design and implement the layout of a CMOS Full Adder. Delay, area,

power and currents of Full Adder will be observed. This lab assumed that students are

familiar with Microwind and Lambda based design rules. The tool used in this lab is

Microwind. The goals for this Lab are:

1. Design of CMOS Full Adder Layout.

2. Layout Design using the tool.

3. Gate delay, area, power and current analysis

2. Theory : CMOS Full Adder

A Full Adder is an important building block of arithmetic circuits in a system. Full adder

accepts three inputs and produces the outputs sum and carry by adding the binary bits with

the help of logic gates. The Full Adder can be optimized using XOR and NAND Gates only in

the following way.

3. Design Diagram / Circuit:

Full Adder using gate circuit

There are many ways to construct the XOR schematic e.g. using expression, using

Transmission gate. We will construct the schematic in the following way. From the table of

XOR Gate.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

The XOR can be read from the Table as follows: IF B=0, OUT=A, IF B=1, OUT=Inv (A). The

principle of the circuit presented below is to enable the A signal to flow to node W1 if B=1

and to enable Inv (A) the signal to flow to node W1 if B=0. The output inverts the node W1

so that we can get the XOR operator.

Schematic of XOR Gate

Layout of XOR Gate

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

4. Lab Instructions:

1. Open Microwind and select the foundry cmos90n

2. Save the design as “Save as” as “Lab05”, and save the design frequently during the lab

session.

3. Draw the layout of nMOS using MOS Generator

4. Draw the layout of pMOS using MOS Generator by setting the appropriate width of

pMOS

5. Connect the transistors using Metal 1 as per design.

6. Draw the rails of DD V and ground rails above and below.

7. Connect the nWell to Vdd.

8. Check the design using DRC for any design rule violation and correct the design in case of

error, again run the DRC and check for errors. Or run the DRC after each change in the

layout.

9. Check for Electrical connections to be valid.

10. Add inputs and outputs to the design; also add virtual capacitance at the output in your

design.

11. Simulate the Design. Observe the values of configuration delay, gate delay,power,

current, VTC, and area.

12. Repeat the design using for different values of transistor’s dimensions, supply voltages.

And observe the changes in configuration delay, gate delay, power, current, VTC, and area

carefully. Make a conclusion of your observations.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

EXPERIMENT-6

“Layout of a Complex gate using 90n micron Technology in MicroWind”

1. Objective

In this lab students will design and implement the layouts of a complex CMOS gate.

The tool used in this lab is MicroWind. The goals for this Lab are:

1.Design of CMOS Complex Gate.

2. Layout Design using the tool.

3. Gate delay, area, power and current analysis and the effects of transistor sizing on these

parameters.

2. Theory

2.1 Complex Gate

The expression for the complex gate is given as under

F=(AD+B(CD+A))`.

As per discussion and design on white board in the Lab, this complex gate can be implemented as

under For pFETs Array

Group1: Two pFETs with inputs “c” & “d” at its gate terminals are connected in parallel.

Group2: A pFET with input “a” at its gate terminal is in series with Group1.

Group3: A pFET with input “b” at its gate terminal is parallel to Group1-Group2.

Group4: Two pFETs with inputs “a” and “d” are in parallel and is connected in series with Group1-

Group2-Group3

For nFETs Array

Group1: Two nFETs with inputs “c” & “d” at its gate terminals are connected in series.

Group2: An nFET with input “a” at its gate terminal is in parallel with Group1.

Group3: An nFET with input “b” at its gate terminal is in seies to Group1- Group2.

Group4: Two nFETs with inputs “a” and “d” are in series and is connected in parallel with Group1-

Group2-Group3.

3. Design Diagram / Circuit:

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

4. Lab Instructions:

1. Open MicroWind and select the foundry cmos025

2. Save the design as “Save as” as “Lab04”, and save the design frequently

during the lab session.

3. Draw the layout of nMOS using MOS Generator

4. Draw the layout of pMOS using MOS Generator by setting the appropriate

width of pMOS

5. Connect the transistors using Metal 1 as per design.

6. Draw the rails of DD V and ground rails above and below.

7. Connect the nWell to DD V

8. Check the design using DRC for any design rule violation and correct the

design in case of error, again run the DRC and check for errors. Or run the DRC after each

change in the layout.

9. Check for Electrical connections to be valid.

10. Add inputs and outputs to the design; also add virtual capacitance at the output in your

design.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

11. Simulate the Design. Observe the values of configuration delay, gate delay, power,

current, VTC, and area.

12. Repeat the design using for different values of transistor’s dimensions, supply voltages.

And observe the changes in configuration delay, gate delay, power, current, VTC, and area

carefully. Make a conclusion of your observations.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

EXPERIMENT-7

“Layout of Multiplexer, Demultiplexer using CMOS 90n micron Technology in

Microwind”.

Objective: In this lab students will design and implement the layouts of Multiplexer,

Demultiplexer. The tool used in this lab is Microwind.

The tasks given in lab include:

• Design of Multiplexer, Demultiplexer.

• Layout Design using the tool.

• Gate delay, area, power and current analysis and the effects of

transistor sizing on these parameters.

Tools used: Microwind

Theory:

Multiplexor

Generally speaking, a multiplexor is used to transmit a large amount of information through

a smaller number of connections. A digital multiplexor is a circuit that selects binary

information from one of many input logic signals and directs it to a single input

line. A behavioral description of the multiplexor is the case statement:

The usual symbol for the multiplexor is given in figure . It consists of the two multiplexed

inputs in0 and in1 on the left side, the command sel at the bottom of the symbol, and the

output f on the right.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

Design of the Multiplexor:

Or

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

Design of Demultiplexor:

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

Task1: Design the layout of 2-to-1 Mux, Simulate the Design. Observe the values of

configuration delay, gate delay, power, current, VTC, and area

Task2: Design the layout of 1-to-2 deMux by using the three different methodsas explained

on the white board, Simulate the Design. Observe the values of configuration delay, gate

delay, power, current, VTC, and area.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

EXPERIMENT-8

“Design and implementation of Layout of Latch in CMOS 0.25 micron Technology

in Microwind”.

Objective: In this lab students will design and implement the layouts of Latch. Delay, area,

power and currents of Latch, Dreg, Clock Divider will be observed. The tool used in this lab

is Microwind.

The tasks given in lab include:

• Design of CMOS Latch layout.

• Layout Design using the tool.

• Gate delay, area, power and current analysis and the effects of transistor sizing on these

parameters.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

Theory:

CMOS CIRCUIT FOR D LATCH:

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

OR

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

EXPERIMENT-9

“Layout of Logic Gates using 90n micron Technology in Microwind”

1. Objective:

In this lab students will design and implement the layouts of different CMOS gates, which includes

AND,OR. The tool used in this lab is Microwind. The goals for this Lab are:

1. Design of CMOS AND and OR Gate.

2. Layout Design using the tool.

3.Gate delay, area, power and current analysis and the effects of transistor sizing on these parameters.

2. Theory :

2.1 AND Gate

As per discussion and design on white board in the Lab, a AND gate can be implemented using four

FETS i.e. two pFETs and two nFETs as the inputs of the gate is two. pFETs are connected in parallel

while nFETs are connected in series, Vdd is supplied to the parallel combination of pFETs while the

series combination of nFETs is grounded. Inputs a & b are applied to the gate terminals of all FETs,

and the output f is obtained from the common junction of these series and parallel combinations as

illustrated in AND circuit under the heading of Design Diagram / Circuit.

2.2OR Gate

As per discussion and design on white board in the Lab, A OR Gate can be implemented using fours

FETS i.e two pFETs and two nFETs as the inputs of the gate is two. pFETs are connected in series

while nFETs are connected in parallel, Vdd is supplied to the series combination of pFETs while the

parallel combination of nFETs is grounded. Inputs a & b are applied to the gate terminals of all

FETs, and the output f is obtained from the common junction of these parallel and series

combinations as

3. Design /Diagram/Circuit:

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

4. Lab Instructions

1. Open Microwind and select the foundry cmos90n

2. Save the design as “Save as” as “Lab05”, and save the design frequently during the lab

session.

3. Draw the layout of nMOS using MOS Generator.

4. Draw the layout of pMOS using MOS Generator by setting the appropriate width of pMOS

5. Connect the transistors using Metal 1 as per design.

6. Draw the rails of and ground rails above and below Vdd

7. Connect the nWell to Vdd

8. Check the design using DRC for any design rule violation and correct the design in case of

error, again run the DRC and check for errors. Or run the DRC after each change in the layout.

9. Check for Electrical connections to be valid.

10. Add inputs and outputs to the design; also add virtual capacitance at the output in your

design.

11. Simulate the Design. Observe the values of configuration delay, gate delay, power, current,

VTC, and area.

12. Repeat the design using for different values of transistor’s dimensions, supply voltages. And

observe the changes in configuration delay, gate delay, power, current, VTC, and area carefully.

VLSI LAB MANUAL BY B. SRILAKSHMI(ECE)

Potrebbero piacerti anche

- Objective: " Layout of Basic Gates Using 0.25 Micron Technology in Microwind"Documento7 pagineObjective: " Layout of Basic Gates Using 0.25 Micron Technology in Microwind"unity123d deew100% (1)

- Objective: "CMOS 0.25 Micron Technology Inverter Characteristics and Layout in Microwind"Documento6 pagineObjective: "CMOS 0.25 Micron Technology Inverter Characteristics and Layout in Microwind"unity123d deew100% (1)

- Optimal Design of A Reversible Full AdderDocumento17 pagineOptimal Design of A Reversible Full AdderMohamedNessuna valutazione finora

- Lab # 01: Introduction To Basic Logic Gate Ic's On Digital Logic Trainer and Proteus Simulation in LabDocumento10 pagineLab # 01: Introduction To Basic Logic Gate Ic's On Digital Logic Trainer and Proteus Simulation in Labearn moneyNessuna valutazione finora

- DLD 5 Lab ReportsDocumento25 pagineDLD 5 Lab ReportsHamza Shah100% (1)

- Detecting and Correcting Errors in CodesDocumento4 pagineDetecting and Correcting Errors in CodesStephenPengNessuna valutazione finora

- Chapter SixDocumento5 pagineChapter Sixyunus memonNessuna valutazione finora

- To Make A DC Switching Circuit Using SCR'sDocumento2 pagineTo Make A DC Switching Circuit Using SCR'sH Aries OñaNessuna valutazione finora

- NPCIL Electronics PaperDocumento9 pagineNPCIL Electronics Papernetcity143Nessuna valutazione finora

- LIC Lecture 3-Current Sources As Active Loads and Voltage Sources MaterialsDocumento4 pagineLIC Lecture 3-Current Sources As Active Loads and Voltage Sources MaterialsMadhavan SamNessuna valutazione finora

- 2016 Ch1-Intro PDFDocumento16 pagine2016 Ch1-Intro PDFTrần Anh TânNessuna valutazione finora

- NMOS and CMOS Design Style With ExamplesDocumento9 pagineNMOS and CMOS Design Style With ExamplesHIMA BINDU0% (1)

- Optical Fiber Transmission Link ElementsDocumento15 pagineOptical Fiber Transmission Link ElementsAchu0% (1)

- Design, Fabrication and Testing of Analog IC AmplifiersDocumento17 pagineDesign, Fabrication and Testing of Analog IC AmplifiersNurul Hanim HashimNessuna valutazione finora

- Chapter 5 Problems CMOS INVERTERDocumento8 pagineChapter 5 Problems CMOS INVERTERShykh SheharyarNessuna valutazione finora

- ECE 438 Assignment 5 - CMOS Logic GatesDocumento9 pagineECE 438 Assignment 5 - CMOS Logic GatesluqmansulymanNessuna valutazione finora

- CMOS Design RulesDocumento21 pagineCMOS Design Rulesrakheep123Nessuna valutazione finora

- DEL ManualDocumento94 pagineDEL ManualAnand BongirNessuna valutazione finora

- Fpga ManualDocumento7 pagineFpga ManualRahul SharmaNessuna valutazione finora

- EMT Assignment 5Documento15 pagineEMT Assignment 5Kelvin KohNessuna valutazione finora

- Introduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)Documento27 pagineIntroduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)TygerYashanshuNessuna valutazione finora

- Cmos LayoutDocumento13 pagineCmos LayoutshastryNessuna valutazione finora

- Advanced Topologiesand TechnologyDocumento34 pagineAdvanced Topologiesand TechnologylakshmiraniNessuna valutazione finora

- Ecl 203 MCQDocumento3 pagineEcl 203 MCQresham k vNessuna valutazione finora

- Microprocessor and Architecture Solution PDFDocumento23 pagineMicroprocessor and Architecture Solution PDFKarmaveer Bhaurao Patil CollegeNessuna valutazione finora

- PMOS, NMOS and CMOS Transmission Gate Characteristics.Documento13 paginePMOS, NMOS and CMOS Transmission Gate Characteristics.Prajwal KhairnarNessuna valutazione finora

- 16-Bit Low Power ALUDocumento10 pagine16-Bit Low Power ALUManu KashyapNessuna valutazione finora

- Lecture 3Documento37 pagineLecture 3James MarshallNessuna valutazione finora

- Energy MeterDocumento11 pagineEnergy MeterRushab SirsatNessuna valutazione finora

- Design of 12-Bit DAC Using CMOS TechnologyDocumento5 pagineDesign of 12-Bit DAC Using CMOS TechnologysanthoshNessuna valutazione finora

- VLSI Lab Part B SolutionsDocumento40 pagineVLSI Lab Part B SolutionsNandiniManinarayanaNessuna valutazione finora

- Microcontroller Lab Manual PDFDocumento61 pagineMicrocontroller Lab Manual PDFManoj SkNessuna valutazione finora

- ASAP7 TutorialDocumento52 pagineASAP7 TutorialAtmadeep DeyNessuna valutazione finora

- Microprocessor All Experiment IT PDFDocumento22 pagineMicroprocessor All Experiment IT PDFSuraj KumarNessuna valutazione finora

- Exercises For Chapter 2Documento1 paginaExercises For Chapter 2Khổng Xuân TrungNessuna valutazione finora

- Cmos Two Stage OpamppublishedDocumento5 pagineCmos Two Stage Opamppublisheddeepak pandeyNessuna valutazione finora

- DOST-ASTI Electric Manual PDFDocumento17 pagineDOST-ASTI Electric Manual PDFJB NavarroNessuna valutazione finora

- MIM Cap ModelDocumento4 pagineMIM Cap ModelDuc DucNessuna valutazione finora

- Adders and MultipliersDocumento59 pagineAdders and Multipliersdbanbumani_501791840Nessuna valutazione finora

- Question PDFDocumento12 pagineQuestion PDFjushwanth100% (1)

- ST2611 PDFDocumento1 paginaST2611 PDFROHITCHOURASIYANessuna valutazione finora

- Twin T NetworkDocumento2 pagineTwin T NetworkVijayalakshmi PrakashNessuna valutazione finora

- Digital Integrated Circuits: A Design PerspectiveDocumento113 pagineDigital Integrated Circuits: A Design Perspectiveapi-127299018Nessuna valutazione finora

- Diffusion in VLSIDocumento21 pagineDiffusion in VLSI12user123100% (5)

- Code Converters, Multiplexers and DemultiplexersDocumento36 pagineCode Converters, Multiplexers and DemultiplexersJohn Oneil F. Quiambao0% (1)

- Interfacing 8253 Timer with 8085 MicroprocessorDocumento2 pagineInterfacing 8253 Timer with 8085 Microprocessormohan100% (1)

- Lic Unit 2 Digital NotesDocumento157 pagineLic Unit 2 Digital NoteslyrixxopediaNessuna valutazione finora

- P23. Mapping of Course Outcome With Program OutcomesDocumento31 pagineP23. Mapping of Course Outcome With Program OutcomesBhaskar MondalNessuna valutazione finora

- Industrial Protection Over Smoke Temperature and LDRDocumento58 pagineIndustrial Protection Over Smoke Temperature and LDRPradeep Avanigadda100% (2)

- 1-Introduction To Semiconductor MaterialsDocumento43 pagine1-Introduction To Semiconductor MaterialsStevie AdrielNessuna valutazione finora

- Interfacing Programs For 8085Documento37 pagineInterfacing Programs For 8085archankumarturagaNessuna valutazione finora

- 10.4.4 Lab - Build A Switch and Router NetworkDocumento5 pagine10.4.4 Lab - Build A Switch and Router NetworkJesus NoyolaNessuna valutazione finora

- 8051 Vs Motorola 68HC11Documento19 pagine8051 Vs Motorola 68HC11zuanne83Nessuna valutazione finora

- Understanding About CMOS Fabrication TechnologyDocumento4 pagineUnderstanding About CMOS Fabrication TechnologyJayesh RaghuwanshiNessuna valutazione finora

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentDocumento43 pagineECE3003 M A 2018: Icrocontroller and Its Applications SsignmentAayoshi DuttaNessuna valutazione finora

- Why VLSI? - Moore's Law. - The VLSI Design ProcessDocumento28 pagineWhy VLSI? - Moore's Law. - The VLSI Design Processlim hyNessuna valutazione finora

- Virtual Labs Presentation IITDocumento26 pagineVirtual Labs Presentation IITDr-Eng Imad ShaheenNessuna valutazione finora

- Modelling & Simulation of BJT Device ModelsDocumento29 pagineModelling & Simulation of BJT Device ModelsvanithapremkumarNessuna valutazione finora

- Enclosure Form of SegregationDocumento18 pagineEnclosure Form of Segregationkkn1234Nessuna valutazione finora

- Chapter 15 - Magnetic PropertiesDocumento10 pagineChapter 15 - Magnetic PropertiesThành Phương TấnNessuna valutazione finora

- 307 - Three Way Intrinsic SafeDocumento2 pagine307 - Three Way Intrinsic SaferajfmcNessuna valutazione finora

- Esquemas y Planos Celdas MT PV Uyuni 8DAB-47925 - SwgGra - 20170125184905Documento3 pagineEsquemas y Planos Celdas MT PV Uyuni 8DAB-47925 - SwgGra - 20170125184905Operaciones YJJNessuna valutazione finora

- Electromagnetic Fields and Waves: Lecture Notes OnDocumento145 pagineElectromagnetic Fields and Waves: Lecture Notes OnSaswat RaysamantNessuna valutazione finora

- Magnetostriction, Barkhausen Noise and Magnetization Processes in Non-Electrical Steels PDFDocumento9 pagineMagnetostriction, Barkhausen Noise and Magnetization Processes in Non-Electrical Steels PDFallanromarioNessuna valutazione finora

- Lab Report On The Working of RelayDocumento4 pagineLab Report On The Working of RelayHira IqbalNessuna valutazione finora

- Istar Edge Install Quick Start Guide Ra3 - LT - enDocumento26 pagineIstar Edge Install Quick Start Guide Ra3 - LT - enJose ElenilsonNessuna valutazione finora

- 3 Channel Spectrum AnalyzerDocumento2 pagine3 Channel Spectrum AnalyzerJack PaneNessuna valutazione finora

- 500 GTP 1180Documento2 pagine500 GTP 1180mahidhar talapaneniNessuna valutazione finora

- 06 - Test Format For Insulation ResistanceDocumento1 pagina06 - Test Format For Insulation ResistanceGajendran Sriram100% (1)

- Accessory Cable GuideDocumento9 pagineAccessory Cable GuideCarmelo BayonNessuna valutazione finora

- Alexander CH 01 Final R1Documento31 pagineAlexander CH 01 Final R1YeabsiraNessuna valutazione finora

- Service Notes: Issued by RJADocumento15 pagineService Notes: Issued by RJAcarlosNessuna valutazione finora

- Eetop - CN - Chapter 7 CMOS ComparatorDocumento38 pagineEetop - CN - Chapter 7 CMOS Comparatorshuhaoyi5Nessuna valutazione finora

- Principles of Operation Principle of High-Frequency Oscillation Type Inductive Proximity SensorDocumento9 paginePrinciples of Operation Principle of High-Frequency Oscillation Type Inductive Proximity SensorRanaIfteeNessuna valutazione finora

- Waynekerr4235 User ManualDocumento123 pagineWaynekerr4235 User ManualTrần Hồng Văn50% (2)

- RRZZ-65B-R4N43 Product SpecificationsDocumento4 pagineRRZZ-65B-R4N43 Product SpecificationsLidia Salmeron DiazNessuna valutazione finora

- Battery Failure PredictionDocumento10 pagineBattery Failure PredictionChris Baddeley100% (1)

- LG Color TV Service ManualDocumento26 pagineLG Color TV Service ManualVadakkevalappilNessuna valutazione finora

- Accident InvestigationDocumento24 pagineAccident InvestigationdhazliNessuna valutazione finora

- DIN Fuses 7.2kV - 36kVDocumento124 pagineDIN Fuses 7.2kV - 36kVlarryNessuna valutazione finora

- Motor StartingDocumento24 pagineMotor Startingeng_mahmoud3000100% (1)

- Partial Discharge Testing For Cables: Electrical Reliability ServicesDocumento4 paginePartial Discharge Testing For Cables: Electrical Reliability ServicesTommy SiddiqNessuna valutazione finora

- 4315 ManualDocumento3 pagine4315 Manualma.betraNessuna valutazione finora

- Reactive Power Managment RPM BookletDocumento72 pagineReactive Power Managment RPM BookletPramod B.WankhadeNessuna valutazione finora

- Tutorial Optical Sources and DetectorsDocumento2 pagineTutorial Optical Sources and DetectorsMir Sameer HassanNessuna valutazione finora

- Wiring DiagramsDocumento70 pagineWiring DiagramsEmerson Fonte Dos Santos FreireNessuna valutazione finora

- Celina Mikolajczak, Michael Kahn, Kevin White, Richard Thomas Long - Lithium-Ion Batteries Hazard and Use AssessmentDocumento126 pagineCelina Mikolajczak, Michael Kahn, Kevin White, Richard Thomas Long - Lithium-Ion Batteries Hazard and Use AssessmentJuan Manuel Rodríguez GonzálezNessuna valutazione finora

- Experiment No. 5 The Wound Rotor Induction MotorDocumento8 pagineExperiment No. 5 The Wound Rotor Induction MotorJoshua DimasalangNessuna valutazione finora