Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Experiment 1

Caricato da

Jomel JomelTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Experiment 1

Caricato da

Jomel JomelCopyright:

Formati disponibili

EXPERIMENT NO.

1

GATE FAMILIARIZATION

OBJECTIVES

1. To identify the input and output terminals of a gate in an IC package.

2. To identify the supply terminals of SSI IC.

3. To determine the state of input and output terminals of SSI gates using LED.

BASIC INFORMATION

Some TTL circuits as shown in Figure 1-1. Each IC is enclosed withing a

14 ot 16 pin package. A notch placed on the left side of the package is used as

reference for the pin numbers. The pins are numbered along the two sides

starting from teh notch and continuing counterclockwise. The inputs and outputs

of the gates are connected to the package pins.

The TTL IC’s are distinguished by their numerical designation, e.g. the

5400 and 7400 series. The former has a wide temperature range is suitable for

military use, while the latter has a narrower temperature range and is suitable for

commercial use. The numerical designation of the 7400 series means that the IC

packages are numbered as 7400, 7401, 7402, etc.

The TTL logic family actually consists of several subfamilies or series.

Table 1-1 list the name of each series and the prefix designation that identifies

the IC as being part of that series. ICs that are part of the high-speed TTL series

have an identification number that starts with 74H; ICs in the Schottky TTL series

starts with 74S; and similarly for the other series.

The differences between the various TTL series are in their electrical

characteristics, e.g., power dissipation, propagation delay, and switching speed.

They do not differ in pin assignment nor on the logic operation performed by the

internal circuits. For example, all the Ics listed in Table 1-1 with an 86 number, no

matter what the prefix, contain four exclusive OR gates with the same pin

assignment in each package.

EXPERIMENT 1: GATES FAMILIARIZATION 1

Table 1-1 Various series of the TTL Logic Family

TTL Series Prefix Example

Standard TTL 74 7486

High-Speed TTL 74H 74H86

Low-Power TTL 74L 74L86

Schottky TTL 74S 74S86

Low-Power Schottky TTL 74LS 74LS86

Advanced Schottky TTL 74AS 74AS86

Advanced Low-Power Schottky 74ALS 74ALS86

TTL

MATERIALS

1 LED

1 9V Battery with connector

2 Resistor 1k ohms

1 Resistor 500 ohms

3 resistor 100 ohms

1 Protoboard / Breadboard

1 Long Nose Pliers

1 Wire Stripper Pliers

Connecting Wires (RED, BLACK, WHITE, VIOLET)

Integrated Circuits (ICs)

1 74LS00

1 74LS02

1 74LS04

1 74LS08

1 74LS32

1 74LS86

PROCEDURES

1. Examine the ICs supplied to you. The number is printed on the surface of

each IC.

74LS00, 74LS02, 74LS04, 74LS08, 74LS32 and 74LS86.

2. Connect the 74LS00 as shown in Figure 1-2. Supply the IC with 5V and

Ground.

3. Using the logic probe, test the status condition or logic level at the input and

output terminals.

4. Of each gate in the IC. Record the logic values in the corresponding tables.

5. Remove the IC mounted on the protoboard and replace it with another IC.

EXPERIMENT 1: GATES FAMILIARIZATION 2

6. Repeat step 3 for each of the other ICs.

+5V

Ground Terminal

Terminal

Figure 1-2 Experimental Circuit Set-up

EXPERIMENT 1: GATES FAMILIARIZATION 3

CIRCUIT DIAGRAMS / SCHEMETICS

14 13 12 11 10 9 8 14 13 12 11 10 9 8

Vcc Vcc

GND GND

1 2 3 4 5 6 7 1 2 3 4 5 6 7

74LS08 - Quad 2-Input AND Gate 74LS00 - Quad 2-Input NAND Gate

14 13 12 11 10 9 8 14 13 12 11 10 9 8

Vcc Vcc

GND GND

1 2 3 4 5 6 7 1 2 3 4 5 6 7

74LS32 - Quad 2-Input OR Gate 74LS86 - Quad 2-Input XOR Gate

14 13 12 11 10 9 8 14 13 12 11 10 9 8

Vcc Vcc

GND GND

1 2 3 4 5 6 7 1 2 3 4 5 6 7

74LS02 - Quad 2-Input NOR Gate 74LS04 - Hex Inverter

Figure 1-1 Basic Gates Pin Configuration

EXPERIMENT 1: GATES FAMILIARIZATION 4

DATA AND RESULTS

Table 1-1 Test Results for 74LS00 IC

Input Output

Terminals Terminals

Pin Logic Pin Logic Table 1-2 Test Results for 74LS02 IC

No. Level No. Level Input Output

1 3 Terminals Terminals

2 6 Pin Logic Pin Logic

4 8 No. Level No. Level

5 11 2 1

9 3 4

10 5 10

12 6 13

13 8

9

Table 1-3 Test Results for 74LS08 IC 11

Input Output 12

Terminals Terminals

Pin Logic Pin Logic Table 1-4 Test Results for 74LS32 IC

No. Level No. Level Input Output

1 3 Terminals Terminals

2 6 Pin Logic Pin Logic

4 8 No. Level No. Level

5 11 1 3

9 2 6

10 4 8

12 5 11

13 9

10

Table 1-5 Test Results for 74LS86 IC 12

Input Output 13

Terminals Terminals

Pin Logic Pin Logic Table 1-6 Test Results for 74LS04 IC

No. Level No. Level Input Output

1 3 Terminals Terminals

2 6 Pin Logic Pin Logic

4 8 No. Level No. Level

5 11 1 2

9 3 4

10 5 6

12 9 8

13 11 10

13 12

EXPERIMENT 1: GATES FAMILIARIZATION 5

QUESTIONS

1. What is the logical equivalent of the “hang” input? __________

2. Identify the following ICs with the same pin configuration.

3. Describe the pin configurations of 74LS02 and 74LS04 ICs.

EXPERIMENT 1: GATES FAMILIARIZATION 6

Potrebbero piacerti anche

- Experiment 1Documento12 pagineExperiment 1Jomar RosalesNessuna valutazione finora

- The Equations of The Currents in Two Parallel Connected Electric Devices Are I1Documento3 pagineThe Equations of The Currents in Two Parallel Connected Electric Devices Are I1Tim Picar100% (1)

- EM308 Lab 001 Jan15Documento7 pagineEM308 Lab 001 Jan15shakeeb mana0% (1)

- ECE 301 Electronics 1: A. Half-Wave RectificationDocumento24 pagineECE 301 Electronics 1: A. Half-Wave RectificationVince Hugo GutibNessuna valutazione finora

- Exp 1 Group 4 DraftDocumento35 pagineExp 1 Group 4 DraftJERUSHA ANNE RETARDONessuna valutazione finora

- Experiment 3,4 and 5Documento10 pagineExperiment 3,4 and 5airaNessuna valutazione finora

- Ac Single Phase First PartDocumento32 pagineAc Single Phase First PartreyiNessuna valutazione finora

- EEM328 Electronics Laboratory - Experiment 3 - Diode ApplicationsDocumento3 pagineEEM328 Electronics Laboratory - Experiment 3 - Diode Applicationsdonatello84Nessuna valutazione finora

- Diode Characteristics PDFDocumento16 pagineDiode Characteristics PDFJOECELLE ABLEGINANessuna valutazione finora

- E104 - Superposition Theorem and LinearityDocumento19 pagineE104 - Superposition Theorem and LinearityRick AlvientoNessuna valutazione finora

- Thevenin's Theorem and Maximum Power TransferDocumento26 pagineThevenin's Theorem and Maximum Power TransferNathaniel PanganibanNessuna valutazione finora

- Experiment 3 Indiv. ReportDocumento3 pagineExperiment 3 Indiv. ReportKyla Mae Arago100% (1)

- TX Line AssignmentDocumento9 pagineTX Line AssignmentShubham SarkarNessuna valutazione finora

- Series Type Voltage RegulatorDocumento4 pagineSeries Type Voltage RegulatorErika VistanNessuna valutazione finora

- Eeeb113 Circuit Analysis 1: Chapter 6: Capacitors and Inductors Sharifah Azma Syed MustaffaDocumento25 pagineEeeb113 Circuit Analysis 1: Chapter 6: Capacitors and Inductors Sharifah Azma Syed MustaffaSharifah Azma100% (1)

- ECS332 2015 Postmidterm HWDocumento69 pagineECS332 2015 Postmidterm HWDeadpool 001Nessuna valutazione finora

- Lista 5Documento22 pagineLista 5vsabioniNessuna valutazione finora

- Final Exam Part 1 StudentDocumento4 pagineFinal Exam Part 1 StudentRJ Balbedina100% (1)

- Performance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDocumento7 paginePerformance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDr-Sanjeev KashyapNessuna valutazione finora

- Batangas State University: The National Engineering UniversityDocumento14 pagineBatangas State University: The National Engineering UniversityDave SmithNessuna valutazione finora

- Exercises For Lecture 5-6-7 - SOLUTIONDocumento8 pagineExercises For Lecture 5-6-7 - SOLUTIONLam Pham Phuoc Loc100% (1)

- Laboratory 1Documento13 pagineLaboratory 1Rn NatNessuna valutazione finora

- EE-5 AC 1-PhaseDocumento15 pagineEE-5 AC 1-PhaseZen GarciaNessuna valutazione finora

- Experiment 4Documento10 pagineExperiment 4djelbouNessuna valutazione finora

- EEM328 Electronics Laboratory - Report4 - BJT BiasingDocumento4 pagineEEM328 Electronics Laboratory - Report4 - BJT Biasingdonatello84Nessuna valutazione finora

- Experiment 10: Junction Field Effect Transistor: Operation and Its Characteristic CurveDocumento6 pagineExperiment 10: Junction Field Effect Transistor: Operation and Its Characteristic CurveDan Joshua EspinaNessuna valutazione finora

- Tutorial Sheet - 9 FET BiasingDocumento1 paginaTutorial Sheet - 9 FET BiasingJatin katiyarNessuna valutazione finora

- UNIT1Documento37 pagineUNIT1Azliana Mohd Taib0% (1)

- Plates in EnerconDocumento38 paginePlates in EnerconJevan Calaque100% (1)

- Lab Manual All ExperimentDocumento62 pagineLab Manual All ExperimentLIFE of PSNessuna valutazione finora

- 02 BJTs & BJT Amplifiers-ProblemsDocumento4 pagine02 BJTs & BJT Amplifiers-ProblemsntldvlaiNessuna valutazione finora

- AC Circuits LAB 1Documento4 pagineAC Circuits LAB 1sarsm56Nessuna valutazione finora

- Diode Tutorial Sheet-1 PDFDocumento4 pagineDiode Tutorial Sheet-1 PDFjeetesh raghuvanshiNessuna valutazione finora

- Topic 1 - Electric CircuitsDocumento70 pagineTopic 1 - Electric CircuitsKavinesh AnanthanNessuna valutazione finora

- Chapter 3 Homework SolutionDocumento23 pagineChapter 3 Homework SolutionsyarifahafizahNessuna valutazione finora

- ADE Lab Manual - Analog Part PDFDocumento21 pagineADE Lab Manual - Analog Part PDFJk RinkuNessuna valutazione finora

- 8086 Pin DiagramDocumento18 pagine8086 Pin DiagramAkash MittalNessuna valutazione finora

- A Balanced Star Connected Load Takes 90 A From A Balanced 3-Phase, 4-Wire Supply. If The Fuses in The Y and B Phases Are Removed, Find The Symmetrical Components of The Line CurrentsDocumento1 paginaA Balanced Star Connected Load Takes 90 A From A Balanced 3-Phase, 4-Wire Supply. If The Fuses in The Y and B Phases Are Removed, Find The Symmetrical Components of The Line CurrentsممشطNessuna valutazione finora

- Set ADocumento5 pagineSet AgregNessuna valutazione finora

- Technological University of The Philippines: Laboratory ReportDocumento10 pagineTechnological University of The Philippines: Laboratory Reportmoy balgosNessuna valutazione finora

- Capacitors PDFDocumento84 pagineCapacitors PDFNaseerUddin100% (1)

- BJT Ac AnalysisDocumento18 pagineBJT Ac AnalysisjjeongdongieeNessuna valutazione finora

- Basic Instrument SymbolsDocumento7 pagineBasic Instrument Symbolssushant_jhawer100% (1)

- Impedance of RL Circuits: Series RL Circuits: Experiment No. 2Documento16 pagineImpedance of RL Circuits: Series RL Circuits: Experiment No. 2NicoNessuna valutazione finora

- Mdefbod Quiz 1Documento1 paginaMdefbod Quiz 1Heiro KeystrifeNessuna valutazione finora

- Tutorial 4: Measurement of R, L, C: 4.1 The Resistors in A Wheatstone Bridge Shown in The AttachedDocumento4 pagineTutorial 4: Measurement of R, L, C: 4.1 The Resistors in A Wheatstone Bridge Shown in The AttachedPc NgNessuna valutazione finora

- PTDU Lab No. 10 Study of Real Time Operation of Bus Bars Abdul Wahab Nasir (02) Bsee 16-20Documento2 paginePTDU Lab No. 10 Study of Real Time Operation of Bus Bars Abdul Wahab Nasir (02) Bsee 16-20Ali ArshadNessuna valutazione finora

- Semiconductor DiodeDocumento6 pagineSemiconductor DiodeChlarisse Dianne SanchezNessuna valutazione finora

- Gas Leakage Alarm With Power Failure SystemDocumento64 pagineGas Leakage Alarm With Power Failure Systeminfo8103Nessuna valutazione finora

- IE LAB3 MalibiranDocumento10 pagineIE LAB3 MalibiranMary Jane MalibiranNessuna valutazione finora

- Lab 7 ArtDocumento8 pagineLab 7 ArtCharles SiringanNessuna valutazione finora

- Solution of Tutorial Sheet-3 (Three Phase Networks) : Ans. Given, - Vab - 45kV, ZL (0.5 + j3), Z (4.5 + j9)Documento10 pagineSolution of Tutorial Sheet-3 (Three Phase Networks) : Ans. Given, - Vab - 45kV, ZL (0.5 + j3), Z (4.5 + j9)Shroyon100% (2)

- KCL KVL ProblemsDocumento5 pagineKCL KVL ProblemsRhemjohn Dave PitongNessuna valutazione finora

- EE21L Experiment 8Documento12 pagineEE21L Experiment 8Jian TumaliNessuna valutazione finora

- EXPERIMENT 3 4 and 5 - LINGAODocumento9 pagineEXPERIMENT 3 4 and 5 - LINGAOairaNessuna valutazione finora

- PeeDocumento8 paginePeeron villanuevaNessuna valutazione finora

- Zener Diode and Diode ApplicationDocumento62 pagineZener Diode and Diode Applicationnibar dyllanNessuna valutazione finora

- CKTS 1: Experiment No. 1Documento11 pagineCKTS 1: Experiment No. 1Andreana AmorNessuna valutazione finora

- Expt 1Documento9 pagineExpt 1PRINCESS JAMIE ARAH GALIASNessuna valutazione finora

- Egylogicl Logicl Exp 1Documento10 pagineEgylogicl Logicl Exp 1Gellie BuenaventuraNessuna valutazione finora

- Exhibit InvDocumento2 pagineExhibit InvJomel JomelNessuna valutazione finora

- QUESTIONDocumento9 pagineQUESTIONJomel JomelNessuna valutazione finora

- Lim BrochureDocumento1 paginaLim BrochureJomel JomelNessuna valutazione finora

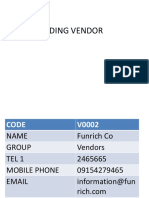

- Adding VendorDocumento4 pagineAdding VendorJomel JomelNessuna valutazione finora

- Lecture 11 - Logic Gates and Boolean (x1) PDFDocumento30 pagineLecture 11 - Logic Gates and Boolean (x1) PDFYouness Ben TibariNessuna valutazione finora

- Ground Vehicle Operations ICAODocumento31 pagineGround Vehicle Operations ICAOMohran HakimNessuna valutazione finora

- Studi Tentang Pelayanan Terhadap Kapal Perikanan Di Pelabuhan Perikanan Pantai (PPP) Tumumpa Kota ManadoDocumento9 pagineStudi Tentang Pelayanan Terhadap Kapal Perikanan Di Pelabuhan Perikanan Pantai (PPP) Tumumpa Kota ManadoAri WibowoNessuna valutazione finora

- Accommodating Expansion of Brickwork: Technical Notes 18ADocumento13 pagineAccommodating Expansion of Brickwork: Technical Notes 18AWissam AlameddineNessuna valutazione finora

- The Extension Delivery SystemDocumento10 pagineThe Extension Delivery SystemApril Jay Abacial IINessuna valutazione finora

- Century 21 South Western Accounting Answer Key Free PDF Ebook Download Century 21 South Western Accounting Answer Key Download or Read Online Ebook Century 21 SouthDocumento8 pagineCentury 21 South Western Accounting Answer Key Free PDF Ebook Download Century 21 South Western Accounting Answer Key Download or Read Online Ebook Century 21 SouthJohn0% (4)

- Labour Law Assignment - Gross NegligenceDocumento6 pagineLabour Law Assignment - Gross NegligenceOlaotse MoletsaneNessuna valutazione finora

- ZTE V4 RNC Commissioning and Integration TrainingDocumento2 pagineZTE V4 RNC Commissioning and Integration TrainingBeena SinghNessuna valutazione finora

- Addressing Diversity Through The Years Special and Inclusive EducationDocumento6 pagineAddressing Diversity Through The Years Special and Inclusive EducationJiezel SurinNessuna valutazione finora

- Malraux Anti-MemoiresDocumento9 pagineMalraux Anti-MemoiresNevenaRistićNessuna valutazione finora

- Samsung Galaxy Watch 5 Pro User ManualDocumento131 pagineSamsung Galaxy Watch 5 Pro User Manualzyron100% (1)

- FMS 427 BusinessPolicy1Documento279 pagineFMS 427 BusinessPolicy1Adeniyi Adedolapo OLanrewajuNessuna valutazione finora

- Centralized PurchasingDocumento2 pagineCentralized PurchasingbiyyamobulreddyNessuna valutazione finora

- Cambridge International AS & A Level: Biology 9700/21Documento18 pagineCambridge International AS & A Level: Biology 9700/21Lavanya EaswarNessuna valutazione finora

- Compressor-Less: Historical ApplicationsDocumento70 pagineCompressor-Less: Historical Applicationssuryakantshrotriya100% (1)

- 6000 Most Common Korean Words - For All TOPIK Levels PDFDocumento232 pagine6000 Most Common Korean Words - For All TOPIK Levels PDFZac67% (3)

- Analytical Chemistry (CHM111) Laboratory ManualDocumento73 pagineAnalytical Chemistry (CHM111) Laboratory ManualKatrina BucudNessuna valutazione finora

- Hemo TecaDocumento17 pagineHemo TecaMafer PilcoNessuna valutazione finora

- MHSS ItalyDocumento9 pagineMHSS Italyromedic36Nessuna valutazione finora

- Final FirstpartDocumento11 pagineFinal FirstpartLance Johnpaul SyNessuna valutazione finora

- Overleaf Keyboard ShortcutsDocumento2 pagineOverleaf Keyboard ShortcutsAlberto GiudiciNessuna valutazione finora

- Theory 2 - The Demand of The Society From The Teacher As A Professional (PPST)Documento6 pagineTheory 2 - The Demand of The Society From The Teacher As A Professional (PPST)Angel RodriguezNessuna valutazione finora

- Exposure: The PhotoreactionDocumento16 pagineExposure: The PhotoreactionGeetha ThiruvengadamNessuna valutazione finora

- Grade 8 - EnglishDocumento2 pagineGrade 8 - EnglishTCHR KIMNessuna valutazione finora

- Pearson Letter To ParentsDocumento2 paginePearson Letter To ParentsPatricia WillensNessuna valutazione finora

- INS2015 Fundamentals of Finance HungCV 1Documento3 pagineINS2015 Fundamentals of Finance HungCV 1Phương Anh NguyễnNessuna valutazione finora

- Chilere - Unitatile de Racire - Technical - Brochures - NX - 0152P - 0812P - EN PDFDocumento72 pagineChilere - Unitatile de Racire - Technical - Brochures - NX - 0152P - 0812P - EN PDFDaniel MilosevskiNessuna valutazione finora

- ENIRAM - Guide To Dynamic Trim Optimization 280611 PDFDocumento14 pagineENIRAM - Guide To Dynamic Trim Optimization 280611 PDFPhineas MagellanNessuna valutazione finora

- Sap Retail Two Step PricingDocumento4 pagineSap Retail Two Step PricingShams TabrezNessuna valutazione finora

- 93c3 Document 3Documento14 pagine93c3 Document 3NONON NICOLASNessuna valutazione finora

- Entropy Equation For A Control VolumeDocumento12 pagineEntropy Equation For A Control VolumenirattisaikulNessuna valutazione finora