Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

1 Self-Bias

Caricato da

Saurav ChourasiaTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

1 Self-Bias

Caricato da

Saurav ChourasiaCopyright:

Formati disponibili

Electronics Devices & Circuits Lab Manual Dept.

of Electronics & Telecommunication

Experiment No:1

TITLE: Design a single stage FET in CS configuration and verify DC operating point

OBJECTIVES: a) To find IDSS and Vp for the given JFET and plot the transfer

characterisics

b) Design a self bias circuit for a single stage JFET Amplifier

in CS Configuration and verify DC operating point.

PRE-LAB REQUISITES:

Analysis & Design of Self bias method of transistor in CS configuration

Concept of DC load line and Q-point.

APPARATUS:

Sr. No. Description Specifications

1. DC Power Supply 0-32V,2A

2. DMM (as current meter) 0-10mA dc

3. Breadboard/PCB ----------

4. DMM (as voltmeter) 0-20V dc

5. Connecting wires ---------

THEORY:

The Junction Field effect Transistor (JFET) is a voltage controlled terminal device. It

has got 3 terminals denoted as Source, Drain & Gate. For an n-channel JFET, drain and

source are n-type and gate is p- type. When a positive voltage is applied between the

drain and source, and gate is shorted to source, the pn junctions are reverse biased &

depletion regions are formed. The channel is more lightly doped than the p type gate, so

the depletion regions penetrate deeply in to the channel. As channel resistance initially

is almost constant and small, drain current I D flows. As VDD is increased, it increases.

This continues till the channel resistance becomes a high value and the current

saturates, and the channel width becomes minimum. This is known as pinch-off. The

corresponding value of VDS is called pinch off voltage Vp and the current is called as

the Drain-Source saturation current (IDSS). When the gate is biased negative with respect

to the source, and a positive voltage is applied between the drain and source, the

channel is narrowed, its resistance is increased, & I D is reduced. When the negative bias

voltage is further increased, the depletion regions meet at the center & I D is cutoff

completely. The value of VGS when ID becomes zero is the VGS(off) or –Vp.

Army Institute of Technology Page 1

Electronics Devices & Circuits Lab Manual Dept. of Electronics & Telecommunication

PROCEDURE:

Transfer Characteristics:

1. Connect the circuit as shown in the figure1.

2. Set voltage VDD to 20V.

3. Set VGS=0 and measure IDSS .

4. Varying VGG gradually, note down both drain current ID and gate-source

voltage(VGS)

5. Take readings of ID vs VGS till ID becomes zero .Note down Vp.

Fig. 1 a. : Set up to find transfer characteristics of FET

Fig. 1 .b : Transfer characteristics of JFET

Army Institute of Technology Page 2

Electronics Devices & Circuits Lab Manual Dept. of Electronics & Telecommunication

OBSERVATION TABLE

VDD= ---------- V

Sr.No VGS ID

b) Self-bias method for FET

Fig.2. CS Amplifier circuit with Self bias

Consider the common source amplifier shown in Fig 2. In self bias the gate – source is

provided by the voltage drop across a resistor in series with the device source terminal.

The voltage drop across RS is VS. The FET gate terminal is grounded with resister R G

hence VG = 0V, as IG= 0 and voltage at source terminal is more than gate so gate is

negative w. r. t. source. So for self-bias circuit

VGS= -IDRs (1)

The fact that ID determines VGS and that VGS sets the ID level means that there is a

feedback effect tending to control ID. Thus if ID increases when the device is changed,

the increased voltage across RS results in an increased gate – source voltage that tends

to lower ID back toward its original level. Similarly, a fall in I D produces a reduced VGS

which tends to raise ID toward its original level

For the output side ,

VDS= VDD-ID(RD+RS) (2)

Army Institute of Technology Page 3

Electronics Devices & Circuits Lab Manual Dept. of Electronics & Telecommunication

CIRCUIT DIAGRAM:

Fig.3 JFET self bias circuit

DESIGN:

1. Assume suitable value of IDQ .

2. Choose VDSQ = [(VDD-Vp)/2 ] +Vp

3. Assume RG= 1 MΩ

4. Find VGS corresponding to ID from Shockley’s equation:

ID = IDSS(1- VGS/Vp)2.

5. For the self-bias circuit,

VGS= -IDRs

Calculate Rs= -VGS/ID

6. Apply KVL to the output side of circuit shown in Fig2 to obtain the value of

RD

VDS= VDD-ID(RD+RS)

7. Build the self-bias circuit on breadboard and verify the designed values.

PROCEDURE:

1. Design the self-bias circuit for CS configuration. Connect circuit for dc analysis

as shown in Fig.3

2. Apply DC Supply voltage (VDD).

3. Measure the values of VDSQ, VGSQ & IDQ .

4. Compare with theoretical values.

Army Institute of Technology Page 4

Electronics Devices & Circuits Lab Manual Dept. of Electronics & Telecommunication

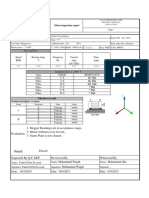

OBSERVATION TABLE

D.C.operating parameter IDQ (in mA) VDSQ (in Volt) VGSQ (in Volt)

Measured Practical

Values

Calculated

Values

DESIGN PROBLEM:

1. Design & Simulate a single Stage JFET amplifier with self bias for given Specifications

(DC Analysis) using BF245. The parameters of device are IDSS = 10mA, VP = 4V

VDD = 15V, IDQ= 4mA, VDSQ = 10V

Army Institute of Technology Page 5

Electronics Devices & Circuits Lab Manual Dept. of Electronics & Telecommunication

REFERENCES:

1. Boylstaed, Nashlesky, “Electronic Devices and Circuits Theory”, 9th Edition, PHI, 2006

2. David A. Bell, “ Electronics Devices and Circuits”, 5 th Edition Oxford press

QUESTIONS:

1. What are the different biasing circuits used for JFET?

2. Explain voltage divider bias method of JFET.

3. Define IDSS and Vp of JFET and show these parameters on the static characteristics

CONCLUSION:

Army Institute of Technology Page 6

Potrebbero piacerti anche

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesDa EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesValutazione: 4.5 su 5 stelle4.5/5 (7)

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisDa EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisNessuna valutazione finora

- Electronic Devices - Circuits Lab ManualDocumento77 pagineElectronic Devices - Circuits Lab ManualpdnkiranNessuna valutazione finora

- BK3120Documento86 pagineBK3120Isaí LemusNessuna valutazione finora

- Schneider Solar Inverter XC Series April 2012 - V2Documento2 pagineSchneider Solar Inverter XC Series April 2012 - V2Vedansh ShrivastavaNessuna valutazione finora

- Electronic Service Manual PDFDocumento110 pagineElectronic Service Manual PDFvictor50% (2)

- Chap3a - FET (v1.2)Documento70 pagineChap3a - FET (v1.2)Al AidenNessuna valutazione finora

- Maellifer CVDocumento0 pagineMaellifer CVAmit ChaudhuriNessuna valutazione finora

- 15 Small Battery Certification PDFDocumento11 pagine15 Small Battery Certification PDFdarkestmatterNessuna valutazione finora

- 1 Self-BiasDocumento6 pagine1 Self-BiasSaurav ChourasiaNessuna valutazione finora

- Design and Verify a Single Stage FET AmplifierDocumento9 pagineDesign and Verify a Single Stage FET Amplifierswapnajeet shendkarNessuna valutazione finora

- Expt 13 - JFET-CharaceristicsDocumento8 pagineExpt 13 - JFET-CharaceristicssamarthNessuna valutazione finora

- Center For Advanced Studies in Engineering, Islamabad Electronics LabDocumento9 pagineCenter For Advanced Studies in Engineering, Islamabad Electronics LabHussain HadiNessuna valutazione finora

- Expt - 11: JFET CharacteristicsDocumento8 pagineExpt - 11: JFET CharacteristicssamarthNessuna valutazione finora

- Device Exp 10Documento2 pagineDevice Exp 10Fattah AbuNessuna valutazione finora

- Exp 04Documento6 pagineExp 04ganga_ch1Nessuna valutazione finora

- Diode, BJT, Zener, MosfetDocumento10 pagineDiode, BJT, Zener, MosfetSundar Krishna MoorthyNessuna valutazione finora

- EXP10 JFET Transistor CharacteristicsDocumento5 pagineEXP10 JFET Transistor CharacteristicsMohammed Dyhia Ali100% (2)

- Electronic Devices and Circuits-Manual - August 2018Documento92 pagineElectronic Devices and Circuits-Manual - August 2018Qasim LodhiNessuna valutazione finora

- ECE 202 - Exp 1Documento4 pagineECE 202 - Exp 1Nusrat FatemaNessuna valutazione finora

- ECE 381L No1aDocumento6 pagineECE 381L No1aNakunaru GretserNessuna valutazione finora

- Experiment - 3Documento8 pagineExperiment - 3arihant gargNessuna valutazione finora

- EE Lab Manuls Fast NuDocumento88 pagineEE Lab Manuls Fast NuMuhammad SaadNessuna valutazione finora

- EEE 111 lab manual 1Documento4 pagineEEE 111 lab manual 1SHADOW manNessuna valutazione finora

- Manual Jfet and MosfetDocumento8 pagineManual Jfet and MosfetSubhadip MaityNessuna valutazione finora

- EEE206 Device Lab ManualDocumento117 pagineEEE206 Device Lab ManualGiaa RahmanNessuna valutazione finora

- EEE111+ (Exp+1) +I v+Characteristics+of+DiodeDocumento4 pagineEEE111+ (Exp+1) +I v+Characteristics+of+DiodeFaria SharifNessuna valutazione finora

- ElectronicsI Part IIIDocumento30 pagineElectronicsI Part IIIChỉnh Nguyễn ThếNessuna valutazione finora

- Experiment No.Documento56 pagineExperiment No.vishugoldy100% (1)

- Lab 6Documento2 pagineLab 6mohhassonaNessuna valutazione finora

- Exp 45Documento11 pagineExp 45tanmay sonawaneNessuna valutazione finora

- Department OF Electronics and Communication EngineeringDocumento3 pagineDepartment OF Electronics and Communication EngineeringRishi Raj KanojiaNessuna valutazione finora

- Experiment No 2 (Fet)Documento4 pagineExperiment No 2 (Fet)Jaideep SinghNessuna valutazione finora

- FSU Electronics PrelabDocumento7 pagineFSU Electronics Prelabcamaguey5Nessuna valutazione finora

- Electronic Device Lab 1 Diode CharacteristicsDocumento9 pagineElectronic Device Lab 1 Diode CharacteristicsVy NguyễnNessuna valutazione finora

- 8 Jfet Amplifying Circuits: 8.1 ObjectivesDocumento5 pagine8 Jfet Amplifying Circuits: 8.1 ObjectivesdjelbouNessuna valutazione finora

- 5.semiconductor Diodes 2014Documento10 pagine5.semiconductor Diodes 2014Bogdan ZenecanNessuna valutazione finora

- Expt4 JFETamp f03Documento3 pagineExpt4 JFETamp f03Rose Analyn Dela CruzNessuna valutazione finora

- SEE 2063 Chapter 2 DIODE Resistance Levels and Equivalent CircuitsDocumento43 pagineSEE 2063 Chapter 2 DIODE Resistance Levels and Equivalent CircuitsVladMihaiVladMihaiNessuna valutazione finora

- Lab Task Exp-1,2,3Documento9 pagineLab Task Exp-1,2,3Ashish patelNessuna valutazione finora

- Experiment No:: Date: AIM: To Obtain Transfer Characteristics of Field Effect Transistor (FET) TheoryDocumento2 pagineExperiment No:: Date: AIM: To Obtain Transfer Characteristics of Field Effect Transistor (FET) TheoryDharmistha VishwakarmaNessuna valutazione finora

- Electronic Devices & Circuits: Laboratory ManualDocumento61 pagineElectronic Devices & Circuits: Laboratory ManualFadila IsmailNessuna valutazione finora

- Eee 111 Lab Manual 2-8 (Latest)Documento32 pagineEee 111 Lab Manual 2-8 (Latest)Ismot Jahan MoniNessuna valutazione finora

- Laboratory Experiment 2 Multistage AmplifierDocumento7 pagineLaboratory Experiment 2 Multistage AmplifierDanilyn Joy AquinoNessuna valutazione finora

- JFET Characteristics Lab GuideDocumento22 pagineJFET Characteristics Lab GuideAnsar AnsarNessuna valutazione finora

- Experiment No 3a MOSFET CharacteristicsDocumento5 pagineExperiment No 3a MOSFET CharacteristicsManikandan P Engineering EEENessuna valutazione finora

- Experiment 1 Eng NaderDocumento8 pagineExperiment 1 Eng Naderياسر العويطيNessuna valutazione finora

- ch7 8 2Documento60 paginech7 8 2avishek aviNessuna valutazione finora

- Lab5 JFET Characteristics and ApplicationDocumento9 pagineLab5 JFET Characteristics and ApplicationMohmmad AlkhaldiNessuna valutazione finora

- 2200L-EXP3 Handout RevisedDocumento2 pagine2200L-EXP3 Handout RevisedHyoung soo KimNessuna valutazione finora

- CDSGA ECDA Expt5 Light Emitting Diode and Zener DiodeDocumento15 pagineCDSGA ECDA Expt5 Light Emitting Diode and Zener DiodeJhacel CelesteNessuna valutazione finora

- Silicon Diode VI CharacteristicsDocumento7 pagineSilicon Diode VI CharacteristicsM. Ahmad RazaNessuna valutazione finora

- Diodes and Their ApplicationsDocumento6 pagineDiodes and Their ApplicationsKarla Alberto TorresNessuna valutazione finora

- ECE20L - 2 - Expt7 - DE LEMOS PDFDocumento10 pagineECE20L - 2 - Expt7 - DE LEMOS PDFNiko de LemosNessuna valutazione finora

- Ee105 Fet LectDocumento61 pagineEe105 Fet LectKahMun LimNessuna valutazione finora

- EEM328 Electronics Laboratory - Report7 - JFET AmplifiersDocumento1 paginaEEM328 Electronics Laboratory - Report7 - JFET Amplifiersdonatello84Nessuna valutazione finora

- EDC Lab ManualDocumento68 pagineEDC Lab ManualRocky AdityaNessuna valutazione finora

- Characteristics of P-N Junction DiodeDocumento38 pagineCharacteristics of P-N Junction Diodeanon_450523292Nessuna valutazione finora

- chapter 4 Ele IDocumento16 paginechapter 4 Ele Ibiruk satnawNessuna valutazione finora

- FET and SCR Characteristics and ApplicationsDocumento21 pagineFET and SCR Characteristics and ApplicationsRachana MedehalNessuna valutazione finora

- Common Source Amplifier ExperimentDocumento3 pagineCommon Source Amplifier Experimentappuamreddy100% (3)

- 2-1 EDC Lab Manual Jntuk R20 - 201021Documento96 pagine2-1 EDC Lab Manual Jntuk R20 - 201021Durgasaiteja923 SunnyNessuna valutazione finora

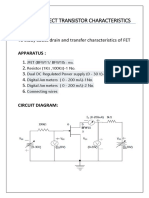

- 6.field Effect Transistor Characteristics: To Study About Drain and Transfer Characteristics of FETDocumento5 pagine6.field Effect Transistor Characteristics: To Study About Drain and Transfer Characteristics of FETTarannum KhatunNessuna valutazione finora

- Experiment 6 Diode CharacteisticsDocumento4 pagineExperiment 6 Diode CharacteisticsAbral QureshiNessuna valutazione finora

- MOSFET TutorialDocumento39 pagineMOSFET Tutorialnoor_dcetNessuna valutazione finora

- MOS CapacitancesDocumento36 pagineMOS CapacitancesSaurav ChourasiaNessuna valutazione finora

- MOSFET DC analysisDocumento29 pagineMOSFET DC analysisSaurav ChourasiaNessuna valutazione finora

- Robu IDC Newslatter August 2019Documento5 pagineRobu IDC Newslatter August 2019Saurav ChourasiaNessuna valutazione finora

- CH 2.2networkDocumento22 pagineCH 2.2networkTeshale AlemieNessuna valutazione finora

- 3.expannded Battery Treatment Service Guide - TCS BatteryDocumento1 pagina3.expannded Battery Treatment Service Guide - TCS BatteryHICHAM el HAYAOUINessuna valutazione finora

- 256 MCDC506 eDocumento3 pagine256 MCDC506 eAndy KristiantoNessuna valutazione finora

- Uninterrupted Power Supply To A Load Using Auto-Selection Between Four Different SourceDocumento3 pagineUninterrupted Power Supply To A Load Using Auto-Selection Between Four Different SourceTahir Abubakar SadiqNessuna valutazione finora

- Neutrik Opticalcon v22 LowDocumento56 pagineNeutrik Opticalcon v22 LowDanny NjomanNessuna valutazione finora

- 10MW Generation Design for Calaguas IslandsDocumento236 pagine10MW Generation Design for Calaguas IslandsNina SakuraNessuna valutazione finora

- VOTANO 100 PresentationDocumento26 pagineVOTANO 100 Presentationbcqbao100% (1)

- Ggsipu CatalogueDocumento54 pagineGgsipu CatalogueSrijan VyasNessuna valutazione finora

- Peak Atlas DCA Pro: User GuideDocumento49 paginePeak Atlas DCA Pro: User GuideLaurentEuniceNessuna valutazione finora

- CCFL Inverter IC OZ960Documento12 pagineCCFL Inverter IC OZ960davesworkshopNessuna valutazione finora

- Exemplo Design e ManufaturaDocumento10 pagineExemplo Design e ManufaturaRenata OliveiraNessuna valutazione finora

- The RF Line: Semiconductor Technical DataDocumento4 pagineThe RF Line: Semiconductor Technical DatabellscbNessuna valutazione finora

- Digital DDS Generator With AD9850 Chip DDS From SQ5RWQDocumento4 pagineDigital DDS Generator With AD9850 Chip DDS From SQ5RWQag1tatorNessuna valutazione finora

- Planning Norms-11 KVDocumento6 paginePlanning Norms-11 KVnitin369Nessuna valutazione finora

- Excess Carriers in SemiconductorsDocumento36 pagineExcess Carriers in SemiconductorsKOKONessuna valutazione finora

- How to perform basic calculations on an electronic calculatorDocumento2 pagineHow to perform basic calculations on an electronic calculatorProduccion TAMNessuna valutazione finora

- Mir20 1 2015Documento1 paginaMir20 1 2015hamadaNessuna valutazione finora

- Guangzhou Hengchi Light Volt Power Generation SystemDocumento30 pagineGuangzhou Hengchi Light Volt Power Generation Systemsubaru WRX STINessuna valutazione finora

- Saf FroDocumento101 pagineSaf FrolkarolinoNessuna valutazione finora

- Price List Siemens Electrical Installation A To Z 22-04-2012Documento36 paginePrice List Siemens Electrical Installation A To Z 22-04-2012Madhu Bn100% (1)

- Lecture - 6 EDocumento33 pagineLecture - 6 ETung HoNessuna valutazione finora

- SvcField8050 C500 CF5001MANUALDocumento428 pagineSvcField8050 C500 CF5001MANUALMarius ManNessuna valutazione finora

- 1202 Frls Cable SpecsDocumento4 pagine1202 Frls Cable Specsparesh joshiNessuna valutazione finora

- BV Rules - TransformersDocumento3 pagineBV Rules - TransformersFebilaNessuna valutazione finora

- Programmable UJT (PUT)Documento4 pagineProgrammable UJT (PUT)Mark Angielo TrillanaNessuna valutazione finora