Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Análisis de Las Técnicas de Modulación SPWM y SVPWM en Control de Inversores Trifásicos de Dos y Tres Niveles - PDF Descargar Libre

Caricato da

Tomas GVCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Análisis de Las Técnicas de Modulación SPWM y SVPWM en Control de Inversores Trifásicos de Dos y Tres Niveles - PDF Descargar Libre

Caricato da

Tomas GVCopyright:

Formati disponibili

Reunión de Otoño de Potencia,

Electrónica y Computación ROPEC' 2012

INTERNACIONAL

Análisis de las técnicas de modulación SPWM y

SVPWM en control de inversores trifásicos de

dos y tres niveles

Daniel Pérez Dorantes, Máximo Hernández Ángeles

Instituto Tecnológico de Morelia

Resumen—El presente artículo es dedicado al estudio de las corrientes de entrada y en la distorsión del voltaje de salida, en

técnicas de modulación SVPWM y SPWM en el control de los inversores.

inversores trifásicos de dos y tres niveles. Las técnicas de En [5], se presenta un método efectivo de modulación con la

modulación se implementan en MATLAB/SIMULINK. Se técnica de vector espacial para un inversor multinivel. El

analiza la eficiencia en el control de la conversión CD-CA y el método está basado en el control de un inversor de dos niveles,

nivel de THD en el voltaje de salida.

cuando el número de niveles se incrementa en un inversor, el

Palabras claves— Electrónica de potencia, Convertidores VSC,

algoritmo de control es más complejo.

SVPWM, SPWM, THD.

Los algoritmos empleados en el presente artículo se basan en

I. INTRODUCCIÓN el desarrollo del método de inversor multinivel a partir de

SVPWM para un inversor de dos niveles [6]. Los resultados

C on la evolución de la electrónica de potencia se dispone comparan a SPWM y SVPWM para inversores de dos y tres

de convertidores estáticos de potencia CD-AC que niveles.

permiten manejar mayor cantidad de energía en los

sistemas eléctricos de potencia, distribución y para la II. TÉCNICA DE CONMUTACIÓN SVPWM PARA

transmisión de energía en DC. UN INVERSOR DE DOS NIVELES.

En las aplicaciones de sistemas de transmisión de alto voltaje

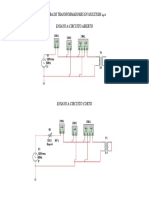

(HVDC) el principal obstáculo es el máximo voltaje soportado La Figura 1 muestra el esquema de un inversor trifásico de dos

por los semiconductores de potencia y la dificultad para niveles alimentando una carga RL. El inversor está formado

conmutar energía en alta potencia. Por lo cual, es necesario por seis interruptores S1 a S6, las señales de control de dichos

desarrollar configuraciones multinivel y multipulso para interruptores se definen por las variables P1 a P6 . Cuando un

manejar potencias más grandes en los convertidores VSC. Los IGBT se conmuta al estado de encendido la señal de control

nuevos sistemas VSC-HVDC, implementados con IGBT son correspondiente tiene el valor 1, y cuando se conmuta a

controlables con técnicas de conmutación PWM [1]. apagado su señal de control tiene un valor 0.

Por otra parte, los convertidores VSC de tres niveles son

implementados en aplicaciones de transmisión de alto voltaje,

debido a que el voltaje de salida puede ser generado por bajas

frecuencias de conmutación, con alta eficiencia, baja

distorsión armónica y una mayor magnitud en la fundamental

del voltaje de salida.

Las técnicas de modulación aplicadas a convertidores VSC

permiten reducir el THD y las pérdidas por conmutación en

los dispositivos semiconductores. Dos técnicas de modulación

ampliamente utilizadas en el control de convertidores VSC son

Figura 1 Inversor trifásico con carga RL

las técnicas SPWM y SVPWM [2]. La técnica SPWM consiste

en emplear varios pulsos de disparo en cada medio ciclo de

voltaje de salida y hacer variar el ancho de cada pulso en Los voltajes de línea a línea se expresan por:

proporción con la amplitud de una onda sinusoidal evaluada

1 1 0

en el centro del mismo pulso. La técnica SVPWM está basada

en la representación de los vectores espaciales de los voltajes 0 1 1 (1)

a, b y c en el plano α y β. Estos vectores permiten que el 1 0 1

voltaje de salida en la fundamental sea alto con una baja

distorsión armónica [3]. Los voltajes de fase se expresan en la forma:

En la referencia [4] se presenta una metodología de las

técnicas PWM, en la reducción de los armónicos de las

Artículo aceptado para ser presentado en la sesión de Posters587 ISBN: 978-607-95476-6-0

Reunión de Otoño de Potencia,

Electrónica y Computación ROPEC' 2012

INTERNACIONAL

2 1 −1 A partir de los ochos vectores disponibles se puede trazar el

−1 2 −1 (2) diagrama vectorial de la Figura 3, donde existe una separación

−1 −1 2 de 60° entre cada vector activo para cubrir el espacio de 360°

en partes iguales y los vectores nulos están en el centro del

De acuerdo a la Figura 1 se tienen 8 combinaciones posibles hexágono.

de encendido y apagado para los interruptores superiores de

cada rama; lo mismo ocurre para los interruptores inferiores, Considerando los interruptores , " , de la Figura 1, se

solo que de manera opuesta. De acuerdo a (1) y (2) los 8 encuentran 8 estados de conmutación como se muestra en la

vectores de conmutación, los voltajes de fase y el voltaje de Figura 3, en donde cada una de las combinaciones se puede

línea a línea en términos de , se pueden establecer como se expresar en forma vectorial como # = ( ), donde x

indica en la Tabla I. =0,...,7. En la Figura 3 se observa que existen dos vectores

nulos, V0 y V7, donde los interruptores " se

Tabla I encuentran abiertos = (000) ó cerrados = (111); V1 a

Vectores de conmutación, voltajes de fase y voltajes de línea

V7, son vectores activos.

Vectores de Vectores de Voltajes de Voltajes de

voltaje conmutación fase línea

a b c

0 0 0 0 0 0 0 0 0

1 0 0 2/3 1 1 1 0 -1

− −

3 3

1 1 0 1/3 1/3 2 0 1 -1

−

3

0 1 0 1 2/3 1 -1 1 0

− − Figura 3. Sectores y vectores de estado de conmutación

3 3

0 1 1 2 1/3 1/3 -1 0 1

− La técnica de modulación SVPWM utilizar el vector de voltaje

3

de referencia &' y los 8 vectores de conmutación para

0 0 1 1 1 2/3 0 -1 1

− − generar el nivel de voltaje deseado a la salida del inversor.

3 3

Con el fin de reducir el número de conmutaciones y obtener el

1 0 1 1/3 2 1/3 1 -1 0

− voltaje máximo en la carga se utiliza el vector &' , los dos

3

vectores activos adyacentes más cercanos y los dos vectores

1 1 1 0 0 0 0 0 0 nulos V0 y V7 en cualquier sector, Figura 3.

Un sistema trifásico puede representarse en un espacio Para implementar la técnica SVPWM, descrita anteriormente,

bidimensional, haciendo una proyección de las coordenadas se aplican los tres pasos siguientes [7]:

abc a un espacio de dos coordenadas, dq, como se ve en la

Figura 2. Esto se logra proyectando los ejes del espacio de tres 1. Cálculo de , y el ángulo α.

dimensiones sobre los dos ejes del plano de dos dimensiones. Considerando la condición presentada en la Figura 2, y

Además el ángulo entre las coordenadas abc debe ser de 120°, se pueden establecer en la forma:

como se indica en la Figura 2.

1 −1/2 −1/2

* + = √ √ (3)

q 0 −

Vref

b Vq

Entonces, el ángulo α queda definido en la forma:

α . = 4 (4)

a d

Vd

2. Determinación de los tiempos de duración T0, T1 y T2.

c Considerando el sector 1 de la Figura 3, se obtiene la Figura 4;

de donde, la duración de los tiempos de conmutación puede

ser calculada como se describe a continuación.

Figura 2. Proyección de un sistema de tres dimensiones abc a un plano de dos

dimensiones.

Artículo aceptado para ser presentado en la sesión de Posters588 ISBN: 978-607-95476-6-0

Reunión de Otoño de Potencia,

Electrónica y Computación ROPEC' 2012

INTERNACIONAL

rama pueden activarse simultáneamente en serie; por ejemplo,

para la fase a se tiene [9]: " P " P " . La

activación simultánea de " conecta a la terminal positiva,

" conecta, dicha terminal, a través de los diodos de

amarre hacia el punto de conexión intermedio, " conecta

a la terminal positiva del circuito de DC a la terminal de CA

de la rama de la fase a, dicha situación se indica en la Figura

5, para la corriente i >0. El voltaje resultante en la terminal de

Figura 4. T1, T2 y T0 del sector 1. CA tiene tres niveles que son +E, 0, -E.

En donde:

56 7&' = (5 7 5 7 )

Esta ecuación puede escribirse en la forma:

cos . 1 cos A/3

56 97&' 9 : @ = 5 : @ 5 * + (5)

>?. 0 >?A/3

Dónde: 0B B

. 0°

Despejando, para los tiempos de conmutación, se tiene:

Figura 5 Inversor de tres niveles

E

D'( G)

5 = 56 F

(6) Los estados de los interruptores de la Figura 5 se pueden

D'(H/)

D'(G) representar de acuerdo a las conmutaciones en el inversor. La

5 = 56 (7) Tabla II indica los estados de conmutación de los interruptores

D'(H/)

de la rama A del inversor de tres niveles. Cuando el estado de

5 = 56 − (5 5 ) (8) la conmutación es 1, indica que los dos interruptores

superiores de la rama A están cerrados y el voltaje del inversor

JKLM 9

9

Entonces: 56 = y = N

QR es +E.

I

F

Donde fz es la frecuencia de conmutación y es el índice de Tabla II.

modulación. Definición de los estados de las conmutaciones

Estado Voltaje

S1 S2 S3 S4

3. Generalización del método del interruptor del inversor

Para los tiempos de conmutación de los vectores espaciales de 1 On On Off Off E

cualquier sector, se considera que están separados 60 grados, 0 Off On On Off 0

-1 Off Off On On -E

para T1 se suman : @ A y para T2 se restan : @ A. Entonces

para cualquier sector se tiene [8]: Similarmente, cuando el estado del interruptor es -1 los dos

interruptores inferiores se encuentran encendidos y el voltaje

5 =

JKLM 9

√OI 9

>?(

H

P>. − P> A>?.4 (9) de QR =-E. Cuando el estado está en 0, los interruptores

JKLM 9

internos y de la rama de la fase a están cerrados y el

√OI 9

5 =

(− cos . >?

A4 >?. cos

A) (10) voltaje en la terminales del inversor es QR = 0.

Cuando el diodo S6 conduce, la corriente en la carga es

5 = 56 − 5 − 5 (11) positiva TQ 0; es decir el punto Z se encuentra conectado a

través de S6 y

Entonces la operación de cada rama del inversor de tres

niveles queda definida por los tres estados de conmutación [1],

III. TÉCNICA DE CONMUTACIÓN SVPWM PARA [-1] y [0]. Considerando las tres fases del inversor se tienen 27

UN INVERSOR DE TRES NIVELES. combinaciones de los estados en los interruptores.

La configuración de un inversor de 3 niveles, con diodo Los voltajes de salida del inversor se pueden agrupar en cuatro

anclado al punto neutro se presenta en la Figura 5. El inversor grupos dependiendo de su magnitud: cero, pequeños,

está formado por 4 interruptores en cada una de sus tres ramas, medianos y grandes, como se indica a continuación.

o fases. Cada interruptor es un conjunto serie-paralelo de

dispositivos de conmutación arreglados para tener los rangos 1) El vector cero ( ) representa tres conmutaciones de estado:

de potencia y voltaje requeridos. Solo 2 interruptores de una [1 1 1], [0 0 0] y [-1 -1 -1]. La magnitud de es cero.

Artículo aceptado para ser presentado en la sesión de Posters589 ISBN: 978-607-95476-6-0

Reunión de Otoño de Potencia,

Electrónica y Computación ROPEC' 2012

INTERNACIONAL

2) Los vectores ( a ), pequeños, tienen una magnitud de Una vez que el vector de referencia se encuentra desplazado a

las nuevas coordenadas, los tiempos de conmutación se

. Cada vector pequeño tiene dos conmutaciones de estado:

calculan mediante las ecuaciones siguientes:

[+1] y [-1].

Y]

3) Los vectores ( a ), medianos, tienen una magnitud de 5 = 5D G[ − 4 (17)

√

√ Y]

. 5 = 5D 4 (18)

√

4) Los vectores ( a W ), grandes, tienen una magnitud de 56 = 5D − 5 − 5 (19)

.

Donde 5 es la duración del vector espacial alineado con el eje

Para establecer el algoritmo SVPWM de un inversor trifásico α, 5 es la duración del vector espacial a 60 grados del eje α y

de tres niveles, cada sector del hexágono de la Figura 3, 56 es la duración del vector espacial cero [10].

utilizado para un inversor trifásico de dos niveles, se puede Los tiempos de conmutación determinados se emplean en el

dividir en cuatro triángulos más pequeños, como se muestra en cálculo de los tiempos de transición de cada vector en las

la Figura 6, para obtener regiones más pequeñas. regiones de cada sector de duración de la conmutación de los

interruptores.

IV. TÉCNICA DE CONMUTACIÓN SPWM.

Esta técnica de control se basa en emplear una modulación

múltiple de varios pulsos de disparo en cada medio ciclo de

voltaje de salida, el ancho de cada pulso varía en proporción

con la amplitud de una onda sinusoidal evaluada en el centro

del mismo pulso.

Figura 6 Vector de referencia y tiempos para el sector 1 La modulación se logra empleando una señal de control

sinusoidal Vcontrol a la frecuencia de salida deseada f1, que es

comparada con una onda portadora triangular para generar las

Cada triángulo de la Figura 6 es por consiguiente un sector del señales de disparo. La frecuencia de la forma de onda

hexágono de dos niveles, Figura 3. En este método, el triangular establece la frecuencia de conmutación del inversor

triángulo al que llega el vector de referencia AP se encuentra fs. La relación de modulación de amplitud es:

sobre la base αβ de coordenadas del vector de referencia. El

origen (0,0) se mueve entonces al vértice del triángulo ^ =

_`aK_b

(20)

correspondiente, Figura 6. Para determinar los triángulos aK]

primero se calculan los parámetros auxiliares X y X , en la

forma: Donde Vcontrol es la amplitud pico de la señal de control y

Vtri, es el pico de la onda portadora triangular. La relación de

Y Y

X = :G @X = √F (12) modulación de frecuencia es:

√

N

G y Z son las coordenadas del vector de referencia AP, X

^ = (21)

d

determina si el triángulo se encuentra en el lado derecho del

sector I,X = 1, o en el lado izquierdo, X = 0. X , determina La acción de la técnica SPWM para el control de disparo de

si se encuentra en la mitad superior,X = 1 o en la mitad los inversores trifásicos de dos y de tres niveles se hace

inferior X = 0. respetando la secuencia de disparo de cada interruptor, los

El vector de referencia se desplaza a la nueva serie de ejes que estados de encendido y apagado de la rama o fase del

se cortan en el vértice principal del triangulo que delimita al convertidor. Estos quedan definidos por medio de la

vector de referencia. Considerando el triángulo delimitador comparación de 3 señales de referencia sinusoidales

como se muestra en la Figura 6, originalmente las coordenadas desfasadas entre si 120°.

del punto P son (G , Z ) y las del punto A son (0, 0) que pasan

a las nuevas coordenadas (G[ , Z[ ) del vector BP, que se V. ANÁLISIS DE LAS TÉCNICAS DE

determinan en la forma siguiente: CONMUTACIÓN SPWM Y SVPWM.

Para el estudio se consideran los inversores, de dos y tres

G[ = G − X X (13)

niveles, conectados a una carga RL en estrella con valores de

√

Z[ = Z − X (14) 0.5Ω y 1mH. Para su implementación en Simulink se utilizan

los bloques de IGBTs, una fuente de voltaje de DC, bloques de

La posición del triangulo se determina por la ecuación: dispositivos RLC, medidores de voltaje y corriente,

proporcionados por el programa.

∆= X 2X (16)

4

Artículo aceptado para ser presentado en la sesión de Posters590 ISBN: 978-607-95476-6-0

Reunión de Otoño de Potencia,

Electrónica y Computación ROPEC' 2012

INTERNACIONAL

Para observar el control de los inversores de dos y tres niveles

200

utilizando las técnicas de modulación SVPWM y SPWM, se 150

consideran dos inversores trifásicos de dos y tres niveles 100

operando con un voltaje de entrada de 200V de DC, generando 50

un voltaje de salida a una frecuencia fundamental de 60 Hz. Se 0

realizan pruebas en el sistema VSC a las frecuencias de -50

conmutación de 1800 Hz y 10k Hz y se considera una relación -100

de modulación de amplitud ma de 0.8. Los resultados -150

obtenidos se presentan en las figuras 7 a 14. -200

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Tiempo(sec)

a) b)

Las figuras 7 a 10 se obtienen para las frecuencias de Figura 10. Resultados obtenidos en inversor de dos niveles a una frecuencia de

conmutación de 1800 Hz y 10k Hz, con control SPWM y conmutación de 10k Hz, a) Voltaje de línea con SPWM, b) Contenido

SVPWM, para un inversor de dos niveles. armónico y THD del voltaje de línea.

200

Las figuras 11 a 14 se obtienen para las frecuencias de 150

conmutación de 1800 Hz y 10k Hz, con control SPWM y 100

SVPWM, para un inversor de tres niveles. 50

0

200

-50

150

-100

100

-150

50

-200

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

0 Tiempo(sec)

-50

a) b)

-100

Figura 11. Resultados obtenidos en un inversor de tres niveles a una

-150 frecuencia de conmutación de 1800 Hz a) Voltaje de línea con SVPWM, b)

-200

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Contenido armónico y THD del voltaje de línea.

Tiempo(sec)

250

a) b) 200

Figura 7. Resultados obtenidos en un inversor de dos niveles a una frecuencia 150

de conmutación de 1800 Hz, a) Voltaje de línea con SVPWM, b) Contenido 100

armónico y THD del voltaje de línea. 50

200 -50

150 -100

100 -150

-200

50 0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Tiempo(sec)

-50

a) b)

Figura 12. Resultados obtenidos para un inversor de tres niveles a una

-100

frecuencia de conmutación de 1800 Hz, a) Voltaje de línea con SPWM, b)

-150 Contenido armónico y THD del voltaje de línea.

-200

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Tiempo(sec)

200

a) b)

150

Figura 8. Resultados obtenidos en un inversor de dos niveles a una frecuencia

100

de conmutación de 1800 Hz, a) Voltaje de línea con SPWM, b) Contenido

50

armónico y THD del voltaje de línea.

0

200 -50

150

-100

100

-150

50

-200

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

0 Tiempo(sec)

-50 a) b)

-100 Figura 13. Resultados obtenidos en un inversor de tres niveles a una

-150 frecuencia de conmutación de 10k Hz a) Voltaje de línea con SVPWM, b)

-200

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Contenido armónico y THD del voltaje de línea.

Tiempo(sec)

a) b)

Figura 9. Resultados obtenidos en un inversor de dos niveles a una frecuencia

de conmutación de 10k Hz, a) Voltaje de línea con SVPWM, b) Contenido

armónico y THD del voltaje de línea.

Artículo aceptado para ser presentado en la sesión de Posters591 ISBN: 978-607-95476-6-0

Reunión de Otoño de Potencia,

Electrónica y Computación ROPEC' 2012

INTERNACIONAL

200 VII. REFERENCIAS

150

100

[1] Ning, Li; Yue, Wang; Yingwei, Jiang; Zhaoan, Wang ,“A fast algorithm

for three-level SVPWM in NPC inverters based on traditional three-level

50

SPWM·” 2nd IEEE International Symposium on Digital 2010, Page(s):

0

53 – 57.

-50

[2] K. Vinoth Kumar, Prawin Angel Michael, Joseph P. John and Dr. S.

-100

Suresh Kumar, ”Simulation and comparison of SPWM and SVPWM

-150 control for three phase inverter”, ARPN Journal of Engineering and

-200 Applied Sciences,Vol.5 No 7, Julio 2010.

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Tiempo(sec)

[3] LI Ning, WANG Yue, JIANG Yingwei and WANG Zhaoan “A Fast

a) b) Algorithm for Three-level SVPWM in NPC Inverters Based on

Figura 14. Resultados obtenidos en un inversor de tres niveles a una Traditional Three-level SPWM”, 2010 2nd IEEE International

frecuencia de conmutación de 10k Hz a) Voltaje de línea con SPWM, b) Symposium on Power Electronics for Distributed Generation Systems.

Contenido armónico y THD del voltaje de línea. [4] Nae-Chun Park, Hyung-Soo Mok, Sang-Hoon Kim, ”Reduction of Input

Current Harmonics for Three Phase PWM Converter Systems under a

En la Tabla III se presenta un resumen de las distorsiones Distorted Utility Voltage”, Journal of Power Electronics, Vol. 10, No. 4,

armónicas obtenidas al emplear las técnicas SPWM y Julio 2010.

SVPWM en los inversores de dos y tres niveles. [5] P.Satish Kumar, J.Amarnath and S.V.L.Narasimham, “An Effective

Space-Vector PWM Method for Multi-level Inverter Based on Two-

Tabla III Resumen de resultados de las simulaciones para SVPWM y SPWM level Inverter” International Journal of Computer and Electrical

Engineering, Vol. 2, No.2, Abril, 2010.

Niveles del Fc SPWM SPWM SVPWM SVPWM [6] Kocalmis,A.; Sunter, S., “Simulation of a Space Vector PWM Controller

inversor Voltaje de THD Voltaje de THD For a Three-Level Voltage-Fed Inverter Motor Drive” IEEE Industrial

salida salida Electronics, IECON 2006 - 32nd Annual Conference 2006, Page(s):

2 1800 138.1 90.23% 183.6 60.6% 1915 – 1920.

2 10k 120.5 58.64% 170 28.32%

3 1800 137.7 41.76% 184.9 30.3% [7] Amit Kumar Gupta, Ashwin M. Khambadkone, “A Space Vector PWM

3 10k 135.4 16.23% 182.1 14.33% Scheme for Multilevel Inverters Based on Two-Level Space Vector

PWM”, IEEE transactions on industrial electronics, vol. 53, No. 5,

October 2006.

VI. CONCLUSIONES [8] Jiajun Liu, Lixiao Yao, Tiansen Wu, Yuan An, “Implementation of

Two-Level SVPWM Algorithm in PSCAD/EMTDC”, Power and

Los resultados del estudio muestran que la distorsión armónica Energy Engineering Conference (APPEEC), 2010 Asia-Pacific

es notablemente menor cuando el inversor empleado es de tres [9] Shan Li, Shuxi Liu, Huihui Xiao and Hongyan Chen, “SVPWM

niveles. Esto es debido al mayor número de niveles de tensión Algorithm Based on Non-orthogonal Coordinate System for a Three-

en el inversor, con lo cual se obtiene una forma de onda más level Inverter Motor Drive”, 2011 Fourth International Conference on

Intelligent Computation Technology and Automation.

sinusoidal en el voltaje de salida. Una menor distorsión

permite trabajar con filtros de salida menores, ya que [10] Yao Zhezhi, Yi Lingzhi, Peng Hanmei, Fu Xi, Deng Dong, “Study of

disminuye el contenido en armónicos de baja frecuencia a Simplified SVPWM Algorithm Based on Three-Level Inverter” 2009,

Page(s): 876 – 881.

filtrar. Este aspecto representa una gran ventaja de los

inversores de tres niveles respecto a los de dos niveles, puesto

que a igual distorsión armónica, los interruptores del inversor VIII. BIOGRAFÍA

de tres niveles pueden conmutar a menos frecuencia, o bien

los filtros de salida pueden ser de menor tamaño.

El análisis de las técnicas demuestra que con SVPWM el Daniel Pérez Dorantes, estudió licenciatura en el Instituto

Tecnológico de Lázaro Cárdenas. Actualmente estudia

voltaje de la fundamental en la salida de los inversores es maestría en ciencias en ingeniería eléctrica en el Instituto

mayor en comparación con SPWM, la razón de la mejora de la Tecnológico de Morelia.

utilización del voltaje de DC es por la relación del voltaje

máximo para SVPWM es de e/√3 y el de SPWM es de

/√

e/2 al comparar los dos valores /

1.155 se tiene

que con SVPWM brinda un 15.5% mas de voltaje en la salida

del inversor.

Máximo Hernández Ángeles, estudió licenciatura,

Con SVPWM se tiene mayor voltaje de utilización de DC y maestría y doctorado en ingeniería eléctrica en la

menor THD en el voltaje de la fundamental de salida de los ESIME-IPN. Actualmente es profesor en el Instituto

inversores de dos y tres niveles en comparación con SPWM. Tecnológico de Morelia.

Artículo aceptado para ser presentado en la sesión de Posters592 ISBN: 978-607-95476-6-0

Potrebbero piacerti anche

- Prueba de Aislamiento A Motor ElectricoDocumento6 paginePrueba de Aislamiento A Motor ElectricoMarcos Ponce CelisNessuna valutazione finora

- Sonido ProfesionalDocumento11 pagineSonido Profesionaldjshanti100% (2)

- Apunte 1Documento21 pagineApunte 1jord001100% (1)

- Atex IEC FinalDocumento17 pagineAtex IEC FinalilcompaNessuna valutazione finora

- Teoria Del CieloDocumento175 pagineTeoria Del CieloAnonymous XPQKHSNessuna valutazione finora

- 01 Movimiento Manual Del Robot Con El JoystickDocumento17 pagine01 Movimiento Manual Del Robot Con El JoystickJose Manuel Moa PerezNessuna valutazione finora

- Inventario VialDocumento23 pagineInventario Vialjoseph1606100% (1)

- Diseño Desarenador SorahuecoDocumento1 paginaDiseño Desarenador SorahuecoClariitha CzNessuna valutazione finora

- Prueba de Transformadores en Multisim 14Documento1 paginaPrueba de Transformadores en Multisim 14Joglupe0% (1)

- Informe de Controladores PIDDocumento20 pagineInforme de Controladores PIDfranco_3210_Nessuna valutazione finora

- ManttoDocumento115 pagineManttoKatherinne SutizalNessuna valutazione finora

- Entradas y SalidasDocumento71 pagineEntradas y SalidasJose Antonio MercadoNessuna valutazione finora

- Certificado 07027f Cidet ActualizadoDocumento2 pagineCertificado 07027f Cidet ActualizadoEDUARDO DIAZ0% (1)

- Sistema Ward-Leonard JoseDocumento4 pagineSistema Ward-Leonard JoseBryan Javier PairazamanNessuna valutazione finora

- Propulsores CDDocumento37 paginePropulsores CDXx OMEGA xXNessuna valutazione finora

- Requerimientos para Repotenciar MotorDocumento2 pagineRequerimientos para Repotenciar MotorAlejandra de las Nieves0% (2)

- Presentacion MotoresDocumento16 paginePresentacion MotoresHERNANDEZ AGUIRRE LUISA FERNANDANessuna valutazione finora

- Troceadores Tipo BDocumento6 pagineTroceadores Tipo BNey Raul Benji JoaquinNessuna valutazione finora

- Motor Trifasico de InduccionDocumento35 pagineMotor Trifasico de InduccioncesarNessuna valutazione finora

- Motores Electricos para BusesDocumento9 pagineMotores Electricos para BusesricardoNessuna valutazione finora

- PrimerDeberDE23 10 2019Documento5 paginePrimerDeberDE23 10 2019Ezequiel VelowssNessuna valutazione finora

- Checklist Alta Tension Gnral - 2019 - TTDocumento5 pagineChecklist Alta Tension Gnral - 2019 - TTjfuenzalidagNessuna valutazione finora

- Taller Inductancia PDFDocumento2 pagineTaller Inductancia PDFWilmerNessuna valutazione finora

- Proyecto Control de Velocidad de Un Motor DCDocumento12 pagineProyecto Control de Velocidad de Un Motor DCalexis pedrozaNessuna valutazione finora

- Arranque Estrella - Triangulo Lo UltimoDocumento15 pagineArranque Estrella - Triangulo Lo UltimoSimcel SrlNessuna valutazione finora

- Listado Normas NTC Ing ElectricaDocumento12 pagineListado Normas NTC Ing Electricawildor01Nessuna valutazione finora

- Rectificador Trifasico de Voltaje y SCRDocumento11 pagineRectificador Trifasico de Voltaje y SCRLuis Collahua CuyaNessuna valutazione finora

- Informe de PWM PDFDocumento12 pagineInforme de PWM PDFCajamarca AlexNessuna valutazione finora

- Practica 3 de MaquinasDocumento12 paginePractica 3 de MaquinasGeo MolinaNessuna valutazione finora

- Motor de Induccion Polifasico GeneralidadesDocumento15 pagineMotor de Induccion Polifasico GeneralidadesSantiago Castro100% (1)

- Contactores Ac1 - Ac3Documento2 pagineContactores Ac1 - Ac3Carlos Lovera Rodriguez100% (1)

- Motores y Generadores DCDocumento9 pagineMotores y Generadores DCMario SalazarNessuna valutazione finora

- Motor de Reluctancia Con InversorDocumento46 pagineMotor de Reluctancia Con InversorMaxNessuna valutazione finora

- Práctica 7 Conversión Digital-Analógico PDFDocumento4 paginePráctica 7 Conversión Digital-Analógico PDFJuan CotacioNessuna valutazione finora

- Sistemas Trifásicos Simétricos y AsimétricosDocumento6 pagineSistemas Trifásicos Simétricos y AsimétricosEdilson Valderrama100% (1)

- Informe 2 AccionamientoDocumento18 pagineInforme 2 AccionamientoAlex Melo CarrascoNessuna valutazione finora

- Laboratorio Maquinas ElectricasDocumento12 pagineLaboratorio Maquinas ElectricasGiovanni Paniura AysaNessuna valutazione finora

- Guía de Instalación PrimeMobileDocumento22 pagineGuía de Instalación PrimeMobilejulian lozanoNessuna valutazione finora

- ProblemasDocumento3 pagineProblemasAgustín RemacheNessuna valutazione finora

- Ensayo Variadores de FrecuenciaDocumento3 pagineEnsayo Variadores de Frecuenciaivan100% (1)

- Taller Final Alex BadilloDocumento9 pagineTaller Final Alex BadilloAlex Badillo100% (1)

- Manual Del TTRDocumento5 pagineManual Del TTRJair Alejandro CANessuna valutazione finora

- Adecuacion de Las Redes de Distribución, Dimensionamiento de Transformadores y Método de Cálculo de Caídas de Voltaje en Redes Secundarias FinalDocumento22 pagineAdecuacion de Las Redes de Distribución, Dimensionamiento de Transformadores y Método de Cálculo de Caídas de Voltaje en Redes Secundarias FinalMiguel ArmasNessuna valutazione finora

- Caracteristicas de Jaula de ArdillaDocumento4 pagineCaracteristicas de Jaula de ArdillaStephanie Zapata SantillánNessuna valutazione finora

- ChopperDocumento9 pagineChopperAngel NavedaNessuna valutazione finora

- Examen Del 5d1 255Documento2 pagineExamen Del 5d1 255Pamela VillarroelNessuna valutazione finora

- Informe Teoria de Control 3Documento16 pagineInforme Teoria de Control 3edison matiasNessuna valutazione finora

- Informe 1 - La Máquina de Corriente Continua-GeneralidadesDocumento7 pagineInforme 1 - La Máquina de Corriente Continua-GeneralidadesCRISTIAN CAMILO GALLEGO GOMEZNessuna valutazione finora

- Transformadores en ParaleloDocumento6 pagineTransformadores en Paraleloreinaldo bolivarNessuna valutazione finora

- Unidad 6-1Documento12 pagineUnidad 6-1Ediquio Gonzalez0% (1)

- Ficha Tecnica Domotica Myhome BticinoDocumento504 pagineFicha Tecnica Domotica Myhome Bticinoirene100% (1)

- Como Calcular Un Transformador de Voltaje PDFDocumento11 pagineComo Calcular Un Transformador de Voltaje PDFJuan CarlosNessuna valutazione finora

- Conversor DACDocumento7 pagineConversor DACDuo Doble ANessuna valutazione finora

- Rectificadores RegenerativosDocumento4 pagineRectificadores Regenerativosxavier2ramos-1Nessuna valutazione finora

- Conversor Ac AcDocumento2 pagineConversor Ac AcAndres Pereira HerreraNessuna valutazione finora

- CERTIFICADO CE - METER HUAWEI MonofasicoDocumento10 pagineCERTIFICADO CE - METER HUAWEI MonofasicoPaula Nanclares Etem100% (1)

- Informe SSW06 WegDocumento15 pagineInforme SSW06 WegsamuelNessuna valutazione finora

- Ejercitario de TransformadoresDocumento2 pagineEjercitario de TransformadoresManuel Nuñez FigueredoNessuna valutazione finora

- Implementación y Análisis de Un Convertidor de DC A Ac Tipo Push PullDocumento10 pagineImplementación y Análisis de Un Convertidor de DC A Ac Tipo Push PullCarolina RestrepoNessuna valutazione finora

- Maquinas Tarea2Documento6 pagineMaquinas Tarea2Darwin Felipe Parra PardoNessuna valutazione finora

- Sistema WardDocumento2 pagineSistema WardL ONessuna valutazione finora

- Lab. 2 - Características Del Diodo y AplicacionesDocumento4 pagineLab. 2 - Características Del Diodo y AplicacionesDavid Chamorro AriasNessuna valutazione finora

- Principios de Funcionamiento Del Regulador Del Voltaje KCR 760Documento10 paginePrincipios de Funcionamiento Del Regulador Del Voltaje KCR 760Karel GómezNessuna valutazione finora

- Taller Evaluativo - 3er Corte Máquinas EléctricasDocumento35 pagineTaller Evaluativo - 3er Corte Máquinas EléctricasDavid Alejandro Diaz RinconNessuna valutazione finora

- 1 PLC'sDocumento54 pagine1 PLC'sRicky SuasnavasNessuna valutazione finora

- Practica Redes IndustrialDocumento23 paginePractica Redes IndustrialLeo NogueraNessuna valutazione finora

- Ropec 2012 123Documento7 pagineRopec 2012 123Jose CNessuna valutazione finora

- Juan TiszaDocumento8 pagineJuan TiszaJhoel Arroyo FloresNessuna valutazione finora

- Proyecto SVM VSI PDFDocumento7 pagineProyecto SVM VSI PDFArielNessuna valutazione finora

- Paper DC AcDocumento11 paginePaper DC AcGadiel Armijos VNessuna valutazione finora

- 3hac050917 TRM Rapid RW 6-EsDocumento1.888 pagine3hac050917 TRM Rapid RW 6-EsDiego GarzaNessuna valutazione finora

- Espel Emi 0331 PDocumento51 pagineEspel Emi 0331 PTomas GVNessuna valutazione finora

- Estandarizacion para La Industria 4 0Documento337 pagineEstandarizacion para La Industria 4 0Tomas GVNessuna valutazione finora

- 06 AsiDocumento21 pagine06 AsiTomas GVNessuna valutazione finora

- Capitulo3 Rev0Documento22 pagineCapitulo3 Rev0Tomas GVNessuna valutazione finora

- Automatizacion y ControlDocumento34 pagineAutomatizacion y ControlTomas GVNessuna valutazione finora

- Automatizacion y ControlDocumento34 pagineAutomatizacion y ControlTomas GVNessuna valutazione finora

- Guía de Primeros Pasos Con CMMT-As-PN - Rev3Documento20 pagineGuía de Primeros Pasos Con CMMT-As-PN - Rev3Tomas GVNessuna valutazione finora

- s71200 System Manual Es-ES Es-ESDocumento1.070 pagines71200 System Manual Es-ES Es-ESDieguito PinguilNessuna valutazione finora

- CMMT ST C8 1C - S0 - Description - 2019 10a - 8113758e1Documento64 pagineCMMT ST C8 1C - S0 - Description - 2019 10a - 8113758e1Tomas GVNessuna valutazione finora

- Ahorro de Espacio: Sistema de Bus de CampoDocumento31 pagineAhorro de Espacio: Sistema de Bus de CampoTomas GVNessuna valutazione finora

- Sensor de ProximidadDocumento37 pagineSensor de ProximidadLuis Antoni Morales DiazNessuna valutazione finora

- 04-Opticos UltrasonicosDocumento19 pagine04-Opticos UltrasonicosTomas GVNessuna valutazione finora

- Unidad Ii Tipos de Sensores de Proximidad PDFDocumento37 pagineUnidad Ii Tipos de Sensores de Proximidad PDFTomas GVNessuna valutazione finora

- Transductores Como FuncionaDocumento4 pagineTransductores Como FuncionaCesar CLNessuna valutazione finora

- Tipos de TermoparesDocumento9 pagineTipos de TermoparesRenzoIlbertoNessuna valutazione finora

- Sistemas de Sensores y ActuadoresDocumento37 pagineSistemas de Sensores y ActuadoresDiego ToroNessuna valutazione finora

- Sistemas de Sensores y ActuadoresDocumento37 pagineSistemas de Sensores y ActuadoresDiego ToroNessuna valutazione finora

- Simbolos Transductores Sensores DetectoresDocumento3 pagineSimbolos Transductores Sensores DetectoresTomas GVNessuna valutazione finora

- Sensores MagneticosDocumento168 pagineSensores MagneticosAlejandro MartínezNessuna valutazione finora

- 28 Sensores Ultras NicosDocumento10 pagine28 Sensores Ultras NicosPapo NoveloNessuna valutazione finora

- Practicas 2345electricos PDFDocumento83 paginePracticas 2345electricos PDFTomas GVNessuna valutazione finora

- Transductores Como FuncionaDocumento4 pagineTransductores Como FuncionaCesar CLNessuna valutazione finora

- 02-Inductivo Capacitivo PDFDocumento34 pagine02-Inductivo Capacitivo PDFTomas GVNessuna valutazione finora

- 02-Inductivo Capacitivo PDFDocumento34 pagine02-Inductivo Capacitivo PDFTomas GVNessuna valutazione finora

- Arduinodelphitokio10 170718161233Documento180 pagineArduinodelphitokio10 170718161233Tomas GVNessuna valutazione finora

- Las Nuevas Tecnologias Aplicadas Al Control AutomaDocumento6 pagineLas Nuevas Tecnologias Aplicadas Al Control AutomaTomas GVNessuna valutazione finora

- 1.1.2muros Estructuras RigidasDocumento35 pagine1.1.2muros Estructuras RigidasJose Antonio Paredes VeraNessuna valutazione finora

- U1taller1 Matemática AplicadaDocumento5 pagineU1taller1 Matemática AplicadaCHRISTIAN PATRICIO QUITO AREVALONessuna valutazione finora

- Guia 3 Estatica Del SolidoDocumento11 pagineGuia 3 Estatica Del SolidoBrayan SNessuna valutazione finora

- Contenido Programatico-Ventilacion de MinasDocumento3 pagineContenido Programatico-Ventilacion de MinasCesar Diaz MalaverNessuna valutazione finora

- Curso de Construcción de Obras SubterraneasDocumento49 pagineCurso de Construcción de Obras SubterraneasNilmer Quispe ChavarriNessuna valutazione finora

- Competencias, Capacidades, Desempeños y Estándares de Aprendizaje de Comunicación - 1º CNDocumento4 pagineCompetencias, Capacidades, Desempeños y Estándares de Aprendizaje de Comunicación - 1º CNalexander2021Nessuna valutazione finora

- Génesis - Creación y CienciaDocumento36 pagineGénesis - Creación y CienciaJuan Antonio Valls Ferrer100% (1)

- Lab3 Quiroz Pereira MarinDocumento9 pagineLab3 Quiroz Pereira MarinAndres QuirozNessuna valutazione finora

- Equilibrioenel PlanoDocumento4 pagineEquilibrioenel Planodeapioth50% (2)

- Trabajo Final CorrelacionesDocumento103 pagineTrabajo Final CorrelacionesAndres LojaNessuna valutazione finora

- Guia 1 Am1c23Documento10 pagineGuia 1 Am1c23Vieja Chadetu LaconNessuna valutazione finora

- Intercambiadores de Calor 1Documento35 pagineIntercambiadores de Calor 1VanessaVG100% (1)

- Sensores de TemperaturaDocumento6 pagineSensores de TemperaturaEsmeralda GuayasaminNessuna valutazione finora

- Medición de Flujo de Hidrocarburos. Artículo FinalDocumento17 pagineMedición de Flujo de Hidrocarburos. Artículo FinalOmar David Ochoa RemolinaNessuna valutazione finora

- Manual de SoldadurasDocumento0 pagineManual de SoldadurasLlacho Colque W. DavidNessuna valutazione finora

- John Berger Poemas de EmigracionDocumento4 pagineJohn Berger Poemas de EmigracionBel SalNessuna valutazione finora

- Taller Circuito ELECTRONICODocumento71 pagineTaller Circuito ELECTRONICOrobertcm1991Nessuna valutazione finora

- Cómo Hacer Un Informe de LaboratorioDocumento10 pagineCómo Hacer Un Informe de LaboratorioIz RemyNessuna valutazione finora

- Practica de Laboratorio #1Documento9 paginePractica de Laboratorio #1Laura DsbNessuna valutazione finora

- Exámen de Física Aplicada Al Buceo Buzo BasicoDocumento10 pagineExámen de Física Aplicada Al Buceo Buzo BasicoAmaru Castro ParedesNessuna valutazione finora

- Planeador de Clase de Fisica 10, 1pDocumento5 paginePlaneador de Clase de Fisica 10, 1pCrave GueNessuna valutazione finora

- Roco PDFDocumento2 pagineRoco PDFAnonymous n3NZBzNessuna valutazione finora