Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Module 1 PDF

Caricato da

hrrameshhrTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Module 1 PDF

Caricato da

hrrameshhrCopyright:

Formati disponibili

DEPT.

OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

UNIT – 1

INTRODUTION TO VLSI

EVOLUTION & TRENDS IN VLSI

INTRODUCTION TO ASIC

o TYPES OF ASIC

FULL CUSTOM ASIC

STANDARD CELL BASED ASIC

GATE ARRAY BASED ASIC

CHANNELLED GATE ARRAY

CHANNEL-LESS ARRAY

STRUCTURED GATE ARRAY

PROGRAMMABLE LOGIC DEVICES

FIELD PROGRAMMABLE GATE ARRAY

ASIC DESIGN FLOW

CMOS LOGIC

oMOS TRANSISTORS

oCMOS LOGIC

REFERENCES

VLSI DESIGN, ECEg 4201 1 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

EVOLUTION & TRENDS IN VLSI

The concept of digital data manipulation has made a dramatic impact on our society.

One has long grown accustomed to the idea of digital computers. Evolving steadily from

mainframe and minicomputers, personal and laptop computers have proliferated into daily

life. More significant, however, is a continuous trend towards digital solutions in all other

areas of electronics. Instrumentation was one of the first non computing domains where

the potential benefits of digital data manipulation over analog processing were recognized.

Other areas such as control were soon to follow. Only recently have we witnessed the

conversion of telecommunications and consumer electronics towards the digital format.

Increasingly, telephone data is transmitted and processed digitally over both wired and

wireless networks. The compact disk has revolutionized the audio world, and digital video

is following in its footsteps.

The idea of implementing computational engines using an encoded data format is by

no means an idea of our times. In the early nineteenth century, Babbage envisioned large-

scale mechanical computing devices, called Difference Engines [Swade93]. Although these

engines use the decimal number system rather than the binary representation now

common in modern electronics, the underlying concepts are very similar. The Analytical

Engine, developed in 1834, was perceived as a general-purpose computing machine, with

features strikingly close to modern computers. Besides executing the basic repertoire of

operations (addition, subtraction, multiplication, and division) in arbitrary sequences, the

machine operated in a two-cycle sequence, called “store” and “mill” (execute), similar to

current computers. It even used pipelining to speed up the execution of the addition

operation!. Unfortunately, the complexity and the cost of the designs made the concept

impractical. For instance, the design of Difference Engine I (part of which is shown in

Figure 1.1) required 25,000 mechanical parts at a total cost of £17,470 (in 1834!).

Figure 1.1 Working part of Babbage’s Difference Engine I (1832), the first known automatic calculator

(from [Swade93], courtesy of the Science Museum of London).

VLSI DESIGN, ECEg 4201 2 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

The electrical solution turned out to be more cost effective. Early digital electronics

systems were based on magnetically controlled switches (or relays). They were mainly

used in the implementation of very simple logic networks. Examples of such are train safety

systems, where they are still being used at present. The age of digital electronic computing

only started in full with the introduction of the vacuum tube. While originally used almost

exclusively for analog processing, it was realized early on that the vacuum tube was useful

for digital computations as well. Soon complete computers were realized. The era of the

vacuum tube based computer culminated in the design of machines such as the ENIAC

(intended for computing artillery firing tables) and the UNIVAC I (the first successful

commercial computer). To get an idea about integration density, the ENIAC was 80 feet

long, 8.5 feet high and several feet wide and incorporated 18,000 vacuum tubes. It became

rapidly clear, however, that this design technology had reached its limits. Reliability

problems and excessive power consumption made the implementation of larger engines

economically and practically infeasible.

All changed with the invention of the transistor at Bell Telephone Laboratories in

1947 [Bardeen48], followed by the introduction of the bipolar transistor by Schockley in

1949 [Schockley49]1. It took till 1956 before this led to the first bipolar digital logic gate,

introduced by Harris [Harris56], and even more time before this translated into a set of

integrated-circuit commercial logic gates, called the Fairchild Micrologic family

[Norman60]. The first truly successful IC logic family, TTL (Transistor-Transistor Logic) was

pioneered in 1962 [Beeson62]. Other logic families were devised with higher performance

in mind. Examples of these are the current switching circuits that produced the first sub-

nanosecond digital gates and culminated in the ECL (Emitter-Coupled Logic) family

[Masaki74]. TTL had the advantage, however, of offering a higher integration density and

was the basis of the first integrated circuit revolution. In fact, the manufacturing of TTL

components is what spear-headed the first large semiconductor companies such as

Fairchild, National, and Texas Instruments. The family was so successful that it composed

the largest fraction of the digital semiconductor market until the 1980s.

Ultimately, bipolar digital logic lost the battle for hegemony in the digital design

world for exactly the reasons that haunted the vacuum tube approach: the large power

consumption per gate puts an upper limit on the number of gates that can be reliably

integrated on a single die, package, housing, or box. Although attempts were made to

develop high integration density, low-power bipolar families (such as I2L—Integrated

Injection Logic [Hart72]), the torch was gradually passed to the MOS digital integrated

circuit approach.

The basic principle behind the MOSFET transistor (originally called IGFET) was

proposed in a patent by J. Lilienfeld (Canada) as early as 1925, and, independently, by O.

Heil in England in 1935. Insufficient knowledge of the materials and gate stability

problems, however, delayed the practical usability of the device for a long time. Once these

were solved, MOS digital integrated circuits started to take off in full in the early 1970s.

Remarkably, the first MOS logic gates introduced was of the CMOS variety [Wanlass63], and

this trend continued till the late 1960s. The complexity of the manufacturing process

VLSI DESIGN, ECEg 4201 3 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

delayed the full exploitation of these devices for two more decades. Instead, the first

practical MOS integrated circuits were implemented in PMOS-only logic and were used in

applications such as calculators. The second age of the digital integrated circuit revolution

was inaugurated with the introduction of the first microprocessors by Intel in 1972 (the

4004) [Faggin72] and 1974 (the 8080) [Shima74]. These processors were implemented in

NMOS-only logic, which has the advantage of higher speed over the PMOS logic.

Simultaneously, MOS technology enabled the realization of the first high density

semiconductor memories. For instance, the first 4Kbit MOS memory was introduced in

1970 [Hoff70].

These events were at the start of a truly astounding evolution towards ever higher

integration densities and speed performances, a revolution that is still in full swing right

now. The road to the current levels of integration has not been without hindrances,

however. In the late 1970s, NMOS-only logic started to suffer from the same plague that

made high-density bipolar logic unattractive or infeasible: power consumption. This

realization, combined with progress in manufacturing technology, finally tilted the balance

towards the CMOS technology, and this is where we still are today. Interestingly enough,

power consumption concerns are rapidly becoming dominant in CMOS design as well, and

this time there does not seem to be a new technology around the corner to alleviate the

problem.

Although the large majority of the current integrated circuits are implemented in

the MOS technology, other technologies come into play when very high performance is at

stake. An example of this is the BiCMOS technology that combines bipolar and MOS devices

on the same die. BiCMOS is used in high-speed memories and gate arrays. When even

higher performance is necessary, other technologies emerge besides the already mentioned

Bipolar silicon ECL family—Gallium-Arsenide, Silicon-Germanium and even

superconducting technologies. These technologies only play a very small role in the overall

digital integrated circuit design scene. With the ever increasing performance of CMOS, this

role is bound to be further reduced with time.

INTRODUCTION TO ASICs

An ASIC (pronounced “a-sick”; bold typeface defines a new term) is an application-

specific integrated circuit —at least that is what the acronym stands for. Before we

answer the question of what that means we first look at the evolution of the silicon chip or

integrated circuit (IC).

Figure 1.1(a) shows an IC package (this is a pin-grid array, or PGA, shown upside down; the

pins will go through holes in a printed-circuit board). People often call the package a chip,

but, as you can see in Figure 1.1(b), the silicon chip itself (more properly called a die) is

mounted in the cavity under the sealed lid. A PGA package is usually made from a ceramic

material, but plastic packages are also common.

VLSI DESIGN, ECEg 4201 4 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

FIGURE 1.1 An integrated circuit (IC). (a) A pin-grid array (PGA) package. (b) The silicon die or chip is

under the package lid.

The physical size of a silicon die varies from a few millimeters on a side to over 1

inch on a side, but instead we often measure the size of an IC by the number of logic gates

or the number of transistors that the IC contains. As a unit of measure a gate equivalent

corresponds to a two-input NAND gate (a circuit that performs the logic function, F = A • B

). Often we just use the term gates instead of gate equivalents when we are measuring chip

size—not to be confused with the gate terminal of a transistor. For example, a 100 kgate IC

contains the equivalent of 100,000 two-input NAND gates.

The semiconductor industry has evolved from the first ICs of the early 1970s and

matured rapidly since then. Early small-scale integration ( SSI ) ICs contained a few (1 to

10) logic gates—NAND gates, NOR gates, and so on—amounting to a few tens of

transistors. The era of medium-scale integration ( MSI ) increased the range of integrated

logic available to counters and similar, larger scale, logic functions. The era of large-scale

integration ( LSI ) packed even larger logic functions, such as the first microprocessors,

into a single chip. The era of very large-scale integration ( VLSI ) now offers 64-bit

microprocessors, complete with cache memory and floating-point arithmetic units—well

over a million transistors—on a single piece of silicon. As CMOS process technology

improves, transistors continue to get smaller and ICs hold more and more transistors.

Some people (especially in Japan) use the term ultralarge scale integration ( ULSI ), but

most people stop at the term VLSI; otherwise we have to start inventing new words.

The earliest ICs used bipolar technology and the majority of logic ICs used either

transistor–transistor logic ( TTL ) or emitter-coupled logic (ECL). Although invented

before the bipolar transistor, the metal-oxidesilicon ( MOS ) transistor was initially

difficult to manufacture because of problems with the oxide interface. As these problems

were gradually solved, metal-gate n -channel MOS ( nMOS or NMOS ) technology

developed in the 1970s. At that time MOS technology required fewer masking steps, was

denser, and consumed less power than equivalent bipolar ICs. This meant that, for a given

performance, an MOS IC was cheaper than a bipolar IC and led to investment and growth of

the MOS IC market.

VLSI DESIGN, ECEg 4201 5 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

By the early 1980s the aluminum gates of the transistors were replaced by

polysilicon gates, but the name MOS remained. The introduction of polysilicon as a gate

material was a major improvement in CMOS technology, making it easier to make two

types of transistors, n –channel MOS and p -channel MOS transistors, on the same IC—a

complementary MOS ( CMOS , never cMOS) technology. The principal advantage of CMOS

over NMOS is lower power consumption. Another advantage of a polysilicon gate was a

simplification of the fabrication process, allowing devices to be scaled down in size.

There are four CMOS transistors in a two-input NAND gate (and a two input NOR

gate too), so to convert between gates and transistors, you multiply the number of gates by

4 to obtain the number of transistors. We can also measure an IC by the smallest feature

size (roughly half the length of the smallest transistor) imprinted on the IC. Transistor

dimensions are measured in microns (a micron, 1 µm, is a millionth of a meter). Thus we

talk about a 0.5 µm IC or say an IC is built in (or with) a 0.5 µm process, meaning that the

smallest transistors are 0.5 µm in length. We give a special label, or lambda , to this

smallest feature size. Since lambda is equal to half of the smallest transistor length, 0.25 µm

in a 0.5 µm process. Many of the drawings in this book use a scale marked with lambda for

the same reason we place a scale on a map.

A modern submicron CMOS process is now just as complicated as a submicron

bipolar or BiCMOS (a combination of bipolar and CMOS) process. However, CMOS ICs have

established a dominant position, are manufactured in much greater volume than any other

technology, and therefore, because of the economy of scale, the cost of CMOS ICs is less

than a bipolar or BiCMOS IC for the same function. Bipolar and BiCMOS ICs arestill used for

special needs. For example, bipolar technology is generally capable of handling higher

voltages than CMOS. This makes bipolar and BiCMOS ICs useful in power electronics, cars,

telephone circuits, and so on.

Some digital logic ICs and their analog counterparts (analog/digital converters, for

example) are standard parts , or standard ICs. You can select standard ICs from catalogs

and data books and buy them from distributors. Systems manufacturers and designers can

use the same standard part in a variety of different microelectronic systems (systems

that use microelectronics or ICs).

With the advent of VLSI in the 1980s engineers began to realize the advantages of

designing an IC that was customized or tailored to a particular system or application rather

than using standard ICs alone. Microelectronic system design then becomes a matter of

defining the functions that you can implement using standard ICs and then implementing

the remaining logic functions (sometimes called glue logic) with one or more custom ICs.

As VLSI became possible you could build a system from a smaller number of components

by combining many standard ICs into a few custom ICs. Building a microelectronic system

with fewer ICs allows you to reduce cost and improve reliability.

Of course, there are many situations in which it is not appropriate to use a custom IC

for each and every part of a microelectronic system. If you need a large amount of memory,

for example, it is still best to use standard memory ICs, either dynamic random-access

VLSI DESIGN, ECEg 4201 6 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

memory ( DRAM or dRAM), or static RAM ( SRAM or sRAM), in conjunction with custom

ICs. One of the first conferences to be devoted to this rapidly emerging segment of the IC

industry was the IEEE Custom Integrated Circuits Conference (CICC), and the proceedings of

this annual conference form a useful reference to the development of custom ICs. As

different types of custom ICs began to evolve for different types of applications, these new

ICs gave rise to a new term: application-specific IC, or ASIC. Now we have the IEEE

International ASIC Conference , which tracks advances in ASICs separately from other types

of custom ICs. Although the exact definition of an ASIC is difficult, we shall look at some

examples to help clarify what people in the IC industry understand by the term.

Examples of ICs that are not ASICs include standard parts such as: memory chips

sold as a commodity item—ROMs, DRAM, and SRAM; microprocessors; TTL or TTL-

equivalent ICs at SSI, MSI, and LSI levels.

Examples of ICs that are ASICs include: a chip for a toy bear that talks; a chip for a

satellite; a chip designed to handle the interface between memory and a microprocessor for

a workstation CPU; and a chip containing a microprocessor as a cell together with other

logic.

As a general rule, if you can find it in a data book, then it is probably not an ASIC, but

there are some exceptions. For example, two ICs that might or might not be considered

ASICs are a controller chip for a PC and a chip for a modem. Both of these examples are

specific to an application (shades of an ASIC) but are sold to many different system vendors

(shades of a standard part). ASICs such as these are sometimes called application-specific

standard products ( ASSPs ).

Trying to decide which members of the huge IC family are application specific is

tricky—after all, every IC has an application. For example, people do not usually consider

an application-specific microprocessor to be an ASIC. I shall describe how to design an ASIC

that may include large cells such as microprocessors, but I shall not describe the design of

the microprocessors themselves. Defining an ASIC by looking at the application can be

confusing, so we shall look at a different way to categorize the IC family. The easiest way to

recognize people is by their faces and physical characteristics: tall, short, thin. The easiest

characteristics of ASICs to understand are physical ones too, and we shall look at these

next. It is important to understand these differences because they affect such factors as the

price of an ASIC and the way you design an ASIC.

Types of ASICs

ICs are made on a thin (a few hundred microns thick), circular silicon wafer, with

each wafer holding hundreds of die (sometimes people use dies or dice for the plural of

die). The transistors and wiring are made from many layers (usually between 10 and 15

distinct layers) built on top of one another. Each successive mask layer has a pattern that

is defined using a mask similar to a glass photographic slide. The first half-dozen or so

VLSI DESIGN, ECEg 4201 7 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

layers define the transistors. The last half-dozen or so layers define the metal wires

between the transistors (the interconnect).

A full-custom IC includes some (possibly all) logic cells that are customized and all

mask layers that are customized. A microprocessor is an example of a full- custom IC—

designers spend many hours squeezing the most out of every last square micron of

microprocessor chip space by hand. Customizing all of the IC features in this way allows

designers to include analog circuits, optimized memory cells, or mechanical structures on

an IC, for example. Full-custom ICs are the most expensive to manufacture and to design.

The manufacturing lead time (the time it takes just to make an IC not including design

time) is typically eight weeks for a full-custom IC. These specialized full-custom ICs are

often intended for a specific application, so we might call some of them full-custom ASICs.

We shall discuss full-custom ASICs briefly next, but the members of the IC family

that we are more interested in are semicustom ASICs, for which all of the logic cells are

predesigned and some (possibly all) of the mask layers are customized. Using predesigned

cells from a cell library makes our lives as designers much, much easier. There are two

types of semicustom ASICs that we shall cover: standard-cell–based ASICs and gate-array–

based ASICs. Following this we shall describe the programmable ASICs, for which all of

the logic cells are predesigned and none of the mask layers are customized. There are two

types of programmable ASICs: the programmable logic device and, the newest member of

the ASIC family, the field programmable gate array.

Full-Custom ASICs

In a full-custom ASIC an engineer designs some or all of the logic cells, circuits, or

layout specifically for one ASIC. This means the designer abandons the approach of using

pretested and pre-characterized cells for all or part of that design. It makes sense to take

this approach only if there are no suitable existing cell libraries available that can be used

for the entire design. This might be because existing cell libraries are not fast enough, or

the logic cells are not small enough or consume too much power. You may need to use full-

custom design if the ASIC technology is new or so specialized that there are no existing cell

libraries or because the ASIC is so specialized that some circuits must be custom designed.

Fewer and fewer full-custom ICs are being designed because of the problems with these

special parts of the ASIC. There is one growing member of this family, though, the mixed

analog/digital ASIC, which we shall discuss next.

Bipolar technology has historically been used for precision analog functions. There

are some fundamental reasons for this. In all integrated circuits the matching of component

characteristics between chips is very poor, while the matching of characteristics between

components on the same chip is excellent. Suppose we have transistors T1, T2, and T3 on

an analog/digital ASIC. The three transistors are all the same size and are constructed in an

identical fashion. Transistors T1 and T2 are located adjacent to each other and have the

same orientation. Transistor T3 is the same size as T1 and T2 but is located on the other

VLSI DESIGN, ECEg 4201 8 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

side of the chip from T1 and T2 and has a different orientation. ICs are made in batches

called wafer lots. A wafer lot is a group of silicon wafers that are all processed together.

Usually there are between 5 and 30 wafers in a lot. Each wafer can contain tens or

hundreds of chips depending on the size of the IC and the wafer.

If we were to make measurements of the characteristics of transistors T1,

T2, and T3 we would find the following:

Transistors T1 will have virtually identical characteristics to T2 on the same IC. We

say that the transistors match well or the tracking between devices is excellent.

Transistor T3 will match transistors T1 and T2 on the same IC very well, but not as

closely as T1 matches T2 on the same IC.

Transistor T1, T2, and T3 will match fairly well with transistors T1, T2, and T3 on a

different IC on the same wafer. The matching will depend on how far apart the two

ICs are on the wafer.

Transistors on ICs from different wafers in the same wafer lot will not match very

well.

Transistors on ICs from different wafer lots will match very poorly.

For many analog designs the close matching of transistors is crucial to circuit operation.

For these circuit designs pairs of transistors are used, located adjacent to each other.

Device physics dictates that a pair of bipolar transistors will always match more precisely

than CMOS transistors of a comparable size. Bipolar technology has historically been more

widely used for full-custom analog design because of its improved precision. Despite its

poorer analog properties, the use of CMOS technology for analog functions is increasing.

There are two reasons for this. The first reason is that CMOS is now by far the most widely

available IC technology. Many more CMOS ASICs and CMOS standard products are now

being manufactured than bipolar ICs. The second reason is that increased levels of

integration require mixing analog and digital functions on the same IC: this has forced

designers to find ways to use CMOS technology to implement analog functions. Circuit

designers, using clever new techniques, have been very successful in finding new ways to

design analog CMOS circuits that can approach the accuracy of bipolar analog designs.

Standard-Cell–Based ASICs

A cell-based ASIC (cell-based IC, or CBIC —a common term in Japan, pronounced

“sea-bick”) uses predesigned logic cells (AND gates, OR gates, multiplexers, and flip-flops,

for example) known as standard cells. We could apply the term CBIC to any IC that uses

cells, but it is generally accepted that a cell-based ASIC or CBIC means a standard-cell–

based ASIC.

The standard-cell areas (also called flexible blocks) in a CBIC are built of rows of

standard cells—like a wall built of bricks. The standard-cell areas may be used in

combination with larger predesigned cells, perhaps microcontrollers or even

microprocessors, known as mega cells. Mega-cells are also called mega-functions, full-

VLSI DESIGN, ECEg 4201 9 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

custom blocks, system-level macros (SLMs), fixed blocks, cores, or Functional Standard

Blocks (FSBs).

The ASIC designer defines only the placement of the standard cells and the interconnect in

a CBIC. However, the standard cells can be placed anywhere on the silicon; this means that

all the mask layers of a CBIC are customized and are unique to a particular customer. The

advantage of CBICs is that designers save time, money, and reduce risk by using a

predesigned, pretested, and pre-characterized standard-cell library. In addition each

standard cell can be optimized individually. During the design of the cell library each and

every transistor in every standard cell can be chosen to maximize speed or minimize area,

for example. The disadvantages are the time or expense of designing or buying the

standard-cell library and the time needed to fabricate all layers of the ASIC for each new

design.

FIGURE 1.2 A cell-based ASIC (CBIC) die with a single standard-cell area (a flexible block) together with

four fixed blocks. The flexible block contains rows of standard cells. This is what you might see through a

low-powered microscope looking down on the die of Figure 1.1(b). The small squares around the edge

of the die are bonding pads that are connected to the pins of the ASIC package.

Figure 1.2 shows a CBIC (looking down on the die shown in Figure 1.1b, for example). The

important features of this type of ASIC are as follows:

All mask layers are customized—transistors and interconnect.

Custom blocks can be embedded.

Manufacturing lead time is about eight weeks.

Each standard cell in the library is constructed using full-custom design methods, but

you can use these predesigned and pre-characterized circuits without having to do any full-

custom design yourself. This design style gives you the same performance and flexibility

advantages of a full-custom ASIC but reduces design time and reduces risk.

Standard cells are designed to fit together like bricks in a wall. Figure 1.3 shows an

example of a simple standard cell (it is simple in the sense it is not maximized for density—

VLSI DESIGN, ECEg 4201 10 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

but ideal for showing you its internal construction). Power and ground buses (VDD and

GND or VSS) run horizontally on metal lines inside the cells.

FIGURE 1.3 Looking down on the layout of a standard cell. This cell would be approximately 25 microns

wide on an ASIC with λ (lambda) = 0.25 microns (a micron is 10 –6 m). Standard cells are stacked like

bricks in a wall; the abutment box (AB) defines the “edges” of the brick. The difference between the

bounding box (BB) and the AB is the area of overlap between the bricks. Power supplies (labeled VDD

and GND) run horizontally inside a standard cell on a metal layer that lies above the transistor layers.

Each different shaded and labeled pattern represents a different layer. This standard cell has center

connectors (the three squares, labeled A1, B1, and Z) that allow the cell to connect to others. The layout

was drawn using ROSE, a symbolic layout editor developed by Rockwell and Compass, and then

imported into Tanner Research’s L-Edit.

Standard-cell design allows the automation of the process of assembling an ASIC.

Groups of standard cells fit horizontally together to form rows. The rows stack vertically to

form flexible rectangular blocks (which you can reshape during design). You may then

connect a flexible block built from several rows of standard cells to other standard-cell

blocks or other full custom logic blocks. For example, you might want to include a custom

interface to a standard, predesigned microcontroller together with some memory. The

microcontroller block may be a fixed-size mega-cell, you might generate the memory using

a memory compiler, and the custom logic and memory controller will be built from flexible

standard-cell blocks, shaped to fit in the empty spaces on the chip.

Both cell-based and gate-array ASICs use predefined cells, but there is a difference—

we can change the transistor sizes in a standard cell to optimize speed and performance,

but the device sizes in a gate array are fixed. This results in a trade-off in performance and

area in a gate array at the silicon level. The trade-off between area and performance is

made at the library level for a standard-cell ASIC.

VLSI DESIGN, ECEg 4201 11 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

Modern CMOS ASICs use two, three, or more levels (or layers) of metal for

interconnect. This allows wires to cross over different layers in the same way that we use

copper traces on different layers on a printed-circuit board. In a two-level metal CMOS

technology, connections to the standard-cell inputs and outputs are usually made using the

second level of metal ( metal2 , the upper level of metal) at the tops and bottoms of the

cells. In a three-level metal technology, connections may be internal to the logic cell (as

they are in Figure 1.3). This allows for more sophisticated routing programs to take

advantage of the extra metal layer to route interconnect over the top of the logic cells. We

shall cover the details of routing ASICs in Chapter 17.

A connection that needs to cross over a row of standard cells uses a feedthrough.

The term feedthrough can refer either to the piece of metal that is used to pass a signal

through a cell or to a space in a cell waiting to be used as a feedthrough—very confusing.

Figure 1.4 shows two feedthroughs: one in cell A.14 and one in cell A.23.

In both two-level and three-level metal technology, the power buses (VDD and GND)

inside the standard cells normally use the lowest (closest to the transistors) layer of metal (

metal1 ). The width of each row of standard cells is adjusted so that they may be aligned

using spacer cells . The power buses, or rails, are then connected to additional vertical

power rails using row-end cells at the aligned ends of each standard-cell block. If the rows

of standard cells are long, then vertical power rails can also be run in metal2 through the

cell rows using special power cells that just connect to VDD and GND. Usually the designer

manually controls the number and width of the vertical power rails connected to the

standard-cell blocks during physical design. A diagram of the power distribution scheme

for a CBIC is shown in Figure 1.4.

FIGURE 1.4 Routing the CBIC (cell-based IC) shown in Figure 1.2. The use of regularly shaped standard

cells, such as the one in Figure 1.3, from a library allows ASICs like this to be designed automatically.

This ASIC uses two separate layers of metal interconnect (metal1 and metal2) running at right angles to

each other (like traces on a printed-circuit board). Interconnections between logic cells uses spaces

(called channels) between the rows of cells. ASICs may have three (or more) layers of metal allowing the

cell rows to touch with the interconnect running over the top of the cells.

VLSI DESIGN, ECEg 4201 12 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

All the mask layers of a CBIC are customized. This allows mega-cells (SRAM, a SCSI

controller, or an MPEG decoder, for example) to be placed on the same IC with standard

cells. Mega-cells are usually supplied by an ASIC or library company complete with

behavioral models and some way to test them (a test strategy). ASIC library companies also

supply compilers to generate flexible DRAM, SRAM, and ROM blocks. Since all mask layers

on a standard-cell design are customized, memory design is more efficient and denser than

for gate arrays.

For logic that operates on multiple signals across a data bus—a datapath (DP )—

the use of standard cells may not be the most efficient ASIC design style. Some ASIC library

companies provide a datapath compiler that automatically generates datapath logic. A

datapath library typically contains cells such as adders, subtracters, multipliers, and

simple arithmetic and logical units (ALUs). The connectors of datapath library cells are

pitch-matched to each other so that they fit together. Connecting datapath cells to form a

datapath usually, but not always, results in faster and denser layout than using standard

cells or a gate array.

Standard-cell and gate-array libraries may contain hundreds of different logic cells,

including combinational functions (NAND, NOR, AND, OR gates) with multiple inputs, as

well as latches and flip-flops with different combinations of reset, preset and clocking

options. The ASIC library company provides designers with a data book in paper or

electronic form with all of the functional descriptions and timing information for each

library element.

Gate-Array–Based ASICs

In a gate array (sometimes abbreviated to GA) or gate-array–based ASIC the

transistors are predefined on the silicon wafer. The predefined pattern of transistors on a

gate array is the base array, and the smallest element that is replicated to make the base

array (like an M. C. Escher drawing, or tiles on a floor) is the base cell sometimes called a

primitive cell ). Only the top few layers of metal, which define the interconnect between

transistors, are defined by the designer using custom masks. To distinguish this type of

gate array from other types of gate array, it is often called a masked gate array (MGA).

The designer chooses from a gate-array library of predesigned and pre-characterized logic

cells. The logic cells in a gate-array library are often called macros. The reason for this is

that the base-cell layout is the same for each logic cell, and only the interconnect (inside

cells and between cells) is customized, so that there is a similarity between gate-array

macros and a software macro. Inside IBM, gate-array macros are known as books (so that

books are part of a library), but unfortunately this descriptive term is not very widely used

outside IBM.

We can complete the diffusion steps that form the transistors and then stockpile

wafers (sometimes we call a gate array a pre-diffused array for this reason). Since only

VLSI DESIGN, ECEg 4201 13 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

the metal interconnections are unique to an MGA, we can use the stockpiled wafers for

different customers as needed. Using wafers prefabricated up to the metallization steps

reduces the time needed to make an MGA, the turnaround time , to a few days or at most a

couple of weeks. The costs for all the initial fabrication steps for an MGA are shared for

each customer and this reduces the cost of an MGA compared to a full-custom or standard-

cell ASIC design.

There are the following different types of MGA or gate-array–based

ASICs:

Channeled gate arrays.

Channel-less gate arrays.

Structured gate arrays.

The hyphenation of these terms when they are used as adjectives explains their

construction. For example, in the term “channeled gate-array architecture,” the gate array

is channeled, as will be explained. There are two common ways of arranging (or arraying)

the transistors on a MGA: in a channeled gate array we leave space between the rows of

transistors for wiring; the routing on a channel-less gate array uses rows of unused

transistors. The channeled gate array was the first to be developed, but the channel-less

gate-array architecture is now more widely used. A structured (or embedded) gate array

can be either channeled or channel-less but it includes (or embeds) a custom block.

a) Channeled Gate Array

Figure 1.5 shows a channeled gate array. The important features of this type of MGA are:

Only the interconnect is customized.

The interconnect uses predefined spaces between rows of base cells.

Manufacturing lead time is between two days and two weeks.

FIGURE 1.5 A channeled gate-array die. The spaces between rows of the base cells are set aside for

interconnect.

VLSI DESIGN, ECEg 4201 14 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

A channeled gate array is similar to a CBIC—both use rows of cells separated by

channels used for interconnect. One difference is that the space for interconnect between

rows of cells are fixed in height in a channeled gate array, whereas the space between rows

of cells may be adjusted in a CBIC.

b) Channel-less Gate Array

Figure 1.6 shows a channel-less gate array (also known as a channel-free gate array ,

sea-of-gates array , or SOG array). The important features of this type of MGA are as

follows:

Only some (the top few) mask layers are customized—the interconnect.

Manufacturing lead time is between two days and two weeks.

The key difference between a channel-less gate array and channeled gate array is

that there are no predefined areas set aside for routing between cells on a channel-less gate

array. Instead we route over the top of the gate-array devices. We can do this because we

customize the contact layer that defines the connections between metal1, the first layer of

metal, and the transistors. When we use an area of transistors for routing in a channel-less

array, we do not make any contacts to the devices lying underneath; we simply leave the

transistors unused.

FIGURE 1.6 A channel-less gate-array or sea-of-gates (SOG) array die. The core area of the die is

completely filled with an array of base cells (the base array).

The logic density—the amount of logic that can be implemented in a given silicon

area—is higher for channel-less gate arrays than for channeled gate arrays. This is usually

attributed to the difference in structure between the two types of array. In fact, the

difference occurs because the contact mask is customized in a channel-less gate array, but

is not usually customized in a channeled gate array. This leads to denser cells in the

channel-less architectures. Customizing the contact layer in a channel-less gate array

allows us to increase the density of gate-array cells because we can route over the top of

unused contact sites.

VLSI DESIGN, ECEg 4201 15 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

c) Structured Gate Array

An embedded gate array or structured gate array (also known as master-slice

or master-image ) combines some of the features of CBICs and MGAs. One of the

disadvantages of the MGA is the fixed gate-array base cell. This makes the implementation

of memory, for example, difficult and inefficient. In an embedded gate array we set aside

some of the IC area and dedicate it to a specific function. This embedded area either can

contain a different base cell that is more suitable for building memory cells, or it can

contain a complete circuit block, such as a microcontroller.

Figure 1.7 shows an embedded gate array. The important features of this type of MGA are

the following:

Only the interconnect is customized.

Custom blocks (the same for each design) can be embedded.

Manufacturing lead time is between two days and two weeks.

An embedded gate array gives the improved area efficiency and increased

performance of a CBIC but with the lower cost and faster turnaround of an MGA. One

disadvantage of an embedded gate array is that the embedded function is fixed. For

example, if an embedded gate array contains an area set aside for a 32 k-bit memory, but

we only need a 16 k-bit memory, then we may have to waste half of the embedded memory

function. However, this may still be more efficient and cheaper than implementing a 32 k-

bit memory using macros on a SOG array.

FIGURE 1.7 A structured or embedded gate-array die showing an embedded block in the upper left

corner (a static random-access memory, for example). The rest of the die is filled with an array of base

cells.

ASIC vendors may offer several embedded gate array structures containing different

memory types and sizes as well as a variety of embedded functions. ASIC companies

wishing to offer a wide range of embedded functions must ensure that enough customers

use each different embedded gate array to give the cost advantages over a custom gate

VLSI DESIGN, ECEg 4201 16 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

array or CBIC (the Sun Microsystems SPARCstation 1 described in Section 1.3 made use of

LSI Logic embedded gate arrays—and the 10K and 100K series of embedded gate arrays

were two of LSI Logic’s most successful products).

Programmable Logic Devices

Programmable logic devices (PLDs) are standard ICs that are available in standard

configurations from a catalog of parts and are sold in very high volume to many different

customers. However, PLDs may be configured or programmed to create a part customized

to a specific application, and so they also belong to the family of ASICs. PLDs use different

technologies to allow programming of the device. Figure 1.8 shows a PLD and the following

important features that all PLDs have in common:

No customized mask layers or logic cells

Fast design turnaround

A single large block of programmable interconnect

A matrix of logic macro-cells that usually consist of programmable array logic followed by a

flip-flop or latch

FIGURE 1.8 A programmable logic device (PLD) die. The macro-cells typically consist of programmable

array logic followed by a flip-flop or latch. The macro-cells are connected using a large programmable

interconnect block.

The simplest type of programmable IC is a read-only memory (ROM). The most

common types of ROM use a metal fuse that can be blown permanently (a Programmable

ROM or PROM). An electrically programmable ROM, or EPROM, uses programmable

MOS transistors whose characteristics are altered by applying a high voltage. You can erase

an EPROM either by using another high voltage (an electrically erasable PROM, or

EEPROM) or by exposing the device to ultraviolet light (UV Erasable PROM, or UVPROM).

There is another type of ROM that can be placed on any ASIC—a mask

programmable ROM (mask-programmed ROM or masked ROM). A masked ROM is a

VLSI DESIGN, ECEg 4201 17 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

regular array of transistors permanently programmed using custom mask patterns. An

embedded masked ROM is thus a large, specialized, logic cell.

The same programmable technologies used to make ROMs can be applied to more

flexible logic structures. By using the programmable devices in a large array of AND gates

and an array of OR gates, we create a family of flexible and programmable logic devices

called logic arrays. The company Monolithic Memories (bought by AMD) was the first to

produce Programmable Array Logic (PAL, a registered trademark of AMD) devices that

you can use, for example, as transition decoders for state machines. A PAL can also include

registers (flip-flops) to store the current state information so that you can use a PAL to

make a complete state machine. Just as we have a mask-programmable ROM, we could

place a logic array as a cell on a custom ASIC. This type of logic array is called a

programmable logic array (PLA). There is a difference between a PAL and a PLA: a PLA

has a programmable AND logic array, or AND plane, followed by a programmable OR logic

array, or OR plane; a PAL has a programmable AND plane and, in contrast to a PLA, a fixed

OR plane.

Depending on how the PLD is programmed, we can have an erasable PLD (EPLD),

or mask-programmed PLD (sometimes called a masked PLD but usually just PLD). The

first PALs, PLAs, and PLDs were based on bipolar technology and used programmable fuses

or links. CMOS PLDs usually employ floating-gate transistors (see Section 4.3, “EPROM and

EEPROM Technology”).

Field-Programmable Gate Arrays

A step above the PLD in complexity is the field-programmable gate array (FPGA ).

There is very little difference between an FPGA and a PLD—an FPGA is usually just larger

and more complex than a PLD. In fact, some companies that manufacture programmable

ASICs call their products FPGAs and some call them complex PLDs . FPGAs are the newest

member of the ASIC family and are rapidly growing in importance, replacing TTL in

microelectronic systems. Even though an FPGA is a type of gate array, we do not consider

the term gate-array–based ASICs to include FPGAs. This may change as FPGAs and MGAs

start to look more alike.

Figure 1.9 illustrates the essential characteristics of an FPGA:

None of the mask layers are customized.

A method for programming the basic logic cells and the interconnect.

The core is a regular array of programmable basic logic cells that can implement

combinational as well as sequential logic (flip-flops).

A matrix of programmable interconnect surrounds the basic logic cells.

Programmable I/O cells surround the core.

Design turnaround is a few hours.

VLSI DESIGN, ECEg 4201 18 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

FIGURE 1.9 A field-programmable gate array (FPGA) die. All FPGAs contain a regular structure of

programmable basic logic cells surrounded by programmable interconnect. The exact type, size, and

number of the programmable basic logic cells varies tremendously.

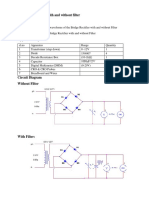

Design Flow

Figure 1.10 shows the sequence of steps to design an ASIC; we call this a design flow. The

steps are listed below (numbered to correspond to the labels in Figure 1.10) with a brief

description of the function of each step.

FIGURE 1.10 ASIC design flow.

1. Design entry. Enter the design into an ASIC design system, either using a Hardware

description language (HDL) or schematic entry.

VLSI DESIGN, ECEg 4201 19 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

2. Logic synthesis. Use an HDL (VHDL or Verilog) and a logic synthesis tool to produce a

netlist —a description of the logic cells and their connections.

3. System partitioning. Divide a large system into ASIC-sized pieces.

4. Pre-layout simulation. Check to see if the design functions correctly.

5. Floor planning. Arrange the blocks of the netlist on the chip.

6. Placement. Decide the locations of cells in a block.

7. Routing. Make the connections between cells and blocks.

8. Extraction. Determine the resistance and capacitance of the interconnect.

9. Post-layout simulation. Check to see the design still works with the added loads of

the interconnect.

Steps 1–4 are part of logical design, and steps 5–9 are part of physical design. There is

some overlap. For example, system partitioning might be considered as either logical or

physical design. To put it another way, when we are performing system partitioning we

have to consider both logical and physical factors.

VLSI DESIGN, ECEg 4201 20 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

MOS Transistors

Silicon (Si), a semiconductor, forms the basic starting material for most integrated

circuits [Tsividis99]. Pure silicon consists of a three-dimensional lattice of atoms. Silicon is

a Group IV element, so it forms covalent bonds with four adjacent atoms, as shown in

Figure 1.11(a). The lattice is shown in the plane for ease of drawing, but it actually forms a

cubic crystal. As all of its valence electrons are involved in chemical bonds, pure silicon is a

poor conductor. The conductivity can be raised by introducing small amounts of impurities,

called dopants, into the silicon lattice. A dopant from Group V of the periodic table, such as

arsenic, has five valence electrons. It replaces a silicon atom in the lattice and still bonds to

four neighbors, so the fifth valence electron is loosely bound to the arsenic atom, as shown

in Figure 1.11(b). Thermal vibration of the lattice at room temperature is enough to set the

electron free to move, leaving a positively charged As+ ion and a free electron. The free

electron can carry current so the conductivity is higher. We call this an n-type

semiconductor because the free carriers are negatively charged electrons. Similarly, a

Group III dopant, such as boron, has three valence electrons, as shown in Figure 1.11(c).

The dopant atom can borrow an electron from a neighboring silicon atom, which in turn

becomes short by one electron. That atom in turn can borrow an electron, and so forth, so

the missing electron, or hole, can propagate about the lattice. The hole acts as a positive

carrier so we call this a p-type semiconductor.

FIGURE 1.11 Silicon Lattice & Dopant Atoms

A junction between p-type and n-type silicon is called a diode, as shown in Figure

1.12. When the voltage on the p-type semiconductor, called the anode, is raised above the

n-type cathode, the diode is forward biased and current flows. When the anode voltage is

less than or equal to the cathode voltage, the diode is reverse biased and very little current

flows. A Metal-Oxide-Semiconductor (MOS) structure is created by superimposing several

layers of conducting and insulating materials to form a sandwich-like structure. These

structures are manufactured using a series of chemical processing steps involving

oxidation of the silicon, selective introduction of dopants, and deposition and etching of

metal wires and contacts. Transistors are built on nearly flawless single crystals of silicon,

which are available as thin flat circular wafers of 15–30 cm in diameter. CMOS technology

provides two types of transistors (also called devices): an n-type transistor (nMOS) and a p-

VLSI DESIGN, ECEg 4201 21 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

type transistor (pMOS). Transistor operation is controlled by electric fields so the devices

are also called Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) or simply

FETs.

FIGURE 1.12 pn Junction Diode Structure & Symbol

Cross-sections and symbols of these transistors are shown in Figure 1.13 The n+

and p+ regions indicate heavily doped n- or p-type silicon.

FIGURE 1.13 a) nMOS Transistor and b) pMOS Transistor

Each transistor consists of a stack of the conducting gate, an insulating layer of

silicon dioxide (SiO2, better known as glass), and the silicon wafer, also called the substrate,

body, or bulk. Gates of early transistors were built from metal, so the stack was called metal

oxide-semiconductor, or MOS. Since the 1970s, the gate has been formed from

polycrystalline silicon (polysilicon), but the name stuck. (Interestingly, metal gates

reemerged in 2007 to solve materials problems in advanced manufacturing processes.) An

nMOS transistor is built with a p-type body and has regions of n-type semiconductor

adjacent to the gate called the source and drain. They are physically equivalent and for now

we will regard them as interchangeable. The body is typically grounded. A pMOS transistor

is just the opposite, consisting of p-type source and drain regions with an n-type body. In a

CMOS technology with both flavors of transistors, the substrate is either n-type or p-type.

VLSI DESIGN, ECEg 4201 22 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

The other flavor of transistor must be built in a special well in which dopant atoms have

been added to form the body of the opposite type.

The gate is a control input: It affects the flow of electrical current between the

source and drain. Consider an nMOS transistor. The body is generally grounded so the p–n

junctions of the source and drain to body are reverse-biased. If the gate is also grounded,

no current flows through the reverse-biased junctions. Hence, we say the transistor is OFF.

If the gate voltage is raised, it creates an electric field that starts to attract free electrons to

the underside of the Si–SiO2 interface. If the voltage is raised enough, the electrons

outnumber the holes and a thin region under the gate called the channel is inverted to act

as an n-type semiconductor. Hence, a conducting path of electron carriers is formed from

source to drain and current can flow. We say the transistor is ON.

For a pMOS transistor, the situation is again reversed. The body is held at a positive

voltage. When the gate is also at a positive voltage, the source and drain junctions are

reverse-biased and no current flows, so the transistor is OFF. When the gate voltage is

lowered, positive charges are attracted to the underside of the Si–SiO2 interface. A

sufficiently low gate voltage inverts the channel and a conducting path of positive carriers

is formed from source to drain, so the transistor is ON. Notice that the symbol for the pMOS

transistor has a bubble on the gate, indicating that the transistor behavior is the opposite of

the nMOS.

The positive voltage is usually called VDD or POWER and represents logic 1 value in

digital circuits. In popular logic families of the 1970s and 1980s, VDD was set to 5 volts.

Smaller, more recent transistors are unable to withstand such high voltages and have used

supplies of 3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V, 1.0 V, and so forth. The low voltage is called

GROUND (GND) or VSS and represents logic 0. It is normally 0 volts.

In summary, the gate of an MOS transistor controls the flow of current between the

source and drain. Simplifying this to the extreme allows the MOS transistors to be viewed

as simple ON/OFF switches. When the gate of an nMOS transistor is 1, the transistor is ON

and there is a conducting path from source to drain. When the gate is low, the nMOS

transistor is OFF and almost zero current flows from source to drain. A pMOS transistor is

just the opposite, being ON when the gate is low and OFF when the gate is high. This switch

model is illustrated in Figure 1.14, where g, s, and d indicate gate, source, and drain. This

model will be our most common one when discussing circuit behavior.

VLSI DESIGN, ECEg 4201 23 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

FIGURE 1.14 Transistor Symbols & Switch Level Models

CMOS LOGIC

The Inverter

FIGURE 1.15 a) Inverter Schematic and b) Symbol = ̅

Figure 1.15 shows the schematic and symbol for a CMOS inverter or NOT gate using

one nMOS transistor and one pMOS transistor. The bar at the top indicates VDD and the

triangle at the bottom indicates GND. When the input A is 0, the nMOS transistor is OFF and

the pMOS transistor is ON. Thus, the output Y is pulled up to 1 because it is connected to

VDD but not to GND. Conversely, when A is 1, the nMOS is ON, the pMOS is OFF, and Y is

pulled down to ‘0.’ This is summarized in Table 1.1.

TABLE 1.1 Inverter Truth Table

VLSI DESIGN, ECEg 4201 24 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

The NAND Gate

FIGURE 1.16 a) 2 input NAND Gate Schematic and b) Symbol = ∙

Figure 1.16(a) shows a 2-input CMOS NAND gate. It consists of two series nMOS

transistors between Y and GND and two parallel pMOS transistors between Y and VDD. If

either input A or B is 0, at least one of the nMOS transistors will be OFF, breaking the path

from Y to GND. But at least one of the pMOS transistors will be ON, creating a path from Y to

VDD. Hence, the output Y will be 1. If both inputs are 1, both of the nMOS transistors will be

ON and both of the pMOS transistors will be OFF. Hence, the output will be 0. The truth

table is given in Table 1.2 and the symbol is shown in Figure 1.16(b). Note that by

DeMorgan’s Law, the inversion bubble may be placed on either side of the gate. In the

figures in this book, two lines intersecting at a T-junction are connected. Two lines crossing

are connected if and only if a dot is shown.

TABLE 1.1 NAND Gate Truth Table

k - input NAND gates are constructed using k series nMOS transistors and k parallel

pMOS transistors. For example, a 3-input NAND gate is shown in Figure 1.17. When any of

the inputs are 0, the output is pulled high through the parallel pMOS transistors. When all

of the inputs are 1, the output is pulled low through the series nMOS transistors.

VLSI DESIGN, ECEg 4201 25 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

FIGURE 1.17 3 input NAND Gate Schematic = ∙ ∙

The CMOS Logic Gates

The inverter and NAND gates are examples of static CMOS logic gates, also called

complementary CMOS gates. In general, a static CMOS gate has an nMOS pull-down network

to connect the output to 0 (GND) and pMOS pull-up network to connect the output to 1

(VDD), as shown in Figure 1.18. The networks are arranged such that one is ON and the

other OFF for any input pattern.

FIGURE 1.18 General Logic Gates Using Pull Up & Pull Down Networks

The pull-up and pull-down networks in the inverter each consist of a single

transistor. The NAND gate uses a series pull-down network and a parallel pull-up network.

More elaborate networks are used for more complex gates. Two or more transistors in

series are ON only if all of the series transistors are ON. Two or more transistors in parallel

are ON if any of the parallel transistors are ON. This is illustrated in Figure 1.19 for nMOS

and pMOS transistor pairs. By using combinations of these constructions, CMOS

combinational gates can be constructed.

VLSI DESIGN, ECEg 4201 26 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

FIGURE 1.19 Connection & Behavior of Series & Parallel Transistors.

In general, when we join a pull-up network to a pull-down network to form a logic

gate as shown in Figure 1.18, they both will attempt to exert a logic level at the output. The

possible levels at the output are shown in Table 1.3. From this table it can be seen that the

output of a CMOS logic gate can be in four states. The 1 and 0 levels have been encountered

with the inverter and NAND gates, where either the pull-up or pull-down is OFF or the

other structure is ON. When both pull-up and pull-down are OFF, the high impedance or

floating Z output state results. This is of importance in multiplexers, memory elements, and

tri-state bus drivers. The crow barred (or contention) X level exists when both pull-up and

pull-down are simultaneously turned ON. Contention between the two networks results in

an indeterminate output level and dissipates static power. It is usually an unwanted

condition.

VLSI DESIGN, ECEg 4201 27 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

TABLE 1.3 Output States of CMOS Logic Gates.

The NOR Gate

FIGURE 1.20 2 Input NOR Gate a) Schematic and b) Symbol = +

A 2-input NOR gate is shown in Figure 1.20. The nMOS transistors are in parallel to

pull the output low when either input is high. The pMOS transistors are in series to pull the

output high when both inputs are low, as indicated in Table 1.4. The output is never crow-

barred or left floating.

TABLE 1.4 NOR Gate Truth Table

Compound Gates

A compound gate performing a more complex logic function in a single stage of logic

is formed by using a combination of series and parallel switch structures. For example, the

VLSI DESIGN, ECEg 4201 28 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

derivation of the circuit for the function = ( · ) + ( · ) is shown in Figure 1.21.

This function is sometimes called AND-OR-INVERT-22, or AOI22 because it performs the

NOR of a pair of 2-input ANDs. For the nMOS pull-down network, take the un inverted

expression ((A · B) + (C · D)) indicating when the output should be pulled to ‘0.’ The AND

expressions (A · B) and (C · D) may be implemented by series connections of switches, as

shown in Figure 1.21(a). Now ORing the result requires the parallel connection of these

two structures, which is shown in Figure 1.21(b). For the pMOS pull-up network, we must

compute the complementary expression using switches that turn on with inverted polarity.

By DeMorgan’s Law, this is equivalent to interchanging AND and OR operations. Hence,

transistors that appear in series in the pull-down network must appear in parallel in the

pull-up network. Transistors that appear in parallel in the pulldown network must appear

in series in the pull-up network. This principle is called conduction complements and has

already been used in the design of the NAND and NOR gates. In the pull-up network, the

parallel combination of A and B is placed in series with the parallel combination of C and D.

This progression is evident in Figure 1.21(c) and Figure 1.21(d). Putting the networks

together yields the full schematic (Figure 1.21(e)). The symbol is shown in Figure 1.21(f ).

FIGURE 1.21 CMOS Compound Gate for Function = ( · )+( · )

VLSI DESIGN, ECEg 4201 29 ROOHA RAZMID AHAMED

DEPT. OF ELECTRICAL & COMPUTER ENGINEERING

DIRE DAWA INSTITUTE OF TECHNOLOGY

DIRE DAWA UNIVERSITY

REFERENCES

Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic, Digital Integrated Circuits A Design Perspective, 2nd

edition

M. Smith, Application-Specific Integrated Circuits, Addison-Wesley, 1997.

Neil H Weste, David Harris, CMOS VLSI Design, A Circuits & Systems Perspective, 3rd Edition, Pearson Education

[Swade93] D. Swade, “Redeeming Charles Babbage’s Mechanical Computer,” Scientific American,pp. 86–91,

February 1993

[Bardeen48] J. Bardeen and W. Brattain, “The Transistor, a Semiconductor Triode,” Phys. Rev., vol. 74, p. 230, July

15, 1948.

[Schockley49] W. Schockley, “The Theory of pn Junctions in Semiconductors and pn-Junction Transistors,” BSTJ,

vol. 28, p. 435, 1949.

[Harris56] J. Harris, “Direct-Coupled Transistor Logic Circuitry in Digital Computers,” ISSCCDigest of Technical

Papers, p. 9, Feb. 1956.

[Norman60] R. Norman, J. Last and I. Haas, “Solid-State Micrologic Elements,” ISSCC Digest of Technical Papers,

pp. 82–83, Feb. 1960.

[Beeson62] R. Beeson and H. Ruegg, “New Forms of All Transistor Logic,” ISSCC Digest of Technical Papers, pp.

10–11, Feb. 1962.

[Masaki74] A. Masaki, Y. Harada and T. Chiba, “200-Gate ECL Master-Slice LSI,” ISSCC Digest of Technical Papers,

pp. 62–63, Feb. 1974.

[Hart72] C. Hart and M. Slob, “Integrated Injection Logic—A New Approach to LSI,” ISSCC Digest of Technical

Papers, pp. 92–93, Feb. 1972.

[Wanlass63] F. Wanlass, and C. Sah, “Nanowatt logic Using Field-Effect Metal-Oxide Semiconductor Triodes,”

ISSCC Digest of Technical Papers, pp. 32–32, Feb. 1963.

[Faggin72] F. Faggin, M.E. Hoff, Jr, H. Feeney, S. Mazor, M. Shima, “The MCS-4 - An LSI Micro-Computer System,”

1972 IEEE Region Six Conference Record, San Diego, CA, April 19-21, 1972, pp.1-6.

[Shima74] M. Shima, F. Faggin and S. Mazor, “An N-Channel, 8-bit Single-Chip Microprocessor,” ISSCC Digest of

Technical Papers, pp. 56–57, Feb. 1974.

[Hoff70] E. Hoff, “Silicon-Gate Dynamic MOS Crams 1,024 Bits on a Chip,” Electronics, pp. 68–73, August 3, 1970.

[Tsividis99] Y. Tsividis, Operation and Modeling of the MOS Transistor, 2nd ed., Boston: McGraw-Hill, 1999.

VLSI DESIGN, ECEg 4201 30 ROOHA RAZMID AHAMED

Potrebbero piacerti anche

- Sample For Solution Manual Starting Out With Python 4th Global Edition by Tony GaddisDocumento32 pagineSample For Solution Manual Starting Out With Python 4th Global Edition by Tony Gaddismina starNessuna valutazione finora

- A Position Paper About Using Cellphone in ClassDocumento3 pagineA Position Paper About Using Cellphone in ClassCristine Joy Remerata Villarosa89% (47)

- Chapter 1-Introduction To The Semiconductor Industry-NEWDocumento28 pagineChapter 1-Introduction To The Semiconductor Industry-NEWhrrameshhrNessuna valutazione finora

- VSFlex Grid 8 Manual 2007Documento288 pagineVSFlex Grid 8 Manual 2007tutunamayanlar1Nessuna valutazione finora

- EC8791 Embedded and Real Time SystemsDocumento78 pagineEC8791 Embedded and Real Time SystemsSivagami ManiNessuna valutazione finora

- VLSI Introduction and Urdhva Tiryagbhyam MultiplierDocumento35 pagineVLSI Introduction and Urdhva Tiryagbhyam MultiplierSneha GurrapuNessuna valutazione finora

- Analog & Digital VLSI Design: A Perspective EE C443 Instructor-In-ChargeDocumento21 pagineAnalog & Digital VLSI Design: A Perspective EE C443 Instructor-In-ChargeAnurag LaddhaNessuna valutazione finora

- Chapter-1 Introduction To Vlsi: 1.1 Very-Large-Scale IntegrationDocumento65 pagineChapter-1 Introduction To Vlsi: 1.1 Very-Large-Scale IntegrationAnonymous oowcaAhZ2Nessuna valutazione finora

- VLSI Study Material Guide to Integrated CircuitsDocumento167 pagineVLSI Study Material Guide to Integrated CircuitsAgnibha Dasgupta100% (1)

- Very Large Scale IntegrationDocumento3 pagineVery Large Scale IntegrationGowtham SpNessuna valutazione finora

- Chapter - 1: Ece Department, AcoeDocumento55 pagineChapter - 1: Ece Department, AcoeSana SriRamyaNessuna valutazione finora

- VLSI ProcessorsDocumento11 pagineVLSI ProcessorsJunaid AwanNessuna valutazione finora

- New Microsoft Word DocumentDocumento3 pagineNew Microsoft Word DocumentSannena GovindaNessuna valutazione finora

- Reducing The Hardware Complexity of A Parallel Prefix AdderDocumento57 pagineReducing The Hardware Complexity of A Parallel Prefix AdderKS Reddy KummithiNessuna valutazione finora

- Introduction To VLSI - VHDLDocumento14 pagineIntroduction To VLSI - VHDLsri.arivazhaganNessuna valutazione finora

- VLSI Design MethodologyDocumento72 pagineVLSI Design MethodologyMandovi BorthakurNessuna valutazione finora

- Digital Circuit Design TrendsDocumento5 pagineDigital Circuit Design TrendsnagarajuNessuna valutazione finora

- How We Made The MicroprocessorDocumento1 paginaHow We Made The MicroprocessorkzeipiNessuna valutazione finora

- Digital Circuits TrendsDocumento6 pagineDigital Circuits TrendsTravis BerkNessuna valutazione finora

- 02 Introduction To VLSI and ASIC DesignDocumento23 pagine02 Introduction To VLSI and ASIC DesignSiva Kumar T SNessuna valutazione finora

- Workshop # 4 Integrated Circuits: Universidad Nueva Esparta Electronic Engineering 254UDocumento4 pagineWorkshop # 4 Integrated Circuits: Universidad Nueva Esparta Electronic Engineering 254UDanielle CTNessuna valutazione finora

- Very-Large-Scale Integration - Wikipedia, The Free EncyclopediaDocumento4 pagineVery-Large-Scale Integration - Wikipedia, The Free EncyclopediaSuneelkrishna RallabhandiNessuna valutazione finora

- Digital ElectronicsDocumento12 pagineDigital ElectronicsTony GonzalezNessuna valutazione finora

- Integrated Circuits ExplainedDocumento30 pagineIntegrated Circuits ExplainedergerNessuna valutazione finora

- Unit I - VlsiDocumento40 pagineUnit I - VlsiIsmartNessuna valutazione finora

- APB Protocol Design Chapter 1 IntroductionDocumento48 pagineAPB Protocol Design Chapter 1 IntroductionVinay kumarNessuna valutazione finora

- Floating Point MultiplierDocumento35 pagineFloating Point Multiplierbindu_ankuNessuna valutazione finora

- Comparison Between Linear and Digital, by AnishDocumento15 pagineComparison Between Linear and Digital, by AnishAnish Dungeon100% (2)

- Vlsi Design: Machmud EffendyDocumento25 pagineVlsi Design: Machmud EffendyVaruliana AzariaNessuna valutazione finora

- Digital Electronics: An Introduction to Digital Circuits and DesignDocumento7 pagineDigital Electronics: An Introduction to Digital Circuits and DesignYunior DagaNessuna valutazione finora

- History: Digital Electronics, Digital Technology or Digital (Electronic) Circuits Are Electronics ThatDocumento16 pagineHistory: Digital Electronics, Digital Technology or Digital (Electronic) Circuits Are Electronics ThatYunior DagaNessuna valutazione finora

- Development in Integrated CircuitsDocumento6 pagineDevelopment in Integrated CircuitsRahul PanwarNessuna valutazione finora

- Introduction To VLSI TechnologyDocumento19 pagineIntroduction To VLSI TechnologyVikas KumarNessuna valutazione finora

- A Historical Perspective of Digital Systems EvolutionDocumento31 pagineA Historical Perspective of Digital Systems EvolutionMvZ509Nessuna valutazione finora

- Adapted From Class Notes of D. Patterson and W. DallyDocumento45 pagineAdapted From Class Notes of D. Patterson and W. Dallyarlenebareno100% (1)

- Chapter 1Documento20 pagineChapter 1danielNessuna valutazione finora

- The History of Microprocessor PDFDocumento28 pagineThe History of Microprocessor PDFTharjaNessuna valutazione finora

- VLSI Design Lab NewDocumento45 pagineVLSI Design Lab NewmtariqanwarNessuna valutazione finora

- Transistor Cpus: Transistor Mainframes Minicomputers Integrated Circuit NanometersDocumento3 pagineTransistor Cpus: Transistor Mainframes Minicomputers Integrated Circuit NanometersfunmastiNessuna valutazione finora

- Departement of Electronics & Communication EngineeringDocumento18 pagineDepartement of Electronics & Communication EngineeringBrajesh KumarNessuna valutazione finora

- Digital ElectronicsDocumento13 pagineDigital ElectronicsVíctor Alfonso Medina LugoNessuna valutazione finora

- Very Large Scale IntegrationDocumento4 pagineVery Large Scale IntegrationballisticanaNessuna valutazione finora

- PDFDocumento39 paginePDFtrupti100% (2)

- Jayapradha VLSI DesignDocumento200 pagineJayapradha VLSI DesignSatyam Kumar VermaNessuna valutazione finora

- VlsiDocumento12 pagineVlsiJaya SwaroopNessuna valutazione finora

- Optical Computing: A Solution to Miniaturization ProblemsDocumento4 pagineOptical Computing: A Solution to Miniaturization ProblemsAnirudha M VNessuna valutazione finora

- Digital Electronics or Digital (Electronic) Circuits AreDocumento11 pagineDigital Electronics or Digital (Electronic) Circuits AreRam MurthyNessuna valutazione finora

- CHAPTER 1 Basic Ideas of Scientific ComputingDocumento7 pagineCHAPTER 1 Basic Ideas of Scientific ComputingArif AliNessuna valutazione finora

- Digital ElectronicsDocumento13 pagineDigital ElectronicsPranitdhanadeNessuna valutazione finora

- Microelectronics Journal: Ioannis Vourkas, Georgios Ch. SirakoulisDocumento12 pagineMicroelectronics Journal: Ioannis Vourkas, Georgios Ch. Sirakouliseng_abdelghany1979Nessuna valutazione finora

- From Sand To Silicon "An Eagle View of Chip Making"Documento36 pagineFrom Sand To Silicon "An Eagle View of Chip Making"DHANAGOPAL R DHANAGOPAL RNessuna valutazione finora

- Ece Board Exam Reviewer in Microelectronics: By: Analene Montesines - NagayoDocumento102 pagineEce Board Exam Reviewer in Microelectronics: By: Analene Montesines - NagayoIan Benedict Lavapie50% (2)

- Vlsi DesignDocumento129 pagineVlsi DesignB RAVI CHANDRANessuna valutazione finora

- Unit IDocumento25 pagineUnit IRamarao BNessuna valutazione finora

- A Training Seminar Presentation On: Vlsi & VHDLDocumento24 pagineA Training Seminar Presentation On: Vlsi & VHDLSagar KumawatNessuna valutazione finora

- Integrated CircuitDocumento21 pagineIntegrated CircuitKennedy OliveiraNessuna valutazione finora

- 1 TO Vlsi: Vlsi Design by DR SP SinghDocumento8 pagine1 TO Vlsi: Vlsi Design by DR SP Singhendryas zewduNessuna valutazione finora

- Training Project of VLSIDocumento52 pagineTraining Project of VLSISYED MOHAMMAD FAIZNessuna valutazione finora

- Unit 1, MOS Transistor (Compatibility Mode)Documento121 pagineUnit 1, MOS Transistor (Compatibility Mode)yashvardhany.ae20Nessuna valutazione finora

- MECA587 Advanced Digital Design For Mechatronics: The Origin of Moore's Law ... and Its ConsequencesDocumento58 pagineMECA587 Advanced Digital Design For Mechatronics: The Origin of Moore's Law ... and Its ConsequencesKourosh KhashayarNessuna valutazione finora

- EC6612 VLSI Design Lab ManualDocumento74 pagineEC6612 VLSI Design Lab ManualVijai MeyyappanNessuna valutazione finora

- Integrated CircuitDocumento13 pagineIntegrated CircuitGilberto ManhattanNessuna valutazione finora

- Vlsi Design PDFDocumento120 pagineVlsi Design PDFHareesh Harsha100% (1)