Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

I) Absolute or Fully Decoding and II) Linear Select or Partial Decoding PDF

Caricato da

Baisakh Sweet100%(1)Il 100% ha trovato utile questo documento (1 voto)

8K visualizzazioni5 pagineMemory Addressing Decoding Technique in 8086 microprocessor

Titolo originale

i) Absolute or Fully Decoding and II) Linear Select or Partial Decoding - PDF

Copyright

© © All Rights Reserved

Formati disponibili

PDF o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoMemory Addressing Decoding Technique in 8086 microprocessor

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF o leggi online su Scribd

100%(1)Il 100% ha trovato utile questo documento (1 voto)

8K visualizzazioni5 pagineI) Absolute or Fully Decoding and II) Linear Select or Partial Decoding PDF

Caricato da

Baisakh SweetMemory Addressing Decoding Technique in 8086 microprocessor

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF o leggi online su Scribd

Sei sulla pagina 1di 5

Address Decoding and Memory Mapping: Memory address decoding is nothing but to assign

an address for each location in the memory chip. The data stored in the memory is accessed by

specifying its address. Memory address can be decoded in two ways:

i) Absolute or Fully decoding and ii) Linear Select or Partial decoding

‘There are many advantages in absolute address decoding,

i) Bach memory location has only one address, there is no duplication in the address,

) Memory can be placed contiguously in the address space of the microprocessor

iii) Future expansion can be made easily without disturbing the existing circuitry

There are few disadvantages in this method

i) Extra decoders are necessary

ii) Some delay will be produced by these extra decoders.

The main advantage of linear select decoding is its simplified decoding circuit. This reduces the

hardware design cost. But there are many disadvantages in this decoding.

{) Multiple addresses are provided for the same location

ii) Complete memory space of the microprocessor is not efficiently used

iii) Adding or interfacing ICs with already existing circuitry is difficult.

Absolute Address Decoding: The 8085 microprocessor has 16 address lines. Therefore it can

access 2'® locations in the physical memory. If all these lines are connected to a single memory

device, it will decode these 16 address lines internally and produces 216 different addresses from

(0000H to FFFFH so that cach location in the memory will have a unique address

AL Ay | Hex Aes

0-0} owl

°

‘AwAu Ay Ay [Au Aw Ar Ae [Ar As As Ay [Ay Ap

oo 0 Of 0-0 0 OFO00 GTO 0

000 0/000 0/000 clo 001) comm

000 0/000 0/000 a\0 01 0| com

Fig. 1.6 Memory Address

Above diagram shows the various memory addresses used in Microprocessor. If more than one

chips are used then some logic must be used to select one particular chip. This is done with the

help of decoder,

TALS138 address decoder to generate the chip select signals for eachmemory block. In this

decoder when the address lines A13, Al4 and A1S are 000, theoutput fineYO will be activated as

shown in Fig 1.7. This in turn selects the firstmemory block. Similarly when these lines are 0OL

(C20, B=0 and A=1) YI will beactivated and the second memory block will be selected.

Block

Select

7aisi3s ee

Fig 1.7: Memory block decoder

In this type of memory interfacing, all the address lines (AO to AIS) have beenused. Each

location in the memory will have a single address. This type of addressdecoding is called as

absolute or fully decoded addressing.

— A,

sal % a a)

uo jon [jan a th

oe ete FO

efor [Oot ou on

oe Li 00 00

a—_16 3

Memory 1 Memory 2 Memory 1 Memory 2

Fig. 1.8: Role of CS signal

According to the value of Ao and Al , any one register will be selected and to select one memory

chip we need one chip select signal CS signal as shown in the next diagram.

If CS" is *O’memory 1 will be selected else memory2 will be selected. And the complete picture

of the interfacing is shown below.

A1S-A8.

al

ven -

MEMW

Fig. 1.9: The complete interfacing diagram

The simple view of RAM is that it is made up of registers that are made up of flip-flops (or

‘memory elements). The number of flip-flops in a “memory register” determines the size of the

memory wordROM on the other hand uses diodes instead of the flip-flops to permanently hold

the information, For the microprocessor to access (Read or Write) information in memory (RAM

or ROM), it needs to do the following:

Select the right memory chip (using part of the address bus). Identify the memory location (using

the rest of the address bus). Access the data (using the data bus).

aan

fee) 21 |2 |

Selhellal/2lalele

Litt ttt t

Fig. 1.10 Memory Interface Diagram

‘Tri-State Buffers: An important circuit element that is used extensively in memory. This buffer

is a logic circuit that has three states: Logic 0, logie1, and high impedance. When this circuit is in

high impedance mode it looks as if it is disconnected from the output completely. This circuit has

two inputs and one output. The first input behaves like the normal input for the circuit. The

second input is an “enable”. If itis set high, the output follows the proper circuit behaviour. If it

is set low, the output looks like a wire connected to nothing.

Input /Output Devices: Pavallel Interfacing: There are two ways to interface 8085 with /O

devices in parallel data transfer mode: Memory Mapped IO and {0 mapped IO.

Memory mapped VO: It considers them like any other memory location. They are assigned a 16-

bit address within the address range of the 8085.The exchange of data with these devices follows

the transfer of data with memory. The user uses the same instructions used for memory.

WO mapped VO: It treats them separately from memory: VO devices are assigned a “port

number” within the 8-bit address range of OOH to FFE. The user in this case would access these

devices using the IN and OUT instructions only

TO mapped IO V/s Memory Mapped 10:

Memory Mapped 0

10 mapped 10

+ 10

reated as memory.

+ 16-bit addres

ng.

+ More Decoder Hardware.

+ Can address 2!°=64K locations.

+ Less memory is available.

+ Memory Instructions are used

+ Memory control signals are used.

+ Arithmetic and logic operations can be

Performed on data.

+ Data transfer byw register and 10,

+ 10 is treated 10.

+ 8 bitaddressing.

+ Less Decoder Hardware

+ Can address 2°=256 locations.

+ Whole memory address space is available.

+ Special Instructions are used like IN,

OUT.

+ Special control signals are used.

+ Arithmetic and logic operations cannot be

Performed on data.

+ Data transfer bAw accumulator and 10.

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5795)

- Virtualengine Brochure 2016 Web 20160401Documento2 pagineVirtualengine Brochure 2016 Web 20160401Vusumzi MzimvubuNessuna valutazione finora

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Lecture1-215331Fuses and SwitchesDocumento62 pagineLecture1-215331Fuses and SwitchesHarsh NegiNessuna valutazione finora

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

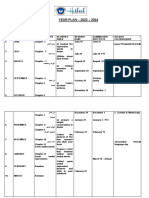

- My Year Plan (2023 - 2024Documento7 pagineMy Year Plan (2023 - 2024therapy mudraNessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Wavin AS Product & Technical Guide PDFDocumento68 pagineWavin AS Product & Technical Guide PDFnamNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- High Speed Disc Brake Judder - The Influence of Passing Through Critical SpeedDocumento4 pagineHigh Speed Disc Brake Judder - The Influence of Passing Through Critical Speedpgp655484Nessuna valutazione finora

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Microsoft Announces First Windows CE Shared Source Program To Allow Commercial Distribution of Modified Source Code - StoriesDocumento11 pagineMicrosoft Announces First Windows CE Shared Source Program To Allow Commercial Distribution of Modified Source Code - StoriesMariusz PruszowskiNessuna valutazione finora

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Rectangular Column CalculationsDocumento1 paginaRectangular Column Calculationsabu taherNessuna valutazione finora

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Volvo - EC340D-EC480D Product BrochureDocumento32 pagineVolvo - EC340D-EC480D Product BrochurePaloma Smith100% (2)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- AWC 2010 CatalogDocumento24 pagineAWC 2010 CatalogMario Lopez100% (1)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- HCIA-AI V1.0 Exam OutlineDocumento6 pagineHCIA-AI V1.0 Exam OutlineMaycol Stven50% (2)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Catalogo Boquillas TanquesDocumento32 pagineCatalogo Boquillas TanquesPunta De Lobos VisionsurfNessuna valutazione finora

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- ZigBee RG 2010Documento32 pagineZigBee RG 2010Alejo Gómez RNessuna valutazione finora

- Precision Air ConditioningDocumento9 paginePrecision Air ConditioningF. A AhmedNessuna valutazione finora

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Fundamnetals of Human GeographyDocumento41 pagineFundamnetals of Human GeographymagicvishNessuna valutazione finora

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- C5 - SalesDocumento6 pagineC5 - SalesancadanicaNessuna valutazione finora

- 9800svc ManualDocumento428 pagine9800svc ManualAxel Betancourt100% (2)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- AllPac and AllFrac Sand Control Screens With Alternate Path TechnologyDocumento2 pagineAllPac and AllFrac Sand Control Screens With Alternate Path Technologyqazim786Nessuna valutazione finora

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1091)

- Pouch Li-Ion Cell Pilot Assembly LineDocumento3 paginePouch Li-Ion Cell Pilot Assembly Linevenugopalan srinivasan100% (1)

- 8 SN, UUID, PN&SLP Tools IntroductionDocumento16 pagine8 SN, UUID, PN&SLP Tools Introductionatharvasaxena93Nessuna valutazione finora

- Mix Design 2Documento15 pagineMix Design 2partha_svnitNessuna valutazione finora

- Raychem HVLVDocumento26 pagineRaychem HVLVpichet_krongyart2859Nessuna valutazione finora

- Research and Application of The EAN-13 Barcode Recognition On IphoneDocumento4 pagineResearch and Application of The EAN-13 Barcode Recognition On IphoneDự Thái HoàngNessuna valutazione finora

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Social Studies Content Enhancement Routines Implementation ReviewDocumento1 paginaSocial Studies Content Enhancement Routines Implementation Reviewapi-215901090Nessuna valutazione finora

- BtoothDocumento87 pagineBtoothSooday Jhaveri100% (1)

- EPA Guidance On Moisture Control (Dragged)Documento1 paginaEPA Guidance On Moisture Control (Dragged)Mitesh KumarNessuna valutazione finora

- OscillatorsDocumento16 pagineOscillatorsJose Manuel Qll100% (1)

- Idoc Vs BapiDocumento2 pagineIdoc Vs BapiKhalid SayeedNessuna valutazione finora

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Abs 1-1113GBDocumento10 pagineAbs 1-1113GBdiogocellestrini100% (1)

- Criminology Students Atittude Towards The Use of Instructional MaterialsDocumento7 pagineCriminology Students Atittude Towards The Use of Instructional MaterialsGlobal Research and Development Services0% (1)

- Clarification of Vehicle Cone IndexDocumento12 pagineClarification of Vehicle Cone IndexrobiniscNessuna valutazione finora

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)