Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Data Sheet

Caricato da

Diego CaceresDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Data Sheet

Caricato da

Diego CaceresCopyright:

Formati disponibili

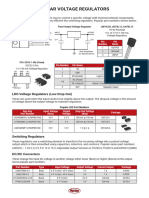

5-V Low-Drop Fixed Voltage Regulator TLE 4270

Features

• Output voltage tolerance ≤ ± 2 %

• Low-drop voltage

• Integrated overtemperature protection

• Reverse polarity protection

• Input voltage up to 42 V P-TO220-5-11

• Overvoltage protection up to 65 V (≤ 400 ms) (P-TO220-5-1)

• Short-circuit proof

• Suitable for use in automotive electronics

• Wide temperature range

• Adjustable reset time

• ESD protection > 4000 V

Type Ordering Code Package

P-TO220-5-12

TLE 4270 Q67000-A9209-A903 P-TO220-5-11 (P-TO220-5-2)

TLE 4270 S Q67000-A9243-A904 P-TO220-5-12

TLE 4270 G Q67006-A9201-A901 P-TO263-5-1

▼ TLE 4270 Q67000-A9209-A801 P-TO220-5-1

▼ TLE 4270 S Q67000-A9243-A802 P-TO220-5-2

▼ TLE 4270 G Q67006-A9201-A802 P-TO220-5-8

P-TO263-5-1

● TLE 4270 D Q67006-A9360 P-TO252-5-1

(P-TO220-5-8)

▼ Not for new design ● New type

Functional Description

This device is a 5-V low-drop fixed-voltage regulator.

The maximum input voltage is 42 V (65 V, ≤ 400 ms).

Up to an input voltage of 26 V and for an output current

up to 550 mA it regulates the output voltage within a

2 % accuracy. The short circuit protection limits the P-TO252-5-1 (D-PAK)

output current of more than 650 mA. The device incorporates overvoltage protection

and temperature protection that disables the circuit at unpermissibly high temperatures.

Semiconductor Group 1 1998-11-01

TLE 4270

Pin Configuration

(top view)

P-TO220-5-11 P-TO220-5-12 P-TO263-5-1

(P-TO220-5-1) (P-TO220-5-2) (P-TO220-5-8)

1 5

RO D

1 5 1 5 Ι GND Q

AEP01922

P-TO252-5-1 (D-PAK)

GND

RO D Ι GND Q

Ι GND Q RO D

AEP01923 AEP02172

1 5

Ι RO D Q

AEP02580

Figure 1

Pin Definitions and Functions

Pin Symbol Function

1 I Input; block to ground directly on the IC with ceramic capacitor

2 RO Reset Output; the open collector output is connected to the 5 V output

via an integrated resistor of 30 kΩ.

3 GND Ground; internally connected to heatsink.

4 D Reset Delay; connect a capacitor to ground for delay time adjustment.

5 Q 5-V Output; block to ground with 22 µF capacitor, ESR < 3 Ω.

Semiconductor Group 2 1998-11-01

TLE 4270

Application Description

The IC regulates an input voltage in the range of 5.5 V < VI < 36 V to VQnom = 5.0 V. Up

to 26 V it produces a regulated output current of more than 550 mA. Above 26 V the

save-operating-area protection allows operation up to 36 V with a regulated output

current of more than 300 mA. Overvoltage protection limits operation at 42 V. The

overvoltage protection hysteresis restores operation if the input voltage has dropped

below 36 V. A reset signal is generated for an output voltage of VQ < 4.5 V. The delay for

power-on reset can be set externally with a capacitor.

Design Notes for External Components

An input capacitor CI is necessary for compensation of line influences. The resonant

circuit consisting of lead inductance and input capacitance can be damped by a resistor

of approx. 1 Ω in series with CI. An output capacitor CQ is necessary for the stability of

the regulating circuit. Stability is guaranteed at values of CQ ≥ 22 µF and an ESR of

< 3 Ω.

Circuit Description

The control amplifier compares a reference voltage, which is kept highly accurate by

resistance adjustment, to a voltage that is proportional to the output voltage and drives

the base of a series transistor via a buffer. Saturation control as a function of the load

current prevents any over-saturation of the power element.

If the output voltage decreases below 4.5 V, an external capacitor CD on pin 4 (D) will be

discharged by the reset generator. If the voltage on this capacitor drops below VDRL, a

reset signal is generated on pin 2 (RO), i.e. reset output is set low. If the output voltage

rises above 4.5 V, CD will be charged with constant current. After the power-on-reset time

the voltage on the capacitor reaches VDU and the reset output will be set high again. The

value of the power-on-reset time can be set within a wide range depending of the

capacitance of CD.

The IC also incorporates a number of internal circuits for protection against:

• Overload

• Overvoltage

• Overtemperature

• Reverse polarity

Semiconductor Group 3 1998-11-01

TLE 4270

Temperature Saturation

Control and

Sensor

Protection

Circuit

1 5

Input Output

Control

Amplifier

Buffer 2 Reset

Adjustment Bandgap Reset Output

+

Reference Generator

- 4 Reset

Delay

3

GND AEB01924

Figure 2

Block Diagram

Semiconductor Group 4 1998-11-01

TLE 4270

Absolute Maximum Ratings

Tj = – 40 to 150 °C

Parameter Symbol Limit Values Unit Notes

min. max.

Input

Voltage VI – 42 42 V

Voltage VI 65 V t ≤ 400 ms

Current II internally limited

Reset Output

Voltage VR – 0.3 7 V

Current IR Internally limited

Reset Delay

Voltage VD – 0.3 7 V

Current ID Internally limited

Output

Voltage VQ – 1.0 16 V

Current IQ Internally limited

Ground

Current IGND – 0.5 – A –

Temperatures

Junction temperature Tj 150 °C –

Storage temperature Tstg – 50 150 °C

Optimum reliability and life time are guaranteed if the junction temperature does not

exceed 125 °C in operating mode. Operation at up to the maximum junction temperature

of 150 °C is possible in principle. Note, however, that operation at the maximum

permitted ratings could affect the reliability of the device.

Semiconductor Group 5 1998-11-01

TLE 4270

Operating Range

Parameter Symbol Limit Values Unit Notes

min. max.

Input voltage VI 6 42 V –

Junction temperature Tj – 40 150 °C –

Thermal Resistance

Junction ambient Rthja – 65 K/W

70 K/W TO263, TO2521)

Junction case Rthjc – 3 K/W t < 1 ms

Zthjc 2 K/W (TO-220/263

Packages)

1)

Soldered in, min. footprint

Characteristics

VI = 13.5 V; – 40 °C ≤ Tj = ≤ 125 °C (unless otherwise specified)

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Output voltage VQ 4.90 5.00 5.10 V 5 mA ≤ IQ ≤ 550 mA;

6 V ≤ VI ≤ 26 V

Output voltage VQ 4.90 5.00 5.10 V 26 V ≤ VI ≤ 36 V;

IQ ≤ 300 mA

Output current IQmax 650 850 – mA VQ = 0 V

limiting

Current Iq – 1 1.5 mA IQ = 5 mA

consumption

Iq = II − IQ

Current Iq – 55 75 mA IQ = 550 mA

consumption

Iq = II – IQ

Current Iq – 70 90 mA IQ = 550 mA; VI = 5 V

consumption

Iq = II – IQ

Drop voltage Vdr – 350 700 mV IQ = 550 mA1)

Semiconductor Group 6 1998-11-01

TLE 4270

Characteristics (cont’d)

VI = 13.5 V; – 40 °C ≤ Tj = ≤ 125 °C (unless otherwise specified)

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Load regulation ∆VQ – 25 50 mV IQ = 5 to 550 mA;

VI = 6 V

Supply voltage ∆VQ – 12 25 mV VI = 6 to 26 V

regulation IQ = 5 mA

Power supply PSRR – 54 – dB fr = 100 Hz;

Ripple rejection Vr = 0.5 VSS

Reset Generator

Switching threshold VRT 4.5 4.65 4.8 V –

Reset High voltage VROH 4.5 – – V –

Reset low voltage VROL – 60 – mV Rintern = 30 kΩ2);

1.0 V ≤ VQ ≤ 4.5 V

Reset low voltage VROL – 200 400 mV IR = 3 mA, VQ = 4.4 V

Reset pull-up R 18 30 46 kΩ internally connected

to Q

Lower reset timing VDRL 0.2 0.45 0.8 V VQ < VRT

threshold

Charge current Id 8 14 25 µA VD = 1.0 V

Upper timing VDU 1.4 1.8 2.3 V –

threshold

Delay time td – 13 – ms CD = 100 nF

Reset reaction time tRR – – 3 µs CD = 100 nF

Overvoltage Protection

Turn-Off voltage VI, ov 42 44 46 V –

1)

Drop voltage = VI – VQ (measured when the output voltage has dropped 100 mV from the nominal value

obtained at 13.5 V input)

2)

Reset peak is always lower than 1.0 V.

Semiconductor Group 7 1998-11-01

TLE 4270

ΙΙ 1 5

ΙQ

1000 µF 470 nF 22 µF

TLE 4270G

2

ΙR

VΙ VQ

4 3

ΙD

VR

VD CD Ι GND

AES01925

Figure 3

Test Circuit

1 5

Input 5 V-Output

470 nF TLE 4270

22 µF

Reset 2 4

to MC

3 100 nF

AES01926

Figure 4

Application Circuit

Semiconductor Group 8 1998-11-01

TLE 4270

VΙ

< t RR

VQ

V RT

dV Ι d

=

V D V DU dt C d

V DRL

td t RR

VR

Power-on-Reset Thermal Voltage Drop Undervoltage Secondary Load

Shutdown at Input Spike Bounce AES01927

Figure 5

Time Response

Semiconductor Group 9 1998-11-01

TLE 4270

Output Voltage VQ versus Output Voltage VQ versus

Temperature Tj Input Voltage VI

AED01928 AED01929

5.20 12

V V

VQ VQ

5.10 10

V Ι = 13.5 V

5.00 8

4.90 6

R L = 25 Ω

4.80 4

4.70 2

4.60 0

-40 0 40 80 120 C 160 0 2 4 6 8 V 10

Tj VΙ

Output Current IQ versus Output Current IQ versus

Temperature Tj Input Voltage VI

AED01930 AED01931

1200 1.2

mA A

ΙQ ΙQ

1000 1.0

T j = 25 C

800 0.8

600 0.6

T j = 125 C

400 0.4

200 0.2

0 0

-40 0 40 80 120 C 160 0 10 20 30 40 V 50

Tj VΙ

Semiconductor Group 10 1998-11-01

TLE 4270

Current Consumption Iq Current Consumption Iq

versus Output Current IQ versus Output Current IQ

AED01932 AED01933

6 80

mA mA

Ιq Ι q 70

5

60

4

50

V Ι = 13.5 V

3 40

V Ι = 13.5 V

30

2

20

1

10

0 0

0 20 40 60 80 mA 120 0 100 200 300 400 mA 600

ΙQ ΙQ

Current Consumption Iq Drop Voltage Vdr versus

versus Input Voltage VI Output Current IQ

AED01934 AED01935

120 800

mA mV

Ιq V Dr 700

100

600

80

500

T j = 125 C

60 400

R L = 10 Ω

300

40

200 Tj =25 C

R L = 20 Ω R L = 50 Ω

20

100

0 0

0 10 20 30 40 V 50 0 200 400 600 mA 1000

VΙ ΙQ

Semiconductor Group 11 1998-11-01

TLE 4270

Charge Current Id Delay Switching threshold VDU

versus Temperature Tj versus Temperature Tj

AED01936 AED01937

8 4.0

µA V

Ιd 7 V dT 3.5

Ιd

6 3.0

V Ι = 13.5 V

5 2.5 V Ι = 13.5 V

VD = 1 V

V DU

4 2.0

3 1.5

2 1.0

1 0.5

0 0

-40 0 40 80 120 C 160 -40 0 40 80 120 C 160

Tj Tj

Semiconductor Group 12 1998-11-01

TLE 4270

Package Outlines

P-TO220-5-1

(Plastic Transistor Single Outline)

10 +0.4 4.6 -0.2

10.2 -0.2 1x45˚

+0.1 +0.1

3.75 1.27

2.8

15.4 ±0.3

19.5 max

8.8 -0.2

16 ±0.4

8.6 ±0.3

10.2 ±0.3

2.6

1 5

1.7 0.4 +0.1

+0.1 1)

0.8 4.5 ±0.4

0.6 M

5x 8.4 ±0.4

1) 1-0.15 at dam bar (max 1.8 from body)

1) 1-0.15 im Dichtstegbereich (max 1.8 vom Körper)

GPT05107

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”. Dimensions in mm

Semiconductor Group 13 1998-11-01

TLE 4270

P-TO220-5-2

(Plastic Transistor Single Outline)

10 +0.4 4.6 -0.2

10.2 -0.2 1x45˚

+0.1 +0.1

3.75 1.27

2.8

15.4 ±0.3

8.8 -0.2

10.9 ±0.2

12.9 ±0.2

1 5

1.7 0.4 +0.1

0.8 +0.1 1) 2.6 ±0.15

0.6 M

5x

1) 1-0.15 at dam bar (max 1.8 from body)

1) 1-0.15 im Dichtstegbereich (max 1.8 vom Körper)

GPT05256

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”. Dimensions in mm

Semiconductor Group 14 1998-11-01

TLE 4270

P-TO220-5-11

(Plastic Transistor Single Outline)

10 ±0.2

A

9.8 ±0.15

8.5 1) 4.4

3.7-0.15 1.27 ±0.1

1)

15.65 ±0.3

2.8 ±0.2

13.4

17±0.3

9.25 ±0.2

0.05

8.6 ±0.3

10.2 ±0.3

3.7 ±0.3

C

0...0.15 0.5 ±0.1

0.8 ±0.1 2.4

1.7 3.9 ±0.4

0.25 M A C

8.4 ±0.4

1)

Typical

All metal surfaces tin plated, except area of cut.

GPT09064

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”. Dimensions in mm

Semiconductor Group 15 1998-11-01

TLE 4270

P-TO220-5-12

(Plastic Transistor Single Outline)

10 ±0.2

A

9.8 ±0.15 B

1)

8.5 4.4

3.7 -0.15 1.27 ±0.1

1)

15.65 ±0.3

2.8 ±0.2

13.4

17±0.3

9.25 ±0.2

0.05

11±0.5

13 ±0.5

0...0.15 0.5 ±0.1

6x

0.8 ±0.1 2.4

1.7

0.25 M A B C

Typical

1) All metal surfaces tin plated, except area of cut.

GPT09065

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”. Dimensions in mm

Semiconductor Group 16 1998-11-01

TLE 4270

P-TO263-5-1

(Plastic Transistor Single Outline)

10 ±0.2 4.4

9.8 ±0.15 1.27 ±0.1

A B

8.5 1) 0.1

0.05

1±0.3

2.4

9.25 ±0.2

8 1)

(15)

2.7 ±0.3

4.7 ±0.5

0...0.15

5x0.8 ±0.1 0.5 ±0.1

4x1.7

8˚ max.

0.25 M A B 0.1

1)

Typical

GPT09113

All metal surfaces tin plated, except area of cut.

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device Dimensions in mm

Semiconductor Group 17 1998-11-01

TLE 4270

P-TO220-5-8

(Plastic Transistor Single Outline)

4.6

1.27

10.2 0.2

8.0 2.6

1)

10.1

8.8

3.5

1.5

0.8

1.7 0.4

4 x 1.7 = 6.8 GPT05873

1) shear and punch direction burr free surface

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device Dimensions in mm

Semiconductor Group 18 1998-11-01

TLE 4270

P-TO252-5-1

(Plastic Transistor Single Outline)

6.5 +0.15 2.3 +0.05

-0.10

-0.10

5.4 ±0.1 B 0.9 +0.08

-0.04

A

1 ±0.1

1 ±0.1

0.8 ±0.15

(4.17)

6.22 -0.2

0...0.15

9.9 ±0.5

0.51 min

0.15 max

per side 5x0.6 ±0.1 0.5 +0.08

-0.04

1.14

0.1

4.56

0.25 M A B GPT09161

All metal surfaces tin plated, except area of cut.

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device Dimensions in mm

Semiconductor Group 19 1998-11-01

Potrebbero piacerti anche

- Abs PDFDocumento98 pagineAbs PDFMarcioMartinhoFerreira100% (3)

- Tle 62326 Low Side SwitchDocumento19 pagineTle 62326 Low Side SwitchDiego Caceres100% (1)

- Proton Arena Jumbuck Engine Electrical 1.5 1.8 Service ManualDocumento50 pagineProton Arena Jumbuck Engine Electrical 1.5 1.8 Service ManualEddie JaiNessuna valutazione finora

- Silergy Corp SY8213FCC - C178246Documento9 pagineSilergy Corp SY8213FCC - C178246Thai LamNessuna valutazione finora

- Proposal PaperDocumento13 pagineProposal Paperapi-331985309Nessuna valutazione finora

- KG934V1 Page 1-5Documento5 pagineKG934V1 Page 1-5Niten Gupta100% (1)

- A2C33648Documento27 pagineA2C33648mohhizbar100% (1)

- Study On Electricity Distribution, Substation Operation & Maintenance of DESCODocumento46 pagineStudy On Electricity Distribution, Substation Operation & Maintenance of DESCOSarwer Hussain Faisal100% (5)

- ABB DC Power - Supplies - Catalog PDFDocumento118 pagineABB DC Power - Supplies - Catalog PDFAdnan Naeem MalikNessuna valutazione finora

- Infineon TLE4275V50 DS v01 - 07 en PDFDocumento17 pagineInfineon TLE4275V50 DS v01 - 07 en PDFjoseNessuna valutazione finora

- 4271 2GDocumento24 pagine4271 2GAlexandre Dantas HenriqueNessuna valutazione finora

- Automotive Power: Low Dropout Linear Voltage RegulatorDocumento20 pagineAutomotive Power: Low Dropout Linear Voltage RegulatorJoshua WardNessuna valutazione finora

- 5-V Low-Drop Fixed Voltage Regulator TLE 4271: FeaturesDocumento20 pagine5-V Low-Drop Fixed Voltage Regulator TLE 4271: FeaturesPablo CervantesNessuna valutazione finora

- Tle 4260Documento15 pagineTle 4260Didier DoradoNessuna valutazione finora

- Regulador 4271-2g PLD MercedesDocumento23 pagineRegulador 4271-2g PLD MercedesDiego CaceresNessuna valutazione finora

- 5-V Low-Drop Fixed Voltage Regulator TLE 4271-2: FeaturesDocumento20 pagine5-V Low-Drop Fixed Voltage Regulator TLE 4271-2: FeaturesHla Swe Oo0% (1)

- 4274GV50 5v Regulator PDFDocumento13 pagine4274GV50 5v Regulator PDFvanadium0Nessuna valutazione finora

- TLE4260Documento15 pagineTLE4260NoelNessuna valutazione finora

- 4260 2s PDFDocumento15 pagine4260 2s PDFmarce822Nessuna valutazione finora

- Infineon TLE4275V33 DS v01 - 20 EN 1079989Documento13 pagineInfineon TLE4275V33 DS v01 - 20 EN 1079989FrankCubidesNessuna valutazione finora

- Low Drop Voltage Regulator TLE 4274: FeaturesDocumento16 pagineLow Drop Voltage Regulator TLE 4274: FeaturesRuddy RalNessuna valutazione finora

- Low Drop Voltage Regulator TLE 4274: FeaturesDocumento16 pagineLow Drop Voltage Regulator TLE 4274: FeaturesAdrian MonzonNessuna valutazione finora

- Infineon TLE4252D DS v01 - 40 ENDocumento13 pagineInfineon TLE4252D DS v01 - 40 ENMohamed AmineNessuna valutazione finora

- Low Dropout Linear Fixed Voltage RegulatorDocumento26 pagineLow Dropout Linear Fixed Voltage RegulatorNur Aishi Putri SyarilNessuna valutazione finora

- Data Sheet TLE4262G Regulador 5v 20 PinesDocumento16 pagineData Sheet TLE4262G Regulador 5v 20 Pinesaagreco73Nessuna valutazione finora

- Voltage Regulator TLE 4274 / 3.3V 2.5V: FeaturesDocumento12 pagineVoltage Regulator TLE 4274 / 3.3V 2.5V: Featurespglez93Nessuna valutazione finora

- 5 V/10 V Low Drop Voltage Regulator TLE 4266: FeaturesDocumento14 pagine5 V/10 V Low Drop Voltage Regulator TLE 4266: FeaturesLuis Mariano TovillasNessuna valutazione finora

- Low Drop Voltage Tracker TLE 4251: FeaturesDocumento13 pagineLow Drop Voltage Tracker TLE 4251: FeaturesAGDO SERVICENessuna valutazione finora

- Voltage Regulator TLE 4274 / 3.3V 2.5V: FeaturesDocumento13 pagineVoltage Regulator TLE 4274 / 3.3V 2.5V: FeaturesdavidNessuna valutazione finora

- Low Drop Voltage Tracker TLE 4250 G: FeaturesDocumento11 pagineLow Drop Voltage Tracker TLE 4250 G: FeaturesJoey Mar AntonioNessuna valutazione finora

- TLE42766 Siemens Elenota - PLDocumento16 pagineTLE42766 Siemens Elenota - PLAnuar Angrac Lopez CruzNessuna valutazione finora

- 5-V Low-Drop Voltage Regulator TLE 4263: FeaturesDocumento17 pagine5-V Low-Drop Voltage Regulator TLE 4263: FeaturesWelleyNessuna valutazione finora

- TLE4470Documento24 pagineTLE4470ricahard61Nessuna valutazione finora

- Low-Drop Voltage Regulator TLE 4276: FeaturesDocumento19 pagineLow-Drop Voltage Regulator TLE 4276: FeaturesshtormlNessuna valutazione finora

- TLE4266G SiemensSemiconductorGroupDocumento9 pagineTLE4266G SiemensSemiconductorGroupDuranRod2013Nessuna valutazione finora

- Regulador de Tension TLE4267-DS-v02 - 51-EnDocumento23 pagineRegulador de Tension TLE4267-DS-v02 - 51-EnJorge Martinez PerezNessuna valutazione finora

- RP108J Series: Low Input Voltage 3A LDO Regulator OutlineDocumento29 pagineRP108J Series: Low Input Voltage 3A LDO Regulator OutlineArie DinataNessuna valutazione finora

- Infineon TLE4276 DataSheet v02 - 90 ENDocumento15 pagineInfineon TLE4276 DataSheet v02 - 90 ENAdrian GarciaNessuna valutazione finora

- 3 A Low Drop Positive Voltage Regulator: Adjustable and FixedDocumento27 pagine3 A Low Drop Positive Voltage Regulator: Adjustable and FixedTT DVNessuna valutazione finora

- TVL ST23 04 Ad0Documento9 pagineTVL ST23 04 Ad0coulsonpfilNessuna valutazione finora

- INPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Documento8 pagineINPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Isaac CostaNessuna valutazione finora

- Sherwood RX-4105bDocumento23 pagineSherwood RX-4105bGilberto0% (1)

- 2576 LDocumento9 pagine2576 LclanonNessuna valutazione finora

- 50s SMD TLE4250GDocumento12 pagine50s SMD TLE4250GSashaNessuna valutazione finora

- Dual Low Drop Voltage Regulator TLE 7469: FeaturesDocumento22 pagineDual Low Drop Voltage Regulator TLE 7469: FeaturesPabloLabruneNessuna valutazione finora

- Infineon TLE4299V33 DS v01 - 01 enDocumento25 pagineInfineon TLE4299V33 DS v01 - 01 enStelian DobreNessuna valutazione finora

- 1932124Documento12 pagine1932124Mauricio GomesNessuna valutazione finora

- Pc2250 Series: Bipolar Analog Integrated CircuitDocumento13 paginePc2250 Series: Bipolar Analog Integrated CircuitkeisinhoNessuna valutazione finora

- Tle 4471Documento26 pagineTle 4471Armando UsedaNessuna valutazione finora

- TPD2015FNDocumento17 pagineTPD2015FNLamayah FordNessuna valutazione finora

- FPF2281 Over-Voltage Protection Load Switch: Features DescriptionDocumento8 pagineFPF2281 Over-Voltage Protection Load Switch: Features DescriptionJosé RepuestoNessuna valutazione finora

- FPF2281 FairchildSemiconductorDocumento7 pagineFPF2281 FairchildSemiconductorjuanNessuna valutazione finora

- TLE4279 SiemensSemiconductorGroupDocumento19 pagineTLE4279 SiemensSemiconductorGroupLuis MezaNessuna valutazione finora

- RT9202Documento16 pagineRT9202bachet56Nessuna valutazione finora

- AL8862QDocumento17 pagineAL8862QIvo MatosNessuna valutazione finora

- TLE4471 InfineonTechnologiesAGDocumento24 pagineTLE4471 InfineonTechnologiesAGjose luisNessuna valutazione finora

- Linear Voltage RegulatorsDocumento1 paginaLinear Voltage Regulatorsanand kumarNessuna valutazione finora

- Wide Bandwidth Single J-Fet Operational Amplifier: LF151 LF251 - LF351Documento9 pagineWide Bandwidth Single J-Fet Operational Amplifier: LF151 LF251 - LF351Charbel TadrosNessuna valutazione finora

- 3A Ultra Low Dropout Linear Regulator: General DescriptionDocumento11 pagine3A Ultra Low Dropout Linear Regulator: General DescriptionIgha Intan PermataNessuna valutazione finora

- FP6321A FitiDocumento14 pagineFP6321A FitiJob GarciaNessuna valutazione finora

- Tle5203 Motor Driver PDFDocumento18 pagineTle5203 Motor Driver PDFJavier CuraNessuna valutazione finora

- 3-A DC Motor Driver TLE 5203: SPT IcDocumento18 pagine3-A DC Motor Driver TLE 5203: SPT IcJavier CuraNessuna valutazione finora

- AN17831ADocumento9 pagineAN17831ARaymond KondengisNessuna valutazione finora

- Tle5205 2Documento23 pagineTle5205 2Richard MachadoNessuna valutazione finora

- 4279G InfenionDocumento18 pagine4279G InfenionAlver TuizaNessuna valutazione finora

- An 15525Documento7 pagineAn 15525Dede Tuhadi PrayitnoNessuna valutazione finora

- Dokumen - Tips - Aladin Diagnostic Software For The Diwa 5 Transmission Turbo Aladin Diagnostic PDFDocumento4 pagineDokumen - Tips - Aladin Diagnostic Software For The Diwa 5 Transmission Turbo Aladin Diagnostic PDFDiego CaceresNessuna valutazione finora

- 75332S. Trans PDFDocumento10 pagine75332S. Trans PDFDiego CaceresNessuna valutazione finora

- Regulador 4271-2g PLD MercedesDocumento23 pagineRegulador 4271-2g PLD MercedesDiego CaceresNessuna valutazione finora

- Lsb02658en PDFDocumento26 pagineLsb02658en PDFsosobiNessuna valutazione finora

- Page Change LED Display: ATS220 ATS Controller Configuration and Instructions Ver1.0 Panel and DisplayDocumento4 paginePage Change LED Display: ATS220 ATS Controller Configuration and Instructions Ver1.0 Panel and DisplayRafael Castillo100% (1)

- SK250MS 180kVA Technical Data Sheets 10 01Documento7 pagineSK250MS 180kVA Technical Data Sheets 10 01Sergio Marín SalasNessuna valutazione finora

- 02 130205 V7.13 EVRC2A-N6, NT Manual ControlDocumento306 pagine02 130205 V7.13 EVRC2A-N6, NT Manual ControlGiancarlo Barahona Aguilar67% (3)

- 1550c Manual PDFDocumento26 pagine1550c Manual PDFhaydarNessuna valutazione finora

- Motors and The NEC PDFDocumento7 pagineMotors and The NEC PDFgl1188Nessuna valutazione finora

- Data 9x Containerized Gas Engine JGS 320 GS - SLDocumento2 pagineData 9x Containerized Gas Engine JGS 320 GS - SLBalast MetheeNessuna valutazione finora

- High Performance Vector Control Yaskawa Ac Drive: V Class, To KW V Class, To KWDocumento66 pagineHigh Performance Vector Control Yaskawa Ac Drive: V Class, To KW V Class, To KWLearning To Become LeadersNessuna valutazione finora

- RT II 1-3k UL KstarDocumento43 pagineRT II 1-3k UL KstarMiguel Pino B100% (1)

- Elec Report (Draft)Documento19 pagineElec Report (Draft)AHMEDNessuna valutazione finora

- Project Proposal For DST & Texas Instruments Inc. India Innovation Challenge Design Contest 2016 Anchored by IIM BangaloreDocumento16 pagineProject Proposal For DST & Texas Instruments Inc. India Innovation Challenge Design Contest 2016 Anchored by IIM BangaloreNitinNessuna valutazione finora

- Alternators: Electrical-Energy GenerationDocumento11 pagineAlternators: Electrical-Energy GenerationPragg AggarwalNessuna valutazione finora

- RR Regulador Retificador ORIGINAL TestDocumento5 pagineRR Regulador Retificador ORIGINAL TestLeonardo HalonNessuna valutazione finora

- Jeannine Uwibambe PDFDocumento94 pagineJeannine Uwibambe PDFHassan SouleymanNessuna valutazione finora

- Cired 2017 Tuesday ProgrammeDocumento19 pagineCired 2017 Tuesday ProgrammeivanramljakNessuna valutazione finora

- REMOTE POSITION INDICATING SYSTEM sw1Documento5 pagineREMOTE POSITION INDICATING SYSTEM sw1Joshua Serna Sanchez II0% (1)

- Ha 25 74 Nxair 50ka enDocumento46 pagineHa 25 74 Nxair 50ka engerardo.aquinoNessuna valutazione finora

- School of Engineering, University of Warwick, Coventry CV4 7AL, UK Supervisor: DR C E OramDocumento1 paginaSchool of Engineering, University of Warwick, Coventry CV4 7AL, UK Supervisor: DR C E OramKyle ByrneNessuna valutazione finora

- Power Engineering DatabaseDocumento48 paginePower Engineering DatabaseArs LanNessuna valutazione finora

- Siemens Mobilett II Portable X RayDocumento2 pagineSiemens Mobilett II Portable X RayTony100% (1)

- Linemonitoring RelaysDocumento4 pagineLinemonitoring RelaysSrikant SuruNessuna valutazione finora

- FVNR: Direct On Line Asynchronous Motor Starter: MotorpactDocumento4 pagineFVNR: Direct On Line Asynchronous Motor Starter: Motorpactmuhammad wafiNessuna valutazione finora

- List of Important Grid Elements - SR - 2021 - MayDocumento108 pagineList of Important Grid Elements - SR - 2021 - Maysiddhesh.chaudhariNessuna valutazione finora

- BPE (22427) ReportDocumento14 pagineBPE (22427) ReportEJ 12 Prathamesh JadhavNessuna valutazione finora