Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Open Source RISC-V Cores

Caricato da

eppleshine0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

77 visualizzazioni1 paginaRISCV COres

Copyright

© © All Rights Reserved

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoRISCV COres

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

77 visualizzazioni1 paginaOpen Source RISC-V Cores

Caricato da

eppleshineRISCV COres

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 1

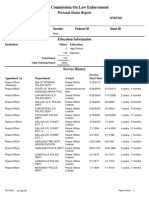

Many RISC-V Open Source Cores… …and

counting…. (source: riscv.org)

Name Maintainer Links User spec License Name Maintainer Links User spec License

rocket SiFive, UCB Bar GitHub 2.3-draft BSD Minerva LambdaConcept GitHub RV32I BSD

freedom SiFive GitHub 2.3-draft BSD

OPenV/mriscv OnChipUIS GitHub RV32I(?) MIT

Berkeley Out-of- Esperanto, UCB GitHub 2.3-draft BSD

VexRiscv SpinalHDL GitHub RV32I[M][C] MIT

Order Machine Bar

(BOOM) Roa Logic RV12 Roa Logic GitHub 2.1 Non-Commercial

License

ORCA VectorBlox GitHub RV32IM BSD

SCR1 Syntacore GitHub 2.2, RV32I/E[MC] Solderpad

RI5CY ETH Zurich, GitHub RV32IMC Solderpad Hardware

Università di Hardware License v. 0.51

Bologna License v. 0.51

Hummingbird Bob Hu GitHub 2.2, RV32IMAC Apache 2.0

Zero-riscy ETH Zurich, GitHub RV32IMC Solderpad E200

Università di Hardware

Bologna License v. 0.51 Shakti IIT Madras Website,GitLab 2.2, BSD

RV64IMAFDC

Ariane ETH Zurich, Website,GitHub RV64GC Solderpad

Università di Hardware ReonV Lucas Castro GitHub GPL v3

Bologna License v. 0.51 PicoRV32 Clifford Wolf GitHub RV32I/E[MC] ISC

Riscy Processors MIT CSAIL CSG Website,GitHub MIT MR1 Tom Verbeure GitHub RV32I Unlicense

SERV Olof Kindgren GitHub RV32I ISC

RiscyOO MIT CSAIL CSG GitHub RV64IMAFD MIT SweRV EH1 Western Digital GitHub RV32IMC Apache 2.0

Lizard Cornell CSL BRG GitHub RV64IM BSD Corporation

Reve-R Gavin Stark GitHub RV32IMAC Apache 2.0

© OpenHW Group - RISC-V / WOSH ETH Zurich 11 June 2019 12

Potrebbero piacerti anche

- Informed Consent For ResearchDocumento4 pagineInformed Consent For ResearchMary MendozaNessuna valutazione finora

- Letter To Ms Claire Kennedy - University Mandated Leave of Absence Polic...Documento3 pagineLetter To Ms Claire Kennedy - University Mandated Leave of Absence Polic...Jacob Lorinc100% (1)

- Cheat Sheet Microservices FinalDocumento2 pagineCheat Sheet Microservices FinalAbhilash Potharaju100% (1)

- Binary ToolsDocumento4 pagineBinary ToolswhitergNessuna valutazione finora

- C2 MatrixDocumento30 pagineC2 MatrixetilawolNessuna valutazione finora

- RED Teaming ToolkitDocumento12 pagineRED Teaming ToolkitDehiker VzlaNessuna valutazione finora

- From The Transistor To The Web Browser: Join Github TodayDocumento2 pagineFrom The Transistor To The Web Browser: Join Github TodayNONAME69Nessuna valutazione finora

- GitHub - Icsharpcode - Ilspy-Vscode - ILSpy Visual Studio Code Extension and Service For Decompiling .NET AssembliesDocumento2 pagineGitHub - Icsharpcode - Ilspy-Vscode - ILSpy Visual Studio Code Extension and Service For Decompiling .NET Assembliesggvn adminNessuna valutazione finora

- GFSGFDocumento3 pagineGFSGFkimjejerzyNessuna valutazione finora

- Third Party and Open Source Notices: Component LicenseDocumento76 pagineThird Party and Open Source Notices: Component LicenseIsro' fajar roslinaNessuna valutazione finora

- Red Teaming ToolkitDocumento28 pagineRed Teaming ToolkitLearnerNessuna valutazione finora

- GitHub - OnionIoT - Python-Spidev Python Module For Interfacing With SPI DevicesDocumento8 pagineGitHub - OnionIoT - Python-Spidev Python Module For Interfacing With SPI Devicesronald decimus MAD-BONDONessuna valutazione finora

- Reverse Shell Cheet SheetDocumento11 pagineReverse Shell Cheet SheetShamsher KhanNessuna valutazione finora

- The Power of Human Connection Review 2Documento81 pagineThe Power of Human Connection Review 2Tajam SoftNessuna valutazione finora

- GitHub - glegrain:STM32-with-macOSDocumento13 pagineGitHub - glegrain:STM32-with-macOSCaio RondonNessuna valutazione finora

- Github Com Blynkkk Blynk LibraryDocumento7 pagineGithub Com Blynkkk Blynk LibraryZhangZaoNessuna valutazione finora

- GitHub - Openmuc - JRXTX - The Java Serial Communication LibraryDocumento3 pagineGitHub - Openmuc - JRXTX - The Java Serial Communication LibraryMarcosNessuna valutazione finora

- LibreCAD - Free Open Source 2D CADDocumento6 pagineLibreCAD - Free Open Source 2D CADFilip Ovidiu PupăzăNessuna valutazione finora

- GitHub - Bcit-Ci - CodeIgniter - Open Source PHP Framework (Originally From EllisLab)Documento3 pagineGitHub - Bcit-Ci - CodeIgniter - Open Source PHP Framework (Originally From EllisLab)Berita UpdateNessuna valutazione finora

- Git GithubDocumento5 pagineGit Githubram dhukeNessuna valutazione finora

- GitHub - Udosteinberg - NOVA - NOVA MicrohypervisorDocumento5 pagineGitHub - Udosteinberg - NOVA - NOVA Microhypervisor宛俊Nessuna valutazione finora

- Dipta Das: Experience EducationDocumento2 pagineDipta Das: Experience EducationShubham SinghNessuna valutazione finora

- digitalWriteFast - Arduino LibrariesDocumento1 paginadigitalWriteFast - Arduino LibrariesNofriagara Davit HarnawanNessuna valutazione finora

- Important Github Repositories For Security: Created TagsDocumento5 pagineImportant Github Repositories For Security: Created TagsTechnical SupportNessuna valutazione finora

- Git & Github - by Carter RheaDocumento29 pagineGit & Github - by Carter RheaUdin KreasiNessuna valutazione finora

- Oversynchronization CandidatesDocumento63 pagineOversynchronization CandidatesKinetaNessuna valutazione finora

- GitHub - SDR-Technologies - NanoSDRDocumento7 pagineGitHub - SDR-Technologies - NanoSDRheshokikiNessuna valutazione finora

- Powerspace GitHubDocumento4 paginePowerspace GitHubKewei HuangNessuna valutazione finora

- DAKOTA PluginDocumento2 pagineDAKOTA PluginAnonymous 1rLNlqUNessuna valutazione finora

- A Modbus TCP Slave For ArduinoDocumento1 paginaA Modbus TCP Slave For ArduinoejoaomelchiorsNessuna valutazione finora

- Third Party AcknowledgementsDocumento7 pagineThird Party AcknowledgementsHakim SabRiNessuna valutazione finora

- Visual Studio Code - Mac, Linux, WindowsDocumento2 pagineVisual Studio Code - Mac, Linux, WindowsJemeraldNessuna valutazione finora

- GitHub - Leokoppel - GP22 - An Arduino Library For The Acam GP22 Time-to-Digital ConverterDocumento2 pagineGitHub - Leokoppel - GP22 - An Arduino Library For The Acam GP22 Time-to-Digital ConverterYung SangNessuna valutazione finora

- Ultimate DevSecOps Library 1706607714Documento27 pagineUltimate DevSecOps Library 1706607714phenhomenal ecommerceNessuna valutazione finora

- Docker - Labs - This Is A Collection of Tutorials For Learning How To Use Docker With Various Tools. Contributions WelcomeDocumento2 pagineDocker - Labs - This Is A Collection of Tutorials For Learning How To Use Docker With Various Tools. Contributions WelcomeMuhammadimran AliNessuna valutazione finora

- SourcegraphDocumento1 paginaSourcegraphlovelifeNessuna valutazione finora

- Openhaystack: Seemoo-LabDocumento17 pagineOpenhaystack: Seemoo-LabCGM technologyNessuna valutazione finora

- GitHub - Arno0x - BluecoatURLFilteringBypass - Bluecoat Proxies URL Filtering Bypass PoC PDFDocumento2 pagineGitHub - Arno0x - BluecoatURLFilteringBypass - Bluecoat Proxies URL Filtering Bypass PoC PDFlofej57555Nessuna valutazione finora

- Third Party NoticesDocumento293 pagineThird Party NoticesLazaNessuna valutazione finora

- Third Party NoticesDocumento63 pagineThird Party NoticesSonam PandeyNessuna valutazione finora

- Ethicalhacker - D-TECT - D-TECT - Pentesting The Modern WebDocumento4 pagineEthicalhacker - D-TECT - D-TECT - Pentesting The Modern WebsanjNessuna valutazione finora

- Appeon PowerBuilderIDE 2021 FreeDownloadTermsDocumento127 pagineAppeon PowerBuilderIDE 2021 FreeDownloadTermsS.D.Nessuna valutazione finora

- A Lyra2 Fpga Core For Lyra2Rev2-Based CryptocurrenciesDocumento5 pagineA Lyra2 Fpga Core For Lyra2Rev2-Based CryptocurrenciesmetNessuna valutazione finora

- CodeBlocks-Arduino Addons To Code Blocks To Support Arduinos and ATtinysDocumento5 pagineCodeBlocks-Arduino Addons To Code Blocks To Support Arduinos and ATtinysBobbyNessuna valutazione finora

- Bomb CrackDocumento2 pagineBomb CrackAlpha3GamingNessuna valutazione finora

- Rust For CDocumento58 pagineRust For Cmanikantamnk11Nessuna valutazione finora

- Hashcat - Advanced Password RecoveryDocumento9 pagineHashcat - Advanced Password RecoverywariszNessuna valutazione finora

- Interplanetary File System For Business (Ipfsfb)Documento6 pagineInterplanetary File System For Business (Ipfsfb)Abu Hayat M HasnatNessuna valutazione finora

- A Design of RISC-V RV32IMAFC Core For MCUDocumento33 pagineA Design of RISC-V RV32IMAFC Core For MCUJavariaNessuna valutazione finora

- WsgidavDocumento3 pagineWsgidavjksdeiiNessuna valutazione finora

- VVX D230 Dect Ip Phone: Open Source SoftwareDocumento4 pagineVVX D230 Dect Ip Phone: Open Source SoftwarecwchowNessuna valutazione finora

- Mbonaci ScalaDocumento142 pagineMbonaci ScalaoscarNessuna valutazione finora

- How We Built Github FastDocumento4 pagineHow We Built Github FastjogotestNessuna valutazione finora

- Why Use Git?: Backtrack Quickly When You Make MistakesDocumento11 pagineWhy Use Git?: Backtrack Quickly When You Make Mistakesbishal_shrivastavaNessuna valutazione finora

- GitHub - Gsavage - Lorem - Ipsum Rails Helper To Generate Lorem Ipsum Within A ViewDocumento2 pagineGitHub - Gsavage - Lorem - Ipsum Rails Helper To Generate Lorem Ipsum Within A ViewКоларовNessuna valutazione finora

- Brew FormulaDocumento152 pagineBrew FormulaManoj John ManuelNessuna valutazione finora

- Paulwaldmann (Paul Waldmann) - Starred GitHubDocumento6 paginePaulwaldmann (Paul Waldmann) - Starred GitHubAnonymous l0YO1cNessuna valutazione finora

- Faq SSHJDocumento4 pagineFaq SSHJkesho81Nessuna valutazione finora

- Open Source Software List: Page 1 of 12Documento12 pagineOpen Source Software List: Page 1 of 12Muhammad IbrahimNessuna valutazione finora

- RP2040 Assembly Language Programming: ARM Cortex-M0+ on the Raspberry Pi PicoDa EverandRP2040 Assembly Language Programming: ARM Cortex-M0+ on the Raspberry Pi PicoNessuna valutazione finora

- Structure of ILODocumento5 pagineStructure of ILOChhavi MittalNessuna valutazione finora

- DevianceDocumento31 pagineDeviancemarcbulaonNessuna valutazione finora

- Notes in Philippine Criminal Justice SystemDocumento5 pagineNotes in Philippine Criminal Justice SystemRemedios Iquiña Reodava88% (8)

- Reflection PaperDocumento1 paginaReflection PaperGeralynEngresoNessuna valutazione finora

- Unit 6 Leadership Ethics and Social ResponsibilityDocumento11 pagineUnit 6 Leadership Ethics and Social Responsibility0463SanjanaNessuna valutazione finora

- Law of Torts and Consumer Protection: Vicarious Liability With Case LawsDocumento12 pagineLaw of Torts and Consumer Protection: Vicarious Liability With Case LawsVishesh RaoNessuna valutazione finora

- Ahrlj 1 - 2015Documento229 pagineAhrlj 1 - 2015jonas msigalaNessuna valutazione finora

- Anti Discrimination PolicyDocumento3 pagineAnti Discrimination PolicySrivastava71Nessuna valutazione finora

- Beauty Without Cruelty Believes ThatDocumento1 paginaBeauty Without Cruelty Believes Thatankush JAINNessuna valutazione finora

- Patient's RightsDocumento7 paginePatient's RightsLorraine RiegoNessuna valutazione finora

- Domestic Violence Act, 2005Documento2 pagineDomestic Violence Act, 2005Dinesh GadkariNessuna valutazione finora

- Belo-Henares v. GuevarraDocumento3 pagineBelo-Henares v. GuevarraRaven TailNessuna valutazione finora

- Topic 8 - Moral Choices Facing Employees (Week 5)Documento13 pagineTopic 8 - Moral Choices Facing Employees (Week 5)Pei JuanNessuna valutazione finora

- Human Rights in PakistanDocumento45 pagineHuman Rights in PakistanCHAUDHARY NAQASH BASHIRNessuna valutazione finora

- Aristotles Virtue Ethics GROUP 1Documento15 pagineAristotles Virtue Ethics GROUP 1Jayc ChantengcoNessuna valutazione finora

- KuMingRoong 0133750Documento20 pagineKuMingRoong 0133750Ku MingroongNessuna valutazione finora

- Explored Note RegardDocumento2 pagineExplored Note RegardJosueNessuna valutazione finora

- White Collar Crimes in Certain Professions in IndiaDocumento14 pagineWhite Collar Crimes in Certain Professions in IndiaAnjana P Nair100% (1)

- United Nations Convention of The Rights of ChildDocumento2 pagineUnited Nations Convention of The Rights of ChildChirodeep RoyNessuna valutazione finora

- Research PaperDocumento2 pagineResearch Paperapi-72644074Nessuna valutazione finora

- 235122Documento537 pagine235122IrynaKovalenkoNessuna valutazione finora

- The Principle of Autonomy: Four Fundamental Ethical PrinciplesDocumento7 pagineThe Principle of Autonomy: Four Fundamental Ethical PrinciplesROMELA MAQUILINGNessuna valutazione finora

- Juvenile InrDocumento9 pagineJuvenile InrJay-r Pabualan DacoNessuna valutazione finora

- SOGIE Bill: Gender Equality or Revenge of The LGBTDocumento15 pagineSOGIE Bill: Gender Equality or Revenge of The LGBTDavid SanianaNessuna valutazione finora

- Roscoe Pound: Social EngineeringDocumento8 pagineRoscoe Pound: Social EngineeringChitraksh MahajanNessuna valutazione finora

- Indeterminate Sentence Law (ISLAW) : How To Determine Maximum and Minimum PenaltiesDocumento5 pagineIndeterminate Sentence Law (ISLAW) : How To Determine Maximum and Minimum PenaltiesKelvin InsigneNessuna valutazione finora

- TCOLE Transcript For Sam AllenDocumento8 pagineTCOLE Transcript For Sam AllenJeremy LiebbeNessuna valutazione finora

- Torture, Rape and Death in Police Custody A Critical Analysis Upon The Basis of Role of JudiciaryDocumento19 pagineTorture, Rape and Death in Police Custody A Critical Analysis Upon The Basis of Role of Judiciaryal mamunNessuna valutazione finora