Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

V BE2 0.7volt, The Value of The DC Voltage V C 2 (In Volts)

Caricato da

John Andrew MañacopDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

V BE2 0.7volt, The Value of The DC Voltage V C 2 (In Volts)

Caricato da

John Andrew MañacopCopyright:

Formati disponibili

1. The Ebers-Moll model of a BJT is valid D.

none of these

A. only in active mode

B. only in active and saturation modes 5. In the RLC circuit shown in the figure, the input voltage is

C. only in active and cut-off modes given by

D. in active, saturation and cut-off modes

2. Assume that the diode in the figure has Von = 0.7 V, but is

otherwise ideal. The magnitude of the current i2 (in mA) is

equal to _____.

The output voltage v0 (t) is

A. cos (200t) + 2sin (500t)

B. 2 cos (200t) + 4sin (500t)

C. sin (200t) + 2cos (500t)

D. 2 sin (200t) + 4cos (500t)

6. The diodes D1 and D2 in the figure are ideal and the

3. Which one of the following statements is correct about an

capacitors are identical. The product RC is very large

ac-coupled common-emitter amplifier operating in the

compared to the time period of the ac voltage. Assuming

mid-band region?

that the diodes do not breakdown in the reverse bias, the

A. The device parasitic capacitances behave like open

output voltage V0 (in volt) at the steady state is ________.

circuits, whereas coupling and by pass capacitances

behave like short circuits.

B. The device parasitic capacitances, coupling

capacitances and bypass capacitances behave like

open circuits.

C. The device parasitic capacitances, coupling

capacitances and bypass capacitances behave like

short circuits.

D. The device parasitic capacitances behave like short

circuits, whereas coupling and bypass capacitances

behave like open circuits.

4. An op-amp has a finite open loop voltage gain of 100. Its

input offset voltage V iOS (=+5 mV) is modeled as shown

in the circuit below. The amplifier is ideal in all other A. 1

respects. V input Is 25 mV. B. 10

C. 0

D. insufficient data

7. Consider the circuit shown in the figure. Assuming V BE1=

V BE2 = 0.7volt, the value of the dc voltage V C 2 (in volts)

is _______.

The output voltage (in millivolts) is _____

A. 413.79

B. 212.45

C. 342.12

10. The minimum number of 2-input NAND gates

required to implement a 2-input XOR gate is

A. 4

B. 5

C. 6

D. 7

11. The z-parameter matrix Z11 Z12 for the two-port

Z21 Z22

network shown in

A. 1

B. 0.5

C. 1.20

D. 3

8. In the Astable multivibrator circuit shown in the

figure, the frequency of oscillation (in kHz) at the output

pin 3 is ___________.

12. For the circuit shown in the figure, R1 = R2 = R3 = 1ohm,

L = 1 H and C =1 F If the input V in = cos(106 t) then the

𝑉 𝑜𝑢𝑡

overall voltage gain of the circuit is ______.

𝑉 𝑖𝑛

A. 6.64

B. 7.25

C. 5.64

D. 13

9. The logic functionality realized by the circuit shown below

is

A. -1

B. -3

C. -2

D. -5

13. Following is the K-map of a Boolean function of five

A. OR variables P, Q, R, S and X. The minimum sum-of-product

B. XOR (SOP) expression for the function is

C. NAND

D. AND

lower threshold voltages for the circuit are,

respectively.

A. +5V and -5V B. +7V and -3V

C. +3V and -7V D. +3V and -3V

17. A good transconductance amplifier should have

A. high input resistance and low output resistance

B. low input resistance and high output resistance

C. high input and output resistances

D. low input and output resistance

18. In the circuit shown, V is a sinusoidal voltage source. The

current I is in phase with voltage V.

14. The Miller effect in the context of a Common Emitter

amplifier explains A. 0.2 B. 0.3

A. an increase in the low-frequency cutoff frequency C. 1 D. 5

B. an increase in the high-frequency cutoff

frequency 19. In a DRAM,

C. a decrease in the low-frequency cutoff frequency A. periodic refreshing is not required

D. a decrease in the high-frequency cutoff frequency B. information is stored in a capacitor

15. Consider the D-Latch shown in the figure, which is C. information is stored in a latch

transparent when its clock input CK is high and has D. both read and write operations can be performed

zero propagation delay. In the figure, the clock simultaneously

signal CLK1 has a 50% duty cycle and CLK2 is a onefifth

period delayed version of CLK1. The duty cycle 20. For the circuit shown in the figure, P and Q are the

at the output latch in percentage is ____. inputs and Y is the output.

A. 30% B. 28%

C. 34% D. 32%

16. For the operational amplifier circuit shown, the

output saturation voltages are ±15V. The upper and

The logic implemented by the circuit is The logic implemented by the circuit is

A. XNOR B. XOR A. XNOR B. XOR

C. NOR D. OR C. NOR D. OR

21. An n-channel enhancement mode MOSFET is biased 25. The output V0 of the diode circuit shown in the figure

at V GS > VTH and V DS > (V GS -V TH), where V GS is is connected to an averaging DC voltmeter. The

the gate-to-source voltage, DS V is the drain-to-source reading on the DC voltmeter in Volts, neglecting the

voltage and V TH is the threshold voltage. voltage drop across the diode, is ______.

Considering channel length modulation effect to be

significant, the MOSFET behaves as a

A. voltage source with zero output impedance

B. voltage source with non-zero output impedance

C. current source with finite output impedance

D. current source with infinite output impedance

22. A connection is made consisting of resistance A in A. 3.18 B. 4.12

series with a parallel combination of resistances B C. 1.23 D. 10

and C. Three resistors of value 10 ohms ,5 ohms,2 ohms are

provided. Consider all possible permutations of the 26. Consider the circuit shown in the figure. Assume

given resistors into the positions A, B, C, and identify base-to- emitter voltage VBE=0.8 V and common

the configurations with maximum possible overall base current gain (α)of the transistor is unity.

resistance, and also the ones with minimum possible

overall resistance. The ratio of maximum to

minimum values of the resistances (up to second

decimal place) is _____.

A. 2.14 B. 1.12

C. 2 D. 0.24

23. An npn bipolar junction transistor (BJT) is operating

in the active region. If the reverse bias across the

base – collector junction is increased, then

A. the effective base width increases and common –

emitter current gain increases

B. the effective base width increases and common –

emitter current gain decreases

C. the effective base width decreases and common

– emitter current gain increases

D. the effective base width decreases and common

– emitter current gain decreases

24. For the circuit shown in the figure, P and Q are the

inputs and Y is the output.

The value of the collector- to – emitter voltage VCE

(in volt) is _______.

A. 6 B. 5

C. 10 D. 7

27. Assuming that transistors M1 and M2 are identical

and have a threshold voltage of 1V, the state of

transistors M1 and M2 are respectively.

A. Saturation, Saturation

B. Linear, Linear

C. Linear, Saturation

D. Saturation, Linear

Potrebbero piacerti anche

- ElecDocumento4 pagineElecJj JumawanNessuna valutazione finora

- Mok 2Documento27 pagineMok 2ERMIAS AmanuelNessuna valutazione finora

- Ae53 Ac53 At53Documento4 pagineAe53 Ac53 At53M Taher BamyaniNessuna valutazione finora

- JEE Main Level Practice Test-20: For JEE & NEET AspirantsDocumento6 pagineJEE Main Level Practice Test-20: For JEE & NEET AspirantsJeet GovindNessuna valutazione finora

- 18 Electronics ExerciseDocumento23 pagine18 Electronics Exercisekenchan0810.kcNessuna valutazione finora

- Analog ElectronicsDocumento29 pagineAnalog ElectronicsSuganyaRavi0% (1)

- Analog Circuits: GATE EC Topic Wise QuestionsDocumento50 pagineAnalog Circuits: GATE EC Topic Wise Questionsdeepthi1993100% (1)

- IN Analog-Electronics PDFDocumento30 pagineIN Analog-Electronics PDFEarn PromotionNessuna valutazione finora

- NK C SI R: Current Electricity, Basic Home Work Sheet-5Documento2 pagineNK C SI R: Current Electricity, Basic Home Work Sheet-5RohanNessuna valutazione finora

- EE - ANALOG and DIGITAL ELECTRONICS PDFDocumento75 pagineEE - ANALOG and DIGITAL ELECTRONICS PDFHariShankarSharmaNessuna valutazione finora

- ISRO CS 2016-Watermark - pdf-80Documento6 pagineISRO CS 2016-Watermark - pdf-80Govind VijayNessuna valutazione finora

- Nodia and Company: Gate Solved Paper Instrumentation Engineering 2003Documento21 pagineNodia and Company: Gate Solved Paper Instrumentation Engineering 2003AkshyaNessuna valutazione finora

- IES EE C 1992 (Electrical Guru - Blogspot.in)Documento10 pagineIES EE C 1992 (Electrical Guru - Blogspot.in)Tanmay PokaleNessuna valutazione finora

- Candidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarksDocumento3 pagineCandidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarksAdhikari SushilNessuna valutazione finora

- Nodia and Company: Gate Solved Paper Instrumentation Engineering 2006Documento23 pagineNodia and Company: Gate Solved Paper Instrumentation Engineering 2006Meet PatelNessuna valutazione finora

- QP D15 De57 PDFDocumento3 pagineQP D15 De57 PDFRajashekarBalyaNessuna valutazione finora

- Gate Solved Paper Ec Analog ElectronicsDocumento77 pagineGate Solved Paper Ec Analog ElectronicssaiNessuna valutazione finora

- Nodia and Company: Gate Solved Paper Electrical Engineering 2007Documento49 pagineNodia and Company: Gate Solved Paper Electrical Engineering 2007pankajNessuna valutazione finora

- Semi ConductorDocumento4 pagineSemi ConductorSchrodinger's CatNessuna valutazione finora

- Practice Sheet - Network Theory BasicsDocumento6 paginePractice Sheet - Network Theory BasicsAakash DewanganNessuna valutazione finora

- Circuit AnalysisDocumento70 pagineCircuit AnalysisFeroz AhmedNessuna valutazione finora

- EC Analog-ElectronicDocumento77 pagineEC Analog-ElectronicGopinathan MNessuna valutazione finora

- Current Electricity - P.SDocumento5 pagineCurrent Electricity - P.SAyush KumarNessuna valutazione finora

- Solutions On Topicwise Examination Questions: Ec: Electronics and CommunicationsDocumento67 pagineSolutions On Topicwise Examination Questions: Ec: Electronics and CommunicationsMallik's ChannelNessuna valutazione finora

- 131101-2 Gtu 3rd Sem PaperDocumento4 pagine131101-2 Gtu 3rd Sem PaperShailesh SankdasariyaNessuna valutazione finora

- Rev B - Neet - Aipmt-Physics-30years Chapterwise SolutionsDocumento2 pagineRev B - Neet - Aipmt-Physics-30years Chapterwise SolutionsPankaj Mishra0% (1)

- TECHNICAL QUIZ EceDocumento7 pagineTECHNICAL QUIZ EceAnonymous eWMnRr70qNessuna valutazione finora

- Current Electricity Question BankDocumento7 pagineCurrent Electricity Question BankchallapallinikhilNessuna valutazione finora

- Electronics MQP Ii Puc 2023-24Documento4 pagineElectronics MQP Ii Puc 2023-24sanjaykashiNessuna valutazione finora

- Ee Power-Electronics PDFDocumento42 pagineEe Power-Electronics PDFPriya DharshiniNessuna valutazione finora

- Nielit Cs 65 PDFDocumento32 pagineNielit Cs 65 PDFNeha KumariNessuna valutazione finora

- Ec-101 - Final PDFDocumento2 pagineEc-101 - Final PDFarjunv_14Nessuna valutazione finora

- CBSE UGC NET Electronic Science Paper 2 June 2007Documento14 pagineCBSE UGC NET Electronic Science Paper 2 June 2007Bhargav. GNessuna valutazione finora

- Aptransco Electronic Engn 2011 Previous Paper 5c60dbb7Documento22 pagineAptransco Electronic Engn 2011 Previous Paper 5c60dbb7Navyadeepika. KokkiralaNessuna valutazione finora

- Nodia and Company: Gate Solved Paper Electrical Engineering 2011Documento39 pagineNodia and Company: Gate Solved Paper Electrical Engineering 2011pankajNessuna valutazione finora

- Department of Electrical and Systems Engineering ESE 206: Electrical Circuits and Systems II - Lab Junction Diode Basics I. PurposeDocumento6 pagineDepartment of Electrical and Systems Engineering ESE 206: Electrical Circuits and Systems II - Lab Junction Diode Basics I. Purposekstu1112Nessuna valutazione finora

- QUIZ 3-NOV23 - CH-1-2-3 - Feb22Documento10 pagineQUIZ 3-NOV23 - CH-1-2-3 - Feb22MUHAMMAD NUR AMNI KHARIMANNessuna valutazione finora

- Chapter-19 Alternating Current and Electromagnetic Waves (PG 359 - 366)Documento8 pagineChapter-19 Alternating Current and Electromagnetic Waves (PG 359 - 366)dummymail6383Nessuna valutazione finora

- Analog EletronicsDocumento2 pagineAnalog EletronicsAjay kumar GuptaNessuna valutazione finora

- Solution Ee Set C 2018Documento16 pagineSolution Ee Set C 2018Dharmender KumarNessuna valutazione finora

- Fitjee Paper Class 10 ElectrcityDocumento4 pagineFitjee Paper Class 10 ElectrcityKeerthivasav 12Nessuna valutazione finora

- JEE Main - 5 - JEE 2023 - PaperDocumento15 pagineJEE Main - 5 - JEE 2023 - PaperDevansh GoelNessuna valutazione finora

- Electrical Engg 2013Documento16 pagineElectrical Engg 2013Srimannarayana NandamNessuna valutazione finora

- Electrical Engg 2013Documento16 pagineElectrical Engg 2013JADDUNessuna valutazione finora

- Semiconductor and Digital Circuit 1693007493Documento4 pagineSemiconductor and Digital Circuit 1693007493samsuzzaman sahinNessuna valutazione finora

- Gate Solved Paper - Ee: Q.1 - Q.20 Carry One Mark EachDocumento33 pagineGate Solved Paper - Ee: Q.1 - Q.20 Carry One Mark EachPonsubramanianNessuna valutazione finora

- GATE ECE 2003 Actual PaperDocumento24 pagineGATE ECE 2003 Actual Paperkibrom atsbhaNessuna valutazione finora

- Semiconductor Electronics Materials, Devices and Simple Circuits - Practice Sheet (PYQ) - (Only PDFDocumento3 pagineSemiconductor Electronics Materials, Devices and Simple Circuits - Practice Sheet (PYQ) - (Only PDFSHREYANSH RAINessuna valutazione finora

- Analog ElectronicsDocumento118 pagineAnalog Electronicsjohn cenaNessuna valutazione finora

- 750913A02101 Electrical CircuitsDocumento2 pagine750913A02101 Electrical CircuitsKURAKULA VIMAL KUMARNessuna valutazione finora

- EC Network AnalysisDocumento70 pagineEC Network AnalysisSamarth UrankarNessuna valutazione finora

- Chapter6 Ex SolDocumento26 pagineChapter6 Ex SolShivani YadavNessuna valutazione finora

- B. List - : Will (Or) How TwoDocumento2 pagineB. List - : Will (Or) How TwoSarvesh SinghNessuna valutazione finora

- DPP 3Documento11 pagineDPP 3mstudy1009Nessuna valutazione finora

- Model Question Paper: Basic ElectronicsDocumento3 pagineModel Question Paper: Basic Electronicsravishpy100% (2)

- D11 - D12 - D13 - 0599 - EEE1001 - Electric Circuits and Systems - 100321Documento2 pagineD11 - D12 - D13 - 0599 - EEE1001 - Electric Circuits and Systems - 100321Yashi GoswamiNessuna valutazione finora

- Semiconductors - DPP 02Documento3 pagineSemiconductors - DPP 02mv7602456Nessuna valutazione finora

- Vmts Jee Part Test 4....Documento17 pagineVmts Jee Part Test 4....harshit pandeyNessuna valutazione finora

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesDa EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNessuna valutazione finora

- Q88-Vessel Tanker Star Prosperity (9383950)Documento10 pagineQ88-Vessel Tanker Star Prosperity (9383950)John Andrew MañacopNessuna valutazione finora

- EastWest Bank Home Loan Application Form SignedDocumento2 pagineEastWest Bank Home Loan Application Form SignedJohn Andrew Mañacop100% (1)

- Makarius Smart Learning: ConfidentialDocumento12 pagineMakarius Smart Learning: ConfidentialJohn Andrew MañacopNessuna valutazione finora

- 3F New World Bldg. Morayta St. Corner P. Paredes St. España, Manila - PhilippinesDocumento1 pagina3F New World Bldg. Morayta St. Corner P. Paredes St. España, Manila - PhilippinesJohn Andrew MañacopNessuna valutazione finora

- Uv5354 XLS EngDocumento8 pagineUv5354 XLS EngJohn Andrew MañacopNessuna valutazione finora

- Venatus Franchise AgreementDocumento34 pagineVenatus Franchise AgreementJohn Andrew MañacopNessuna valutazione finora

- Startup One-PagerDocumento1 paginaStartup One-PagerJohn Andrew MañacopNessuna valutazione finora

- Letter of Intent Makarius Smart Learning X The Maroon BluebookDocumento1 paginaLetter of Intent Makarius Smart Learning X The Maroon BluebookJohn Andrew MañacopNessuna valutazione finora

- ISV GTM Guide Final 12 - 15 - 16Documento39 pagineISV GTM Guide Final 12 - 15 - 16John Andrew MañacopNessuna valutazione finora

- UntitledDocumento1 paginaUntitledJohn Andrew MañacopNessuna valutazione finora

- 2023 Virtual Training Calendar-SampleDocumento16 pagine2023 Virtual Training Calendar-SampleJohn Andrew MañacopNessuna valutazione finora

- NXT AIS - Updated Enterprise Catalog-SAMPLEDocumento33 pagineNXT AIS - Updated Enterprise Catalog-SAMPLEJohn Andrew MañacopNessuna valutazione finora

- CEM One League Pre-Class Assignment 2Documento1 paginaCEM One League Pre-Class Assignment 2John Andrew MañacopNessuna valutazione finora

- Correct Wording For LinkedIn - ResumeDocumento3 pagineCorrect Wording For LinkedIn - ResumeJohn Andrew MañacopNessuna valutazione finora

- Makarius Introduction Y CombinatorDocumento1 paginaMakarius Introduction Y CombinatorJohn Andrew MañacopNessuna valutazione finora

- JETIR2008117Documento6 pagineJETIR2008117John Andrew MañacopNessuna valutazione finora

- WSJ Theranos Walgreens - 2016Documento5 pagineWSJ Theranos Walgreens - 2016John Andrew MañacopNessuna valutazione finora

- Smart Shopping Carts AI VisionDocumento9 pagineSmart Shopping Carts AI VisionJohn Andrew MañacopNessuna valutazione finora

- What Will I Do If It Is Just 40days Before The Board Exam (Updated) - (Sept11-Oct20) PDFDocumento11 pagineWhat Will I Do If It Is Just 40days Before The Board Exam (Updated) - (Sept11-Oct20) PDFanjoNessuna valutazione finora

- SM2Z5V1 / SM2Z200: 2W Zener DiodesDocumento4 pagineSM2Z5V1 / SM2Z200: 2W Zener DiodesZoltán ÁgostonNessuna valutazione finora

- Fire Alarm Using ThermistorDocumento3 pagineFire Alarm Using ThermistorUjjal Dey100% (1)

- Invertor 5000wattDocumento27 pagineInvertor 5000wattFlorinNessuna valutazione finora

- Solution Sheet 2 Electronic CircuitsDocumento15 pagineSolution Sheet 2 Electronic CircuitsWajdi BELLILNessuna valutazione finora

- Standards LED's FINALDocumento5 pagineStandards LED's FINALRudy StanciuNessuna valutazione finora

- Kalibracja Lampy Service Manual Engl. HfeDocumento162 pagineKalibracja Lampy Service Manual Engl. HfeSebastian SamolewskiNessuna valutazione finora

- Midterms - MachinesDocumento4 pagineMidterms - MachinesKirk Daniel ObregonNessuna valutazione finora

- Faculty of Natural and Applied Sciences Department of Physics PHY 108 Electricity and Magnetism Experiment 4: TransformerDocumento7 pagineFaculty of Natural and Applied Sciences Department of Physics PHY 108 Electricity and Magnetism Experiment 4: TransformerChukwunomso UnaoguNessuna valutazione finora

- Layout of 110kV SwitchyardDocumento1 paginaLayout of 110kV SwitchyardJayarajan Jayarajan C NNessuna valutazione finora

- Ekor - Rpa Series 020: Self-Powered Protection UnitDocumento4 pagineEkor - Rpa Series 020: Self-Powered Protection UnitAlexander BakirovNessuna valutazione finora

- VARROCDocumento9 pagineVARROCmaniamson87% (15)

- 7.noload and Blocked Rotor Test On Singlephase Induction MotorDocumento5 pagine7.noload and Blocked Rotor Test On Singlephase Induction Motormandadi_sailesh100% (2)

- Piezoelectricity:: Principle Knock SensorsDocumento1 paginaPiezoelectricity:: Principle Knock Sensorsdassi99Nessuna valutazione finora

- Aci 22.0KW Falownik Berges Co Sinus Acm Manual PDFDocumento66 pagineAci 22.0KW Falownik Berges Co Sinus Acm Manual PDFJessé Cunha50% (2)

- Term 2 Class Xii Physics PracticalsDocumento7 pagineTerm 2 Class Xii Physics PracticalsBakir Raza PashaNessuna valutazione finora

- Install Electrical Metallic - Nonmetallic (PVC Conduit)Documento13 pagineInstall Electrical Metallic - Nonmetallic (PVC Conduit)Rex Chambers LadaoNessuna valutazione finora

- Load Sharing Module: ApplicationsDocumento2 pagineLoad Sharing Module: ApplicationsGonzalo Villalobos SanchezNessuna valutazione finora

- Installation and Operation Manual: 701A Digital Speed Control For Reciprocating EnginesDocumento64 pagineInstallation and Operation Manual: 701A Digital Speed Control For Reciprocating EnginesS M NaveedNessuna valutazione finora

- Oz964gn PDFDocumento14 pagineOz964gn PDFJesus E Lopez B100% (1)

- Ss 30Documento2 pagineSs 30vicky khanNessuna valutazione finora

- External PNP Transistor CircuitDocumento5 pagineExternal PNP Transistor Circuitefremofe100% (1)

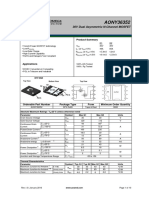

- AONY36352: 30V Dual Asymmetric N-Channel MOSFETDocumento10 pagineAONY36352: 30V Dual Asymmetric N-Channel MOSFETrobertjavi1983Nessuna valutazione finora

- Mixer Amplifiers BG-2035 BG-2060 BG-2120: Operating InstructionsDocumento20 pagineMixer Amplifiers BG-2035 BG-2060 BG-2120: Operating InstructionsR HastomoNessuna valutazione finora

- EDS+03-6650+Gas+Insulated+Switchgear+72 5kV+and+145kVDocumento25 pagineEDS+03-6650+Gas+Insulated+Switchgear+72 5kV+and+145kVarifadha4460% (1)

- History of Grounding Earthing Practices in The United StatesDocumento14 pagineHistory of Grounding Earthing Practices in The United StatesObatai Khan100% (1)

- Turck MS24 112 RDocumento2 pagineTurck MS24 112 RDavid Ulises Yunganina ZeaNessuna valutazione finora

- Surge Arrester TypeDocumento4 pagineSurge Arrester Typefahri adrianNessuna valutazione finora

- AC Motors: Siemens STEP 2000 CourseDocumento45 pagineAC Motors: Siemens STEP 2000 CourseFauzan AffanNessuna valutazione finora

- Westinghouse Ds and DSL Low Voltage Power Circuit Breakers and Cell PartsDocumento28 pagineWestinghouse Ds and DSL Low Voltage Power Circuit Breakers and Cell PartsRodney PimentaNessuna valutazione finora

- PVC Flexible CableDocumento3 paginePVC Flexible CableMWNessuna valutazione finora