Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Cavite State University: Republic of The Philippines

Caricato da

Janjan Iruguin0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

22 visualizzazioni3 pagineThis document discusses the implementation of an AND gate using Electric software. It provides the truth table for an AND gate with inputs A, B, and C and output F. It also includes screenshots of the AND gate circuit schematic created in Electric, the corresponding netlist, and the simulation results showing the voltage waveforms for inputs A, B, C and output F.

Descrizione originale:

Titolo originale

ANDGATEIMPLEMENTATION3INPUT.docx

Copyright

© © All Rights Reserved

Formati disponibili

DOCX, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoThis document discusses the implementation of an AND gate using Electric software. It provides the truth table for an AND gate with inputs A, B, and C and output F. It also includes screenshots of the AND gate circuit schematic created in Electric, the corresponding netlist, and the simulation results showing the voltage waveforms for inputs A, B, C and output F.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOCX, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

22 visualizzazioni3 pagineCavite State University: Republic of The Philippines

Caricato da

Janjan IruguinThis document discusses the implementation of an AND gate using Electric software. It provides the truth table for an AND gate with inputs A, B, and C and output F. It also includes screenshots of the AND gate circuit schematic created in Electric, the corresponding netlist, and the simulation results showing the voltage waveforms for inputs A, B, C and output F.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOCX, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 3

Republic of the Philippines

CAVITE STATE UNIVERSITY

Don Severino de las Alas Campus

Indang, Cavite

(046) 415-0010 / (046) 415-0021

www.cvsu.edu.ph

AND GATE IMPLEMENTATION

Given

𝐹 =𝐴𝑥𝐵𝑥𝐶

Truth Table

𝑨 B C F

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 0

1 0 0 0

1 0 1 0

1 1 0 0

1 1 1 1

Screenshots

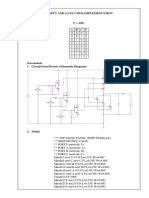

1. Circuit from Electric (Schematic Diagram)

Iruguin, Jan Marielle Laboratory Activity 8 Engr.Sumadsad 1

201511407 / BSECE 5-1 AND GATE 10/07/2019 00 2

2.

00

2. Netlist

*** TOP LEVEL FACET: AND3{sch}

** GROUND NET: 0 (net1)

** PORT A (network: A)

** PORT B (network: B)

** PORT C (network: C)

** PORT F (network: F)

Cnode28 0 F 100F

Mnode5 F net2 0 0 N L=0.70U W=1.60U

Mnode6 F net3 0 0 N L=0.70U W=1.60U

Mnode7 F net4 0 0 N L=0.70U W=1.60U

Mnode8 net6 net4 F net5 P L=0.70U W=9.60U

Mnode9 net7 net3 net6 net5 P L=0.70U W=9.60U

Mnode10 net5 net2 net7 net5 P L=0.70U W=9.60U

Mnode22 net4 C 0 0 N L=0.70U W=1.60U

Mnode23 net5 C net4 C P L=0.70U W=6.40U

Mnode24 net3 B 0 0 N L=0.70U W=1.60U

Mnode25 net5 B net3 B P L=0.70U W=6.40U

Mnode26 net5 A net2 A P L=0.70U W=6.40U

Mnode27 net2 A 0 0 N L=0.70U W=1.60U

** Sources and special nodes:

Vnode12 net5 0 3

Vnode19 C 0 pulse 0 3 0 1n 1n 50n 100n

Vnode20 B 0 pulse 0 3 0 1n 1n 100n 200n

Vnode21 A 0 pulse 0 3 0 1n 1n 200n 400n

.PRINT TRAN V(F)+18 V(C)+12 V(B)+6 V(A)

.TRAN 1p 400n 1n 1n

.END

3. Simulation Results

Iruguin, Jan Marielle Laboratory Activity 8 Engr.Sumadsad 2

00

00

201511407 / BSECE 5-1 AND GATE 10/07/2019 2

Potrebbero piacerti anche

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Photonics, Volume 1: Fundamentals of Photonics and PhysicsDa EverandPhotonics, Volume 1: Fundamentals of Photonics and PhysicsNessuna valutazione finora

- Or Gate Implementation 3 in PutDocumento3 pagineOr Gate Implementation 3 in PutJanjan IruguinNessuna valutazione finora

- 3-Input and Gate Cmos Implementation Given F Abc Truth Table A B C FDocumento2 pagine3-Input and Gate Cmos Implementation Given F Abc Truth Table A B C FKevin SimonsNessuna valutazione finora

- Lab SheetDocumento18 pagineLab SheetRaz MansorNessuna valutazione finora

- Digital Lab ManualDocumento69 pagineDigital Lab ManualRajesh MohanNessuna valutazione finora

- Digital Electronics LabmanualDocumento66 pagineDigital Electronics LabmanualToaster97Nessuna valutazione finora

- Soluções de Testes e ExamesDocumento21 pagineSoluções de Testes e ExamesLara MonteiroNessuna valutazione finora

- Ic Lab AllDocumento45 pagineIc Lab AllRaghu KasulaNessuna valutazione finora

- NANOMETRICAL DEVICES - MOSFET SOI AND SOI HI-K in Synopsys SentaurusDocumento23 pagineNANOMETRICAL DEVICES - MOSFET SOI AND SOI HI-K in Synopsys SentaurusJuan VALVERDENessuna valutazione finora

- Lab Manual EC AllDocumento383 pagineLab Manual EC Allanshuj11Nessuna valutazione finora

- Lab Manual 8085 MicroprocessorDocumento43 pagineLab Manual 8085 MicroprocessorManvendra Singh0% (1)

- Vlsi Assignment Harry2007Documento26 pagineVlsi Assignment Harry2007hk5050Nessuna valutazione finora

- Experiment No 3 Combinational Circuits: Binary Adder and Subtractor Circuits Learning ObjectivesDocumento20 pagineExperiment No 3 Combinational Circuits: Binary Adder and Subtractor Circuits Learning ObjectivesSHELPTSNessuna valutazione finora

- Waveform: Figure 3: Xor Gate Using WinspiceDocumento21 pagineWaveform: Figure 3: Xor Gate Using WinspiceFritz FatigaNessuna valutazione finora

- Lab Report 1Documento4 pagineLab Report 1Zani PhiriNessuna valutazione finora

- Lab Title: Objectives: Material Required:: Sinusoidal Steady StateDocumento11 pagineLab Title: Objectives: Material Required:: Sinusoidal Steady Stateahmed shahNessuna valutazione finora

- ESim Lab ManualDocumento61 pagineESim Lab ManualDhana PrasadNessuna valutazione finora

- Lab Report 3 Digital SystemDocumento5 pagineLab Report 3 Digital Systemmuhammad adibuddinNessuna valutazione finora

- BDSSSSSSDocumento66 pagineBDSSSSSSshanmukhasaiNessuna valutazione finora

- Lab - Manual - DIGITAL LOGIC GATESDocumento38 pagineLab - Manual - DIGITAL LOGIC GATESMinh SơnNessuna valutazione finora

- Preview Report For Experiment 1: SimulationsDocumento5 paginePreview Report For Experiment 1: Simulations이훈석Nessuna valutazione finora

- Visvesvaraya National Institute of Technology Nagpur: Vlsi Design MTECH 2021-23 Nano LabDocumento12 pagineVisvesvaraya National Institute of Technology Nagpur: Vlsi Design MTECH 2021-23 Nano LabRutvik PatelNessuna valutazione finora

- Fiitjee Mid Phase Test - Hints & SolutionsDocumento4 pagineFiitjee Mid Phase Test - Hints & SolutionsAkashdeep RamnaneyNessuna valutazione finora

- ELEG 220 01 and 02 SP15 Final ExamDocumento18 pagineELEG 220 01 and 02 SP15 Final ExamSaied Aly SalamahNessuna valutazione finora

- B.Tech Curriculum 2019Documento6 pagineB.Tech Curriculum 2019parabaran VNessuna valutazione finora

- Answer Sheet LAB E3 DIGITAL MODULE - FLIP FLOP AND COUNTERDocumento7 pagineAnswer Sheet LAB E3 DIGITAL MODULE - FLIP FLOP AND COUNTERBen EdwardNessuna valutazione finora

- Electronic Lab Report 3Documento4 pagineElectronic Lab Report 3Selcan KurtNessuna valutazione finora

- Iii. Data and ResultDocumento9 pagineIii. Data and ResultHero CourseNessuna valutazione finora

- Logic Circuit SImplificationDocumento3 pagineLogic Circuit SImplificationjframil.a12139502Nessuna valutazione finora

- Lab D2 CombinationalLogicCircuitDocumento10 pagineLab D2 CombinationalLogicCircuitdhanabadee.kNessuna valutazione finora

- Tabel Data Hasil Percobaan BAB IV No. I1 (Amp) V1 (Volt) P1 (Watt) I2 (Amp) Cos Z (Ohm) R (Ohm) X (Ohm) A 1. 2. 3. 4. 5. 6. 7. 8. 9. 10Documento5 pagineTabel Data Hasil Percobaan BAB IV No. I1 (Amp) V1 (Volt) P1 (Watt) I2 (Amp) Cos Z (Ohm) R (Ohm) X (Ohm) A 1. 2. 3. 4. 5. 6. 7. 8. 9. 10alfatNessuna valutazione finora

- Electric Oscillations Lab 4Documento14 pagineElectric Oscillations Lab 4Lukas KingmaNessuna valutazione finora

- European Capacitor Material Codes: Kaizerpowerelectronics - DKDocumento6 pagineEuropean Capacitor Material Codes: Kaizerpowerelectronics - DKBookymanNessuna valutazione finora

- European Capacitor Material CodesDocumento6 pagineEuropean Capacitor Material CodesStigma1967Nessuna valutazione finora

- Es Lab ManualDocumento52 pagineEs Lab Manual19-L-0219 SainadhNessuna valutazione finora

- Date: 17/7/2008: RLC Response of Step InputDocumento32 pagineDate: 17/7/2008: RLC Response of Step InputARVINDNessuna valutazione finora

- Tda 7266Documento9 pagineTda 7266Miloud ChouguiNessuna valutazione finora

- 2N2218-2N2219 2N2221-2N2222: High-Speed SwitchesDocumento5 pagine2N2218-2N2219 2N2221-2N2222: High-Speed SwitchesAnggiet ZoaNessuna valutazione finora

- Tda 7266Documento9 pagineTda 7266hawarnetNessuna valutazione finora

- Rajshahi University of Engineering and TechnologyDocumento13 pagineRajshahi University of Engineering and TechnologysafinjunaedNessuna valutazione finora

- Wa0013Documento12 pagineWa0013Meena SinghNessuna valutazione finora

- Experiment No.: 1.1 Title: Design of Half Adder and Full Adder Circuit Using LTSPICE SoftwareDocumento13 pagineExperiment No.: 1.1 Title: Design of Half Adder and Full Adder Circuit Using LTSPICE SoftwareLima IslamNessuna valutazione finora

- Mong Bang He So Nen Thay DoiDocumento96 pagineMong Bang He So Nen Thay DoiThanh PhongNessuna valutazione finora

- Tda 7266Documento9 pagineTda 7266huitlamenNessuna valutazione finora

- DemoHisto enDocumento216 pagineDemoHisto enRapho Ponce De LNessuna valutazione finora

- Ic DigitalDocumento16 pagineIc DigitalRajashekar ReddyNessuna valutazione finora

- BTL Logic Design Lab Manual 10ESL38 3rd Sem 2011Documento67 pagineBTL Logic Design Lab Manual 10ESL38 3rd Sem 2011Manjunath JiNessuna valutazione finora

- Lab Report ElectronicDocumento41 pagineLab Report Electronichyebibie0% (1)

- Exp 10Documento2 pagineExp 10Piyas ChowdhuryNessuna valutazione finora

- ECCE4466: Power Electronics Student Lab Manual: Department of Electrical and Computer EngineeringDocumento20 pagineECCE4466: Power Electronics Student Lab Manual: Department of Electrical and Computer Engineeringsenpai_mendozaNessuna valutazione finora

- Vlsi ManualDocumento60 pagineVlsi Manualdilawar sumraNessuna valutazione finora

- Lab 5 Binary ArithmeticDocumento5 pagineLab 5 Binary ArithmeticRifah Shanjida Momo100% (1)

- Chapter-5: Results and AnalysisDocumento8 pagineChapter-5: Results and Analysis임광식Nessuna valutazione finora

- Advanced Fiitjee PaperDocumento8 pagineAdvanced Fiitjee PaperKratosNessuna valutazione finora

- Natural Frequencies of BeamsDocumento10 pagineNatural Frequencies of BeamsPurwandy HasibuanNessuna valutazione finora

- Pandit Deendayal Energy University School of Technology 5 Btech Electrical EnggDocumento2 paginePandit Deendayal Energy University School of Technology 5 Btech Electrical EnggDhanNessuna valutazione finora

- Beginning Digital Electronics through ProjectsDa EverandBeginning Digital Electronics through ProjectsValutazione: 5 su 5 stelle5/5 (1)

- British Commercial Computer Digest: Pergamon Computer Data SeriesDa EverandBritish Commercial Computer Digest: Pergamon Computer Data SeriesNessuna valutazione finora

- Two-Phase Hybrid Cryptography Algorithm For Wireless Sensor NetworksDocumento18 pagineTwo-Phase Hybrid Cryptography Algorithm For Wireless Sensor NetworksJanjan IruguinNessuna valutazione finora

- Lecture 1 - Transmission Line Theory Version 3Documento55 pagineLecture 1 - Transmission Line Theory Version 3Anup NaskarNessuna valutazione finora

- David K. Cheng - Field and Wave ElectromagneticsDocumento515 pagineDavid K. Cheng - Field and Wave Electromagneticsnikee7285% (26)

- Module 9 PDFDocumento23 pagineModule 9 PDFJanjan IruguinNessuna valutazione finora

- Multipleaccessppt PDFDocumento54 pagineMultipleaccessppt PDFJanjan IruguinNessuna valutazione finora

- A Web Based IoT Solution For Monitoring DataDocumento1 paginaA Web Based IoT Solution For Monitoring DataJanjan IruguinNessuna valutazione finora

- The Cloverleaf Antenna: A Compact Wide-Bandwidth Dual-Polarization Feed For CHIMEDocumento3 pagineThe Cloverleaf Antenna: A Compact Wide-Bandwidth Dual-Polarization Feed For CHIMEJanjan IruguinNessuna valutazione finora

- HistoryDocumento23 pagineHistoryJanjan IruguinNessuna valutazione finora

- School of Tourism Management: Submitted byDocumento7 pagineSchool of Tourism Management: Submitted byJanjan IruguinNessuna valutazione finora

- Go, Maria Dannica M. - OJT1 Weekly ReportDocumento11 pagineGo, Maria Dannica M. - OJT1 Weekly ReportJanjan IruguinNessuna valutazione finora

- MEC1633Documento12 pagineMEC1633potatoNessuna valutazione finora

- 5 - SP3000 - Frontier Installation ProcedureDocumento42 pagine5 - SP3000 - Frontier Installation ProcedureDavide Lacchini100% (1)

- Keep in Mind The Five Key Test Points LCD Screen Logic BoardDocumento2 pagineKeep in Mind The Five Key Test Points LCD Screen Logic BoardClubedoTecnicoNessuna valutazione finora

- HCF 4082Documento7 pagineHCF 4082parayasa50Nessuna valutazione finora

- 00 IntroductionDocumento15 pagine00 IntroductionEzhilarasan KaliyamoorthyNessuna valutazione finora

- Module III-Chapter-4-SMATV SystemDocumento16 pagineModule III-Chapter-4-SMATV SystemJeNessuna valutazione finora

- DatasheetDocumento61 pagineDatasheetalv.Nessuna valutazione finora

- FINAL-GROUP-5 Transistors BJT Oct 14asdsdasdDocumento27 pagineFINAL-GROUP-5 Transistors BJT Oct 14asdsdasdFrancis Valdez LopezNessuna valutazione finora

- EC8352 LessonPlanDocumento7 pagineEC8352 LessonPlanramarajanNessuna valutazione finora

- Multistage Transistor AmplifiersDocumento8 pagineMultistage Transistor Amplifiersbree789Nessuna valutazione finora

- User ManualDocumento19 pagineUser ManualЮрий ГерасимюкNessuna valutazione finora

- Analog & Digital SignalsDocumento15 pagineAnalog & Digital SignalsNouman MemonNessuna valutazione finora

- CD4093BM/CD4093BC Quad 2-Input NAND Schmitt Trigger: General DescriptionDocumento6 pagineCD4093BM/CD4093BC Quad 2-Input NAND Schmitt Trigger: General DescriptionCristian MorenoNessuna valutazione finora

- MRDocumento1 paginaMRRyke Dwiko PuteriNessuna valutazione finora

- Epson R800 SMDocumento174 pagineEpson R800 SMInteletracNessuna valutazione finora

- XS1010 1212INSTfinalDocumento6 pagineXS1010 1212INSTfinalTitus-Adelin IonNessuna valutazione finora

- 9.3 Astable Multivibrator: Return NextDocumento8 pagine9.3 Astable Multivibrator: Return Nextsankar2015Nessuna valutazione finora

- C VIEWDocumento1 paginaC VIEWarcheranmNessuna valutazione finora

- Autocycle IcDocumento2 pagineAutocycle Iccanales117Nessuna valutazione finora

- User'S Guide: Easycoder® Pd42 PrinterDocumento126 pagineUser'S Guide: Easycoder® Pd42 Printerkrana26Nessuna valutazione finora

- Project Title: Wireless Power Transmission Using Tesla Coil AbstractDocumento5 pagineProject Title: Wireless Power Transmission Using Tesla Coil AbstractKalyan Reddy AnuguNessuna valutazione finora

- Bruce Array Antenna - Coaxial Whip AntennaDocumento3 pagineBruce Array Antenna - Coaxial Whip AntennaRobert TurnerNessuna valutazione finora

- Aoc Le32a1326 Le32a3520 715G4629 - M01 - 000 - 004KDocumento83 pagineAoc Le32a1326 Le32a3520 715G4629 - M01 - 000 - 004KFrancisco Antonio50% (2)

- Manual FW230 PDFDocumento16 pagineManual FW230 PDFaze20100% (1)

- EC1 (1) Phy, LABDocumento4 pagineEC1 (1) Phy, LABalhassanthNessuna valutazione finora

- Lecture 6 Optical ModulatorsDocumento26 pagineLecture 6 Optical ModulatorsSyed Muhammad DanishNessuna valutazione finora

- Antenna SpecificationsDocumento2 pagineAntenna SpecificationsRobertNessuna valutazione finora

- Amit Kaushik 8008Documento13 pagineAmit Kaushik 8008Tanya GosainNessuna valutazione finora

- FMG3015-R20A: Gigabit Active Fiber Bridge With CATVDocumento4 pagineFMG3015-R20A: Gigabit Active Fiber Bridge With CATVppancxooNessuna valutazione finora