Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Physical Design

Caricato da

Shweth0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

64 visualizzazioni11 pagineit has all questions of physical design.

Titolo originale

physical design

Copyright

© © All Rights Reserved

Formati disponibili

DOCX, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoit has all questions of physical design.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOCX, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

64 visualizzazioni11 paginePhysical Design

Caricato da

Shwethit has all questions of physical design.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOCX, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 11

1. list of all inputs to start PD flow and whats inside.

In which file standard

cells height and row information's mentioned.

2. Sanity checks?

3. whats the effects with input floating nets in netlist and what do you do ?

4. channel length calculation and where is the information's of macros given.

5. setup and hold time definitions with diagram.

6. why clock period is not required in hold time calculation.

7. basics of latchup and remedies

8. how does tools do placement optimizations

9. crosstalk and remedies.

10.Antenna and remedies.

11.time borrowing concepts in latches.

12.Draw INV, AND and OR gate using 2 inputs mux.

13.why we need setup and hold time for flops.

14.define meta-stable state and Noise margins.

15.inter gate clocking (IGT) why do we use it? (what is static and dynamic

power co

16.nsumption's).

17.define CMOS operating modes with drain current equation.

18.what is crosstalk window concepts.

19.Antenna effects and remedies.

20.who is your client?, what are the tools did you used?

21.what are the inputs did you get form synthesis guy?

22.how did you validate that?

23.some questions on SDC check

24.pick any one of block and explain PD flow.how did you place macros?

25.what is the minimum space did you follow in your design?

26.present technologies not using straps for macros, then what is the use to

give VDD and VSS in between two macros

27.what are the metal layers did you used in your design?

28.M1 is used for standard cells, so which layer did you connected this M1 -

means did you connected to M9 or M8?

29.what are the checks you have done after placement

30.what are the inputs required to start CTS?

31.what is the spec file consists of: he is expecting each and every statements

in the spec file

32.how did you analyse setup reports?

33.what is the reasons for set up (by seeing the report we should give the

answer-not theoretically

34.how did you overcome that?

35.what is DRV, what are those?

36.how did you fixed tran violation?

37.Do you know IR drop, did you work on IR drop tool?

38.what is the important of clock gating?

39.where will you place the clock gating cells-near to source or sync?

40.what are the DRC's did you faced?

41.list out any 10 DRC.

42.insertion and skew delay for your design.

43.How did you overcome the congestion?

44.Out of all paths how did you know which cell is giving setup violation and

how did you overcome that.

45.what is the minimum space did you follow in your design?

46.present technologies not using straps for macros, then what is the use to

give VDD and VSS in between two macros

47.M1 is used for standard cells, so which layer did you connected this M1 -

means did you connected to M9 or M8?

48.where will you place the clock gating cells-near to source or sync?

49.what are the DRC's did you faced? 22. list out any 10 DRC.

50.how did you start your Project flow? (Expectation was to mention all

inputs and from whom we get, sanity checks and why we do it)

51.Floorplan (expectation was to explain wrt one block)

52.Do we need to keep spacing between macro if it doesnât have pins

facing each other.( expectation was to justify our answer)

53.In the flow why macros were placed only at the bottom

54.How do we Qualify floorplan

55.Before starting placement what we do?

56.Congestion and solution

57.Checks after placement

58.Qualifying placement

59.Before starting cts what we need to do (analyze the quality of placement)

60.Inputs to CTS

61.What we analyze after CTS

62.How we can tell CTS is build properly

63.Clock path (why do we set transition limit) If library has max tran limit of

1ns and you are getting 900ps as transition value, can you take it further

(No as c

64.lock tree has a chain of buffer we will see min pulse width violation

âclock absorptionâ)

65.What you did in routing

66.Steps in routing

67.Have you run caliber (inputs to DRC and LVS)

68.List some DRCâs and LVS issues

69.timing problem to calculate setup and hold slack

70.explain vth ( on what it depends )

71.explain latchup( how do you reduce )

72.why are fillers used

73.what are end cap cells ?

74.what are decap cells ?

75.Power planning, EM violation - he expected more :-)

76.Do we place anything b/w Macros?

77.How do you estimate die size?

78.How do you calculate Aspect Ratio?

79.How you place macros? For my exp, 10-15 Macros was not sufficient. He

was expect

80.ing 100/150+ M ï

81.Do you know test mode? How do you insert scan chains? How it is done?

82.Do you know about set_false_path, clock_groups, mutually_exclusive,

asynchronous case_analysis?

83.Case 1: there is a 2:1 mux. set_case_analysis is set to â0â.Case 2: there

is another 2:1mux. set_disable_timing is set on B->Y.What is the

difference? Explain w.r.t timing arcs.

84.What is the difference b/w Exclude pin and Ignore Pin?

85.Command to spread the cells.

86.During Placement if more cells are added(utilization increases) by the tool,

what could be the reason?

87.How setup/hold analysis are done on CGCs?

88.Why ENDCAP and WELL TAP are added before Placement only?

89.During FloorPlan, if IO info is not given, then how will you proceed? Say,

you cant ask the manager(he too doesn't know) nor you can assume and

add.

90.Let's say after Placement there is setup violation. What will you do? How

will you analyze? How will you validate the violation?

91.Why power stripes routed in the top metal layers?

92.Why do you use alternate routing approach HVH/VHV (Horizontal-

Vertical-Horizontal/Vertical-Horizontal-Vertical)?

93.What are several factors to improve propagation delay of standard cell?

94.How do you compute net delay (interconnect delay) / decode RC values

present in tech file?

95.What are various ways of timing optimization in synthesis tools?

96.What would you do in order not to use certain cells from the library?

97.How delays are characterized using WLM (Wire Load Model)?

98.What are various techniques to resolve congestion/noise?

99.Letâs say there enough routing resources available, timing is fine, can

you increase clock buffers in clock network? If so will there be any impact

on other parameters?

100. How do you optimize skew/insertion delays in CTS (Clock Tree

Synthesis)?

101. What are pros/cons of latch/FF (Flip Flop)?

102. How you go about fixing timing violations for latch- latch paths?

103. As an engineer, letâs say your manager comes to you and asks for

next project die size estimation/projection, giving data on RTL size,

performance requirements. Howdo you goabout the figuring out and come

up with die size considering physical aspects?

104. How will you design inserting voltage island scheme between macro

pins crossing

105. core and are at different power wells? What is the optimal resource

solution?

106. What are various formal verification issues you faced and how did

you resolve?

107. How do you calculate maximum frequency given setup, hold, clock

and clock skew?

108. What are effects of meta-stability?

109. What are the challenges you faced in place and route, FV (Formal

Verification),

110. ECO(Engineering Change Order) areas?

111. How long the design cycle for your designs?

112. What part are your areas of interest in physical design?

113. Explain ECO (Engineering Change Order) methodology.

114. Explain CTS (Clock Tree Synthesis) flow.

115. What kind of routing issues you faced?

116. How does STA (Static Timing Analysis) in OCV (On Chip Variation)

conditions done? How do you set OCV (On Chip Variation) in IC

compiler? How is timing correlation done before and after place and

route?

117. If there are too many pins of the logic cells in one place within core,

what kind of issues would you face and how will you resolve?

118. Define hash/ @array in perl.

119. Using TCL (Tool Command Language, Tickle) how do you set

variables?

120. What is ICC (IC Compiler) command for setting derate factor/

command to perform

121. physical synthesis?

122. What are nano route options for search and repair?

123. What were your design skew/insertion delay targets?

124. How is IR drop analysis done? What are various statistics available in

reports?

125. Explain pin density/ cell density issues, hotspots?

126. How will you relate routing grid with manufacturing grid and judge if

the routing grid is set correctly?

127. What is the command for setting multi cycle path?

128. If hold violation exists in design, is it OK to sign off design? If not,

why?

129. How are timing constraints developed?

130. Explain timing closure flow/methodology/issues/fixes.

131. Explain SDF (Standard Delay Format) back annotation/ SPEF

(Standard Parasitic Exchange Format) timing correlation flow.

132. Given a timing path in multi-mode multi-corner, how is STA (Static

Timing Analysis) performed in order to meet timing in both modes and

corners, how are PVT (Process-Voltage-Temperature)/derate factors

decided and set in the Primetime flow?

133. With respect to clock gate, what are various issues you faced at

various stages in the physical design flow?

134. What are synthesis strategies to optimize timing?

135. Explain ECO (Engineering Change Order) implementation flow.

Given post routed database and functional fixes, how will you take it to

implement ECO (EngineeringC

136. hange Order) and what physical and functional checks you need to

perform?

137. In building the timing constraints, do you need to constrain all IO

(Input-Output) ports?

138. Can a single port have multi-clocked? How do you set delays for such

ports?

139. How is scan DEF (Design Exchange Format) generated?

140. What is purpose of lock up latch in scan chain?

141. How do you set inter clock uncertainty?

142. In DC (Design Compiler), how do you constrain clocks, IO (Input-

Output) ports, maxcap,max tran?

143. What are differences in clock constraints from pre CTS (Clock Tree

Synthesis) to post

144. How is clock gating done?

145. what constraints you add in CTS (Clock Tree Synthesis) for clock

gates?

146. What is tradeoff between dynamic power (current) and leakage power

(current)?

147. How do you reduce standby (leakage) power?

148. Explain top level pin placement flow? What are parameters to decide?

149. Given block level netlists, timing constraints, libraries, macro LEFs

(Layout Exchange Format/Library Exchange Format), how will you start

floor planning?

150. With net length of 1000um how will you compute RC values, using

equations/tech file info?

151. What do noise reports represent?

152. What does glitch reports contain?

153. What are CTS (Clock Tree Synthesis) steps in IC compiler?

154. What do clock constraints file contain?

155. How to analyze clock tree reports?

156. What do IR drop Voltagestorm reports represent?

157. Where /when do you use DeCAP (Decoupling Capacitor) cells?

158. What are various power reduction techniques?

159. What is setup/hold? What are setup and hold time impacts on timing?

How will you fix setup and hold violations?

160. Explain function of Muxed FF (Multiplexed Flip Flop) /scan FF (Scal

Flip Flop).

161. What are tested in DFT (Design for Testability)?

162. In equivalence checking, how do you handle scan en signal?

163. In terms of CMOS (Complimentary Metal Oxide Semiconductor),

explain physical parameters that affect the propagation delay?

164. Why is power signal routed in top metal layers?

165. How do you minimize clock skew/ balance clock tree?

166. Given 11 minterms and asked to derive the logic function.

167. Given C1= 10pf, C2=1pf connected in series with a switch in

between, at t=0 switch is open and one end having 5v and other end zero

voltage; compute the voltage across C2 when the switch is closed?

168. Explain the modes of operation of CMOS (Complimentary Metal

Oxide Semiconductor) inverter? Show IO (Input-Output) characteristics

curve.Implement a ring oscillator.

169. How to slow down ring oscillator?

170. How do you optimize power at various stages in the physical design

flow?

171. What timing optimization strategies you employ in pre-layout /post-

layout stages?

172. What are process technology challenges in physical design?

173. Design divide by 2, divide by 3, and divide by 1.5 counters. Draw

timing diagrams.

174. What are multi-cycle paths, false paths? How to resolve multi-cycle

and false paths?

175. Given a flop to flop path with combo delay in between and output of

the second flop feedback to combo logic. Which path is fastest path to

have hold violation and how will you resolve?

176. What are RTL (Register Transfer Level) coding styles to adapt to

yield optimal backend design?

177. Draw timing diagrams to represent the propagation delay, set up, hold,

recovery,removal, minimum pulse width.

178. Do you know about input vector controlled method of leakage

reduction?

179. How can you reduce dynamic power?

180. What are the vectors of dynamic power?

181. How will you do power planning?

182. If you have both IR drop and congestion how will you fix it?

183. Is increasing power line width and providing more number of straps

are the only solution to IR drop?

184. In a reg to reg path if you have setup problem where will you insert

buffer-near to launching flop or capture flop? Why?

185. How will you decide best floorplan?

186. What is the most challenging task you handled?

187. What is the most challenging job in P&R flow?

188. How will you synthesize clock tree?

189. How many clocks were there in this project?

190. How did you handle all those clocks?

191. Are they come from seperate external resources or PLL?

192. Why buffers are used in clock tree?

193. What is cross talk?

194. How can you avoid cross talk?

195. How shielding avoids crosstalk problem? What exactly happens

there?

196. How spacing helps in reducing crosstalk noise?

197. Why double spacing and multiple vias are used related to clock?

198. How buffer can be used in victim to avoid crosstalk?

199. What parameters (or aspects) differentiate Chip Design & Block level

design??

200. How do you place macros in a full chip design?

201. Differentiate between a Hierarchical Design and flat design?

202. Which is more complicated when u have a 48 MHz and 500 MHz

clock design?

203. Name few tools which you used for physical verification?

204. What are the input files will you give for primetime correlation?

205. What are the algorithms used while routing? Will it optimize wire

length?

206. How will you decide the Pin location in block level design?

207. If the routing congestion exists between two macros, then what will

you do?

208. How will you place the macros?

209. How will you decide the die size?

210. If lengthy metal layer is connected to diffusion and poly, then which

one will affect by antenna problem?

211. If the full chip design is routed by 7 layer metal, why macros are

designed using 5LM instead of using 7LM?

212. How did u handle the Clock in your design?

213. What are the Input needs for your design?

214. What is SDC constraint file contains?

215. How did you do power planning?

216. How to find total chip power?

217. How to calculate core ring width, macro ring width and strap or trunk

width?

218. How to find number of power pad and IO power pads?

219. What are the problems faced related to timing?

220. How did u resolve the setup and hold problem?

221. If in your design 10000 and more numbers of problems come, then

what you will do?

222. In which layer do you prefer for clock routing and why?

223. If in your design has reset pin, then itâll affect input pin or output

pin or both?

224. During power analysis, if you are facing IR drop problem, then how

did u avoid?

225. Define antenna problem and how did u resolve these problem?

226. How delays vary with different PVT conditions? Show the graph.

227. Explain the flow of physical design and inputs and outputs for each

step in flow.

228. What is cell delay and net delay?

229. What are delay models and what is the difference between them?

230. What is wire load model?

231. What does SDC constraints has?

232. Why higher metal layers are preferred for Vdd and Vss?

233. What is logic optimization and give some methods of logic

optimization.

234. What is the significance of negative slack?

235. What is signal integrity? How it affects Timing?

236. What is IR drop? How to avoid .how it affects timing?

237. What is EM and it effects?

238. What are types of routing?

239. What is a grid .why we need and different types of grids?

240. What is core and how u will decide w/h ratio for core?

241. What is effective utilization and chip utilization?

242. What is latency? Give the types?

243. How the width of metal and number of straps calculated for power

and ground?

244. What is negative slack ? How it affects timing?

245. What is track assignment?

246. What is grided and gridless routing?

247. What is a macro and standard cell?

248. What is congestion?

249. Whether congestion is related to placement or routing?

250. What are clock trees?

251. What are clock tree types?

252. Which layer is used for clock routing and why?

253. What is cloning and buffering?

254. What are placement blockages?

255. How slow and fast transition at inputs effect timing for gates?

256. What is antenna effect?

257. What are DFM issues?

258. What is .lib, LEF, DEF, .tf?

259. What is the difference between synthesis and simulation?

260. What is metal density, metal slotting rule?

261. What is OPC, PSM?

262. Why clock is not synthesized in DC?

263. What are high-Vt and low-Vt cells?

264. What corner cells contains?

265. What is the difference between core filler cells and metal fillers?

266. How to decide number of pads in chip level design?

267. What is tie-high and tie-low cells and where it is used

268. What is LEF?

269. What is DEF?

270. what is techfile?

271. what is .tf?

272. what is .lib?

273. what is .db file?

274. What are the steps involved in designing an optimal pad ring?

275. What are the steps that you have done in the design flow?

276. What are the issues in floor plan?

277. How can you estimate area of block?

278. How much aspect ratio should be kept (or have you kept) and what is

the utilization?

279. How to calculate core ring and stripe widths?

280. What if hot spot found in some area of block? How you tackle this?

281. After adding stripes also if you have hot spot what to do?

282. What is threshold voltage? How it affect timing?

283. What is content of lib, lef, sdc?

284. What is meant my 9 track, 12 track standard cells?

285. What is scan chain? What if scan chain not detached and reordered? Is

it compulsory?

286. What is setup and hold? Why there are ? What if setup and hold

violates?

287. In a circuit, for reg to reg path ...Tclktoq is 50 ps, Tcombo 50ps,

Tsetup 50ps,

288. tskew is 100ps. Then what is the maximum operating frequency?

289. How R and C values are affecting time?

290. How ohm (R), fared (C) is related to second (T)?

291. What is transition? What if transition time is more?

292. What is difference between normal buffer and clock buffer?

293. What is antenna effect? How it is avoided?

294. What is ESD?

295. What is cross talk? How can you avoid?

296. How double spacing will avoid cross talk?

297. What is difference between HFN synthesis and CTS?

298. What is hold problem? How can you avoid it?

299. For an iteration we have 0.5ns of insertion delay and 0.1 skew and for

other iteration 0.29ns insertion delay and 0.25 skew for the same circuit

then which one you will select? Why?

300. What is partial floor plan?

Potrebbero piacerti anche

- The Nanofab Group: EE 4345 - Semiconductor Electronics Design Project - Spring 2002Documento24 pagineThe Nanofab Group: EE 4345 - Semiconductor Electronics Design Project - Spring 2002ShwethNessuna valutazione finora

- ELEC 353 Latch Up PDFDocumento20 pagineELEC 353 Latch Up PDFShwethNessuna valutazione finora

- SDCDocumento17 pagineSDCShwethNessuna valutazione finora

- NMOS FundamentalsDocumento71 pagineNMOS FundamentalsManjit KaurNessuna valutazione finora

- Set Clock Groups - Micro-IP IncDocumento6 pagineSet Clock Groups - Micro-IP IncShwethNessuna valutazione finora

- What Is Timing Analysis PDFDocumento62 pagineWhat Is Timing Analysis PDFShwethNessuna valutazione finora

- 09 PlacementDocumento41 pagine09 PlacementRaffi SkNessuna valutazione finora

- Faults, Testing & Test GenerationDocumento34 pagineFaults, Testing & Test GenerationShwethNessuna valutazione finora

- Physical Design For Asic - Linux PDFDocumento7 paginePhysical Design For Asic - Linux PDFShwethNessuna valutazione finora

- VT STD CellsDocumento40 pagineVT STD CellsJithin SNessuna valutazione finora

- Synopsys Class 2 5 1Documento67 pagineSynopsys Class 2 5 1prashanth kumarNessuna valutazione finora

- 09 PlacementDocumento41 pagine09 PlacementRaffi SkNessuna valutazione finora

- Ir Drop and Electro Migeration Desing Flow PDFDocumento29 pagineIr Drop and Electro Migeration Desing Flow PDFSonu SangwanNessuna valutazione finora

- Standard CellDocumento53 pagineStandard CellShwethNessuna valutazione finora

- LefdefrefDocumento32 pagineLefdefrefSandesh Kumar B VNessuna valutazione finora

- PD Flow I - Floorplan - Physical Design, STA & Synthesis, DFT, Automation & Flow Dev, Verification Services. Turnkey ProjectsDocumento21 paginePD Flow I - Floorplan - Physical Design, STA & Synthesis, DFT, Automation & Flow Dev, Verification Services. Turnkey ProjectsShwethNessuna valutazione finora

- Difference Between Eco and FillerDocumento1 paginaDifference Between Eco and FillerShwethNessuna valutazione finora

- Fab StepsDocumento20 pagineFab StepsShwethNessuna valutazione finora

- Lect05 LIBDocumento14 pagineLect05 LIBarnabd88Nessuna valutazione finora

- VLSI Basics - Clock Tree OptimizationDocumento3 pagineVLSI Basics - Clock Tree OptimizationShwethNessuna valutazione finora

- Chap4-111206 Placement AlgorithmDocumento63 pagineChap4-111206 Placement AlgorithmAnait Ul HaqueNessuna valutazione finora

- PD InputsDocumento3 paginePD InputsShwethNessuna valutazione finora

- CamScanner ScansDocumento9 pagineCamScanner ScansShwethNessuna valutazione finora

- ASIC Design TypesDocumento28 pagineASIC Design TypesShwethNessuna valutazione finora

- Class 08: NMOS, Pseudo-NMOSDocumento6 pagineClass 08: NMOS, Pseudo-NMOSPoonam Pratap KadamNessuna valutazione finora

- Standard Cell Types and Their UsesDocumento8 pagineStandard Cell Types and Their UsesShwethNessuna valutazione finora

- Physical Design PDFDocumento11 paginePhysical Design PDFShwethNessuna valutazione finora

- Digital VLSI Design Timing Analysis: Semester A, 2018-19 Lecturer: Dr. Adam TemanDocumento72 pagineDigital VLSI Design Timing Analysis: Semester A, 2018-19 Lecturer: Dr. Adam TemanAsShabNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Cablescout ManualDocumento2 pagineCablescout ManualArturo Orozco CastilloNessuna valutazione finora

- Tdf-4-Mu - Time-Lag User Manual - enDocumento36 pagineTdf-4-Mu - Time-Lag User Manual - enBilal WirkNessuna valutazione finora

- Zone Selective Interlocking On Instantaneous (I-ZSI) PDFDocumento7 pagineZone Selective Interlocking On Instantaneous (I-ZSI) PDFjumpingjack229Nessuna valutazione finora

- ErrataDocumento2 pagineErrataRalph J LagdaminNessuna valutazione finora

- Serie CE-65 Absolute Rotary EncoderDocumento38 pagineSerie CE-65 Absolute Rotary EncoderCarlos DenedNessuna valutazione finora

- Reverse Engineering Power Management On NVIDIADocumento9 pagineReverse Engineering Power Management On NVIDIALeofodãoNessuna valutazione finora

- Fizik Lab ReportDocumento5 pagineFizik Lab ReportnajwaNessuna valutazione finora

- Services HarshitaDocumento1 paginaServices HarshitaMs.Muskaan JainNessuna valutazione finora

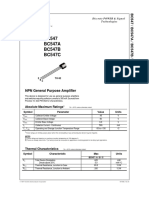

- BC547 BC547A BC547B BC547C: NPN General Purpose AmplifierDocumento2 pagineBC547 BC547A BC547B BC547C: NPN General Purpose Amplifierﺑﺮﻫﺎﻥ ﺍﻟﺘﻤﻴﻤﻲNessuna valutazione finora

- Project Standards and Specifications Power System Design Rev01Documento9 pagineProject Standards and Specifications Power System Design Rev01totongopNessuna valutazione finora

- Noise Suppression EMIFILr Capacitor Signal Lines Data SheetDocumento2 pagineNoise Suppression EMIFILr Capacitor Signal Lines Data SheetJuan CoronelNessuna valutazione finora

- Sony 6060fw Service Manual SearchableDocumento54 pagineSony 6060fw Service Manual SearchablefacundoenNessuna valutazione finora

- Unit 2Documento16 pagineUnit 2danishmaniNessuna valutazione finora

- Code of Practice For Power System ProtectionDocumento3 pagineCode of Practice For Power System ProtectionR.EASWARANNessuna valutazione finora

- Steval Astra1bDocumento28 pagineSteval Astra1bRemi SarkisNessuna valutazione finora

- Ansys Ansoft MaxwellDocumento2 pagineAnsys Ansoft MaxwellGustavo Myrria0% (1)

- NEA Electrical EstimateDocumento40 pagineNEA Electrical EstimateSurendra MaharjanNessuna valutazione finora

- Huawei 5G Power BoostLi ESM-48150B1 Datasheet Draft A - (20201111)Documento2 pagineHuawei 5G Power BoostLi ESM-48150B1 Datasheet Draft A - (20201111)Odai Kiwan100% (2)

- 1220e Manual enDocumento72 pagine1220e Manual enAlexandra GarciaNessuna valutazione finora

- ECE3073 2014 Lab 3Documento5 pagineECE3073 2014 Lab 3Andrew WalleyNessuna valutazione finora

- Industrial Ethernet Switch GuideDocumento22 pagineIndustrial Ethernet Switch GuideSivertNessuna valutazione finora

- Service Manual A3300M ....Documento59 pagineService Manual A3300M ....QooNessuna valutazione finora

- Powerone p110002Documento13 paginePowerone p110002Jim BeanNessuna valutazione finora

- Full-Wave Center-Tapped Rectifier Tutorial - Basic Electronics - EnglishDocumento5 pagineFull-Wave Center-Tapped Rectifier Tutorial - Basic Electronics - EnglishMuhammad Al WafiNessuna valutazione finora

- 3.20 Fire Alarm Notification WireDocumento4 pagine3.20 Fire Alarm Notification WireJamesNessuna valutazione finora

- OsiSense XC Special Format - XR2AB04K80Documento3 pagineOsiSense XC Special Format - XR2AB04K80BOURICHNessuna valutazione finora

- Chapter 2 TransformerDocumento58 pagineChapter 2 Transformerquocdung NguyenNessuna valutazione finora

- V I CharacteristicsDocumento3 pagineV I CharacteristicsJoshua DuffyNessuna valutazione finora

- 3730-1 Positioner for Pneumatic Control ValvesDocumento6 pagine3730-1 Positioner for Pneumatic Control ValvesJuan MuñozNessuna valutazione finora

- Smartfem: Analysis and Design of Electrical DrivesDocumento49 pagineSmartfem: Analysis and Design of Electrical DrivesM. T.Nessuna valutazione finora