Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

VLSI

Caricato da

akramuddin mohammedTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

VLSI

Caricato da

akramuddin mohammedCopyright:

Formati disponibili

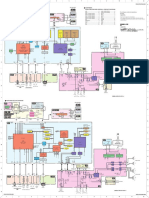

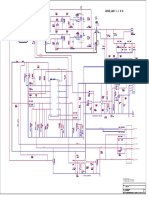

WSP Upstream Perim Upstream Perim Downstream

250MHz max AXI4 (64)

Async AXI2AXI

clk_fic64_2 fic2_aclk

WSP Downstream

fic_2 DLL (FIC2)

Feedthroughs

250MHz max AXI4 (64)

Async AXI2AXI

Redund clk_fic64_0 fic0_aclk

ATPG DLL (FIC0)

WTAP MBIST ancy AXI4 (64)

AXI Bus Trace

FPGA Fabric

OCCs fic_0 Async AXI2AXI

Control Trace

Note: All AXI buses with red dot are Async AXI2AXI 250MHz max AXI4 (64)

Fed into Trace block for monitoring

clk_fic64_1 fic1_aclk

Processor DLL (FIC1)

AXI4 (64)

AXI4 (64)

Instruction Trace fic_1 Async AXI2AXI

fic4_hclk

JTAG DLL (FIC4)

AXI4 (64)

clk_crypto

AHBL (32)

(WSP overlay)

mss_cpu_core MPU AHBL (32) Streaming i/f

AHBL (32)

Async AHB2AXI

JTAG

User

AHBL (32) Crypto

Async AXI2AHB AHBL (32) GMII

M15 /MII

AXI4 (64) AXI4 (64)

JTAG M3 AHBL (32)

corecomplex AXI4 (64) AXI4 (64) fic_4 200MHz max

S9 M1 125MHz

AXI4 (64) AXI4 (64)

M2

SGMII

PHY

AXI4 (64) AXI4 (64)

M4 TBI

AXI to TileLink

Debug Module

Platform Level

Interrupt Control SCB

TileLink

FPGA Fabric

AXI4 (64) AXI4 (64) AXI4 (64)

S8 M5 GEM_0

Downstream

DMA Engine

MPU

JTAG 800MHz Private

IOSCB

AXI4 (64) AXI4 (64) SCB

max M6 GEM_1 SysReg BRIDGE SCB

E51 U54 U54 U54 U54

16KB L1 I$ 32KB L1 I$ or 32KB L1 I$ or 32KB L1 I$ or 32KB L1 I$ or

AXI4 (64) AXI4 (64) AHB AHBL (32) USB

M7 2AXI

or 8KB ITIM 28KB ITIM 28KB ITIM 28KB ITIM 28KB ITIM 2.0 AXI4 (64)

AXI Switch

SCB clk_ioscb

AXI4 (64) P (80MHz)

AXI4 (64) AXI AXI4 (64) eMMC/

RV64IMAC RV64GC RV64GC RV64GC RV64GC M8 2AXI

H

Async

SD/SDIO Y

AXI2AXI

Upstream

8KB DTIM 32KB L1 D$ 32KB L1 D$ 32KB L1 D$ 32KB L1 D$ AXI4 (64) SCB

AXI4 (64)

IOSCB

M9 MASTER SCB

AXI4 (64) (MSS

AXI4 (64) S4 DRI)

D0 M10 AXI4 (64) ULPI

S1

TileLink to AXI

AXI4 (64)

D1 M11 AXI4 (64)

clk_cpu S2

MSS AXI4 (64)

(800MHz max) F0 M12 AXI4 AXI2 AHBL (32)

Clock TileLink B64 D128 Switch S5

clk_axi F1 AXI4 (64) M13 (64) AHB

AHB2 APB (32) eNVM

Control Controller

eNVM

(400MHz max) AXI4 (64) APB

WCB NC M14 AXI4 AXI2

S6 AHBL (32)

(64) AHB

MSS Corner

clk_in_mss AHB2

(800MHz) APB QSPI-XIP

TileLink Coherence Manager AXI4 (64)

S3 Watchdog_0

AXI4 (64) Watchdog_1

400MHz S7 APB (32) Watchdog_2

Watchdog_3

MSS IO

max

clk_in_reference 2MB L2 Cache/Scratchpad or 1.875MB LIM Watchdog_4 clk_usb (60MHz)

APB (32) MSS_GPIO_0

(125MHz) eMMC Device

MSS_GPIO_1

Note: Secondary APB is also SDINBDG4-8G

connected MSS_GPIO_2

to all peripherals and user may

Timer configure each peripheral to be CDC CAN_0

accessed by primary or secondary

CDC CAN_1

TL2AXI4 400MHz SPI_0

max IOMUX

(128)

AXI4

SPI_1

MMUART_0

clk_rtc MMUART_1

MMUART_2

(1MHz) MMUART_3

MMUART_4

FPGA Fabric

Seg Seg

400MHz I2C_0

AXI4

(128)

(64)

AXI4

max

Cacheable DDR Non-cacheable DDR I2C_1

CDC CDC APB (32)

PROJECT FRQMETER

G5SoC DDR Controller MSTIMER

H2FINTCTRL interrupt

(400MHz)

clk_in_dfi

TITLE MSS Functional L2 Cache MBIST fic3_pclk

fic_3 clk_fic64_3 DLL (FIC3)

Partition DFI (half rate) RTC

3850 North 1st Street 128b @ 400MHz Async APB (32)

REV 1.37

San Jose, CA 95134 AXI2APB 250MHz max

DRAWN

Ciaran Murphy MSS DDR PHY SGMII PHY

BY

(32/36b DDR-1600 @ IO pads)

MSS DDR Training

DATE 21 Mar 2019 SHEET 1 of 1

Potrebbero piacerti anche

- Instant Assessments for Data Tracking, Grade 2: MathDa EverandInstant Assessments for Data Tracking, Grade 2: MathNessuna valutazione finora

- Instant Assessments for Data Tracking, Grade 4: MathDa EverandInstant Assessments for Data Tracking, Grade 4: MathValutazione: 5 su 5 stelle5/5 (2)

- Acd-Gf-Phase 1Documento1 paginaAcd-Gf-Phase 1locNessuna valutazione finora

- Schematics Blackberry 9700-OnyxDocumento18 pagineSchematics Blackberry 9700-OnyxedgarNessuna valutazione finora

- Motorola V3 1Documento3 pagineMotorola V3 1Techno Max IT SolutionsNessuna valutazione finora

- Dortoir AAA-plan Clim Étage 1Documento1 paginaDortoir AAA-plan Clim Étage 1lando de chanceNessuna valutazione finora

- Level 3 Repair: 8-1. Block DiagramDocumento79 pagineLevel 3 Repair: 8-1. Block DiagramAli UnlockNessuna valutazione finora

- CRT Board: Subject To Change Without NoticeDocumento2 pagineCRT Board: Subject To Change Without NoticeVlade NaumovskiNessuna valutazione finora

- Samsung GT E3210 08 Level 3 Repair Block PCB Diagrams Flow Chart of TroubleshootingDocumento38 pagineSamsung GT E3210 08 Level 3 Repair Block PCB Diagrams Flow Chart of TroubleshootingMayank Mani SinghNessuna valutazione finora

- 311 Ebd 9010 - 1Documento1 pagina311 Ebd 9010 - 1Angel Lazarte DueñasNessuna valutazione finora

- East Midland Wallasey SidDocumento1 paginaEast Midland Wallasey Sidmax.kirzinger01Nessuna valutazione finora

- BRONZE - VNS LAB InformationDocumento6 pagineBRONZE - VNS LAB InformationClaudio SalinasNessuna valutazione finora

- Bus Blaster-Stm32Documento1 paginaBus Blaster-Stm32Ahmad AzharNessuna valutazione finora

- (Vietmobile - VN) : 8. Level 3 RepairDocumento45 pagine(Vietmobile - VN) : 8. Level 3 RepairVietmobile PageNessuna valutazione finora

- Acd-Gf-Phase 2Documento1 paginaAcd-Gf-Phase 2locNessuna valutazione finora

- Service Manual: SchematicsDocumento42 pagineService Manual: SchematicsKen LeeNessuna valutazione finora

- DIAGRAMA Cat c15 BiturboDocumento2 pagineDIAGRAMA Cat c15 Biturbohecazorla75% (4)

- Speedy Current Affairs eBook (हिंदी)Documento149 pagineSpeedy Current Affairs eBook (हिंदी)pankaj paswanNessuna valutazione finora

- ProductChart A2-Web PDFDocumento1 paginaProductChart A2-Web PDFAllan NallaNessuna valutazione finora

- Mx800dual Cable SchemaDocumento2 pagineMx800dual Cable SchemaAditya K SinghNessuna valutazione finora

- TTL-1 Floor: Drawing Title: Factory Name: Address: Date: Design & Drawing By: Checked By: Approved By: Page NoDocumento1 paginaTTL-1 Floor: Drawing Title: Factory Name: Address: Date: Design & Drawing By: Checked By: Approved By: Page NoMunzurulKaderNessuna valutazione finora

- 11 Corolla / Auris (Cont. Next Page) : Engine Control (1ND-TV)Documento3 pagine11 Corolla / Auris (Cont. Next Page) : Engine Control (1ND-TV)varenziaNessuna valutazione finora

- 5PK Midi A Body AopDocumento1 pagina5PK Midi A Body AopJubayer SabujNessuna valutazione finora

- Visio-7 - Cement - Mill - 1 - Local - Net - Configuration - Rev 03Documento1 paginaVisio-7 - Cement - Mill - 1 - Local - Net - Configuration - Rev 03Khan Mujtaba KhanNessuna valutazione finora

- Transformer /175W Line Safety Line: MotorDocumento1 paginaTransformer /175W Line Safety Line: Motororo plataNessuna valutazione finora

- 2SK2663Documento1 pagina2SK2663hectorsevillaNessuna valutazione finora

- ETAP Direct2D PrintingDocumento1 paginaETAP Direct2D PrintingDarshit VyasNessuna valutazione finora

- OSLD With Time GradingDocumento1 paginaOSLD With Time GradingDarshit VyasNessuna valutazione finora

- Schematics XT1962 LatamDocumento63 pagineSchematics XT1962 LatamIsaias Daniel Moreno BravoNessuna valutazione finora

- SM-M405F Tshoo 7 WWW - deviceDB.xyzDocumento30 pagineSM-M405F Tshoo 7 WWW - deviceDB.xyzmobile planetNessuna valutazione finora

- Koilwar-Bhojpur Toll Plaza TOOL BOOTH DETAILDocumento1 paginaKoilwar-Bhojpur Toll Plaza TOOL BOOTH DETAILManinder ChaudharyNessuna valutazione finora

- Historian Databases ChemaDocumento1 paginaHistorian Databases ChemaDuqueCKNessuna valutazione finora

- Cpu SH7727: Am EncDocumento1 paginaCpu SH7727: Am EncLenovo IncognitoNessuna valutazione finora

- Hanover 6500 BB-PL Lab1 Ver5Documento4 pagineHanover 6500 BB-PL Lab1 Ver5Federico RossettiNessuna valutazione finora

- ARM Cortex-A72 Block DiagramDocumento1 paginaARM Cortex-A72 Block Diagram文帅宋Nessuna valutazione finora

- 8-Schematic Diagram (Ver2.0)Documento4 pagine8-Schematic Diagram (Ver2.0)Kadër Stevïe ĽfcNessuna valutazione finora

- Cabinet Group - Inverter (Inverter Cabinet) : Traction Motor 1Documento1 paginaCabinet Group - Inverter (Inverter Cabinet) : Traction Motor 1guido_hernan_2Nessuna valutazione finora

- Schematics-3116084tablet China Procesador A33Documento8 pagineSchematics-3116084tablet China Procesador A33Luis Rodriguez100% (1)

- ARM Cortex-A76 Block DiagramDocumento1 paginaARM Cortex-A76 Block Diagram文帅宋Nessuna valutazione finora

- Marvellous Logic Building Asignment - 10Documento5 pagineMarvellous Logic Building Asignment - 10Saurabh DhokeNessuna valutazione finora

- Cue Sheet WZ 16-2-02Documento1 paginaCue Sheet WZ 16-2-02NicolasNessuna valutazione finora

- Act A3 Fujilift Safety Line 220V PDFDocumento1 paginaAct A3 Fujilift Safety Line 220V PDFGhjNessuna valutazione finora

- Ps - WP - Flashblade As Archive For Rubrik - 02Documento20 paginePs - WP - Flashblade As Archive For Rubrik - 02Wilson OliveiraNessuna valutazione finora

- Mapa de Riesgos - MinaDocumento1 paginaMapa de Riesgos - MinajavierlopezminelgNessuna valutazione finora

- Vertex XT1635-SchematicsDocumento61 pagineVertex XT1635-SchematicsYeimer LopezNessuna valutazione finora

- (Kas001043 - Inq - 2021 - 10 - 0016256) - Ewd Kick Sensor 716BDocumento1 pagina(Kas001043 - Inq - 2021 - 10 - 0016256) - Ewd Kick Sensor 716BBYU OTOVLOGNessuna valutazione finora

- Overall Earthing LayoutDocumento1 paginaOverall Earthing LayoutSOUMENNessuna valutazione finora

- TroubDocumento55 pagineTroubТолон СабыркулуулуNessuna valutazione finora

- Motor StartingDocumento1 paginaMotor StartingMoazam AliNessuna valutazione finora

- Carvin Schematic - RX1200 System Master Rev D EDocumento4 pagineCarvin Schematic - RX1200 System Master Rev D EdodNessuna valutazione finora

- Ground FloorDocumento1 paginaGround FloorHassan RazaNessuna valutazione finora

- Legends and Symbols: Ground Floor Facility Layout Second Floor Air Handling Unit LayoutDocumento1 paginaLegends and Symbols: Ground Floor Facility Layout Second Floor Air Handling Unit Layoutinno de los santosNessuna valutazione finora

- CIVIL ROCKET? CHART Civil Ki Goli (Civil Junction)Documento1 paginaCIVIL ROCKET? CHART Civil Ki Goli (Civil Junction)MR. PRANAV KUMAR67% (3)

- Mb Thoát Nước Tầng 1,2 - Tl:1/125: X1 X2 X3 X4 X5 X6 X7 X8 X9 X10 X11 X13 X12 X4' X6'Documento1 paginaMb Thoát Nước Tầng 1,2 - Tl:1/125: X1 X2 X3 X4 X5 X6 X7 X8 X9 X10 X11 X13 X12 X4' X6'Đỗ Thanh HùngNessuna valutazione finora

- Smart Water Management System IoTDocumento11 pagineSmart Water Management System IoTSuddharth AgrawalNessuna valutazione finora

- Samsung Power Board Circuit BN44-00368B-1-2-2Documento1 paginaSamsung Power Board Circuit BN44-00368B-1-2-2Jair BezerraNessuna valutazione finora

- CAN2 Power-Train (Engine Control and Pump Control) CAN2 Power-Train (Engine Control and Pump Control)Documento18 pagineCAN2 Power-Train (Engine Control and Pump Control) CAN2 Power-Train (Engine Control and Pump Control)Boran CarmonaNessuna valutazione finora

- Chaoshan Electrical PlanDocumento4 pagineChaoshan Electrical PlanMilbert CandelarioNessuna valutazione finora

- ESC OverviewDocumento3 pagineESC Overviewraytsao65Nessuna valutazione finora

- Lc200 Engine Control W DPFDocumento7 pagineLc200 Engine Control W DPFMichael Frank Vasques RenaciaNessuna valutazione finora

- Three-State Buffers: - Output LOW, HIGH, or Hi-ZDocumento30 pagineThree-State Buffers: - Output LOW, HIGH, or Hi-ZYunus TorunNessuna valutazione finora

- Dimm PC 520 Iu HBDocumento96 pagineDimm PC 520 Iu HBankitdhimancrNessuna valutazione finora

- To Move The Heat Away From The CPU: Bottom of FormDocumento5 pagineTo Move The Heat Away From The CPU: Bottom of Formdj_eqc7227Nessuna valutazione finora

- Assignment 3: 1. Given The MIPS Assembly CodeDocumento12 pagineAssignment 3: 1. Given The MIPS Assembly CodePhan TanNessuna valutazione finora

- Verifying A Low Power Design: Asif JafriDocumento10 pagineVerifying A Low Power Design: Asif JafrispaulsNessuna valutazione finora

- LCD Screen 8051Documento23 pagineLCD Screen 8051ahimpli100% (2)

- JNTU MCA - Semester I (From 2004 Batch) - MC 1.2 - Computer OrganizationDocumento3 pagineJNTU MCA - Semester I (From 2004 Batch) - MC 1.2 - Computer OrganizationpraveenmpkNessuna valutazione finora

- Clap Counter Using 8051 Microcontroller (AT89C51) : Description Circuit Diagram Code ComponentsDocumento4 pagineClap Counter Using 8051 Microcontroller (AT89C51) : Description Circuit Diagram Code ComponentsKarthik Dm60% (5)

- DLD Lab ManualDocumento60 pagineDLD Lab ManualUmesh BhadadeNessuna valutazione finora

- Welcome To The F2833x - Tutorial: Module 1: IntroductionDocumento26 pagineWelcome To The F2833x - Tutorial: Module 1: IntroductionMaria MEKLINessuna valutazione finora

- 8085 Instruction Addressing Modes ImppDocumento87 pagine8085 Instruction Addressing Modes ImppRohan VaidyaNessuna valutazione finora

- Superset Adder PaperDocumento5 pagineSuperset Adder Paperw7jh9a2Nessuna valutazione finora

- VLSI Presentation Fall 23Documento26 pagineVLSI Presentation Fall 23Pathul02Nessuna valutazione finora

- OpenWrt Project - TP-Link TL-WA901NDDocumento8 pagineOpenWrt Project - TP-Link TL-WA901NDJoao WerleyNessuna valutazione finora

- PIC16F84ADocumento88 paginePIC16F84ASantosNessuna valutazione finora

- Chap8-MOS Memory and Storage CircuitsDocumento44 pagineChap8-MOS Memory and Storage CircuitsMạnh Cường TrầnNessuna valutazione finora

- Cypress DOS Driver User's GuideDocumento5 pagineCypress DOS Driver User's Guidesathi86Nessuna valutazione finora

- Timing Analysis: Path GroupDocumento18 pagineTiming Analysis: Path GroupkocchopNessuna valutazione finora

- Learning-Guide-Elex 75 Ay 2022-2023Documento5 pagineLearning-Guide-Elex 75 Ay 2022-2023Welma SambajonNessuna valutazione finora

- System Unit-The Main Part of A Microcomputer, Sometimes Called The Chassis. ItDocumento15 pagineSystem Unit-The Main Part of A Microcomputer, Sometimes Called The Chassis. ItJay Ann GonzagaNessuna valutazione finora

- DDI0406B Arm Architecture Reference Manual Errata Markup 8 0Documento2.158 pagineDDI0406B Arm Architecture Reference Manual Errata Markup 8 0Sarojini GovindanNessuna valutazione finora

- Vit Ece 5th Year SyllabusDocumento16 pagineVit Ece 5th Year Syllabuspranavateja12399Nessuna valutazione finora

- Notebook Computer Notebook Computer W241BU/W241BUQ/W240BU/W245BUQ/W248BUQ/ W241BU/W241BUQ/W240BU/W245BUQ/W248BUQ/ W249BUQ W249BUQ Service ManualDocumento5 pagineNotebook Computer Notebook Computer W241BU/W241BUQ/W240BU/W245BUQ/W248BUQ/ W241BU/W241BUQ/W240BU/W245BUQ/W248BUQ/ W249BUQ W249BUQ Service ManualTiago da Silva PereiraNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitectureShiv Kumar100% (1)

- Spider Rtu DocumentDocumento3 pagineSpider Rtu DocumentNeelakandan MasilamaniNessuna valutazione finora

- Ad 114Documento4 pagineAd 114Fadzilah NijiNessuna valutazione finora

- FPGADocumento16 pagineFPGAdayat_ridersNessuna valutazione finora

- Design Analysis of NAND Gate Using Cascode-Voltage Switch LogicDocumento4 pagineDesign Analysis of NAND Gate Using Cascode-Voltage Switch LogicNeha Prashant VermaNessuna valutazione finora

- Bascom AvrxmegaDocumento49 pagineBascom AvrxmegaSalome DaquilemaNessuna valutazione finora

- Amx Axcent3 ManualDocumento34 pagineAmx Axcent3 ManualNoah WestonNessuna valutazione finora