Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Cs Notes

Caricato da

Arti DwivediTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Cs Notes

Caricato da

Arti DwivediCopyright:

Formati disponibili

1

UNIT-V

Content

Memory & Programmable Logic Devices: Digital Logic Families: DTL, DCTL,

TTL, ECL & CMOS etc., Fan Out, Fan in, Noise Margin; RAM, ROM, PLA,

PAL; Circuits of Logic Families, Interfacing of Digital Logic Families, Circuit

Implementation using ROM, PLA and PAL; CPLD and FPGA.

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

2

Q-1 What is Fan-Out?

Ans: Fan out specifies the number of standard loads that the output of the gate can drive without

impairment of its normal operation

Q2- What is Noise Margin in digital circuits?

Ans:It is the maximum noise voltage added to an input signal of a digital circuit that does not cause an

undesirable change in the circuit output. It is expressed in volts

Q-3: Explain Logic Family classification.

Ans: Logic families are sets of chips that may implement different logical functions but use the

same type of transistors and voltage levels for logical levels and for the power supplies. These

families vary by speed, power consumption, cost, voltage & current levels. The most widely used

families are:

DL (Diode- logic)

DTL (Diode-transistor logic)

RTL (Resistor-transistor logic)

TTL (Transistor -transistor logic)

ECL (Emitter-coupled logic)

MOS (Metal-oxide semiconductor)

CMOS (Complementary Metal-oxide semiconductor)

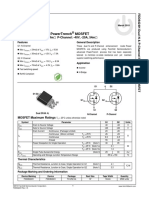

Q-4 Write TTL Parameters

Ans: based on bipolar transistors one of the most widely used families of small- and medium-

scale devices – rarely used for VLSI

typically operated from a 5V supply

typical noise immunity about 1 – 1.6 V

many forms, some optimised for speed, power, etc.

High-speed versions comparable to CMOS (~ 1.5 ns)

low-power versions down to about 1 mW/gate

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

3

Q-5 What is PROM?

Ans: Read Only Memory (ROM) is a memory device, which stores the binary information permanently.

That means, we can’t change that stored information by any means later. If the ROM has programmable

feature, then it is called as Programmable ROM (PROM). The user has the flexibility to program the

binary information electrically once by using PROM programmer.

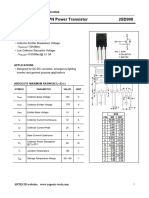

Q-6 What is PAL ( Programmable Array Logic )

Ans:PAL is a programmable logic device that has Programmable AND array & fixed OR array. The

advantage of PAL is that we can generate only the required product terms of Boolean function instead

of generating all the min terms by using programmable AND gates. The block diagram of PAL is shown in

the following figure.

Q-7 What is PLA (Programmable Logic Array)

Ans: PLA is a programmable logic device that has both Programmable AND array & Programmable OR

array. Hence, it is the most flexible PLD. The block diagram of PLA is shown in the following figure.

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

4

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

5

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

6

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

7

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

8

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

9

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

10

10

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

11

11

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

12

12

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

13

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

14

13

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

15

14

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

16

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

17

15

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

18

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

19

16

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

20

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

21

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

22

17

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

23

18

19

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

24

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

25

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

26

20

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

27

21

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

28

22

23

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

29

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

30

24

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

31

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

32

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

33

25

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

34

26

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

35

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

36

Digital Logic Design(REC-301) By: Navneet Pal (Assistant Professor)

Potrebbero piacerti anche

- Lect 01Documento40 pagineLect 01Erva ŞengülNessuna valutazione finora

- Eech TNGDocumento870 pagineEech TNGEzlan Harith0% (1)

- Sub1 1 Theory IC Design Flow NguyenHungQuan 201309Documento52 pagineSub1 1 Theory IC Design Flow NguyenHungQuan 201309Nguyễn Văn HảoNessuna valutazione finora

- Osou Pgdca Syllabus 18Documento14 pagineOsou Pgdca Syllabus 18S KaurNessuna valutazione finora

- Cs 341 Lecture1Documento11 pagineCs 341 Lecture1luckyNessuna valutazione finora

- DCA Syllabus 2018 OnwardsDocumento8 pagineDCA Syllabus 2018 OnwardsAkash BhoiNessuna valutazione finora

- Computer-Aided Design TechniquesDa EverandComputer-Aided Design TechniquesE. WolfendaleNessuna valutazione finora

- Galgotias College Digital Signal Processing Course FileDocumento12 pagineGalgotias College Digital Signal Processing Course FileJapjeet KaurNessuna valutazione finora

- ECE419 Digital Vlsi Design 16937::tapsi Singh 3.0 1.0 0.0 4.0 Courses With Numerical and Conceptual FocusDocumento8 pagineECE419 Digital Vlsi Design 16937::tapsi Singh 3.0 1.0 0.0 4.0 Courses With Numerical and Conceptual FocusanakshaNessuna valutazione finora

- Lec8 Programming in R FunctionsDocumento11 pagineLec8 Programming in R FunctionsShashank GautamNessuna valutazione finora

- Software Architecture and UMLDocumento6 pagineSoftware Architecture and UMLmahaNessuna valutazione finora

- Dec3033 Computer Architecture and Organization - SDocumento7 pagineDec3033 Computer Architecture and Organization - Skshika meganathanNessuna valutazione finora

- University Institute of Information Technology: Course ProfileDocumento3 pagineUniversity Institute of Information Technology: Course ProfileAyesha banoNessuna valutazione finora

- On Python For Mechanical Engineers Internship: Carried Out at Decibels Lab PVT LTDDocumento15 pagineOn Python For Mechanical Engineers Internship: Carried Out at Decibels Lab PVT LTDUmesh KashiNessuna valutazione finora

- AKTU University Syllabus Mapping E-ResourcesDocumento6 pagineAKTU University Syllabus Mapping E-ResourcesNaman SharmaNessuna valutazione finora

- CS DS2Documento37 pagineCS DS2Srinivas KanakalaNessuna valutazione finora

- DSP 5Documento5 pagineDSP 5kashyap.piyush2003Nessuna valutazione finora

- Digital System Design Course OverviewDocumento5 pagineDigital System Design Course OverviewKama AzuraNessuna valutazione finora

- ASIC-System On Chip-VLSI Design Backend (Physical Design) Interview Questions and AnswersDocumento7 pagineASIC-System On Chip-VLSI Design Backend (Physical Design) Interview Questions and AnswersRohith RajNessuna valutazione finora

- Certificate: Reliability of Software Analysis in Structural Engineering (RCC)Documento9 pagineCertificate: Reliability of Software Analysis in Structural Engineering (RCC)Nikhil KumbharNessuna valutazione finora

- Astronomical Data Analysis Using Python: Yogesh WadadekarDocumento35 pagineAstronomical Data Analysis Using Python: Yogesh WadadekarRaHuL MuSaLeNessuna valutazione finora

- MNNIT Allahabad B.Tech (Information Technology) SyllabusDocumento57 pagineMNNIT Allahabad B.Tech (Information Technology) SyllabusGod FatherNessuna valutazione finora

- PR ZXVDocumento8 paginePR ZXVBSSudaniNessuna valutazione finora

- FPL_20_RISCV_NTTDocumento8 pagineFPL_20_RISCV_NTTahmedosama8272Nessuna valutazione finora

- EE-307 Digital System Design: Lecture # 02Documento35 pagineEE-307 Digital System Design: Lecture # 02Talha KhalidNessuna valutazione finora

- 11-Speech Encryption and DecryptionDocumento13 pagine11-Speech Encryption and Decryptionapi-19799369Nessuna valutazione finora

- Visvesvaraya Technological University BELGAUM-590014: Walking RobotDocumento58 pagineVisvesvaraya Technological University BELGAUM-590014: Walking Robot1DT19CS119 Pruthvika ReddyNessuna valutazione finora

- 00031523-BLADES An Artificial Intelligence Approach ToDocumento13 pagine00031523-BLADES An Artificial Intelligence Approach ToPratibha V. HegdeNessuna valutazione finora

- ECE 3561 Advanced Digital Design: Department of Electrical and Computer Engineering The Ohio State UniversityDocumento20 pagineECE 3561 Advanced Digital Design: Department of Electrical and Computer Engineering The Ohio State Universitypaku deyNessuna valutazione finora

- A Very Compact FPGA Implementation of LED and PHOTONDocumento19 pagineA Very Compact FPGA Implementation of LED and PHOTONabdelli aliNessuna valutazione finora

- VNR VJIT Course Catalogue for III Semester CSE & ITDocumento37 pagineVNR VJIT Course Catalogue for III Semester CSE & ITSumanth MerugaNessuna valutazione finora

- Introduction-EE3491Documento8 pagineIntroduction-EE3491JR PhoenixNessuna valutazione finora

- EE-307 Fpga Based System Design: Lecture # 02Documento35 pagineEE-307 Fpga Based System Design: Lecture # 02Muhammad AnasNessuna valutazione finora

- VNR Vignana Jyothi Institute of Engineering & Technology Hyderabad B.Tech. Ii Year (Computer Science and Business Systems) Iii Semester R19Documento40 pagineVNR Vignana Jyothi Institute of Engineering & Technology Hyderabad B.Tech. Ii Year (Computer Science and Business Systems) Iii Semester R19Raghu VadlamaniNessuna valutazione finora

- Car Park ReportDocumento64 pagineCar Park ReportLeelavathi ReddyNessuna valutazione finora

- DPSD Unit 3Documento175 pagineDPSD Unit 3Pragna SidhireddyNessuna valutazione finora

- Course Outline - Digital Logic DesignDocumento10 pagineCourse Outline - Digital Logic DesignTauqir HassanNessuna valutazione finora

- Execute A Solution Taking Into Consideration Design Requirements and Pertinent Contextual Elements. (Block Diagram/Flow Chart/circuit Diagram)Documento4 pagineExecute A Solution Taking Into Consideration Design Requirements and Pertinent Contextual Elements. (Block Diagram/Flow Chart/circuit Diagram)TRUE LOVERSNessuna valutazione finora

- Old M.tech BDA CurriculumDocumento32 pagineOld M.tech BDA Curriculumvasudevn1Nessuna valutazione finora

- cs224r Practical Deep RLDocumento77 paginecs224r Practical Deep RLmichael AmponsahNessuna valutazione finora

- Chapter1-Software Engineering & Data ScienceDocumento30 pagineChapter1-Software Engineering & Data ScienceKomi David ABOTSITSENessuna valutazione finora

- Proj No. Title: A/P Chong Yong Kim A/P Gan Woon SengDocumento5 pagineProj No. Title: A/P Chong Yong Kim A/P Gan Woon SengTần LongNessuna valutazione finora

- NATIONAL INSTITUTE OF TECHNOLOGY, HAMIRPUR (HP)-177005 Department of Computer Science & Engineering Modified Teaching Scheme (B.Tech. in CSE) Effective From July-2010Documento61 pagineNATIONAL INSTITUTE OF TECHNOLOGY, HAMIRPUR (HP)-177005 Department of Computer Science & Engineering Modified Teaching Scheme (B.Tech. in CSE) Effective From July-2010ankesh45Nessuna valutazione finora

- Big Data - SRM University PDFDocumento29 pagineBig Data - SRM University PDFSarit ChakrabortyNessuna valutazione finora

- Designing A G2 Structure Using Python With Graphical User InterfaceDocumento9 pagineDesigning A G2 Structure Using Python With Graphical User InterfaceRajani TogarsiNessuna valutazione finora

- 2011-LogarithmicMultiplierinHardwareImplementationofNeuralNetworksDocumento12 pagine2011-LogarithmicMultiplierinHardwareImplementationofNeuralNetworksSohan SaiNessuna valutazione finora

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocumento6 pagineCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNessuna valutazione finora

- Siddaganga Institute of TechnologyDocumento4 pagineSiddaganga Institute of TechnologyAbhishek M ShivalingaiahNessuna valutazione finora

- Week1 - Introduction To Machine Learning and ToolkitDocumento102 pagineWeek1 - Introduction To Machine Learning and ToolkitVivek ThotaNessuna valutazione finora

- Introduction To R ProgrammingDocumento19 pagineIntroduction To R ProgrammingDipyaman ChoudhuryNessuna valutazione finora

- 3distribution DesignDocumento65 pagine3distribution Designsriram sharathNessuna valutazione finora

- R19 Cse (Iot)Documento368 pagineR19 Cse (Iot)pushpa lathaNessuna valutazione finora

- Prof. Dr. P.Ramasubramanian Annai Vailankanni College of EngineeringDocumento139 pagineProf. Dr. P.Ramasubramanian Annai Vailankanni College of EngineeringTawseef ShaikhNessuna valutazione finora

- Resource Roadmap, HangukquantDocumento9 pagineResource Roadmap, HangukquantTony KhánhNessuna valutazione finora

- Routine Spring 2022 BSE VI 1Documento1 paginaRoutine Spring 2022 BSE VI 1Nabin TimsinaNessuna valutazione finora

- Automated Design of Steel Trusses SoftwareDocumento12 pagineAutomated Design of Steel Trusses SoftwareNasriyah SolaimanNessuna valutazione finora

- ADE (Unit 4) (PLD)Documento42 pagineADE (Unit 4) (PLD)Pranav dawareNessuna valutazione finora

- DESIGN ALGORITHMS TO SOLVE COMMON PROBLEMS: Mastering Algorithm Design for Practical Solutions (2024 Guide)Da EverandDESIGN ALGORITHMS TO SOLVE COMMON PROBLEMS: Mastering Algorithm Design for Practical Solutions (2024 Guide)Nessuna valutazione finora

- Running Head: "R Studio": Ranendra Lakha University of Cumberlands Dr. Cynthia Mcmahon Analyzing and Visualizing DataDocumento10 pagineRunning Head: "R Studio": Ranendra Lakha University of Cumberlands Dr. Cynthia Mcmahon Analyzing and Visualizing DataArti DwivediNessuna valutazione finora

- UNIT-1: - Thed Haiman - Murphy-Et-Al Roles of CommunicationDocumento11 pagineUNIT-1: - Thed Haiman - Murphy-Et-Al Roles of CommunicationShashwat TripathiNessuna valutazione finora

- Akhilesh-Green Computing - ResponseDocumento1 paginaAkhilesh-Green Computing - ResponseArti DwivediNessuna valutazione finora

- Susmita Prajapati University of Cumberlands Dr. Cynthia Mcmahon Analyzing and Visualizing DataDocumento10 pagineSusmita Prajapati University of Cumberlands Dr. Cynthia Mcmahon Analyzing and Visualizing DataArti DwivediNessuna valutazione finora

- CNS Unit 4Documento11 pagineCNS Unit 4Arti DwivediNessuna valutazione finora

- Unit-13 AssignmentDocumento4 pagineUnit-13 AssignmentArti DwivediNessuna valutazione finora

- Nikhil wk3Documento2 pagineNikhil wk3Arti DwivediNessuna valutazione finora

- ADocumento3 pagineAArti DwivediNessuna valutazione finora

- Quiz TaranveerDocumento6 pagineQuiz TaranveerArti DwivediNessuna valutazione finora

- Divya - WK 3 - Research - Analyzing & Visualizing DataDocumento7 pagineDivya - WK 3 - Research - Analyzing & Visualizing DataArti DwivediNessuna valutazione finora

- Market Equilibrium, Competitive Firms, and Industry AnalysisDocumento3 pagineMarket Equilibrium, Competitive Firms, and Industry AnalysisArti DwivediNessuna valutazione finora

- Business EnvironmentDocumento41 pagineBusiness EnvironmentArti DwivediNessuna valutazione finora

- Analyzing Data Collection TechniquesDocumento7 pagineAnalyzing Data Collection TechniquesArti DwivediNessuna valutazione finora

- Running Head: "Covid 19" 1Documento4 pagineRunning Head: "Covid 19" 1Arti DwivediNessuna valutazione finora

- Wireless & Mobile Communication (EEC-801) Unit-IDocumento11 pagineWireless & Mobile Communication (EEC-801) Unit-IArti DwivediNessuna valutazione finora

- IPSec and IP security protocols explainedDocumento18 pagineIPSec and IP security protocols explainedArti DwivediNessuna valutazione finora

- Laser AktuDocumento17 pagineLaser AktuMohitNessuna valutazione finora

- Sales Distribution ManagementDocumento58 pagineSales Distribution ManagementArti DwivediNessuna valutazione finora

- AI NotesDocumento10 pagineAI NotesArti DwivediNessuna valutazione finora

- Cybersecurity Fundamentals ExplainedDocumento1 paginaCybersecurity Fundamentals ExplainedArti DwivediNessuna valutazione finora

- Unit - 5: Anuj Khanna Assistant Profesor (Kiot, Kanpur)Documento23 pagineUnit - 5: Anuj Khanna Assistant Profesor (Kiot, Kanpur)Arti DwivediNessuna valutazione finora

- CCP Unit 3Documento28 pagineCCP Unit 3Arti DwivediNessuna valutazione finora

- CCP Unit 5Documento8 pagineCCP Unit 5Arti DwivediNessuna valutazione finora

- Basic Electrical EngineeringDocumento69 pagineBasic Electrical EngineeringArti DwivediNessuna valutazione finora

- Chap 5Documento24 pagineChap 5api-37022560% (1)

- Diagram PC3.3 For QSK60-P8Documento20 pagineDiagram PC3.3 For QSK60-P8Trần Quang ToánNessuna valutazione finora

- Expansor EP-06Documento5 pagineExpansor EP-06cronica.motaNessuna valutazione finora

- STEPPER MOTOR DEFINITIONDocumento19 pagineSTEPPER MOTOR DEFINITIONIan Bagunas100% (2)

- Technical Specification of Nyy Flexible 1x10 RM 0.6/1.0 (1.2) KV CableDocumento1 paginaTechnical Specification of Nyy Flexible 1x10 RM 0.6/1.0 (1.2) KV CableRasel AhmedNessuna valutazione finora

- Joysticks: We Build It So You Can Control ItDocumento5 pagineJoysticks: We Build It So You Can Control ItJohnNessuna valutazione finora

- Low Forward Voltage Switching Diode SpecificationDocumento4 pagineLow Forward Voltage Switching Diode Specificationsamsularief03100% (2)

- DC Shunt Motor Speed and Torque CharacteristicsDocumento9 pagineDC Shunt Motor Speed and Torque CharacteristicsEric CalejaNessuna valutazione finora

- Tmdrive: Ac/Dc Drive SeriesDocumento8 pagineTmdrive: Ac/Dc Drive SeriesEliasNessuna valutazione finora

- Spare Material 400kvDocumento12 pagineSpare Material 400kvsuleman247Nessuna valutazione finora

- Experiment # 05: Parallel Operation of Two Single Phase TransformersDocumento4 pagineExperiment # 05: Parallel Operation of Two Single Phase TransformersNasir Ali / Lab Engineer, Electrical Engineering DepartmentNessuna valutazione finora

- Charging Failures & Battery MaintenanceDocumento1 paginaCharging Failures & Battery MaintenanceJesus Amaya ArizaNessuna valutazione finora

- Ume Ingepac Ef LD EngDocumento717 pagineUme Ingepac Ef LD EngSittiporn KulsapsakNessuna valutazione finora

- GP-3300/3400 Series Installation Guide: CautionDocumento16 pagineGP-3300/3400 Series Installation Guide: Cautionng4c4anh4nguy4n-1Nessuna valutazione finora

- Arduino Temperature Fan Based Speed ControlDocumento3 pagineArduino Temperature Fan Based Speed ControlImma TzNessuna valutazione finora

- SPWM V/HZ InverterDocumento51 pagineSPWM V/HZ InverterLabi BajracharyaNessuna valutazione finora

- FDD8424H-92711 - Transistor de Efeito de CampoDocumento12 pagineFDD8424H-92711 - Transistor de Efeito de CampoTiago LeonhardtNessuna valutazione finora

- Pass Laboratories: Page 1 of 6Documento6 paginePass Laboratories: Page 1 of 6aoctaNessuna valutazione finora

- DatasheetDocumento4 pagineDatasheetcendrezNessuna valutazione finora

- DU Series MCCB CatalogueDocumento16 pagineDU Series MCCB CatalogueUjwal MalhotraNessuna valutazione finora

- CPU-XL VariSpark IOM 12-13Documento97 pagineCPU-XL VariSpark IOM 12-13SaasiNessuna valutazione finora

- The Case of Failed TransformerDocumento84 pagineThe Case of Failed Transformerlbk50100% (1)

- Efficient Flyback Driver for Cylindrical Rectified TV FlybacksDocumento3 pagineEfficient Flyback Driver for Cylindrical Rectified TV FlybacksArnab AcharyaNessuna valutazione finora

- MS357Documento8 pagineMS357Maiquel HorstNessuna valutazione finora

- Conector EuromoldDocumento2 pagineConector EuromoldElio ByrneNessuna valutazione finora

- Single Line DiagramDocumento15 pagineSingle Line DiagramKhang TrangNessuna valutazione finora

- GEYA ELECTRICAL CO.,LTD Instruction Manual for Asymmetric Cycler Time Relay GRT8-SDocumento2 pagineGEYA ELECTRICAL CO.,LTD Instruction Manual for Asymmetric Cycler Time Relay GRT8-SRamius HamdaniNessuna valutazione finora

- CTO 550 115 Current TransformerDocumento3 pagineCTO 550 115 Current Transformersagar ramaniNessuna valutazione finora

- 2 SD 998Documento2 pagine2 SD 998Felipe CastroNessuna valutazione finora

- Receptaculo Con Tapa y Caja Mod. ARE-6424Documento7 pagineReceptaculo Con Tapa y Caja Mod. ARE-6424Rolando GilNessuna valutazione finora

- EDC Objective QuestionsDocumento8 pagineEDC Objective QuestionsBhanu KodaliNessuna valutazione finora