Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

EPC2036 - Enhancement Mode Power Transistor: V, 100 V R, 73 M I, 1.7 A

Caricato da

LuisTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

EPC2036 - Enhancement Mode Power Transistor: V, 100 V R, 73 M I, 1.7 A

Caricato da

LuisCopyright:

Formati disponibili

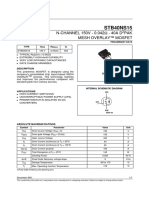

eGaN® FET DATASHEET EPC2036

EPC2036 – Enhancement Mode Power Transistor

VDSS , 100 V D

RDS(on) , 73 mΩ G EFFICIENT POWER CONVERSION

ID , 1.7 A S

HAL

Gallium Nitride is grown on Silicon Wafers and processed using standard CMOS equipment

leveraging the infrastructure that has been developed over the last 60 years. GaN’s exceptionally

high electron mobility and low temperature coefficient allows very low RDS(on), while its lateral

device structure and majority carrier diode provide exceptionally low QG and zero QRR. The end

result is a device that can handle tasks where very high switching frequency, and low on-time are

beneficial as well as those where on-state losses dominate. EPC2036 eGaN® FETs are supplied only in

passivated die form with solder bumps

Die Size: 0.9 mm x 0.9 mm

Maximum Ratings

Applications

Drain-to-Source Voltage (Continuous) 100

VDS V • High Speed DC-DC conversion

Drain-to-Source Voltage (up to 10,000 5ms pulses at 150˚C) 120 • Wireless Power Transfer

• High Frequency Hard-Switching and

Continuous (TA = 25˚C, R θJA= 340˚C/W) 1.7 Soft-Switching Circuits

ID A

Pulsed (25˚C, TPULSE = 300 µs) 18 • LiDAR/Pulsed Power Applications

• Class-D Audio

Gate-to-Source Voltage 6

VGS V Benefits

Gate-to-Source Voltage -4 • Ultra High Efficiency

TJ Operating Temperature -40 to 150

• Ultra Low RDS(on)

˚C • Ultra low QG

TSTG Storage Temperature -40 to 150 • Ultra small footprint

www.epc-co.com/epc/Products/eGaNFETs/EPC2036.aspx

Static Characteristics (TJ= 25˚C unless otherwise stated)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

BVDSS Drain-to-Source Voltage VGS = 0 V, ID = 300 µA 100 V

IDSS Drain Source Leakage VDS = 80 V, VGS = 0 V 20 250 µA

Gate-to-Source Forward Leakage VGS = 5 V 0.1 0.9 mA

IGSS

Gate-to-Source Reverse Leakage VGS = -4 V 20 250 µA

VGS(TH) Gate Threshold Voltage VDS = VGS, ID = 0.6 mA 0.8 1.4 2.5 V

RDS(on) Drain-Source On Resistance VGS = 5 V, ID = 1 A 62 73 mΩ

VSD Source-Drain Forward Voltage IS = 0.5 A, VGS = 0 V 1.9 V

All measurements were done with substrate shorted to source.

Thermal Characteristics

TYP UNIT

RθJC Thermal Resistance, Junction to Case 6.5 ˚C/W

RθJB Thermal Resistance, Junction to Board 65 ˚C/W

RθJA Thermal Resistance, Junction to Ambient (Note 1) 100 ˚C/W

Note 1: RθJA is determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board.

See http://epc-co.com/epc/documents/product-training/Appnote_Thermal_Performance_of_eGaN_FETs.pdf for details.

EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2018 | | 1

eGaN® FET DATASHEET EPC2036

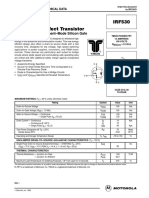

Dynamic Characteristics (TJ= 25˚C unless otherwise stated)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

CISS Input Capacitance 75 90

COSS Output Capacitance VDS = 50 V, VGS = 0 V 50 75 pF

CRSS Reverse Transfer Capacitance 0.7 1.1

RG Gate Resistance 0.6 Ω

QG Total Gate Charge VDS = 50 V, VGS = 5 V, ID = 1 A 700 910

QGS Gate-to-Source Charge 170

QGD Gate-to-Drain Charge VDS = 50 V, ID = 1 A 140 240

pC

QG(TH) Gate Charge at Threshold 120

QOSS Output Charge VDS = 50 V, VGS = 0 V 3900 5900

QRR Source-Drain Recovery Charge 0

All measurements were done with substrate shorted to source.

Figure 1: Typical Output Characteristics at 25°C Figure 2: Transfer Characteristics

18 18

15 ID – Drain Current (A) 15

ID – Drain Current (A)

12 12

25˚C

9 9 125˚C

VGS = 5 V VDS = 3 V

VGS = 4 V

6 6

VGS = 3 V

VGS = 2 V

3 3

0 0

0 0.5 1.0 1.5 2.0 2.5 3.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

VDS – Drain-to-Source Voltage (V) VGS – Gate-to-Source Voltage (V)

Figure 3: RDS(on) vs. VGS for Various Drain Currents Figure 4: RDS(on) vs. VGS for Various Temperatures

250 250

ID = 0.5 A

RDS(on) – Drain-to-Source Resistance (mΩ)

RDS(on) – Drain-to-Source Resistance (mΩ)

ID = 1.0 A 25˚C

200 200

ID = 1.5 A 125˚C

ID = 2.0 A

ID = 1 A

150 150

100 100

50 50

0 0

2.0 2.5 3.0 3.5 4.0 4.5 5.0 2.0 2.5 3.0 3.5 4.0 4.5 5.0

VGS – Gate-to-Source Voltage (V) VGS – Gate-to-Source Voltage (V)

EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2018 | | 2

eGaN® FET DATASHEET EPC2036

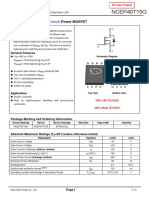

Figure 5a: Capacitance (Linear Scale) Figure 5b: Capacitance (Log Scale)

140

100

120 COSS = CGD + CSD

CISS = CGD + CGS

100 CRSS = CGD

Capacitance (pF)

Capacitance (pF)

10

80

COSS = CGD + CSD

CISS = CGD + CGS

60 CRSS = CGD

40 1

20

0 0.1

0 20 40 60 80 100 0 20 40 60 80 100

VDS – Drain-to-Source Voltage (V) VDS – Drain-to-Source Voltage (V)

Figure 6: Gate Charge Figure 7: Reverse Drain-Source Characteristics

5 18

ID = 1 A 15

4 25˚C

VDS = 50 V

VGS – Gate-to-Source Voltage (V)

ISD – Source-to-Drain Current (A)

125˚C

12

3

9

2

6

1

3

0 0

0 0.2 0.4 0.6 0.8 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

QG – Gate Charge (nC) VSD – Source-to-Drain Voltage (V)

Figure 8: Normalized On Resistance vs. Temperature Figure 9: Normalized Threshold Voltage vs. Temperature

2.0 1.40

ID = 1 A 1.30 ID = 0.6 mA

Normalized On-State Resistance RDS(on)

1.8 VGS = 5 V

Normalized Threshold Voltage

1.20

1.6

1.10

1.4 1.00

0.90

1.2

0.80

1.0

0.70

0.8 0.60

0 25 50 75 100 125 150 0 25 50 75 100 125 150

TJ – Junction Temperature (°C) TJ – Junction Temperature (°C)

All measurements were done with substrate shortened to source.

EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2018 | | 3

eGaN® FET DATASHEET EPC2036

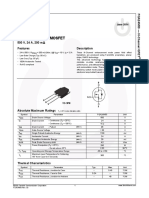

Figure 10: Gate Leakage Current

3.0

2.5

25˚C

125˚C

IG – Gate Current (mA)

2.0

1.5

1.0

0.5

0

0 1 2 3 4 5 6

VGS – Gate-to-Source Voltage (V)

Figure 11: Transient Thermal Response Curves

Junction-to-Board

1 Duty Cycle:

ZθJB, Normalized Thermal Impedance

0.5

0.1

0.1

0.05

0.02

PDM

0.01

0.01

t1

t2

0.001

Notes:

Single Pulse Duty Factor: D = t1/t2

Peak TJ = PDM x ZθJB x RθJB + TB

0.0001

10-5 10-4 10-3 10-2 10-1 1 10+1

tp, Rectangular Pulse Duration, seconds

Junction-to-Case

1 Duty Cycle:

ZθJB, Normalized Thermal Impedance

0.5

0.2

0.1

0.1

0.05

0.02

PDM

0.01

0.01

t1

t2

0.001

Single Pulse Notes:

Duty Factor: D = t1/t2

Peak TJ = PDM x ZθJC x RθJC + TC

0.0001

10-6 10-5 10-4 10-3 10-2 10-1 1

tp, Rectangular Pulse Duration, seconds

EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2018 | | 4

eGaN® FET DATASHEET EPC2036

Figure 12: Safe Operating Area

10

I D – Drain Current (A)

Limited by RDS(on)

Pulse Width

1

100 ms100 ms

10 ms10 ms

1 ms

100 µs1 ms

100 µs

0.1

0.1 1 10 100

VDS - Drain-Source Voltage (V)

TJ = Max Rated, TC = +25°C, Single Pulse

TAPE AND REEL CONFIGURATION

4mm pitch, 8mm wide tape on 7”reel Loaded Tape Feed Direction

d e f g

7” reel Die

b orientation

YYY dot

c AB Gate

a solder bar is

under this

corner

Die is placed into pocket

solder bar side down

EPC2036 (note 1) (face side down)

Dimension (mm) target min max

a 8.00 7.90 8.30

b 1.75 1.65 1.85

c (see note) 3.50 3.45 3.55

d 4.00 3.90 4.10

e 4.00 3.90 4.10

Note 1: MSL 1 (moisture sensitivity level 1) classified according to IPC/JEDEC industry standard.

f (see note) 2.00 1.95 2.05

Note 2: Pocket position is relative to the sprocket hole measured as true position of the pocket,

g 1.5 1.5 1.6 not the pocket hole.

DIE MARKINGS

AB Laser Markings

Die orientation dot Part

YYY Number Part # Lot_Date Code

Gate Pad bump is Marking Line 1 Marking line 2

under this corner EPC2036 AB YYY

EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2018 | | 5

eGaN® FET DATASHEET EPC2036

A

DIE OUTLINE DIM MIN Nominal MAX

Solder Bump View g

A 870 900 930

B 870 900 930

2 4 c 450 450 450

d 450 450 450

e 210 225 240

d

Pads 1 is Gate; f 210 225 240

Pad 3 is Drain; g 187 208 229

Pads 2, 4 are Source

1 3

e c

f

Side View

(625)

815 Max

165+/- 17

SEATING PLANE

RECOMMENDED 900 The land pattern is solder mask defined

LAND PATTERN Solder mask is 10 μm smaller per side than bump

(measurements in µm)

Pads 1 is Gate;

1 3

Pad 3 is Drain;

X4 Pads 2, 4 are Source

900

200 +20 / - 10 (*)

450

242

2 4

225

225 450

* minimum 190

RECOMMENDED 900 Recommended stencil should be 4mil (100 µm) thick, must

STENCIL DRAWING 250 be laser cut, openings per drawing.

(measurements in µm)

0

Intended for use with SAC305 Type 4 solder, reference 88.5%

R6

metals content.

900

450

Additional assembly resources available at

http://epc-co.com/epc/DesignSupport/AssemblyBasics.aspx

225

225 450

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein to

improve reliability, function or design. EPC does not assume any liability arising out of the application or use of any product or circuit Information subject to change

described herein; neither does it convey any license under its patent rights, nor the rights of others. without notice.

eGaN® is a registered trademark of Efficient Power Conversion Corporation. Revised May, 2018

EPC Patent Listing: epc-co.com/epc/AboutEPC/Patents.aspx

EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2018 | | 6

Potrebbero piacerti anche

- EPC2035 - Enhancement Mode Power Transistor: V, 60 V R, 45 M I, 1.7 ADocumento6 pagineEPC2035 - Enhancement Mode Power Transistor: V, 60 V R, 45 M I, 1.7 AEdwin GualavisiNessuna valutazione finora

- EPC2020 Datasheet PDFDocumento6 pagineEPC2020 Datasheet PDFblackslash82Nessuna valutazione finora

- EPC2020 - Enhancement Mode Power Transistor: V, 60 V R, 2.2 mΩ I, 90 ADocumento6 pagineEPC2020 - Enhancement Mode Power Transistor: V, 60 V R, 2.2 mΩ I, 90 Ablackslash82Nessuna valutazione finora

- EPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 ADocumento6 pagineEPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 AЕвгений ИвановNessuna valutazione finora

- EPC2001 DatasheetDocumento6 pagineEPC2001 Datasheetrudra_1Nessuna valutazione finora

- EPC2020 - Enhancement Mode Power Transistor: V, 60 V R, 2.2 mΩ I, 90 ADocumento6 pagineEPC2020 - Enhancement Mode Power Transistor: V, 60 V R, 2.2 mΩ I, 90 AEdwin GualavisiNessuna valutazione finora

- Infineon IRFP4229 DataSheet v01 - 01 ENDocumento9 pagineInfineon IRFP4229 DataSheet v01 - 01 ENRoni Div MasterphpNessuna valutazione finora

- EPC2050 - Enhancement-Mode Power Transistor Preliminary Specification SheetDocumento8 pagineEPC2050 - Enhancement-Mode Power Transistor Preliminary Specification SheetЕвгений ИвановNessuna valutazione finora

- Advanced Power Electronics Corp.: N-Channel Enhancement-Mode Power MOSFETDocumento6 pagineAdvanced Power Electronics Corp.: N-Channel Enhancement-Mode Power MOSFETruup2010 AlexNessuna valutazione finora

- MTP60N06Documento8 pagineMTP60N06Pablo AllosiaNessuna valutazione finora

- 28N50F FairchildSemiconductorDocumento8 pagine28N50F FairchildSemiconductorgabosakrNessuna valutazione finora

- gs66516b Ds Rev 211025Documento16 paginegs66516b Ds Rev 211025Yuri AdmiNessuna valutazione finora

- Datasheet 3Documento8 pagineDatasheet 3RAMESH JUNJUNessuna valutazione finora

- Transitor de CompuDocumento7 pagineTransitor de CompuWilmenNessuna valutazione finora

- Irfp4227pbf PDFDocumento8 pagineIrfp4227pbf PDFTyron DsouzaNessuna valutazione finora

- Irfp4232Pbf: PDP MosfetDocumento9 pagineIrfp4232Pbf: PDP MosfetLuiz Clemente PimentaNessuna valutazione finora

- Irg4Ph50Ud: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery Diode Ultrafast Copack IgbtDocumento10 pagineIrg4Ph50Ud: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery Diode Ultrafast Copack IgbtAnonymous 7lirmoNessuna valutazione finora

- Infineon IRL3705N DS v01 - 02 ENDocumento9 pagineInfineon IRL3705N DS v01 - 02 ENFrancisco Mendoza BalderasNessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento8 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataErroz RosadiNessuna valutazione finora

- Fdd390N15Alz: N-Channel Powertrench MosfetDocumento9 pagineFdd390N15Alz: N-Channel Powertrench Mosfetserrano.flia.coNessuna valutazione finora

- Mosfet 4242Documento8 pagineMosfet 4242cruz yorisNessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento8 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataElvis LinaresNessuna valutazione finora

- fdp054n10 PDFDocumento8 paginefdp054n10 PDFAldi DwprstwnNessuna valutazione finora

- Ap4na1r4cmt ADocumento6 pagineAp4na1r4cmt AMar GaoNessuna valutazione finora

- TC6215 N-And P-Channel Enhancement-Mode Dual MOSFET: Features General DescriptionDocumento5 pagineTC6215 N-And P-Channel Enhancement-Mode Dual MOSFET: Features General DescriptionfelipekillerNessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento13 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataEdson CostaNessuna valutazione finora

- Gan GS66516T-DS-Rev-210727Documento20 pagineGan GS66516T-DS-Rev-210727Venkatesan SwamyNessuna valutazione finora

- IRGP50B60PD1PBFDocumento11 pagineIRGP50B60PD1PBFtecnicogato27Nessuna valutazione finora

- Irfp640: DSS D DS (On)Documento2 pagineIrfp640: DSS D DS (On)dennis ovichNessuna valutazione finora

- P-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento10 pagineP-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataAnonymous nQ4z7PNessuna valutazione finora

- SM3331PSQG: Features Pin DescriptionDocumento10 pagineSM3331PSQG: Features Pin DescriptionJesus MendezNessuna valutazione finora

- Littelfuse Power Semiconductor Ignition IGBT Devic-1224117Documento10 pagineLittelfuse Power Semiconductor Ignition IGBT Devic-1224117ProbadorAutomotrizNessuna valutazione finora

- Irf6775mpbf PDFDocumento10 pagineIrf6775mpbf PDFMárcio FerreiraNessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento6 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DatavetchboyNessuna valutazione finora

- STB40NS15: N-CHANNEL 150V - 0.042 - 40A D PAK Mesh Overlay™ MosfetDocumento7 pagineSTB40NS15: N-CHANNEL 150V - 0.042 - 40A D PAK Mesh Overlay™ Mosfetamit singhNessuna valutazione finora

- 100N10 EtcDocumento5 pagine100N10 EtcJm TechNessuna valutazione finora

- 65N06 Series: N-Channel Power MOSFET (63A, 55volts) DescriptionDocumento8 pagine65N06 Series: N-Channel Power MOSFET (63A, 55volts) DescriptionRamon Cuba LopezNessuna valutazione finora

- (Buck Switch 2 GaN 60A) GS66516B-DS-Rev-200402Documento16 pagine(Buck Switch 2 GaN 60A) GS66516B-DS-Rev-200402Nguyen Dinh TuyenNessuna valutazione finora

- Silicon Carbide Power MOSFET C3M MOSFET Technology: N-Channel Enhancement ModeDocumento10 pagineSilicon Carbide Power MOSFET C3M MOSFET Technology: N-Channel Enhancement Modealllim88Nessuna valutazione finora

- HX50N06 Heatsink Planar N-Channel Power MOSFETDocumento6 pagineHX50N06 Heatsink Planar N-Channel Power MOSFETDaniel OrtizNessuna valutazione finora

- IRF150 Hexfet Transistors JANTX2N6764 THRU-HOLE (TO-204AA/AE) JANTXV2N6764 (REF:MIL-PRF-19500/543) 100V, N-CHANNELDocumento7 pagineIRF150 Hexfet Transistors JANTX2N6764 THRU-HOLE (TO-204AA/AE) JANTXV2N6764 (REF:MIL-PRF-19500/543) 100V, N-CHANNELHarshal VaidyaNessuna valutazione finora

- IRF150 Hexfet Transistors JANTX2N6764 THRU-HOLE (TO-204AA/AE) JANTXV2N6764 (REF:MIL-PRF-19500/543) 100V, N-CHANNELDocumento7 pagineIRF150 Hexfet Transistors JANTX2N6764 THRU-HOLE (TO-204AA/AE) JANTXV2N6764 (REF:MIL-PRF-19500/543) 100V, N-CHANNELAlex OrdazNessuna valutazione finora

- Order this semiconductor technical data sheetDocumento8 pagineOrder this semiconductor technical data sheetd4wq3Nessuna valutazione finora

- IRFB4227PBF Infineon Datasheet 9782845Documento3 pagineIRFB4227PBF Infineon Datasheet 9782845IvanNessuna valutazione finora

- Auirfz44Vzs: DSS DS (On)Documento12 pagineAuirfz44Vzs: DSS DS (On)Jesús alberto sanchez aularNessuna valutazione finora

- Datasheet MOSFET - 2N7000 - Supertex IIIDocumento6 pagineDatasheet MOSFET - 2N7000 - Supertex IIICristian Daniel BerettaNessuna valutazione finora

- Irf530 DDocumento8 pagineIrf530 DnooneezNessuna valutazione finora

- NCEP40T15G: Super TrenchDocumento6 pagineNCEP40T15G: Super TrenchwilsonNessuna valutazione finora

- SMPS IGBT Module with Ultrafast Soft Recovery DiodeDocumento10 pagineSMPS IGBT Module with Ultrafast Soft Recovery DiodeIvanilto Martins da CruzNessuna valutazione finora

- Irgp 35 B 60 PDDocumento11 pagineIrgp 35 B 60 PDflywheel2006Nessuna valutazione finora

- 2N7000 N-Channel Enhancement-Mode Vertical Dmos Fets: Features General DescriptionDocumento5 pagine2N7000 N-Channel Enhancement-Mode Vertical Dmos Fets: Features General DescriptionNìcòlàs HedNessuna valutazione finora

- Ap4n2r1mt V1Documento6 pagineAp4n2r1mt V1Mar GaoNessuna valutazione finora

- 100V N-Channel Mosfets: General DescriptionDocumento5 pagine100V N-Channel Mosfets: General DescriptionMariusNessuna valutazione finora

- B60ne06l 16Documento5 pagineB60ne06l 16Antonio RuanoNessuna valutazione finora

- Fdp3651U N-Channel Powertrench Mosfet: 100V, 80A, 15M Features ApplicationsDocumento6 pagineFdp3651U N-Channel Powertrench Mosfet: 100V, 80A, 15M Features ApplicationsAli R.MNessuna valutazione finora

- 900V 1.4Ω N-channel Power MOSFETDocumento5 pagine900V 1.4Ω N-channel Power MOSFETeverestoNessuna valutazione finora

- Fqa 24 N 50Documento8 pagineFqa 24 N 50CristhianNessuna valutazione finora

- NCEP4090GUDocumento6 pagineNCEP4090GUMar GaoNessuna valutazione finora

- FSCL S A0001051898 1Documento14 pagineFSCL S A0001051898 1LuisNessuna valutazione finora

- 8077 SPL Hovedpublikation - UK - WEB FINAL-ADocumento60 pagine8077 SPL Hovedpublikation - UK - WEB FINAL-ALuisNessuna valutazione finora

- AN4629Documento41 pagineAN4629Billy PhillipsNessuna valutazione finora

- AN-400 Application NoteDocumento6 pagineAN-400 Application NoteLuisNessuna valutazione finora

- Self-Study Research: Surfacing The Art of Pedagogy in Teacher EducationDocumento15 pagineSelf-Study Research: Surfacing The Art of Pedagogy in Teacher EducationanupriyaNessuna valutazione finora

- EMC Filter Design With RB Common Mode ChokesDocumento22 pagineEMC Filter Design With RB Common Mode Chokeskaem1189Nessuna valutazione finora

- Universal Active Filter: Features DescriptionDocumento16 pagineUniversal Active Filter: Features DescriptionLuisNessuna valutazione finora

- Newtec Application Note Iot ScadaDocumento8 pagineNewtec Application Note Iot ScadaLuisNessuna valutazione finora

- AN-31 Amplifier Circuit Collection PDFDocumento42 pagineAN-31 Amplifier Circuit Collection PDFcasagrandeNessuna valutazione finora

- Application Note AN-1084: Power MOSFET BasicsDocumento13 pagineApplication Note AN-1084: Power MOSFET Basicshardcore18Nessuna valutazione finora

- High Frequency Surface Mount Power Over Ethernet TransformersDocumento3 pagineHigh Frequency Surface Mount Power Over Ethernet TransformersLuisNessuna valutazione finora

- Application Note AN-1084: Power MOSFET BasicsDocumento13 pagineApplication Note AN-1084: Power MOSFET Basicshardcore18Nessuna valutazione finora

- Snoa 621 CDocumento26 pagineSnoa 621 CLalit GoelNessuna valutazione finora

- Sensor TemperatureDocumento1 paginaSensor TemperatureLuisNessuna valutazione finora

- Buck Converter Design NoteDocumento17 pagineBuck Converter Design NoteZhao XuNessuna valutazione finora

- BJT 1Documento14 pagineBJT 1Deeptonabho DuttaNessuna valutazione finora

- Fds 6875Documento5 pagineFds 6875dreyes3773Nessuna valutazione finora

- Introduction To VLSI: by Bhushan PatilDocumento47 pagineIntroduction To VLSI: by Bhushan PatilInderJeet GehlotNessuna valutazione finora

- Level 54 Bsim4Documento17 pagineLevel 54 Bsim4sohamgNessuna valutazione finora

- 2N4393 TransistorDocumento2 pagine2N4393 TransistorJuan Carlos Arellano BeltránNessuna valutazione finora

- Elec CommsDocumento1 paginaElec Commsseia deirahNessuna valutazione finora

- William Stallings Computer Organization and Architecture 8th Edition Internal MemoryDocumento20 pagineWilliam Stallings Computer Organization and Architecture 8th Edition Internal MemorySheikh ZainNessuna valutazione finora

- TCAD Based Analysis of Gate Leakage Current For High-K Gate Stack MOSFETDocumento4 pagineTCAD Based Analysis of Gate Leakage Current For High-K Gate Stack MOSFETIDESNessuna valutazione finora

- Irhlf77214 250V Radhard N MosfetDocumento9 pagineIrhlf77214 250V Radhard N MosfetarsebiscuitsNessuna valutazione finora

- Databook Zener Diodes (SMD) PDFDocumento369 pagineDatabook Zener Diodes (SMD) PDFgondoNessuna valutazione finora

- Aeroflex MetelicsDocumento188 pagineAeroflex MetelicsPratikNessuna valutazione finora

- I2N65 Series: N-Channel Power MOSFET 12A, 650volts DescriptionDocumento7 pagineI2N65 Series: N-Channel Power MOSFET 12A, 650volts DescriptionMariusNessuna valutazione finora

- PN3565 Transistor NPNDocumento1 paginaPN3565 Transistor NPNJuliansyahNessuna valutazione finora

- 100N50P IXFB Power Mosfet PDFDocumento5 pagine100N50P IXFB Power Mosfet PDFHưng HQNessuna valutazione finora

- Cta12 14 BomDocumento6 pagineCta12 14 BomIstván GerencsérNessuna valutazione finora

- BXXXXX EPROM Corss Reference For Car ECUDocumento6 pagineBXXXXX EPROM Corss Reference For Car ECUMariano VieraNessuna valutazione finora

- Nov Dec 2017Documento2 pagineNov Dec 2017manashNessuna valutazione finora

- EE136 S07 SyllabusDocumento2 pagineEE136 S07 Syllabusmaneem08Nessuna valutazione finora

- Raros y DiscontinuadosDocumento30 pagineRaros y Discontinuadosjackass_tNessuna valutazione finora

- GaN Sequencing CircuitDocumento5 pagineGaN Sequencing Circuitbharathi83Nessuna valutazione finora

- Bipolar Junction Transistors ExplainedDocumento43 pagineBipolar Junction Transistors ExplainedskarthikmtechNessuna valutazione finora

- Experiment 11: NPN BJT Common Emitter CharacteristicsDocumento7 pagineExperiment 11: NPN BJT Common Emitter CharacteristicsMalikAlrahabiNessuna valutazione finora

- Tda16810g 1Documento1 paginaTda16810g 1shohrat0% (1)

- Vlsi Question BankDocumento14 pagineVlsi Question BankGokila Vani50% (2)

- Troubleshooting HEX Lite Router BoardDocumento4 pagineTroubleshooting HEX Lite Router Boardantonio muñozNessuna valutazione finora

- BC558 Transistor Pinout, Equivalent, Uses, Features & Applications - ComponentsDocumento11 pagineBC558 Transistor Pinout, Equivalent, Uses, Features & Applications - ComponentsAderinla OkeowoNessuna valutazione finora

- MOS Field Effect Transistor 2SK3919: SMD Type IC Mosfet SMD TypeDocumento1 paginaMOS Field Effect Transistor 2SK3919: SMD Type IC Mosfet SMD Typeserrano.flia.coNessuna valutazione finora

- Lecture 2 The Manufacturing Process 2020Documento48 pagineLecture 2 The Manufacturing Process 2020Noam ShemlaNessuna valutazione finora

- Basics of Photovoltaic Cells and The Photovoltaic EffectDocumento15 pagineBasics of Photovoltaic Cells and The Photovoltaic Effectpranjal dubeyNessuna valutazione finora

- Emx1 / Umx1N / Imx1: General Purpose Transistor (Dual Transistors)Documento9 pagineEmx1 / Umx1N / Imx1: General Purpose Transistor (Dual Transistors)Juan CarlosNessuna valutazione finora