Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

FQPF 5 P 20

Caricato da

alf gon gonTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

FQPF 5 P 20

Caricato da

alf gon gonCopyright:

Formati disponibili

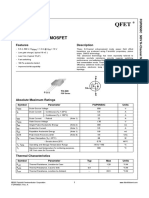

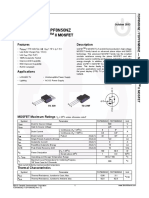

FQPF5P20

May 2000

QFET TM

FQPF5P20

200V P-Channel MOSFET

General Description

These P-Channel enhancement mode power field effect

transistors are produced using Fairchild’s proprietary, Features

planar stripe, DMOS technology. • -3.4A, -200V, RDS(on) = 1.4Ω @VGS = -10 V

This advanced technology has been especially tailored to • Low gate charge ( typical 10 nC)

minimize on-state resistance, provide superior switching • Low Crss ( typical 12 pF)

performance, and withstand high energy pulse in the • Fast switching

avalanche and commutation mode. These devices are well

• 100% avalanche tested

suited for high efficiency switching DC/DC converters.

S

!

●

G! ●

▶ ▲

●

GD S TO-220F !

FQPF Series D

Absolute Maximum Ratings TC = 25°C unless otherwise noted

Symbol Parameter FQPF5P20 Units

VDSS Drain-Source Voltage -200 V

ID Drain Current - Continuous (TC = 25°C) -3.4 A

- Continuous (TC = 100°C) -2.15 A

IDM Drain Current - Pulsed (Note 1) -13.6 A

VGSS Gate-Source Voltage ± 30 V

EAS Single Pulsed Avalanche Energy (Note 2) 330 mJ

IAR Avalanche Current (Note 1) -3.4 A

EAR Repetitive Avalanche Energy (Note 1) 3.8 mJ

dv/dt Peak Diode Recovery dv/dt (Note 3) -5.5 V/ns

PD Power Dissipation (TC = 25°C) 38 W

- Derate above 25°C 0.3 W/°C

TJ, TSTG Operating and Storage Temperature Range -55 to +150 °C

Maximum lead temperature for soldering purposes,

TL 300 °C

1/8" from case for 5 seconds

Thermal Characteristics

Symbol Parameter Typ Max Units

RθJC Thermal Resistance, Junction-to-Case -- 3.29 °C/W

RθJA Thermal Resistance, Junction-to-Ambient -- 62.5 °C/W

©2000 Fairchild Semiconductor International Rev. A, May 2000

FQPF5P20

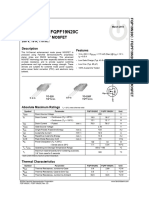

Elerical Characteristics TC = 25°C unless otherwise noted

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BVDSS Drain-Source Breakdown Voltage VGS = 0 V, ID = -250 µA -200 -- -- V

∆BVDSS Breakdown Voltage Temperature

ID = -250 µA, Referenced to 25°C -- -0.17 -- V/°C

/ ∆TJ Coefficient

IDSS VDS = -200 V, VGS = 0 V -- -- -1 µA

Zero Gate Voltage Drain Current

VDS = -160 V, TC = 125°C -- -- -10 µA

IGSSF Gate-Body Leakage Current, Forward VGS = -30 V, VDS = 0 V -- -- -100 nA

IGSSR Gate-Body Leakage Current, Reverse VGS = 30 V, VDS = 0 V -- -- 100 nA

On Characteristics

VGS(th) Gate Threshold Voltage VDS = VGS, ID = -250 µA -3.0 -- -5.0 V

RDS(on) Static Drain-Source

VGS = -10 V, ID = -1.7 A -- 1.1 1.4 Ω

On-Resistance

gFS Forward Transconductance VDS = -40 V, ID = -1.7 A (Note 4) -- 2.15 -- S

Dynamic Characteristics

Ciss Input Capacitance VDS = -25 V, VGS = 0 V, -- 330 430 pF

Coss Output Capacitance f = 1.0 MHz -- 75 98 pF

Crss Reverse Transfer Capacitance -- 12 15 pF

Switching Characteristics

td(on) Turn-On Delay Time -- 9 28 ns

VDD = -100 V, ID = -4.8 A,

tr Turn-On Rise Time -- 70 150 ns

RG = 25 Ω

td(off) Turn-Off Delay Time -- 12 35 ns

(Note 4, 5)

tf Turn-Off Fall Time -- 25 60 ns

Qg Total Gate Charge VDS = -160 V, ID = -4.8 A, -- 10 13 nC

Qgs Gate-Source Charge VGS = -10 V -- 2.8 -- nC

Qgd Gate-Drain Charge (Note 4, 5) -- 5.2 -- nC

Drain-Source Diode Characteristics and Maximum Ratings

IS Maximum Continuous Drain-Source Diode Forward Current -- -- -3.4 A

ISM Maximum Pulsed Drain-Source Diode Forward Current -- -- -13.6 A

VSD Drain-Source Diode Forward Voltage VGS = 0 V, IS = -3.4 A -- -- -5.0 V

trr Reverse Recovery Time VGS = 0 V, IS = -4.8 A, -- 175 -- ns

Qrr Reverse Recovery Charge dIF / dt = 100 A/µs (Note 4)

-- 1.07 -- µC

Notes:

1. Repetitive Rating : Pulse width limited by maximum junction temperature

2. L = 42.8mH, IAS = -3.4A, VDD = -50V, RG = 25 Ω, Starting TJ = 25°C

3. ISD ≤ -4.8A, di/dt ≤ 300A/µs, VDD ≤ BVDSS, Starting TJ = 25°C

4. Pulse Test : Pulse width ≤ 300µs, Duty cycle ≤ 2%

5. Essentially independent of operating temperature

©2000 Fairchild Semiconductor International Rev. A, May 2000

FQPF5P20

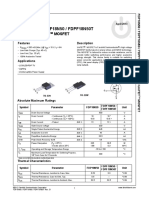

• Improved dv/dt capability

10

1

Top :

VGS

-15.0 V Typic 10

1

-10.0 V

-8.0 V

-7.0 V

-6.5 V

-6.0 V

-I D , Drain Current [A]

0

-I D, Drain Current [A]

10 Bottom : -5.5 V

0

10 150℃

-1

10

25℃

※ Notes : ※ Notes :

1. 250μs Pulse Test -55℃ 1. VDS = -40V

2. TC = 25℃ 2. 250μs Pulse Test

-2 -1

10 10

10

-1

10

0

10

1 2 4 6 8 10

-VDS, Drain-Source Voltage [V] al -VGS , Gate-Source Voltage [V]

Characteristics

Figure 1. On-Region Characteristics Figure 2. Transfer Characteristics

3.0

1

10

2.4 VGS = - 10V

Drain-Source On-Resistance

-I DR , Reverse Drain Current [A]

VGS = - 20V

RDS(on) [ Ω ],

1.8

0

10

1.2

0.6 ※ Notes :

150℃ 25℃

※ Note : TJ = 25℃ 1. VGS = 0V

2. 250μs Pulse Test

0.0 -1

10

0 3 6 9 12 0.0 0.5 1.0 1.5 2.0 2.5 3.0

-ID , Drain Current [A] -VSD , Source-Drain Voltage [V]

Figure 3. On-Resistance Variation vs. Figure 4. Body Diode Forward Voltage

Drain Current and Gate Voltage Variation vs. Source Current

and Temperature

750 12

Ciss = Cgs + Cgd (Cds = shorted)

Coss = Cds + Cgd

Crss = Cgd VDS = -40V

10

600 VDS = -100V

-V GS , Gate-Source Voltage [V]

VDS = -160V

8

Ciss

Capacitance [pF]

450

6

Coss

300

※ Notes : 4

1. VGS = 0 V

Crss 2. f = 1 MHz

150

2

※ Note : ID = -4.8 A

0 0

10

-1

10

0

10

1 0 2 4 6 8 10 12

-VDS, Drain-Source Voltage [V] QG, Total Gate Charge [nC]

Figure 5. Capacitance Characteristics Figure 6. Gate Charge Characteristics

©2000 Fairchild Semiconductor International Rev. A, May 2000

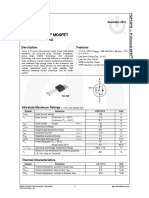

FQPF5P20

Typical Characteristics (Continued)

1.2 2.5

2.0

Drain-Source Breakdown Voltage

1.1

Drain-Source On-Resistance

-BV DSS , (Normalized)

RDS(ON) , (Normalized)

1.5

1.0

1.0

0.9 ※ Notes :

1. VGS = 0 V 0.5 ※ Notes :

2. ID = -250 μA 1. VGS = -10 V

2. ID = -2.4 A

0.8 0.0

-100 -50 0 50 100 150 200 -100 -50 0 50 100 150 200

o o

TJ, Junction Temperature [ C] TJ, Junction Temperature [ C]

Figure 7. Breakdown Voltage Variation Figure 8. On-Resistance Variation

vs. Temperature vs. Temperature

Operation in This Area

is Limited by R DS(on)

1

10 3

1 ms

-I D, Drain Current [A]

-I D, Drain Current [A]

10 ms

100 ms

2

DC

0

10

※ Notes : 1

o

1. TC = 25 C

o

-1 2. TJ = 150 C

10

3. Single Pulse

0

0 1 2

10 10 10 25 50 75 100 125 150

-VDS, Drain-Source Voltage [V] TC, Case Temperature [℃]

Figure 9. Maximum Safe Operating Area Figure 10. Maximum Drain Current

vs. Case Temperature

( t) , T h e r m a l R e s p o n s e

D = 0 .5

0

10

0 .2

※ N o te s :

0 .1 1 . Z θ J C ( t) = 3 .2 9 ℃ / W M a x .

2 . D u ty F a c to r , D = t 1 /t 2

0 .0 5 3 . T J M - T C = P D M * Z θ J C ( t)

-1

10

0 .0 2 PDM

0 .0 1

θ JC

t1

t2

Z

s i n g le p u ls e

-2

10

-5 -4 -3 -2 -1 0 1

10 10 10 10 10 10 10

t 1 , S q u a r e W a v e P u ls e D u r a t io n [ s e c ]

Figure 11. Transient Thermal Response Curve

©2000 Fairchild Semiconductor International Rev. A, May 2000

FQPF5P20

Gate Charge Test Circuit & Waveform

VGS

Same Type

50KΩ

as DUT Qg

12V 200nF

300nF -10V

VDS

VGS Qgs Qgd

DUT

-3mA

Charge

Resistive Switching Test Circuit & Waveforms

RL

VDS t on t off

td(on) tr td(off)

VGS VDD tf

RG VGS

10%

-10V DUT

90%

VDS

Unclamped Inductive Switching Test Circuit & Waveforms

L 1 BVDSS

VDS EAS = ---- L IAS2 --------------------

2 BVDSS - VDD

tp Time

ID

RG VDD VDS (t)

VDD

ID (t)

-10V DUT

IAS

tp BVDSS

©2000 Fairchild Semiconductor International Rev. A, May 2000

FQPF5P20

Peak Diode Recovery dv/dt Test Circuit & Waveforms

VDS

DUT _

I SD

L

Driver

RG

Compliment of DUT

(N-Channel) VDD

VGS • dv/dt controlled by RG

• ISD controlled by pulse period

Gate Pulse Width

VGS D = --------------------------

Gate Pulse Period 10V

( Driver )

Body Diode Reverse Current

I SD

( DUT ) IRM

di/dt

IFM , Body Diode Forward Current

VDS VSD

( DUT )

Body Diode VDD

Forward Voltage Drop

Body Diode Recovery dv/dt

©2000 Fairchild Semiconductor International Rev. A, May 2000

FQPF5P20

Package Dimensions

TO-220F

3.30 ±0.10

10.16 ±0.20 ø3.18 ±0.10 2.54 ±0.20

(7.00) (0.70)

6.68 ±0.20

15.87 ±0.20

15.80 ±0.20

(1.00x45°)

MAX1.47

9.75 ±0.30

0.80 ±0.10

(3

0°

)

#1

0.35 ±0.10 +0.10

0.50 –0.05 2.76 ±0.20

2.54TYP 2.54TYP

[2.54 ±0.20] [2.54 ±0.20]

4.70 ±0.20

9.40 ±0.20

©2000 Fairchild Semiconductor International Rev. A, May 2000

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx™ HiSeC™ SuperSOT™-8

Bottomless™ ISOPLANAR™ SyncFET™

CoolFET™ MICROWIRE™ TinyLogic™

CROSSVOLT™ POP™ UHC™

E2CMOS™ PowerTrench® VCX™

FACT™ QFET™

FACT Quiet Series™ QS™

FAST® Quiet Series™

FASTr™ SuperSOT™-3

GTO™ SuperSOT™-6

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;

NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR

INTERNATIONAL.

As used herein: result in significant injury to the user.

1. Life support devices or systems are devices or systems 2. A critical component is any component of a life support

which, (a) are intended for surgical implant into the body, device or system whose failure to perform can be

or (b) support or sustain life, or (c) whose failure to perform reasonably expected to cause the failure of the life support

when properly used in accordance with instructions for use device or system, or to affect its safety or effectiveness.

provided in the labeling, can be reasonably expected to

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In This datasheet contains the design specifications for

Design product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

©2000 Fairchild Semiconductor International Rev. A, January 2000

Potrebbero piacerti anche

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Lely Welger AP 530 Manual deDocumento94 pagineLely Welger AP 530 Manual deJimmy ZettenbergNessuna valutazione finora

- 6025e PDFDocumento43 pagine6025e PDFmuppetscrapNessuna valutazione finora

- Datasheet FQPF11P06Documento8 pagineDatasheet FQPF11P06John SalsaNessuna valutazione finora

- FQP5N50C/FQPF5N50C: 500V N-Channel MOSFETDocumento10 pagineFQP5N50C/FQPF5N50C: 500V N-Channel MOSFETalllim88Nessuna valutazione finora

- FQB5N60CDocumento9 pagineFQB5N60CadilsonmagnNessuna valutazione finora

- FQP6N50C: 500V N-Channel MOSFETDocumento8 pagineFQP6N50C: 500V N-Channel MOSFETHenry ToroNessuna valutazione finora

- FQPF10N60CDocumento10 pagineFQPF10N60Cmiloud1911Nessuna valutazione finora

- FQP6N60C/FQPF6N60C: 600V N-Channel MOSFETDocumento10 pagineFQP6N60C/FQPF6N60C: 600V N-Channel MOSFETmaster -DvNessuna valutazione finora

- FQPF6N60 - 600V, 3a6Documento8 pagineFQPF6N60 - 600V, 3a6RenatoMaiaNessuna valutazione finora

- FQD7P06: P-Channel QFET MosfetDocumento9 pagineFQD7P06: P-Channel QFET MosfetIsela LopezNessuna valutazione finora

- FQP9N50CDocumento10 pagineFQP9N50CGaouldNessuna valutazione finora

- HY27UF084G2B HynixSemiconductorDocumento7 pagineHY27UF084G2B HynixSemiconductorDrew AlbaneseNessuna valutazione finora

- fqpf5n50cf Fqpf5n50cftu PDFDocumento8 paginefqpf5n50cf Fqpf5n50cftu PDFALFREDO BARREZUETANessuna valutazione finora

- IRFW730Documento10 pagineIRFW730Jorge HernÁn Hoyos VÉlezNessuna valutazione finora

- 9n90c fqpf9n90cDocumento10 pagine9n90c fqpf9n90cTahar BenacherineNessuna valutazione finora

- FQP9N90C/FQPF9N90C: 900V N-Channel MOSFETDocumento10 pagineFQP9N90C/FQPF9N90C: 900V N-Channel MOSFETHeru susantoNessuna valutazione finora

- FQA36P15: 150V P-Channel MOSFETDocumento8 pagineFQA36P15: 150V P-Channel MOSFETsefermanNessuna valutazione finora

- FQP7N65C/FQPF7N65C: 650V N-Channel MOSFETDocumento10 pagineFQP7N65C/FQPF7N65C: 650V N-Channel MOSFETOneto Ayah KhayraNessuna valutazione finora

- Fqa19n60 PDFDocumento8 pagineFqa19n60 PDFHưng HQNessuna valutazione finora

- FQP19N20CDocumento10 pagineFQP19N20CVinicio VieiraNessuna valutazione finora

- FQP10N20C / FQPF10N20C: N-Channel QFET MosfetDocumento10 pagineFQP10N20C / FQPF10N20C: N-Channel QFET MosfethenriquegonferNessuna valutazione finora

- fcp11n60 fcpf11n60 PDFDocumento10 paginefcp11n60 fcpf11n60 PDFÁńä Átéńćià DóvàlésNessuna valutazione finora

- FQP10N20C/FQPF10N20C: 200V N-Channel MOSFETDocumento10 pagineFQP10N20C/FQPF10N20C: 200V N-Channel MOSFETIvanNessuna valutazione finora

- Frfet: FQA24N50FDocumento8 pagineFrfet: FQA24N50FqaisersgsNessuna valutazione finora

- FQP8N60C: N-Channel QFET MosfetDocumento8 pagineFQP8N60C: N-Channel QFET MosfetVuksanov ZarkoNessuna valutazione finora

- FQD4P25Documento9 pagineFQD4P25javabir128Nessuna valutazione finora

- FQPF7N65C FairchildSemiconductorDocumento10 pagineFQPF7N65C FairchildSemiconductorNovri AndiNessuna valutazione finora

- FQPF50N06Documento8 pagineFQPF50N06Leydi jazmín Herrera ortizNessuna valutazione finora

- FQPF7N80C FQPF7N80CDocumento12 pagineFQPF7N80C FQPF7N80Cmadeline cruzata downerNessuna valutazione finora

- 24N60 Data SheetDocumento8 pagine24N60 Data Sheetahangeraqib3333Nessuna valutazione finora

- Mosfet FQP50N06 60V - 50a PDFDocumento8 pagineMosfet FQP50N06 60V - 50a PDFGiraldoCarpioRamosNessuna valutazione finora

- FQP 70 N 10Documento8 pagineFQP 70 N 10Rahmat Destia HidayantoNessuna valutazione finora

- 16N60 Fairchild SemiconductorDocumento10 pagine16N60 Fairchild SemiconductorPop-Coman SimionNessuna valutazione finora

- 18N80T DatasheetDocumento10 pagine18N80T DatasheetVịnh DemoNessuna valutazione finora

- HM10N60FDocumento8 pagineHM10N60FВіталій ПузакNessuna valutazione finora

- Qfet Qfet Qfet Qfet: FQP13N10Documento8 pagineQfet Qfet Qfet Qfet: FQP13N10trabadoresincorformes incubadoraNessuna valutazione finora

- DatasheetDocumento8 pagineDatasheetjailton ferreiraNessuna valutazione finora

- IRF830B/IRFS830B: 500V N-Channel MOSFETDocumento10 pagineIRF830B/IRFS830B: 500V N-Channel MOSFETNilton sergio gomes linsNessuna valutazione finora

- FDP20N50 184794Documento11 pagineFDP20N50 184794Paulo NogueiraNessuna valutazione finora

- FQP12P10: P-Channel QFET MosfetDocumento8 pagineFQP12P10: P-Channel QFET MosfetCrdz LouisNessuna valutazione finora

- Fqa 85 N 06Documento8 pagineFqa 85 N 06romioalinNessuna valutazione finora

- FQPF12N60C FairchildSemiconductorDocumento9 pagineFQPF12N60C FairchildSemiconductorAkhmad Isnaeni RamdaniNessuna valutazione finora

- FQB10N20C/FQI10N20C: 200V N-Channel MOSFETDocumento9 pagineFQB10N20C/FQI10N20C: 200V N-Channel MOSFETDjalma MotaNessuna valutazione finora

- 6N90C Mosfet N PDFDocumento10 pagine6N90C Mosfet N PDFHưng HQNessuna valutazione finora

- Qfet Qfet Qfet Qfet: FQP6N60Documento8 pagineQfet Qfet Qfet Qfet: FQP6N60Franco GutierrezNessuna valutazione finora

- FCP 11 N 60Documento10 pagineFCP 11 N 60alive ElectronicsNessuna valutazione finora

- FQP10N60C DatasheetzDocumento10 pagineFQP10N60C DatasheetzagesoporteNessuna valutazione finora

- FCP11N60/FCPF11N60: General Description FeaturesDocumento10 pagineFCP11N60/FCPF11N60: General Description FeaturesRodrigo MagNessuna valutazione finora

- DatasheetDocumento8 pagineDatasheetRegisk8 OliveiraNessuna valutazione finora

- Fqa38n30 310169Documento9 pagineFqa38n30 310169Владимир ВайнерNessuna valutazione finora

- Fdp8N50Nz / Fdpf8N50Nz: N-Channel Unifet Ii MosfetDocumento10 pagineFdp8N50Nz / Fdpf8N50Nz: N-Channel Unifet Ii MosfetsrasicNessuna valutazione finora

- FQD11P06 / FQU11P06: P-Channel QFET MosfetDocumento9 pagineFQD11P06 / FQU11P06: P-Channel QFET MosfetMansurjanNessuna valutazione finora

- Fcb20N60: N-Channel Superfet MosfetDocumento9 pagineFcb20N60: N-Channel Superfet MosfetEo GpNessuna valutazione finora

- FQPF13N50CFDocumento8 pagineFQPF13N50CFPiotr vvNessuna valutazione finora

- FFB 2907 - FairchildDocumento8 pagineFFB 2907 - FairchildStevenNessuna valutazione finora

- FQPF 8 N 60 CFDocumento8 pagineFQPF 8 N 60 CFBhadreshkumar SharmaNessuna valutazione finora

- Fdp52N20 / Fdpf52N20T: UnifetDocumento10 pagineFdp52N20 / Fdpf52N20T: UnifetJoão de barroNessuna valutazione finora

- 20 N 60Documento10 pagine20 N 60Asep AcengNessuna valutazione finora

- Irf614b, Irfs614bDocumento11 pagineIrf614b, Irfs614bSastra DjinggaNessuna valutazione finora

- DZS EWaste Collection FlyerDocumento1 paginaDZS EWaste Collection FlyerWXYZ-TV Channel 7 DetroitNessuna valutazione finora

- Fire Fighting SystemsDocumento68 pagineFire Fighting SystemsAyman AlssametNessuna valutazione finora

- Codigos SP y SC Aficio 2075Documento212 pagineCodigos SP y SC Aficio 2075Xelcop RojasNessuna valutazione finora

- N Series: BoostersDocumento5 pagineN Series: BoostersMohamed Nagim Cheikh AhmedNessuna valutazione finora

- 1vcp000931 Rev e CA DcbreakDocumento26 pagine1vcp000931 Rev e CA DcbreakMouth GoonieNessuna valutazione finora

- Asme b16.5 Class 150 Flanges Bolting Pattern and Dimensions Chart Northwest FastenerDocumento1 paginaAsme b16.5 Class 150 Flanges Bolting Pattern and Dimensions Chart Northwest FastenerRyan SolomonNessuna valutazione finora

- Ease of Use: Product Sheet Thermoflexx 80Documento4 pagineEase of Use: Product Sheet Thermoflexx 80Chamakhi AmeurNessuna valutazione finora

- Parker Válvula de Segurança Modelos Type HDocumento2 pagineParker Válvula de Segurança Modelos Type HFrancisco Javier Leal BrachoNessuna valutazione finora

- Practical Guide To Electrical Grounding, 1st Edition, 1999-EricoDocumento134 paginePractical Guide To Electrical Grounding, 1st Edition, 1999-EricoFABIANO FREIRE DA SILVANessuna valutazione finora

- Group 3 Electrical SystemDocumento16 pagineGroup 3 Electrical SystemTaha RdmanNessuna valutazione finora

- Manual Centrífuga HERMLE Z - 326Documento48 pagineManual Centrífuga HERMLE Z - 326Lucila Figueroa GalloNessuna valutazione finora

- P1.3.R02 LBG Linear Bar Grille.A4Documento6 pagineP1.3.R02 LBG Linear Bar Grille.A4ekahNessuna valutazione finora

- Pilz Pnoz - User ManualDocumento26 paginePilz Pnoz - User ManualWellington MatosNessuna valutazione finora

- Addressable Optical-Smoke Fire Detector FD7130: Technical DataDocumento1 paginaAddressable Optical-Smoke Fire Detector FD7130: Technical DatamohammadNessuna valutazione finora

- LuxOR Revalia Spec SheetDocumento2 pagineLuxOR Revalia Spec SheetmonicaNessuna valutazione finora

- MT Overview CatalogueDocumento8 pagineMT Overview Catalogue1339979Nessuna valutazione finora

- S01DCXX8S20-Heating and Air ConditioningDocumento203 pagineS01DCXX8S20-Heating and Air ConditioningIon Olteanu100% (1)

- CodeDocumento72 pagineCodeKushal BajracharyaNessuna valutazione finora

- Etp, Boq - AaaDocumento8 pagineEtp, Boq - Aaagnbuildtech Pvt ltdNessuna valutazione finora

- Grove 6350 PDFDocumento28 pagineGrove 6350 PDFechavarriNessuna valutazione finora

- FM09016A NV Series HD Upgrade NAE100 101 ExcitersDocumento9 pagineFM09016A NV Series HD Upgrade NAE100 101 ExcitersBG JluisNessuna valutazione finora

- Chapter 4:jfet: Junction Field Effect TransistorDocumento67 pagineChapter 4:jfet: Junction Field Effect TransistorMohammad NasutionNessuna valutazione finora

- Tp6667 Generator SetsDocumento108 pagineTp6667 Generator SetsRoberto Sanchez ZapataNessuna valutazione finora

- Endress KatalogDocumento72 pagineEndress KatalogpnsanatNessuna valutazione finora

- SCR Triggering MethodsDocumento12 pagineSCR Triggering Methodsbangs34Nessuna valutazione finora

- 03 Greasing SystemDocumento3 pagine03 Greasing SystemAnonymous vyUisZImrNessuna valutazione finora

- 6 - Transportation ElectrificationDocumento98 pagine6 - Transportation ElectrificationNamiraNessuna valutazione finora

- Experiment 07Documento3 pagineExperiment 07Harsh KalamNessuna valutazione finora