Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Hardware Architecture and Registers of the 8085 Microprocessor

Caricato da

CsTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Hardware Architecture and Registers of the 8085 Microprocessor

Caricato da

CsCopyright:

Formati disponibili

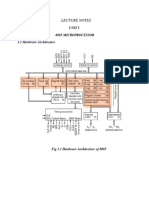

Hardware Architecture of 8085 Microprocessor :

There are totally six programmer accessible registers namely B,C,D,E,H,L that can either function as single 8-

bit register (such as B,C,D,E,H,L) or as 16-bit register pair such as BC , DE, HL. In case of register pair the

higher order byte is stored in first register (for example B-register in BC register pair) and lower order byte is

stored in second register (for example C-register in BC register pair). The HL register additionally functions as

MEMORY POINTER or DATA POINTER in MEMORY BASED DATA MOVEMENT INSTRUCTIONS.

The 8-bit registers W and Z are used for TEMPORARY DATA STORAGE when data is (i) moved between

registers (ii) Moved from internal registers to external data bus and vice-versa.

The 16-bit STACK POINTER(SP) is used to hold the address of TOP of STACK residing in external RAM. TOP OF

STACK is a STACK LOCATION where a RECENT PUSH OPERATION occurred. The type of STACK implemented is

LIFO(LAST IN FIRST OUT) , wherein the the element that is inserted into the LAST STACK location will be the

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

FIRST element to be removed. Two types of operations associated with STACK : (i) PUSH(INSERT) (ii) POP

(REMOVE). The SP gets decremented by 2 for every PUSH operation and incremented by 2 for every POP

operation. Default value of SP = FFFFH

The 16-bit PROGRAM COUNTER (PC) is used to hold the ADDRESS OF NEXT INSTRUCTION TO BE EXECUTED. It

increments or decrements by :

1 for 1-byte instruction

2 for 2-byte instruction

3 for 3-byte instruction

Default Value of PC = 0000H

The Incrementer/Decrementer Address Latch is used to hold the INCREMENTED or DECREMENTED contents of

PC and SP.

The 8-bit BUFFERS (Lower order MULTIPLEXED Address and Data Bus Buffer[AD7-AD0] and Higher order Address

Bus Buffer[A15-A8]) acts as a DATA COMMUNICATION INTERFACE between INTERNAL DATA BUS and EXTERNAL

DATA BUS. The address bus (A15-A0) carries the content of PC and SP. The data bus (D7-D0) carries the content

of BC , DE , PSW , HL register pairs.

The 8-bit INSTRUCTION REGISTER is used to hold the OPCODE (HEXADECIMAL EQUIVALENT of an INSTRUCTION).

The INSTRUCTION DECODER is used for enabling a PARTICULAR INTERNAL COMPONENT of 8085 microprocessor

based upon the instruction received.

The MACHINE CYCLE ENCODER is used for providing information about the CURRENTLY EXECUTING MACHINE

CYCLE of an INSTRUCTION EXECUTION.

The 8-bit ALU is used to perform the following ARITHMETIC and LOGICAL OPERATIONS :

ARITHMETIC OPERATIONS :

8-bit and 16-bit ADDITION with and without CARRY

8-bit and 16-bit SUBTRACTION with and without BORROW

8-bit and 16-bit INCREMENT operation

8-bit and 16-bit DECREMENT operation

8-bit BINARY to BCD CONVERSION

LOGICAL OPERATIONS :

8-bit AND , OR , NOT , XOR operations

1-bit SET and RESET operation

8-bit ROTATE LEFT and RIGHT operations with and without CARRY.

The components of ALU are : (i) ACCUMULATOR (ii) TEMP (iii) 8-bit ALU (iv) FLAG

ACCUMULATOR :

8-bit REGISTER that acts as SOURCE or DESTINATION REGISTER in case of DATA TRANSFER INSTRUCTIONS

8-bit REGISTER that acts as SOURCE AND/OR DESTINATION REGISTER in case of DATA MANIPULATION (or

ARITHMETIC and LOGICAL) INSTRUCTIONS.

First SOURCE operand in case of DATA MANIPULATION INSTRUCTIONS.

TEMP :

8-bit REGISTER that acts as SECOND SOURCE operand in case of DATA MANIPULATION INSTRUCTIONS.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

FLAG REGISTER:

D7 D6 D4 D2 D0

S Z AC P CY

Positive Number or Negative Number in the ACCUMULATOR (Sign bit [S])

Even Parity or Odd Parity in ACCUMULATOR (Parity bit [P])

Carry or borrow occurring at HIGHER ORDER NIBBLE of ACCUMULATOR (Carry bit or Overflow bit [CY])

Carry or borrow occurring at LOWER ORDER NIBBLE of ACCUMULATOR(Auxiliary Carry bit[AC])

Zero or Non-zero value in ACCUMULATOR(Zero bit).

Combination of ACCUMULATOR and FLAG REGISTER is called PSW (Program Status Word).

ACCUMULATOR(8-BITS) FLAG(5-BITS)

FIG. PSW.

The TIMING and CONTROL circuitry is used for GENERATING TIMING , CONTROL and STATUS signals that is

required for operation of INTERNAL and EXTERNAL CIRCUITRIES of 8085 microprocessor IN SYNCHRONISM

The SERIAL CONTROL CIRCUITRY is used for SHIFTING the contents into and out-of of ACCUMULATOR and an

EXTERNAL REMOTE PERIPHERAL DEVICE as SEQUENCE of 1-BITs.

The INTERRUPT CONTROL CIRCUITRY is used for receiving EDGE AND/OR LEVEL TRIGGERED INTERRUPT

SIGNALS from EXTERNAL PERIPHERAL DEVICES and accordingly SEND an ACKNOWLEDGEMENT to the

interrupting device when the CPU branches to the corresponding Interrupt Vector Address. 8085 supports 5

hardware interrupts and 8 software interrupts.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

Pin diagram of 8085 Microprocessor :

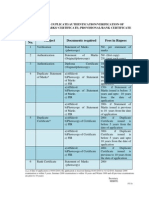

S.No PIN Number Description

POWER SUPPLY AND FREQUENCY SIGNALS

1. VCC Connected to +5V.

2. VSS Connected to GROUND

3. X1 and X2 LC circuit or RC circuit or Crystal connected between these two pins.

Provides the INPUT signal for generating CLOCK signal.

4. CLK OUT Frequency of CLOCK output signal = 0.5 × Frequency of input signal.

ADDRESS AND DATA BUS

5. AD0-AD7 Lower order 8-bit multiplexed address and data bus

Acts as Address Bus during T1 state of a machine cycle and Data Bus during T2 and

T3 states of a machine cycle.

When acting as address bus , it carries lower order byte of a memory location or

the 8-bit address of a I/O port.

6. A8-A15 Higher order address bus

Acts as Address bus throughout a machine cycle.

When acting as address bus , it carries higher order byte of a memory location or

the 8-bit address of I/O port

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

CONTROL AND STATUS SIGNALS

7. ALE ADDRESS LATCH ENABLE SIGNAL

Enables an external latch for demultiplexing the AD0-AD7 bus into A0-A7 and D0-

D7.

Active during T1 state of each machine cycle

8. ̅̅̅̅

𝑅𝐷 and ̅̅̅̅̅

𝑊𝑅 Active low signals

When RD signal is activated (ie.RD = 0) , the microprocessor reads a 8-bit data

from a selected memory location or Input port

When WR signal is activated (i.e. WR = 0) , the microprocessor writes a 8-bit data

into a selected memory location or output port.

Active during T2 and T3 states of each machine cycle.

9. ̅ , S0 ,

IO/𝑀 IO/𝑀 ̅ signal indicates whether 8085 microprocessor is currently accessing a

S1 memory location or I/O port. IO/𝑀 ̅ = 0 means 8085 is accessing a memory

̅

location and IO/𝑀 = 1 means 8085 is accessing a I/O port.

IO/𝑀̅ together with status signals S1 and S0 indicate what is the current machine

cycle executed by 8085 microprocessor.

Machine Cycle Status Signals

IO/𝑀̅ S1 S0

Bus Idle or No 0 0 0

Operation

Memory Write 0 0 1

I/O Write 1 0 1

Memory Read 0 1 0

I/O Read 1 1 0

INTR 1 1 1

Acknowledge

INTERRUPT SIGNALS

9. RST 5.5 – RST 8085 microprocessor supports 5 hardware interrupts.

7.5 , TRAP , Activating any one pin (TRAP or RST 7.5 or RST 6.5 or RST 5.5 or INTR) causes the

INTR , ̅̅̅̅̅̅̅

𝐼𝑁𝑇𝐴 microprocessor to complete its CURRENT INSTRUCTION EXECUTION.

Activation of INTA(INTerrupt Acknowledgement) signal by 8085 microprocessor

indicates it has accepted the INTR interrupt from the requesting device.

SERIAL I/O SIGNALS

10. SID , SOD SID refers to SERIAL INPUT DATA PIN

CONTENT IS FED INTO THE ACCUMULATOR FROM AN EXTERNAL DEVICE

THROUGH ITS MOST SIGNIFICANT BIT.

SOD refers to SERIAL OUTPUT DATA PIN

CONTENT IS FED OUT FROM THE ACCUMULATOR TO AN EXTERNAL DEVICE

THROUGH ITS MOST SIGNIFICANT BIT.

DMA (DIRECT MEMORY ACCESS) SIGNALS

11. HOLD , HOLD SIGNAL indicates that another microcontroller or microprocessor is

̅̅̅̅̅̅̅̅

𝐻𝐿𝐷𝐴 requesting the 8085 microprocessor to use its address bus , data bus and control

bus.

HLDA SIGNAL indicates the 8085 microprocessor has given permission to usage of

its buses to the requesting microcontroller or microprocessor

RESET SIGNALS

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

12. ̅̅̅̅̅̅̅̅̅̅̅̅̅

𝑅𝐸𝑆𝐸𝑇 𝐼𝑁 , Activating the RESET IN SIGNAL does the following :

RESET OUT Sets the PC value to 0000H

Clears the INTE (INTERRUPT ENABLE) flag (i.e. Interrupts are disabled)

Clears the HLDA flip-flop (i.e. DMA operation is discontinued)

Tri-states the address bus , data bus and control bus

Assigns random values to data registers.

Activation of RESET OUT signal indicates the following :

Reset operation is going inside the processor

Used for resetting the devices connected externally to 8085

microprocessor

Timing Diagrams of 8085 Microprocessor :

Instruction Cycle : Fetching , Decoding and Execution of a single 8085 instruction; Group of 1 to 5 machine cycles

constitute an Instruction cycle.

Machine Cycle : A Memory or I/O read and write operation ; Group of 3 to 6 T-states constitute a Machine cycle.

T-state or Clock period or clock cycle : A clock pulse consisting of falling edge followed by rising edge. T-state is

the time interval between TWO NEGATIVE or FALLING CLOCK EDGES.

Different types of machine cycles are as follows:

Opcode or Instruction Fetch Machine Cycle :

In this machine cycle , 8085 MICROPROCESSOR finds the nature of instruction to be executed.

During T1 state , the 8085 microprocessor places the contents of program counter on the address bus.

The Higher Order Byte of PC placed in A15-A8 bus and Lower Order Byte of PC placed in AD7-AD0 bus.

The ALE signal is activated which separates the AD7-AD0 bus by enabling an external latch for holding

the lower order byte of PC.

During T2 state , the RD signal enables the memory location present in A15-A0 bus.

During T3 state , the opcode from the addressed memory location is placed in D7-D0 bus and the RD

signal is disabled.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

During T4 state , the opcode is decoded by the instruction decoder to decide whether to enter another

T5 , T6-states or to enter T1 state of next machine cycle.

During T5 and T6 states , 8085 microprocessor performs STACK WRITE , INTERNAL 16-bit and

CONDITIONAL RETURN operations depending upon the type of instruction.

Instruction with 4 T-states in Opcode Fetch Cycle : MOV A , B ; ADD B

Instruction with 6 T-states in Opcode Fetch Cycle : PCHL , DCX H

Memory Read Machine Cycle :

In this machine cycle , 8085 microprocessor reads the data from a external RAM or ROM location.

During T1 state , the 8085 microprocessor places the contents of PC or SP or General Purpose Register

Pair on the address bus. The Higher Order Byte of PC or SP or the register pair placed in A15-A8 bus and

Lower Order Byte of PC or SP or the register pair placed in AD7-AD0 bus. The ALE signal is activated

which separates the AD7-AD0 bus by enabling an external latch for holding the lower order byte of PC or

SP or register pair.

During T2 state , the RD signal enables the memory location present in A15-A0 bus and 8-bit data is

placed in D7-D0 bus.

During T3 state , the 8-bit in D7-D0 bus is placed into a 8-bit register and the RD signal is disabled.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

Memory Write Machine Cycle :

In this machine cycle , 8085 microprocessor writes the data into a external RAM or ROM location.

During T1 state , the 8085 microprocessor places the contents of SP or General Purpose Register Pair on

the address bus. The Higher Order Byte of SP or the register pair placed in A15-A8 bus and Lower Order

Byte of SP or the register pair placed in AD7-AD0 bus. The ALE signal is activated which separates the

AD7-AD0 bus by enabling an external latch for holding the lower order byte of SP or register pair.

During T2 state , the WR signal enables the memory location present in A15-A0 bus and data in the D7-

D0 bus.

During T3 state , the WR signal is disable the memory location , thereby terminating the write cycle.

I/O Read Machine Cycle :

In this machine cycle , 8085 microprocessor reads the data from an external input port.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

During T1 state , the 8085 microprocessor places the input port address on A15-A0 bus.

During T2 state , the RD signal enables the Input Port present in A15-A8 bus or A7-A0 bus and 8-bit

data is placed in D7-D0 bus.

During T3 state , the 8-bit in D7-D0 bus is placed into a 8-bit register and the RD signal is disabled.

I/O Write Machine Cycle:

In this machine cycle , 8085 microprocessor writes the data into an external output port.

During T1 state , the 8085 microprocessor places the input port address on A15-A0 bus.

During T2 state , the WR signal enables the Output Port present in A15-A8 bus or A7-A0 bus and 8-

bit data is placed in D7-D0 bus.

During T3 state , the 8-bit in D7-D0 bus is placed into the addressed output port and the WR signal is

disabled.

Interrupt Acknowledgement Cycle :

In this machine cycle , 8085 microprocessor responds to an interrupt request sent by a

peripheral device .

The peripheral device places a RST or CALL instruction in the D7-D0 bus.

In case if the received opcode is that of CALL instruction , three machine cycles are taken. One

cycle for receiving the opcode , second cycle and thire cycles for receiving the branching

address. During these machine cycles , the value of PC is not incremented.

During 4th and 5th machine cycles , the current contents of PC are written into the TOP of STACK

pointed by the SP.

Then the 8085 microprocessor places the branching address onto PC.

In case if the received opcode is that of RST instruction (Software Interrupt) , execution is similar

to that of CALL instruction , except 4th and 5th machine cycles does not occur.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

Bus Idle Machine Cycle :

Bus Idle means neither a read or write operation occurs through the bus.

The concept of Bus Idle Machine cycle is explained for DAD instruction , RST and TRAP interrupts

Fig. BUS IDLE MACHINE CYCLE for DAD instruction

DAD instruction takes 10 T-states to execute. 4 T-states for opcode fetch and 6 T-states for adding the 16-bit

contents of HL register pair and given register pair. During those 6 T-states neither a memory or I/O read or

write operation takes place in the bus. These T-states are referred as BUS IDLE machine cycle. In case of DAD

instruction , RD and ALE signals are not activated.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

Fig. BUS IDLE MACHINE CYCLE for TRAP instruction

During INTERNAL OPCODE GENERATION for TRAP and RST instructions , 8085 executes BUS IDLE

machine cycles. In response to TRAP interrupt , 8085 enters into BUS IDLE machine cycle and invokes

RESTART instruction , stores the content of PC onto STACK , and places 0024H (Vector address of TRAP

instruction) onto PC.

Interrupt Structure of 8085 Microprocessor :

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

TRAP (RST 4.5) :

Highest Priority , Non-maskable , Level and Edge triggered interrupt. The Level and Edge triggering means

TRAP must remain HIGH till it is ACKNOWLEDGED. The Level and Edge triggering avoids FALSE TRIGGERING

due to NOISE and TRANSIENTS.

Interrupt Vector Address of TRAP interrupt = 4.5 × 8 = 0024H [24H is the hexadecimal equivalent of 3610)

Two ways to reset TRAP interrupt :

By applying EXTERNAL RESET signal to MICROPROCESSOR

By giving a INTERNAL TRAP ACKNOWLEDGEMENT SIGNAL.

RST 7.5 :

Second highest priority , Maskable , Positive Edge Triggered interrupt

Interrupt Vector address of RST 7.5 interrupt : 7.5 × 8 = 003CH (3CH is the hexadecimal equivalent of 6010)

Interrupt enabled and disabled using SIM , EI(Enable Interrupt ) , DI (Disable Interrupt) instructions.

Two ways to reset RST 7.5 interrupt :

Using SIM(Set Interrupt Mask) instruction

Using INTERNALLY generated ACKNOWLEDGEMENT signal.

RST 6.5 :

Third highest priority , Maskable ,Positive Level Triggered interrupt.

Interrupt Vector address of RST 6.5 interrupt : 6.5 × 8 = 0034H (34H is the hexadecimal equivalent of 5210)

Interrupt enabled and disabled using SIM , EI(Enable Interrupt ) , DI (Disable Interrupt) instructions.

RST 5.5 :

Fourth highest priority , Maskable , Positive Level Triggered Interrupt

Interrupt Vector address of RST 5.5 interrupt : 5.5 × 8 = 002CH (2CH is the hexadecimal equivalent of 4510)

Interrupt enabled and disabled using SIM , EI(Enable Interrupt ) , DI (Disable Interrupt) instructions.

INTR :

Fifth(Lowest) priority , Maskable , Positive Level Triggered Interrupt

No Vector Address Available ; Vector Address to be provided by Intel 8259 (Programmable Interrupt

Controller)

Interrupt enabled and disabled using SIM , EI(Enable Interrupt ) , DI (Disable Interrupt) instructions.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

Fig.External Logic That gives RST 7 instruction opcode.

There are 8 software interrupts namely RST 0 to RST 7 , where 0 to 7 are called INTERRUPT NUMBERS. The

vector address for the respective interrupts are found by multiplying the corresponding INTERRUPT numbers by

8.

Eg. Interrupt Vector Address for RST 5 : 5 × 8 = 0028H (28H is the hexadecimal equivalent of 4010)

I/O Data Transfer Schemes :

(i) Program Controlled I/O (or) Programmed I/O (or) Polling Control :

Data transfer between a microprocessor or microcontroller and I/O port only when I/O transfer instructions

are executed.

The Microprocessor or Microcontroller checks the status bit of the I/O device to check its readiness before

initiating data transfer. This process is called POLLING.

Example : Communication between INTEL 8279 (Programmable Keyboard and Display Controller) and

INTEL 8085 microprocessor or INTEL 8051 microcontroller.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

(ii) Interrupt Program Controlled I/O (or) Interrupt Driven I/O :

The peripheral wanting to send a data to the microprocessor or microcontroller sends an interrupt request.

On receiving the request , the microprocessor or microcontroller completes its current execution and

transfers the program control to the ISR of the corresponding requesting device.

The ISR performs the data transfer to the microprocessor or microcontroller and then returns back to its

main program at the point it was interrupted.

Example : Communication between INTEL 8259 (Programmable Interrupt Controller) and INTEL 8085

microprocessor or INTEL 8051 microcontroller

Hardware Controlled I/O (or) Direct Memory Access [DMA]:

The DMA Controller sends a HOLD signal to the microprocessor or Microcontroller to initiate the data

transfer.

In response to the HOLD signal , the microprocessor or microcontroller sends an acknowledgement signal to

DMA controller and releases its address bus , data bus and control bus which is then held by DMA controller.

The DMA controller transfers the data at high speed to the microprocessor’s or microcontroller’s RAM.

After the data transfer is completed , the DMA Controller gives back the address bus , data bus and control

bus to the microprocessor or microcontroller.

Example : Communication between INTEL 8237/8257 (Programmable DMA Controller) and INTEL 8085

microprocessor or INTEL 8051 microcontroller.

I/O Control by Handshake signals :

In this type , HANDSHAKE signals are used by microprocessor or microcontroller for checking the readiness

of the device with which it is communicating and also synchronize the timing of data transfer.

Handshaking is the process of exchange of specific characters between sending and receiving device to get

ready with necessary settings for their communication to take place.

Example : Communication between INTEL 8251(Programmable USART)(or) INTEL 8255(Programmable

Peripheral Interface) and INTEL 8085 microprocessor or INTEL 8051 microcontroller.

I/O Control by Ready Signal :

This type of Data transfer takes place between a slower I/O device and a microprocessor and

microcontroller.

The microprocessor or microcontroller checks the readiness of the device with which it is communicating by

polling its READY pin. If READY pin of microprocessor or microcontroller is activated , it means the peripheral

port is ready for communication. If Ready pin is not activated the microprocessor or microcontroller

generates WAIT STATES for the peripheral port to get ready for communication.

Example : Communication between INTEL 8218/8219 (Programmable Bus Controller) and INTEL 8085

microprocessor or INTEL 8051 microcontroller.

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

Memory Organization of 8085 Microprocessor :

Concept of Memory Interfacing :

8085 Microprocessor contains 16-bit address bus . So it can access upto 216 = 64 KB of memory location. But

the amount of memory to be used by 8085 microprocessor depends on application.

EPROM (s) are used as PROGRAM or CODE MEMORY and RAM(s) are used as DATA MEMORY. When EPROM

and RAM is used , TOTAL MEMORY SPACE IS SHARED BETWEEN THEM.

EPROM should be located from 0000H since reset address of PC is 0000H.

The main requirements for memory interfacing : (i) Select Chip (ii) Identify Register [memory location] (iii)

Enable appropriate buffer.

In order to communicate with memory , it is necessary to decode the address from the microprocessor. There

are two types of memory decoding techniques : (i) Absolute or Full Decoding (ii) Linear or Partial Decoding.

In Absolute or Full Decoding technique , all the HIGHER ORDER ADDRESS LINES are decoded to select the

memory chip and for that purpose , appropriate logic levels must be present in the address lines. This

ADDRESSING TECHNIQUE IS USED IN LARGE MEMORY BASED MICROPROCESSOR SYSTEMS.

In Linear or Partial Decoding technique , only ONE OF THE HIGHER ORDER ADDRESS LINES are used to select

the memory chip and for that purpose , the address line is connected to individual CHIP SELECT pins through

NOT gate. This ADDRESSING TECHNIQUE IS USED IN SMALL MEMORY BASED MICROPROCESSOR SYSTEMS.

The main advantage of this technique is REDUCED COST and main disadvantage of this technique is MULTIPLE

OR SHADOW ADDRESSES ARE FORMED.

Design a microprocessor system for the 8085 microprocessor such that it should contain 16 KB EPROM

implemented using two 8 KB EPROM and a 4 KB RAM implemented using two 2 KB RAM using Absolute

decoding technique

Memory IC A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address

SA of EEPROM 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0000H

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

EA of EPROM 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1FFFH

SA of EEPROM 2 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 2000H

EA of EPROM 2 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 3FFFH

SA of RAM 1 0 1 0 X X 0 0 0 0 0 0 0 0 0 0 0 4000H

EA of RAM 1 0 1 0 X X 1 1 1 1 1 1 1 1 1 1 1 47FFH

SA of RAM 2 0 1 1 X X 0 0 0 0 0 0 0 0 0 0 0 6000H

EA of RAM 2 0 1 1 X X 1 1 1 1 1 1 1 1 1 1 1 67FFH

Design memory system for the 8085 microprocessor such that it should contain 1 KB EEPROM and 1KB RAM

using Linear Decoding or Partial Decoding.

A1 A A A A A A A A A A

Memory IC A15 A14 A13 A12 A11 Address

0 9 8 7 6 5 4 3 2 1 0

SA of EEPROM

0 X X X X X 0 0 0 0 0 0 0 0 0 0 0000H

EA of EPROM 0 X X X X X 1 1 1 1 1 1 1 1 1 1 3FFFH

SA of RAM 1 X X X X X 0 0 0 0 0 0 0 0 0 0 8000H

EA of RAM 1 X X X X X 1 1 1 1 1 1 1 1 1 1 83FFH

SA – Starting Address EA – Ending Address

Prepared by Mr.S.Sayeekumar , AP/ EEE , RMD ENGINEERING COLLEGE

Potrebbero piacerti anche

- EE309 MP Mod1 Ktunotes - inDocumento17 pagineEE309 MP Mod1 Ktunotes - inDivya KrishnanNessuna valutazione finora

- 8085 Architecture & Pin DescriptionFileDocumento19 pagine8085 Architecture & Pin DescriptionFileKaseya TakahashiNessuna valutazione finora

- MicroprocessorDocumento29 pagineMicroprocessorArnab RayNessuna valutazione finora

- EE6502 MPMC Two Marks With AnswerDocumento10 pagineEE6502 MPMC Two Marks With Answervlsimani9110100% (1)

- Unit I PDFDocumento25 pagineUnit I PDFSomnath2014Nessuna valutazione finora

- Intro To 8085Documento23 pagineIntro To 8085Vivek KumarNessuna valutazione finora

- Microprocessor NotesDocumento60 pagineMicroprocessor NotesVijay KumarNessuna valutazione finora

- Intel 8085 Microprocessor Architecture GuideDocumento18 pagineIntel 8085 Microprocessor Architecture GuideGautamNessuna valutazione finora

- Chapter 1.1-8085 Architecture-IntroductionDocumento34 pagineChapter 1.1-8085 Architecture-IntroductionBulbula Kumeda100% (1)

- 8085 Pin Diagram and ArchitectureDocumento8 pagine8085 Pin Diagram and ArchitectureSneha SinghNessuna valutazione finora

- EE8551-Mpmc Two MarksDocumento23 pagineEE8551-Mpmc Two MarksmenakadevieceNessuna valutazione finora

- Lecture1423722820 PDFDocumento101 pagineLecture1423722820 PDFdavNessuna valutazione finora

- Unit-1 (1) Draw and Explain The Internal Architecture of 8085Documento11 pagineUnit-1 (1) Draw and Explain The Internal Architecture of 8085Mann MehtaNessuna valutazione finora

- 8085 Features, Signal DescriptionDocumento13 pagine8085 Features, Signal DescriptionRakesh Kumar DNessuna valutazione finora

- Microprocessor and Micro ControllerDocumento118 pagineMicroprocessor and Micro ControllerShiva ShanNessuna valutazione finora

- 8085 Microprocessor Architecture, Pin DiagramDocumento10 pagine8085 Microprocessor Architecture, Pin DiagramSachin Jaysenan0% (1)

- Programming 8085 Microprocessor ArchitectureDocumento34 pagineProgramming 8085 Microprocessor ArchitectureAbhinandan JainNessuna valutazione finora

- M4 Yash AllabadiDocumento6 pagineM4 Yash Allabadidegijon661Nessuna valutazione finora

- Poriyaan 1cmfA62QmpEUSssZeK 4a3Lq-KUrzO1jADocumento171 paginePoriyaan 1cmfA62QmpEUSssZeK 4a3Lq-KUrzO1jAS. GobikaNessuna valutazione finora

- 3-Ee8551-Microprocessors and MicrocontrollersDocumento109 pagine3-Ee8551-Microprocessors and MicrocontrollersKeerthana SahadevanNessuna valutazione finora

- Intel 8085 Microprocessor Architecture GuideDocumento6 pagineIntel 8085 Microprocessor Architecture GuideDipesh YadavNessuna valutazione finora

- Model exam answer key for 8085 microprocessorDocumento21 pagineModel exam answer key for 8085 microprocessorVenkatesan SundaramNessuna valutazione finora

- Microprocessor 8085 NotesDocumento48 pagineMicroprocessor 8085 NotesDewal ChaturvediNessuna valutazione finora

- 8085 Microprocessor - Functional Units: AccumulatorDocumento5 pagine8085 Microprocessor - Functional Units: AccumulatorDeep KambleNessuna valutazione finora

- Ee8551 8085 NotesDocumento31 pagineEe8551 8085 NotesKUMARANSCRNessuna valutazione finora

- Syllabus: 8085 ArchitectureDocumento25 pagineSyllabus: 8085 Architecturetamilvendhan87Nessuna valutazione finora

- An Over View of 8085Documento12 pagineAn Over View of 8085nskprasad89Nessuna valutazione finora

- 8085 MicroprocessorDocumento25 pagine8085 Microprocessorprofessor2062Nessuna valutazione finora

- Microprocessor - 8085 Internal ArchitectureDocumento25 pagineMicroprocessor - 8085 Internal ArchitectureTanveer Ahmed HakroNessuna valutazione finora

- Lec 1-2-8085 ArchitectureDocumento34 pagineLec 1-2-8085 ArchitectureHazrat Haad Muhammad Shaukat Ali KhanNessuna valutazione finora

- 8051 Microcontroller Architecture and Features in 40 CharactersDocumento7 pagine8051 Microcontroller Architecture and Features in 40 Characterssabin3sNessuna valutazione finora

- Microprocessor and Micro Controller Lecture NotesDocumento118 pagineMicroprocessor and Micro Controller Lecture NotesSivanesh SK50% (2)

- MPI GTU Study Material E-Notes Unit-7 13052022115255AMDocumento13 pagineMPI GTU Study Material E-Notes Unit-7 13052022115255AMHarsh ShahNessuna valutazione finora

- 8-bit Microprocessor 8085 Features and ArchitectureDocumento29 pagine8-bit Microprocessor 8085 Features and ArchitectureAnif Ilham IsmailNessuna valutazione finora

- MPMC NotesDocumento301 pagineMPMC NotesVarinder KumarNessuna valutazione finora

- Intel 8085 ArchitectureDocumento8 pagineIntel 8085 ArchitectureAravind VJNessuna valutazione finora

- Introduction To Microprocessor 8085Documento23 pagineIntroduction To Microprocessor 8085GousAttarNessuna valutazione finora

- BGK MPMC Unit-3 Q and ADocumento21 pagineBGK MPMC Unit-3 Q and AMallesh ArjaNessuna valutazione finora

- Programming With 8085 MicroprocessorDocumento33 pagineProgramming With 8085 MicroprocessorBlackk SpydoNessuna valutazione finora

- MPI (Slides 8085 Microprocessor)Documento20 pagineMPI (Slides 8085 Microprocessor)Rosh_MiNessuna valutazione finora

- Architecture and Instruction Set of the 8-bit Microprocessor 8085Documento80 pagineArchitecture and Instruction Set of the 8-bit Microprocessor 8085vsalaiselvamNessuna valutazione finora

- Microprocessor 8-bit TitleDocumento55 pagineMicroprocessor 8-bit TitleAASTHA KIETNessuna valutazione finora

- MPMC Eee Unit - I 8085 ProcessorDocumento35 pagineMPMC Eee Unit - I 8085 ProcessorAnonymous zaMNkL100% (1)

- 8085 Microprocessor Signal GroupsDocumento27 pagine8085 Microprocessor Signal GroupsSheena Ann StonehillNessuna valutazione finora

- Unit IIIDocumento50 pagineUnit IIISamuel KuantumNessuna valutazione finora

- 8085 MaterialDocumento12 pagine8085 MaterialsameerNessuna valutazione finora

- Svcet: Sri Vidya College of Engineering & Technology Course Material (Question Bank)Documento4 pagineSvcet: Sri Vidya College of Engineering & Technology Course Material (Question Bank)Balaprakash VadivelNessuna valutazione finora

- MPMC Note DWNLDDDocumento18 pagineMPMC Note DWNLDDArya TJNessuna valutazione finora

- BCA VI Sem Microprocessor & Assembly Language ProgrammingDocumento24 pagineBCA VI Sem Microprocessor & Assembly Language ProgrammingRkf LanesraNessuna valutazione finora

- L4 - 8085 ArchitectureDocumento24 pagineL4 - 8085 ArchitectureHabirah Mahmood MutanganaNessuna valutazione finora

- Cs2 Practical PDFDocumento62 pagineCs2 Practical PDFMaitri ShahNessuna valutazione finora

- 8085 Microprocessor Architecture and Programming-1Documento92 pagine8085 Microprocessor Architecture and Programming-1ShubhamNessuna valutazione finora

- Basic Concepts of MicroprocessorsDocumento32 pagineBasic Concepts of MicroprocessorsAakrati SharmaNessuna valutazione finora

- COA LAb File-ShubhiDocumento28 pagineCOA LAb File-ShubhiKrishan Kant ShuklaNessuna valutazione finora

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Da EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Nessuna valutazione finora

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDa EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNessuna valutazione finora

- Features of 8085 microprocessor and comparison with 8086Documento7 pagineFeatures of 8085 microprocessor and comparison with 8086CsNessuna valutazione finora

- 498 PDFDocumento35 pagine498 PDFHassan AllawiNessuna valutazione finora

- Pin Diagram of 8085.PDF ImpDocumento48 paginePin Diagram of 8085.PDF ImpKRISHNAVINOD100% (1)

- Post Name: Data Entry Operator (Contractual) Post Name: Data Entry Operator (Contractual) Post Name: Data Entry Operator (Contractual)Documento27 paginePost Name: Data Entry Operator (Contractual) Post Name: Data Entry Operator (Contractual) Post Name: Data Entry Operator (Contractual)CsNessuna valutazione finora

- What Is Normalization Why Is It Important How Do You Normalize OnlyDocumento1 paginaWhat Is Normalization Why Is It Important How Do You Normalize OnlyCsNessuna valutazione finora

- Microprocessorlabmanual EE0310Documento87 pagineMicroprocessorlabmanual EE0310dhilipkumarNessuna valutazione finora

- LNM 1Documento42 pagineLNM 1KANHIYA78100% (1)

- 8085 Microprocessor Ramesh S. GaonkarDocumento330 pagine8085 Microprocessor Ramesh S. Gaonkarrohit31bark64% (22)

- Jeca Zones 2k19Documento1 paginaJeca Zones 2k19CsNessuna valutazione finora

- ScribdtestlolDocumento2 pagineScribdtestlolCsNessuna valutazione finora

- Scribd Test Lol and Where Test Download LolollolDocumento1 paginaScribd Test Lol and Where Test Download LolollolCsNessuna valutazione finora

- File PDFDocumento1 paginaFile PDFCsNessuna valutazione finora

- Authentication Verification Letter For Portal 1Documento2 pagineAuthentication Verification Letter For Portal 1pradeepajadhavNessuna valutazione finora

- Task 7 CompleteDocumento1 paginaTask 7 Completeapi-335293732Nessuna valutazione finora

- SPE 00 301120 40mah en 1.0verDocumento10 pagineSPE 00 301120 40mah en 1.0verAndreea FilipNessuna valutazione finora

- BS WaterDocumento0 pagineBS WaterAfrica OdaraNessuna valutazione finora

- DLL Q4 Week 9Documento69 pagineDLL Q4 Week 9Aiza ConchadaNessuna valutazione finora

- Autel Maxisys Citroen v4.10 Coverage TableDocumento58 pagineAutel Maxisys Citroen v4.10 Coverage TableBeto HoffmannNessuna valutazione finora

- A&E Price List - EditedDocumento5 pagineA&E Price List - EditedMostafa MohamedNessuna valutazione finora

- Dairy Farm Group Case StudyDocumento5 pagineDairy Farm Group Case Studybinzidd007Nessuna valutazione finora

- Aerodynamic Interactions Explain Tacoma Narrows Bridge FailureDocumento11 pagineAerodynamic Interactions Explain Tacoma Narrows Bridge FailureglowingbrakesNessuna valutazione finora

- Project Final ReportDocumento80 pagineProject Final ReportVirendra Sonawane0% (1)

- Yodlee CrossSell Case StudyDocumento4 pagineYodlee CrossSell Case StudylocalonNessuna valutazione finora

- 02 CNC Lab Manual NIT APDocumento3 pagine02 CNC Lab Manual NIT APDevesh RehanNessuna valutazione finora

- BDocumento136 pagineBJuan Manuel Ugalde FrancoNessuna valutazione finora

- Consultants New Rates GR Dated 09.05.2019Documento11 pagineConsultants New Rates GR Dated 09.05.2019Shakti SinghNessuna valutazione finora

- Java Important Questions SetDocumento64 pagineJava Important Questions SetChairil Aditya NurfadlilahNessuna valutazione finora

- LOW POWER SOLUTIONSDocumento48 pagineLOW POWER SOLUTIONSDavidNessuna valutazione finora

- Performance of Fiber ReinforcedDocumento16 paginePerformance of Fiber ReinforcedBang BangNessuna valutazione finora

- Drilling Industry Glossary TermsDocumento25 pagineDrilling Industry Glossary Termsahoua100% (1)

- Trawler SampleDocumento80 pagineTrawler SampleChet Stephens100% (2)

- Constable: Punjab PoliceDocumento2 pagineConstable: Punjab PoliceAbid SaeedNessuna valutazione finora

- Essbase Studio User's Guide 11.1.2.3Documento406 pagineEssbase Studio User's Guide 11.1.2.3suchaiNessuna valutazione finora

- Japanese Construction Firms enDocumento4 pagineJapanese Construction Firms enLanang Ardi ParinggaNessuna valutazione finora

- Infosys CaseDocumento7 pagineInfosys CasenikeesinghNessuna valutazione finora

- CamScanner Scanned DocumentDocumento1.284 pagineCamScanner Scanned DocumentGeorgeanne 25100% (1)

- Planta Electrica Control MedicionDocumento51 paginePlanta Electrica Control MedicionjorgevchNessuna valutazione finora

- Advantages of JeepneyDocumento3 pagineAdvantages of JeepneyCarl James L. MatrizNessuna valutazione finora

- Richard Bandler's Guide to Harnessing HypnosisDocumento3 pagineRichard Bandler's Guide to Harnessing HypnosisChristy Mayo0% (1)

- Minds, Brains, and Computers PDFDocumento8 pagineMinds, Brains, and Computers PDFJorge de La BarreNessuna valutazione finora

- Understanding Otdr Understanding-otdr-po-fop-tm-aePo Fop TM AeDocumento1 paginaUnderstanding Otdr Understanding-otdr-po-fop-tm-aePo Fop TM AeAgus RiyadiNessuna valutazione finora

- KhkghkjghkjghohoiDocumento9 pagineKhkghkjghkjghohoiY a n i. A h m e dNessuna valutazione finora