Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Automatic Power Factor Detection and Cor

Caricato da

AshritaCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Automatic Power Factor Detection and Cor

Caricato da

AshritaCopyright:

Formati disponibili

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

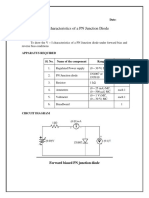

EXPERIMENT NO:1

SEMICONDUCTOR PN JUNCTION DIODES

CHARACTERISTICS

AIM: i. To plot the V–I characteristics of a Semiconductor PN – Junction diode.

ii. To find the following parameters from the Forward & Reverse characteristics.

a) Cut in voltage-V

b) Static forward resistance RF at If=20mA

c) Reverse saturation current-Ico

d) Dynamic forward resistance-rf

e) Dynamic reverse resistance-Rr

APPARATUS:

i. Diode(Ge-DR25 / Si-1N4148), Resistors 180Ω/5W & 10KΩ .

ii. D.C Regulated Power Supply (0-30V)

iii. Digital multimeter (0-1V)

iv. Ammeter (0-50mA) (0-100µA)

v. Bread board, Single stand wires

CIRCUIT DIAGRAM:

Fig.1

Fig.1: Circuit arrangement for the study of the Forward characteristics of a Diode.

Theory :

Under forward bias configuration the positive terminal of the battery is connected to P-side and

negative terminal of the battery is connected to N-side as shown in the figure above large amount of the

current flows through the junction under this condition.

When P-N junction is forward biased, the holes are repelled from the positive electrode and the

electrons from the negative electrode of the power supply, and are forced to move towards the junction.

Some of the holes and electrons in the depletion region recombine themselves. This

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

reduces the width of the depletion layer and the height of the potential barrier. As a result of this

more number of majority charge carriers flow through the P-N junction.

PROCEDURE:

i. Ensure that D.C Power supply is switched OFF. Keep the voltage control knob in the

minimum position and current control knob in maximum position.

ii. Connect the circuit as shown in Fig –1 for forward characteristics making use of silicon diode.

iii. Vary the power supply voltage such that the voltage across the diode is varied 0-1V in

steps of 0.1 volts .Note down Vf and If in the table.

iv. Draw the Vf Vs If characteristics and find out the cut – in voltage Vr for diode from it.

Ensure that the current through the diode does not exceed 50mA.

v. Repeat the experiment using germanium diode.

vi. Present the results at the end of the experiment.

vii. Estimate the forward resistance of the diode from the relation = [Δ V f / Δ If ]

CIRCUIT DIAGRAM:

Fig.2:Circuit arrangement for the study of the Reverse characteristics of a Diode.

Theory :

In the reverse bias positive electrode of the battery is connected to N-side and the negative

electrode to P-side. When a P-N junction is reverse biased, the holes in the P region are attracted

towards the negative electrode of the battery and the electrons in the N region are attracted

towards the positive electrode.

Thus the majority carriers are drawn away from the junction. This widens the depletion

layer and increases the height of the potential barrier. Hence there is no current flow due to

majority carriers under reverse bias. A small amount of current due to diffusion of minority charge

carriers across the junction flows through the reversed biased PN junction. Generation of the

minority carriers is dependent upon the ambient temperature and is independent of the applied

reverse voltage, as can be seen from the

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

PROCEDURE :

i. Connect the circuit as shown in Fig-2 for reverse bias characteristics making use of a

silicon diode

ii. Vary the voltage across the diode from 0-20 volts in steps of 1V and record the reverse

saturation current in µA.

iii. Draw the reverse characteristics Vr, Ir .

iv. Find out the reverse saturation current Ir. Estimate the reverse resistance Rr from the

characteristic curve from the relation Rr = [Δ Vr / Δ Ir]

v. Repeat the experiment using germanium diode.

vi. Present the results at the end of the experiment.

OBSERVATIONS:

Forward Characteristics Reverse Characteristics

TABLE - I TABLE-II

S. S. No

No Vf (Volts) If (mA) Vr (Volts) Ir ( µA)

0.0 0

0.1 2

0.2 3

0.3 -

- -

- -

- -

- -

1.0 20.0

MODEL GRAPHS:

Forward and Reverse Characteristic curves :

Fig.3: Forward and Reverse characteristics of a Diode

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULTS:

The parameters of the Silicon and Germanium diodes are estimated from the static forward and

reverse characteristics and are presented below.

Experimentally observed Parameters Silicon Germanium

Cut-in voltage –V V V

RF Ohms Ohms

Rr K.Ω K.Ω

DISCUSSIONS:

1. What are the cut-in voltages for the two diodes used ? Give reasons why they are different?

2. What is meant by forward and reverse bias ?

3. Name the applications of the diodes.

4. What is meant by depletion layer or intrinsic / Space charge region

5. What is meant by recombination?

6. Write examples of N type & P type materials?

7. What is reverse Saturation Current?

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO : 2

ZENER DIODE CHARACTERISTICS

AIM : To Plot the V–I Characteristics of a Zener Diode

APPARATUS :

i. Zener Diode 8Z2V, Resistor 180Ω /5W.

ii. Regulated Power Supply ( 0-30V).

iii. Ammeters (0 - 50mA) – 3 No.s

iv. Decade Resistance Box, Bread board, Single stand wires.

v. Voltmeter (0-20V).

CIRCUIT DIAGRAM :

Fig.2 Circuit arrangement for the study of the characteristics of a Zener Diode under

Reverse Bias

Theory:

The Zener diode is a Silicon PN junction device. It is operated in the reverse

breakdown region. When a reverse voltage across a diode is increased a critical voltage called a

breakdown voltage is reached at which the reverse current increases rapidly. The reverse

breakdown of a PN junction may occur either due to Avalanche breakdown effect or Zener

breakdown effect or both.

PROCEDURE:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

i. Connect the circuit as per the Diagram shown in Fig –2

ii. Ensure that the power supply is switched OFF. Keep the voltage control knob in the

minimum position and current control knob in maximum position.

iii. Vary the power supply such that the increment in the input voltage, V i is 2V. Record the

corresponding values of Vz voltage across the Zener Diode and Iz current through the

Zener as shown in Table-I. Do not exceed the Zener current Iz more than the 50 mA.

iv. Plot V – I characteristics of Zener diode in reverse bias region as shown in Fig.3

identify the Zener break down voltage Vz.

v. Calculate the resistance of the Zener diode in the linear part of the breakdown region

with the help of the formula Rz = [Δ Vz / Δ Iz ]

vi. Present the results at the end of the experiment.

OBSERVATIONS:

Table-I: V- I characteristics of Zener diode Under Reverse Bias

SUPPLY VOLTAGE VOLTAGE ACROSS CURRENT THROUGH

S NO Vi (Volts) ZENER ZENER Iz(mA)

Vz (Volts)

0

1

2

.

.

.

.

20

EXPECTED GRAPH:

Fig .3

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULTS:

i. Zener breakdown voltage V br =

ii. Zener resistance in the breakdown region Rz =

DISCUSSIONS:

i. Name the applications of Zener diodes?

ii. Explain Zener effect and avalanche effect?

iii. Why Zener diode characteristics are taken in reverse bias?

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

ZENER VOLTAGE REGULATOR

AIM: i. To study the load current regulation and

ii. Input voltage regulation of a Zener Voltage Regulator.

APPARATUS:

i. Resistors -180Ώ / 5W, Zener Diode 8Z2V .

ii. Regulated Power supply (0-30V / 1Amp) – 1No.

iii. Voltmeters (0-30V) – 1No, Ammeters (0-50mA) – 3No.s

iv. Decade Resistance Box (DRB) as RL – 1No.

V. Bread board, Single stand wires.

CIRCUIT DIAGRAM:

Fig.1:Circuit arrangement for Zener Voltage Regulator

Theory:

Zener diode is used as a Voltage Regulator. The source voltage Vi and resistor Rs are

selected so that initially the diode is operating in the breakdown region. Here the diode voltage,

which is also the voltage across the load RL is VZ and the diode current is IZ. The diode will now

regulate the load voltage against variations in load currents and against variations in supply voltage

Vi because in the breakdown region large changes in diode current produce only small changes in

diode voltage. Moreover, it maintains a constant voltage across its terminals over a specified range

of Zener current values.

PROCEDURE:[For Load Current Regulation]:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

i. Connect the circuit as per the Diagram shown in Fig – 1.

ii. Ensure that the power supply is switched OFF. Keep the voltage control knob in the minimum

position and current control knob in maximum position.

iii. Adjust the input voltage Vi such that it is greater than the Zener breakdown voltage by about

10Volts and fix the same.

iv. Open the load resistance circuit and note the no-load voltage VnL corresponding to IL= 0

(zero load current)

v. Now connect RL (DRB) as shown in circuit diagram then vary it such that load current IL

increases from minimum to a maximum of 50 mA in steps of about 5 mA. Note down the

output voltage, Load current and Zener current, Vo, IL, Iz record them as shown in Table-I.

vi. Draw the Graph between IL and VL. Calculate the % Regulation with the help of the following

relation. % Regulation =[ (VnL – VL) / VnL ] x 100 ---------------------- (I)

vii. Draw the graph between IL and % regulation.

OBSERVATIONS:

(a). Load Current Regulation

At No load voltage Vnl measured at IL=0

Table-I

Load Current Zener Current Total Current Load Voltage %

S NO IL(mA) Iz(mA) IT(mA) VL (volts) Regulation

0 0 0 0 0

5

10

-

-

-

-

-

50

MODEL GRAPHS:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULT:

DISCUSSIONS:

i. What is meant by load current regulation.

% of load regulation = {(V no load – V load) / V no load } x 100

at constant in put voltage.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO: 3

(A)HALF – WAVE RECTIFIER

AIM: a) To connect a Half - Wave rectifier.

b) To measure D.C. and ripple voltages for different filter configurations.

c) To observe the out put wave forms using a CRO and

d) To study the load characteristics of the rectifier without any filter and with

C, L and section filters.

APPARATUS:

i. Circuit board.

ii. Ammeter (0-100mA)

iii. Voltmeter (0-30V)

iv. Patch cords.

v. Cathode ray Oscilloscope.

CIRCUIT DIAGRAM:

Fig.1:Circuit arrangement for half wave Rectifier

PROCEDURE:

1. Connect the circuit diagram as shown in figure.

2. Note down the secondary transformer voltage with AC digital voltmeter.

3. To study the performance of the Half- wave rectifier without any filter and with different

filters.

a) Record the observations in the following table by noting down the V dc and Vac corresponding to

different Idc load currents. First note down the No-load voltage Vdc and Vac corresponding to

Idc=0. Then increase the load current insteps of 5mA up to a maximum of 50 mA by varying the

load resistance Rl. At each value of Idc note down the corresponding value theVdc, Vrms (RMS

value of ripple out put voltage) and out put wave forms.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

*Note -Vdc corresponding to Idc=0 will be the no-load voltage = Vnl.

Plot the graphs

a) Idc vs Vdc

b) Calculate the % of regulation at different load currents and Plot the graph as shown in the

diagram using the formula.

% Regulation r = {(Vnl-Vl)/Vl} x 100 | Il = constant (=25mA), Ripple factor will be zero

at Il=0(since Vnl and Vl be the same at Il=0 ).

= Iac / Idc = Vac / Vdc.

4. To study the performance of Half-wave rectifier without any filter and with different filters

repeat the experimental procedure of step 3 in corresponding to 1.Shunt capacitor filter 2.

Inductor filter. 3. L-section filter 4. - section filter.

Compare the reading of step 3 and 4 with theoretical values.

OBSERVATIONS:

TABLE.1

S Idc Vdc Vac Ripple factor %Regulation

N (mA) (volts) V(rms) RL = Vdc / Idc =Vac/Vdc r={(Vnl-Vl)/Vnl }x100

O

0

5

10

.

50

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

MODEL GRAPHS:

RESULTS:

DISCUSSIONS:

It is observed experimentally that

1. ---------- filter gives better regulation.

2. --------- filter gives better ripple factor.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO: 3

(B) FULL - WAVE RECTIFIER

AIM: a) To connect a Full - Wave rectifier.

b) To measure D.C. and ripple voltages for different filter configurations.

c) To observe the out put wave forms using a CRO and

d) To study the load characteristics of the rectifier without any filter and with C

L and section filters.

APPARATUS:

i. Circuit board.

ii. Ammeter (0-100mA)

iii. Voltmeter (0-30V)

iv. Patch cords.

v. Cathode ray Oscilloscope.

CIRCUIT DIAGRAM:

Fig.1:Circuit arrangement for Full wave Rectifier

Theory:

Any electrical device, which offers a low resistance to current in one direction but the high

resistance to the current in the opposite direction, is called rectifier. They are capable of

converting a sinusoidal input waveform into a Uni directional waveform.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

PROCEDURE:

1. Connect the circuit diagram as shown in figure.

2. Note down the secondary transformer voltage with AC digital voltmeter.

3. To study the performance of the full- wave rectifier without any filter and

with different filters.

a). Record the observations in the following table by noting down the Vdc and Vac

corresponding to different Idc load currents. First note down the No-load voltage Vdc and

Vac corresponding to Idc=0. Then increase the load current insteps of 5mA up to a maximum

of 50 mA. At each value of Idc note down the corresponding value Vdc, Vrms(RMS value of

ripple out put voltage) and out put wave forms.

Plot the graphs

a) Idc vs Vdc

b) Calculate the % of regulation at different load currents and plot the graph Il as

shown in the diagram using the formula.

% Regulation r = {(Vnl-Vl)/Vl} x 100 | Il = constant (=25mA),

which will be zero at Il=0(since Vnl and Vl be the same at Il=0 ).

= Iac / Idc = Vac / Vdc.

4. To study the performance of full-wave rectifier without any filter and with different filters

repeat the experimental procedure of step 3 in corresponding 1.Shunt capacitor filter 2. Inductor

filter. 3.L-section filter 4. - section filter.

Compare the reading of step 3 and 4 with theoretical values.

OBSERVATIONS:

TABLE :1

Idc Vdc Vac RL = Ripple %Regulation

(mA) (volts) (Vrms) Vdc / factor r={(Vnl-Vl)/Vnl

Idc =Vac/Vdc }x100

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

MODEL GRAPHS:

RESULTS:

DISCUSSIONS:

It is observed experimentally that

1. ----------- filter gives better regulation.

2. ----------- filter gives better ripple factor.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO: 4

STATIC CHARACTERISTICS OF TRANSISTOR

IN COMMON BASE CONFIGURATION

AIM: To obtain the input and output characteristics of given transistor in CB

configuration.

APPARATUS:

i. Transistor CL100, Resistors 4.7KΩ,470Ω.

ii. Ammeters (0-50mA) – 2 Nos.

iii. Voltmeters (0-1 V & 0-30 V)

iv. Bread board, Single stand wires.

v. Regulated Power Supply (0-30V).

1. INPUT CHARACTERISTICS :

CIRCUIT DIAGRAM :

Fig.1: The Circuit diagram for the study of input characteristics of a Transistor in common-base

configuration .

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

Theory:

Input characteristic curves give the relationship between the emitter current [I E]

and the emitter to base voltage[VEB] for a constant collector to base voltage [V CB]. As the

collector to base voltage (VCB) is increased above one volt, the curve shifts upwards. It occurs due

to the phenomenon called “Base width Modulation” or “Early Effect”.

PROCEDURE:

1. Connect the circuit as shown in Fig-1.

2. Ensure that the power supply is switched OFF. Keep the voltage control knob in the minimum

position and current control knob in maximum position.

3. Switch ON the power supply. Adjust Vcc such that Vcb is zero.

4. Vary IE with the help of VEE in steps( say 1mA )and record the corresponding values of VBE in

the Table-I shown below. Make sure that the collector current, Ic does not exceed 25mA.

5. This set of observations gives the input characteristics With V CB=0V.

6. Repeat steps from 1 to 4 for different values of VCB say VCB = 5V , 10V and for VCB open (This

can be done by opening one of the out put terminals.)

7. Draw the input characteristics IE Vs VEB for different values of VCB as shown In Fig.3(a).

8. Represent all the results at the end of the experiment.

OBSERVATIONS :

Table-I: Input Characteristics

VCB = 0 V VCB = 5 V VCB = 10 V VCB = OPEN

S. No.

IE(mA) VEB(V) IE(mA) VEB (V) IE(mA) VEB (V) IE(mA) VEB (V)

1. 0

2. 5

3. 10

4. 15

5. 20

6. 25

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

MODEL GRAPH:

2.OUT PUT CHARACTERISTICS:

CIRCUIT DIAGRAM:

Fig.2 : Circuit diagram for the study of output characteristics of a Transistor in common-

base configuration.

Theory:

Output characteristic curves give the relationship between the collector current(I C) and

the collector to base voltage (VCB) for a constant emitter current (IE). The curve may be divided

into three important regions namely saturation region, active region, and cut-off region.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

PROCEDURE:

1. Connect the circuit as per the circuit Diagram shown in Fig – 2.

2. Ensure that the power supply is switched OFF. Keep the voltage control knob in the

Minimum position and current control knob in maximum position.

3. Switch ON the power supply. Adjust VEE to get IE=0 mA.

4. Fix the collector to base voltage (VCB). Record the corresponding values of collector

currents, IC in the table shown below .

5. Repeat the steps from 1 to 4 for different values of IE from 1 to 10ma.( not exceed to25mA)

6. Draw the output characteristics VCB Vs IC for different values of VCB.

7. Present all the results at the end of the experiment.

OBSERVATIONS :

Table – II: Output Characteristics

IE=0mA IE=10 mA IE=20 mA IE=30 mA

S. No.

VCB (V) IC (mA) VCB(V) IC(mA) VCB(V) IC(mA) VCB(V) IC(mA)

1. 0

2. .

3. .

4. .

5. .

- .

- 10

MODEL GRAPH :

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULTS:

The input and output characteristics are drawn are shown in Fig.3(a)and Fig.3(b) and the

following hybrid parameters are estimated from the graphs.

1.hib = [ VEB IE] = at VCB = constant.

2.hrb = [ VEB / VCB] = at IE = constant.

Are computed from the input characteristics

3. hob = [ Ic / VCB]= at IE = constant.

4. hfb = [ Ic / IE] = _______at VCB = constant.

Are computed from the output characteristics

DISCUSSIONS :

i. Indicate the various regions, (Active region, Saturation region and cut off region) on the

Out put characteristics of the transistor and discuss them.

ii. What does early effect or Base width modulation means?

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO: 5

STATIC CHARACTERISTICS OF TRANSISTOR

IN COMMON EMITTER CONFIGURATION

AIM: To obtain the input and output characteristics of given transistor in CE

configuration.

APPARATUS:

i. Transistor CL100,Resistors 47KΩ, 1KΩ

ii. Ammeters (0-50mA) – 2 Nos.

iii. Voltmeters (0-1 V, 0-30 V)

iv. Bread board, Single stand wires.

v. Regulated Power Supply (0-30V).

INPUT CHARACTERISTICS:

CIRCUIT DIAGRAM:

Fig.1: Circuit diagram for the study of input characteristics of a Transistor in common-

Emitter configuration.

Theory: These curves give the relationship between the base current (I B) and the base to

emitter voltage (VBE) for a constant collector to emitter voltage (V CE). As the collector to emitter

voltage is increased above 1V, the curves shifts downwards because as V CE is increased, the

depletion width in the base region increases and this reduces the effective base width, which in

turn reduces the base current.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

PROCEDURE:

i. Connect the circuit as shown in Fig-1.

ii. Ensure that the power supply is switched OFF. Keep the voltage control knob in the minimum

Position and current control knob in maximum position.

iii. Switch ON the power supply. Adjust VCC such that VCE=0V (this can also be done by switching

OFF the Vcc supply and shorting the two outputs leads. Vary I B with the help of VBB in steps of

10µA and record the corresponding values of V BE in the Table –I shown below and record the

corresponding values of V BE (base to emitter voltage).

iv. Make sure that the collector current Ic does not exceed 25mA. This set of readings gives

the input characteristics of VCE=0V.

v. Repeat steps (1-4) for different values of VCE say VCE =0.1 v, 0.2V, 0.3V, 1V.

vi. Draw input characteristic IB Vs VBE for different values of VCE.

vii. Estimate h-parameters from the characteristic curves.

viii. Present all the results at the end of the experiment.

OBSERVATIONS:

Table – I: Input Characteristics

VCE= 0V VCE= 0.1V VCE= 0.2V VCE= 0.3V VCE= 1V

SNO

IB VEB IB VEB IB VEB IB VEB IB VEB

( (V) (µAmp (V) (µAmp) (V) (µAmp) (V) (µAmp) (V)

Amp) )

1. 5 5 5 5 5

2. 10 10 10 10 10

3. 20 20 20 20 20

4. 30 30 30 30 30

5. 40 40 40 40 40

6. 50 50 50 50 50

7. 60 60 60 60 60

8. 70 70 70 70 70

9. 80 80 80 80 80

10. 90 90 90 90 90

11. 100 100 100 100 100

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

MODEL GRAPH(Input Characteristics):

Fig: input characteristics of transistor in CE configuration.

2. OUTPUT CHARACTERISTICS:

CIRCUIT DIAGRAM:

Fig.2 Circuit diagram for the study of output characteristics of a Transistor in common-Emitter

configuration

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

Theory:

Output characteristic gives the relationship between the collector to emitter voltage (V CE)

and collector current(IC) for a constant base current (IB).

The curves may be divided into three important regions namely Saturation region Active

region and Cut-off region.

PROCEDURE:

i. Connect the circuit as per the Diagram shown in Fig – 2

ii. Ensure that the power supply is switched OFF. Keep the voltage control knob in the minimum

position and current control knob in maximum position. Switch ON the power supply .

iii. With the help of power supply VEE make the input current IB=10A. Vary collector to emitter

voltage (VCE) in suitable steps of 0.1 volts starting from 0 volts. Record the corresponding

values of collector currents IC, in the Table-II. This set of readings gives the output

characteristics for IB=10A.

iv. Repeat step iii for different values of base current say Ib=10A-100A in steps of 10A.

v. Draw the output characteristic Vce vs IC.

vi.. Estimate h-parameters from the characteristics curve.

vii. Present all the results at the end of the experiment.

OBSERVATIONS:

Table-II: Output Characteristics

S.No. IB=20µAmp IB=40 µAmp IB=60 µAmp IB=80 µAmp

VCE(Volts) IC(mA) VCE(Volts) IC(mA) VCE(Volts) IC(mA) VCE(Volts) IC(mA)

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

MODEL GRAPH:

Output Characteristics

RESULTS:

The input and output characteristics are drawn are shown in Fig.3(a)and Fig.3(b) and the

following hybrid parameters are estimated from the graphs.

1. hie= VBE Ib atVCE= constant.

2. hre= VBE/ VCE at Ib= constant.

Are computed from the input characteristics

3.hoe= Ic / VCE atIB=constant.

4.hfe= Ic / Ib at VCE= constant

Are computed from the output characteristics

DISCUSSIONS:

i. Indicate the various regions, (Active region, Saturation region and cut off region) on

the out put characteristics of the transistor.

ii. Estimate Ic and Vce from the circuit shown

iii. What are the differences between common emitter and common base input and out

put characteristics?

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO: 6

STATIC CHARACTERISTICS OF TRANSISTOR

IN COMMON COLLECTOR CONFIGURATION

AIM: To obtain the input and output characteristics of given transistor in CC

configuration.

APPARATUS:

i. Transistor CL100, Resistors47KΩ,1KΩ,500Ω.

ii. Ammeters (0-50mA) – 2 Nos.

iii. Voltmeters (0-1 V, 0-30 V)

iv. Bread board, Single stand wires.

v. Regulated Power Supply (0-30V).

1.INPUT CHARACTERISTICS :

CIRCUIT DIAGRAM :

Fig.1 Circuit diagram for the study of input characteristics of a Transistor in common-

collector configuration .

Theory:

Input characteristic curves give the relationship between the base current (IB) and

the base to collector voltage (VBC) for a constant collector to base voltage (VEC)

PROCEDURE:

i. Connect the circuit as shown in Fig-1.

ii. Ensure that the power supply is switched OFF. Keep the voltage control knob in the

minimum position and current control knob in maximum position.

iii. Switch ON the power supply. Adjust VEC =2V

iv. Vary IB with the help of VBB in steps of 10µA and record the corresponding values of VBC

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

in the Table –I. Make sure that the collector current IC does not exceed 25mA.

v. Repeat steps from i to iv for different values of VEC say VEC =5V, 10V and for VBC open

(This can be done by opening one of the output terminals).

vi. Draw the input characteristics IB verses VBC for different values of VEC in Fig.3(a).

vii. Estimate h-parameters from the characteristics curve.

viii. Present all the results at the end of the experiment.

OBSERVATIONS:

Table –1. Input Characteristics

VCE =2V VCE =5V VCE =10V VCE =open

S.No.

IB VBC IB VBC IB VBC IB VBC

(µA) (Volts) (µA) (Volts) (µA) (Volts) (µA) (Volts)

1. 0 0 0 0

2. 5 5 5 5

3. 10 10 10 10

4. 20 20 20 20

5. 30 30 30 30

6. 40 40 40 40

7. 50 50 50 50

MODEL GRAPH:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

2.Output Characteristics:

Fig.2 Circuit diagram for the study of output characteristics of a Transistor in common-

collector configuration

Theory: The output characteristics curves give the relationship between collector to emitter

voltage (VEC) and the emitter current (IE)

PROCEDURE:

i. Connect the circuit as shown in Fig-2.

ii. Ensure that the power supply is switched OFF. Keep the voltage control knob in the

minimum

position and current control knob in maximum position.

iii. Switch ON the power supply. Adjust VEC =2V

iv. Fix the collector to emitter voltage (VEC) . Record the corresponding values of emitter

current (IE) in the table shown below.

v. Repeat steps from i to iv for different values of VEC say VEC =5V, 10V and for VBC open

(This can be done by opening one of the output terminals).

vi. Draw the output characteristics for different values of V EC in Fig.3(b).

viii. Present all the results at the end.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

OBSERVATIONS:

Table – II Output Characteristics

IB =20(µA) IB =40(µA) IB =60(µA) IB =80(µA) IB =100(µA)

S.No.

VEC IE VEC IE VEC IE VEC IE VEC IE

(Volts) (mA) (Volts) (mA) (Volts) (mA) (Volts) (mA) (Volts) (mA)

1.

2.

3.

4.

5.

6.

7.

MODEL GRAPH:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULTS:

The input and output characteristics are drawn and the following hybrid parameters are

estimated from the graphs.

hic = VBC Ib at VEC= constant.

hrc = VBC / VEC at IB= constant.

Are computed from the input characteristics

hoc = IE / VEC at IB=constant.

hfc = IE / IB at VEC= constant

Are computed from the output characteristics

DISCUSSIONS:

Indicate the various regions (Active region, Saturation region and cut-off region) on the output

characteristics of the transistor and discuss them.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO: 7

FIELD EFFECT TRANSISTOR - STATIC

CHARACTERISTICS

AIM:

a) To obtain the static characteristics(output and transfer characteristics) of a

given Field Effect Transistor (FET).

b) Identify the Ohmic, Pinch-off and breakdown regions of the characteristics

and to estimate the values of drain resistance (rd), trans-conductance- gm

and the amplification factor –A from the characteristics.

APPARATUS:

i. Diode OA79, Resistors 220Ω, FET-BFW10

ii. Mille Ammeters (0-25mA)

iii. Voltmeter (0-30 V)

iv. Single stand wires, Bread board.

v. Regulated Power Supply (0-30V)

CircuitDiagram:

Fig.1 circuit diagram for studying the characteristics of a FET

Theory:

The Field effect Transistor is a three terminal Uni polar device in which the current through

the device is controlled by the electric field, unlike the case of bipolar transistors. Hence, they

offer very high input impedance compared to bipolar devices. A reverse biased diode is included in

the path of the gate to protect the FET from any accidental forward biasing. A high input

impedance digital voltmeter should be connected between the gate and source.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

(i). Drain Characteristics or output characteristics:

These curves give the relationship between the drain to source voltage V ds and drain

current Id for different values of gate to source voltage V gs. As Vgs is increased pinch-off voltage

is reached at lower value of drain current and Vds also decreases as compared to that when V gs is

zero.

(ii). Transfer characteristics or input characteristics:

These curves gives the relationship between drain current Id and gate to source voltage Vgs

for different values of drain to source voltage Vds. These are also called as Trans-conductance

curves.

PROCEDURE:

i. Make the connections as shown in the circuit Diagram shown in fig-1.

ii. Ensure that the power supply is switched OFF. Keep the voltage control knob in the minimum

position and current control knob in maximum position.

OUTPUT CHARACTERISTICS:

i. Set V gs = -1Volts by varying V gg. Gradually increase the drain to source voltage by varying V dd

from 0 – 10 Volts in steps of I volt and note down the drain current I d .

ii. Repeat this for V gs = -2 Volts and V gs = -3.0 Volts. ------------------

iii. Record the observations in Table-I

iv. Plot V ds versus Id for different values of V gs.

v. Draw the output characteristics V ds versus Id as shown in Fig.2(a), and calculate the drain

resistance rd from the graph in the linear region of the characteristics by

rd = [V ds / Id] at V gs = constant.

vi. Present all the results at the end of the experiment.

OBSERVATIONS:

TABLE-I : Output characteristics

V gs =- 0.0V V gs = -1V V gs =-2V Vgs =-3V

S.No.

Vds(V) Id (mA) Vds (V) Id (mA) Vds (V) Id (mA) Vds (V) Id (mA)

1. 0.0

2. 0.5

3. 1.0

4. -

5. -

6. -

7. -

8. -

9. -

10 10.0

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

TRANSFER CHARACTERISTICS:

i. Set V ds = 2 Volts by varying Vdd .

ii. Increase Vgs from 0 to 5 volts in steps of 0.5 volts gradually and note down the values for

Id.

iii. Repeat this for V ds = 5 volts and V ds = 10 Volts.

iv. Plot the graph V gs versus Id for constant V ds as shown in Fig.2(b) and calculate the

Trans-conductance (gm) from the graph in the linear region of the characteristics

g m = [Id/V gs] at V ds = constant.

v. Present all the results at the end of the experiment.

OBSERVATIONS:

TABLE-II : Transfer characteristics

V ds = 2 V V ds = 4 V V ds = 6 V

S NO

Vgs (V) Id (mA) Vgs (V) Id (mA) Vgs (V) Id (mA)

MODEL GRAPHS:

Drain or Output Characteristics Transfer Characteristics

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULT:

The parameters of the FET are

Drain resistance rd =

Transconductance gm =

Amplification factor = rd . gm

DISCUSSIONS:

i. Why FET is called unipolar device ?

ii. What are the differences between FET& UJT?

iii. Why FET is called voltage control device?

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO:8

C.E AMPLIFIER

AIM:

To obtain the frequency response characteristics of the C.E.amplifier and

calculating 3db bandwidth.

To estimate maximum signal handling capacity of amplifier in the mid frequency

band.

To measure the I/P impedance and O/P impedance of the amplifier.

To observe the phase response of amplifier

APPARATUS:

i. C.R.O, D.C Regulated power supply ,

ii. Signal generator,

iii. Transistor BC107, Resistors 1K,10K,100K,1K,2.2KΩ, Capacitors 10μF-(3),

iv. Bread board, patch cords (or) single stand wires.

CIRCUIT DIAGRAM :

PROCEDURE:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

1. Connect the circuit as shown in figure, and check for the D.C conditions of the transistor to

ensure that it is in active region . Obtain the maximum signal handling capacity (also known as

over load characteristic) at constant input signal frequency of 1 KHz as follows (i.e), Vary the

input voltage from 0 to 2V in suitable steps 10mV.

Plot the characteristic of out put voltage Vs input voltage. Indicate the point where the

distortion begins to set in the O/P. The corresponding amplitude of the I/P voltage gives the

maximum signal handling capacity for the amplifier.

2. a) Measurement of input impedance :

Fix the frequency at 1KHz note the values of Vs ,Vi and calculate the input impedance Zi by

using the following equations.

Iin = (Vs – Vi) / Rs Zi = Vi / Iin.

b) Measurement of out put impedance :

At 1KHz frequency note the un-load o/p voltage V0. Then Connect a decade resistance box

across the O/P terminals and adjust its value such that V0 falls to half of the unloaded value.

The reading on the decade resistance box gives the value of out put impedance Z0.

3. Gain Vs frequency response :

i) Keeping the input voltage constant (below maximum signal handling capacity) vary the

frequency from 10 Hz onwards in suitable steps up to a frequency where the out put voltage

falls to less than half of the maximum out put voltage in the mid band.

ii) Plot a graph of gain (Vo/Vi) Vs frequency on a semi log graph sheet and determine the

bandwidth.

OBSERVATIONS: Vi = Volts(rms).

S.NO FREQUENCY Vo (V) Av = (Vo/Vi) Av(db)=20 log(Vo/Vi)

4. Phase difference Vs frequency response :-

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

i) Using C.R.O measure the phase difference between Vin and Vout as the frequency of the

input signal is varied in suitable steps and tabulate the results as shown below. Plot the

phase Vs frequency.

FREQUENCY OFI/P SIGNAL

a b Ø = invers sin(b/a)

Note : Find the phase difference between the input and the output signals at 2 or 3 frequencies in

the lower frequency, mid-frequency and the High –frequency segments of the characteristic.

MODEL GRAPHS:

Amplitude response

Phase response

RESULT:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

SNO PARAMETER THEORITICAL EXPERIMENTAL

1. Maximum signal handling capacity

2. Input impedance

3. Out put impedance

4. Mid band voltage gain

5. 3db gain

6. Lower half power frequencyf1=very small

7.

Upper half power frequency f2

8.

Band width B=(f2-f1) = f2

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO:9

EMITTER FOLLOWER

AIM:

i) To obtain maximum signal handling capacity (over load characteristic) by

plotting the out put voltage verses the input voltage a fixed frequency of

1 KHz (in the mid frequency band).

ii) To measure the I/P impedance and O/P impedance of the amplifier.

iii) To obtain the frequency response of the amplifier

a) Gain Vs Frequency b) Phase difference Vs Frequency.

APPARATUS:

i. C.R.O, D.C Regulated power supply ,

ii. Signal generator,

iii. Transistor BC107,

iv. Resistors 1K, 10K,100K,470Ω, Capacitors10μF,22μF,

v. Bread board, patch cords (or) Single stands wires.

CIRCUIT DIAGRAM:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

PROCEDURE:

1. .Connect the circuit as shown in figure, and check for the D.C conditions of the transistor to

ensure that it is in active region . Obtain the maximum signal handling capacity (also known as over

load characteristic) at constant input signal frequency of 1 KHz as follows (i.e), Vary the input

voltage from 0 to 2V in suitable steps 10mV.

Plot the characteristic of out put voltage Vs input voltage. Indicate the point where the

distortion begins to set in the O/P. The corresponding amplitude of the I/P voltage gives the

maximum signal handling capacity for the amplifier.

2. a) Measurement of input impedance :

Fix the frequency at 1KHz note the values of Vs ,Vi and calculate the input impedance Zi by

using the following equations.

Iin = (Vs – Vi) / Rs Zi = Vi / Iin.

b) Measurement of out put impedance :

At 1KHz frequency note the un-load o/p voltage V0. Then Connect a decade resistance box

across the O/P terminals and adjust its value such that V0 falls to half of the unloaded value.

The reading on the decade resistance box gives the value of out put impedance Z0.

3. Gain Vs frequency response :

i) Keeping the input voltage constant (below maximum signal handling capacity) vary the

frequency from 10 Hz onwards in suitable steps up to a frequency where the out put voltage

falls to less than half of the maximum out put voltage in the mid band.

ii) Plot a graph of gain (Vo/Vi) Vs frequency on a semi log graph sheet and determine the

bandwidth.

OBSERVATIONS: Vi = Volts(rms).

S.NO FREQUENCY Vo (V) Av = (Vo/Vi) Av(db)=20 log(Vo/Vi)

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

4. Phase difference Vs frequency response :-

i) Using C.R.O measure the phase difference between Vin and Vout as the frequency of the

input signal is varied in suitable steps and tabulate the results as shown below. Plot the

phase Vs frequency.

FREQUENCY OFI/P SIGNAL

a b Ø = invers sin(b/a)

Note : Find the phase difference between the input and the output signals at 2 or 3 frequencies in

the lower frequency, mid-frequency and the High –frequency segments of the characteristic.

MODEL GRAPHS:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULT:

SNO PARAMETER THEORITICAL EXPERIMENTAL

1. Maximum signal handling capacity

2. Input impedance

3. Out put impedance

4. Mid band voltage gain

5. 3db gain

6. Lower half power frequencyf1=very small

7.

Upper half power frequency f2

8.

Band width B=(f2-f1) = f2

DISCUSSION :

1. The phase difference between in put and out put for an emitter follower at the mid frequency

is

-----------------.

2. For emitter follower which parameter or characteristics are highest compare it with C.B

configuration.

3. Operation of emitter follower.

4. The feed back used in emitter follower --------------------.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO:10

FET AMPLIFIER

AIM:

i) To obtain maximum signal handling capacity (over load characteristic)

by plotting the out put voltage verses the input voltage a fixed frequency of 1KHz (in the

mid frequency band).

ii) To measure the I/P impedance and O/P impedance of the amplifier

iii) To obtain the frequency response of the amplifier

a) Gain Vs Frequency b) Phase difference Vs Frequency.

APPARATUS:

i. C.R.O, D.C Regulated power supply ,

ii. Signal generator ,

iii. Transistor BFW10, Resistors 100K,1M,1K,2.2KΩ, Capacitors 10μF-(3),

iv. Bread board, patch cords (single stands wires).

CIRCUIT DIAGRAM :

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

PROCEDURE :

1. Connect the circuit as shown in figure, and check for the D.C conditions of the transistor to

ensure that it is in active region . Obtain the maximum signal handling capacity (also known as

over load characteristic) at constant input signal frequency of 1 KHz as follows (i.e), Vary the

input voltage from 0 to 2V in suitable steps 10mV.

Plot the characteristic of out put voltage Vs input voltage. Indicate the point where the

distortion begins to set in the O/P. The corresponding amplitude of the I/P voltage gives the

maximum signal handling capacity for the amplifier.

2. a) Measurement of input impedance :

Fix the frequency at 1KHz note the values of Vs ,Vi and calculate the input impedance Zi by

using the following equations.

Iin = (Vs – Vi) / Rs Zi = Vi / Iin.

b) Measurement of out put impedance

At 1KHz frequency note the un-load o/p voltage V0. Then Connect a decade resistance

box across the O/P terminals and adjust its value such that V0 falls to half of the unloaded

value. The reading on the decade resistance box gives the value of out put impedance Z0.

3. Gain Vs frequency response :

Keeping the input voltage constant (below maximum signal handling capacity) vary the

frequency from 10 Hz onwards in suitable steps up to a frequency where the out put voltage

falls to less than half of the maximum out put voltage in the mid band.

Plot a graph of gain (Vo/Vi) Vs frequency on a semi log graph sheet and determine the

bandwidth.

OBSERVATIONS: Vi = Volts.

S.NO FREQUENCY Vo (V) Av = (Vo/Vi) Av(db)=20 log(Vo/Vi)

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

4. Phase difference Vs frequency response :-

Using C.R.O measure the phase difference between Vin and Vout as the frequency of the input

signal is varied in suitable steps and tabulate the results as shown below. Plot the phase Vs

frequency.

FREQUENCY

OFI/P SIGNAL a b Ø = invers sin(b/a)

Note : Find the phase difference between the input and the output signals at 2 or 3 frequencies in

the lower frequency, mid-frequency and the High –frequency segments of the characteristic.

MODEL GRAPHs:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULT :

SNO PARAMETER THEORITICAL EXPERIMENTAL

1. Maximum signal handling capacity

2. Input impedance

3. Out put impedance

4. Mid band voltage gain

5. 3dbgain Lower half power

6. frequencyf1=very small

7. Upper half power frequency f2

8. Band width B=(f2-f1) = f2

RESULTS & DISCUSSION :

1. The phase difference between in put and out put for common source FET amplifier at the mid

frequency is -----------------.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO:11

CHARACTERISTICS OF A SILICON CONTROLED

RECTIFIER (SCR)

AIM:To Study the forward characteristics of the given SCR (TY 6004) for different gate currents.

APPARATUS :

i. SCR TY6004,Resistors 500Ω,

ii. Voltmeter(0-20V), Ammeter(0-100mA,0-500mA)

iii. Regulator Power Supply (0-30V),

iv. Decad Resistance box, Bread board, Single stand wires.

Circuit Diagram:

Fig.1 circuit diagram for the study of the characteristics of SCR

Theory :

i. SCR firing is indicated by the sudden increase of current I A in the anode circuit along with a

sudden fall in voltage across SCR‟s anode to cathode.

ii. If SCR is on „ON‟ state the anode current is sufficient enough to hold this SCR in ON

PROCEDURE:

i. Connect the circuit as shown in the Fig.1

ii. Connect (0-500ma) Digital multimeter in anode circuit, (0-20)v voltmeter across SCR and

(0-100)ma meter in the gate circuit.

iii. Adjust gate current to any value in the range of (4.1,4.2,4.3………5.8,5.9,6.0)ma with the help of

the power supply V2and a series resistance (potentiometer) in the gate circuit.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

iv. Care should be exercised in adjusting the gate current in very small steps of 0.1V to enable the

observation of the anode current variations carefully. Otherwise it is difficult to observe and

record the same.

v. Initially fix the gate current IG = 0, and vary power supply V1 from its minimum and note down

the

readings of VAK and IA tabulate these values in the table.

vi. Repeat step v for a different value of gate current.

vii. Plot the observations as shown in Table-1.

OBSERVATIONS:

Table -I

IG1=0 mA IG2=4.41mA IG3=4.46mA

S.No VAK(Volts) IA (mA) VAK (Volts) IA (mA) VAK (Volts) IA (mA)

MODEL GRAPH:

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULTS:

It is experimentally observed that –

i. The holding current for the SCR TY 6004 is ________ mA

ii. The blocking region for Ig =0 extends upto__________ volts

iii. The break over voltage VBR ___________________________________ Volts

Specifications of SCR ( TY 6004)

i. Repetitive peak reverse voltages (open gate voltages) VRRM400V

ii. Rms On state current Irms --------------- 6 Amps

iii. Average trigger voltage Vgt--------------- 1.5v

iv. Surge Non-Repetitive ON state current------- 7A

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

EXPERIMENT NO:12

UNIJUCTION TRANSISTOR CHARACTERISTICS

AIM: i. To study the static characteristics of a given UJT (2N2646)

ii. Identify the negative resistance region and estimate the resistance of the device.

APPARATUS:

1. UJT (2N2646), Resistors 220Ω

2. Ammeter (0-50mA)

3. Voltmeter (0-30 V)- 1 No, and (0-10V) – 1No.

4. Regulated Power Supply (0-30V), Bread board. Single stand wires.

Circuit Diagram:

FIG:1 circuit diagram for the study of the characteristics

Theory :

The Uni-junction transistor (UJT) is a three terminal silicon semiconductor device. The

UJT has only one PN junction. The PN junction is formed between the emitter and the base regions.

The emitter region is heavily doped. The emitter region is closer to base (B1) terminal than base

(B2). The operational difference between FET and UJT is that FET is normally operated with gate

junction reverse biased, whereas useful behavior of UJT occurs when the emitter is forward

biased.

PROCEDURE:

i. Connect the circuit as shown in Fig.1 above.

ii. Ensure that the power supply is switched OFF. Keep the voltage control knob in the minimum

position and current control knob in maximum position.

iii. Switch ON the power supply. Keep V BB at 5volts. Now vary VEB1 by varying VEE. Note down IE

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

once UJT is ON, Increase the emitter current IE in small steps of 5mA and note down the

Corresponding VEB1 value upto a maximum of 50mA.

iv. Repeat above steps for V EB = 10V and 15V. Plot graph of IE versus V EB1 for different values of

VBB as shown in Fig.3.

v. Calculate resistance of the UJT in the negative resistance region using the formula

r(-) = V EB1 / I E at V BB = constant.

OBSERVATIONS:

Table-I

S.No. VBB=5 V VBB=8 V VBB=10 V

IE (ma) VEB1 (V) IE (ma) VEB1(V) IE(ma) VEB1(V)

1.

2.

3.

4.

5.

6.

7.

8.

MODEL GRAPH:

FIG:Characteristics of a UJT (2N2646)

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

DEPARTMENT OF

ELECTRONICS AND COMMUNICATIONS ENGINEERING

RESULT:

i. The operation of UJT as a negative resistance device is verified.

ii. Present results of the experiment

R (-) = … ohms at VBB=5V

R (-) =……ohms at VBB=10V

R (-) = … ohms at VBB=15V

i. The operation of UJT as a negative resistance device is verified.

Specifications:

Intrinsic stand off ratio :ή

Peak point emitter current : Ipeak

Valley point current : Iv

DISCUSSIONS:

i. Draw the equivalent circuit of the UJT?

ii. Name a few of the applications of the UJT?

rB1 = -ΔVEB1 / ΔIE at Constant VBB.

VNRVJIET ELECTRONIC DEVICES AND CIRCUITS LAB MANUAL

Potrebbero piacerti anche

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesDa EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesValutazione: 4.5 su 5 stelle4.5/5 (7)

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDa EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsValutazione: 3 su 5 stelle3/5 (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Passive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2Da EverandPassive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2Nessuna valutazione finora

- Fate NumeneraDocumento24 pagineFate Numeneraimaginaari100% (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Chetan Bhagat - Three Mistakes of My LifeDocumento144 pagineChetan Bhagat - Three Mistakes of My LifeGayathri ParthasarathyNessuna valutazione finora

- Basic Electronics LabDocumento60 pagineBasic Electronics Labrahulsingle67% (3)

- ASD Fan CalculatorsDocumento14 pagineASD Fan CalculatorslubricacionNessuna valutazione finora

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisDa EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisNessuna valutazione finora

- Building SOR 01.12.2020 Volume 1Documento437 pagineBuilding SOR 01.12.2020 Volume 1Shiv Shankar Shukla82% (11)

- S934 - Instruction ManualDocumento36 pagineS934 - Instruction ManualTony MarascaNessuna valutazione finora

- Edc Lab ManualDocumento70 pagineEdc Lab ManualreneeshczNessuna valutazione finora

- Electron DeviceDocumento112 pagineElectron DevicekrishnaNessuna valutazione finora

- Full Site PDFDocumento23 pagineFull Site PDFpursuwNessuna valutazione finora

- Electromagnetic Foundations of Electrical EngineeringDa EverandElectromagnetic Foundations of Electrical EngineeringNessuna valutazione finora

- Electronic Devices - Circuits Lab ManualDocumento77 pagineElectronic Devices - Circuits Lab ManualpdnkiranNessuna valutazione finora

- EDC Lab ManualDocumento112 pagineEDC Lab ManualPradeep Kumar SNessuna valutazione finora

- Pruebas y Mantenimiento Automático Centralizado para Detectores de Humo Direccionales Vesda VeaDocumento50 paginePruebas y Mantenimiento Automático Centralizado para Detectores de Humo Direccionales Vesda Veasanti0305Nessuna valutazione finora

- Semiconductor Devices and Circuits LaboratoryDocumento53 pagineSemiconductor Devices and Circuits LaboratoryKaryampudi RushendrababuNessuna valutazione finora

- EDC Lab ManualDocumento68 pagineEDC Lab ManualRocky AdityaNessuna valutazione finora

- EDC Lab ManualDocumento63 pagineEDC Lab Manualranjitha gavniNessuna valutazione finora

- EDC Lab Manual EeeDocumento106 pagineEDC Lab Manual EeeVishnu Kumar NadarNessuna valutazione finora

- Electronics 1Documento42 pagineElectronics 1Shanti Emmanuelle EscabarteNessuna valutazione finora

- SDC Lab Manual - PDFDocumento41 pagineSDC Lab Manual - PDFRonitNessuna valutazione finora

- List of ExperimentsDocumento214 pagineList of Experimentssenthil786Nessuna valutazione finora

- s3 LabDocumento54 pagines3 LabVishal bijiNessuna valutazione finora

- Principle of Electronics EnggDocumento47 paginePrinciple of Electronics EnggNilabh KumarNessuna valutazione finora

- Electron Devices and Circuits LaboratoryDocumento213 pagineElectron Devices and Circuits Laboratoryrajesh0682Nessuna valutazione finora

- Sdc-Labmanual by Prabhu Kumar SurarapuDocumento62 pagineSdc-Labmanual by Prabhu Kumar Surarapuprabhu4scribdNessuna valutazione finora

- Electronic Devices & Circuits: Laboratory ManualDocumento61 pagineElectronic Devices & Circuits: Laboratory ManualFadila IsmailNessuna valutazione finora

- 11-Hardware - Characteristics of PN Junction Diode & Zener Diode Software - Full Wave Bridge Rectifier-29-1Documento6 pagine11-Hardware - Characteristics of PN Junction Diode & Zener Diode Software - Full Wave Bridge Rectifier-29-1Zack ZackNessuna valutazione finora

- Edc Lab ManualDocumento216 pagineEdc Lab ManualKalai YarasiNessuna valutazione finora

- Ecb 2182 Electronics and Microprocessors Lab Manual: S.Sadhish Prabhu, Ap/EceDocumento63 pagineEcb 2182 Electronics and Microprocessors Lab Manual: S.Sadhish Prabhu, Ap/EceNeoNessuna valutazione finora

- 2-1 EDC Lab Manual Jntuk R20 - 201021Documento96 pagine2-1 EDC Lab Manual Jntuk R20 - 201021Durgasaiteja923 SunnyNessuna valutazione finora

- Ee LabDocumento28 pagineEe LabBalajiNessuna valutazione finora

- Experiment 6 Diode CharacteisticsDocumento4 pagineExperiment 6 Diode CharacteisticsAbral QureshiNessuna valutazione finora

- Semi ManialDocumento44 pagineSemi ManialSatadru DasNessuna valutazione finora

- Laboratory Manual: SRM UniversityDocumento54 pagineLaboratory Manual: SRM UniversityreneeshczNessuna valutazione finora

- V-I Characteristics of PN Junction DiodeDocumento6 pagineV-I Characteristics of PN Junction DiodeAditya GorrepatiNessuna valutazione finora

- KEC151P - Lab - Experiments - UPDATED ONEDocumento34 pagineKEC151P - Lab - Experiments - UPDATED ONEAkshat GuptaNessuna valutazione finora

- Clippers ExperimentDocumento45 pagineClippers ExperimentSrirevathi BalapattabiNessuna valutazione finora

- Exp 02Documento7 pagineExp 02M. Ahmad RazaNessuna valutazione finora

- V-I Characteristics of PN Junction DiodeDocumento5 pagineV-I Characteristics of PN Junction Dioder21745566100% (1)

- Lab Manual EE552Documento50 pagineLab Manual EE552s.r.Nessuna valutazione finora

- List of Experiments: Ee2207 Electronic Devices and Circuits Laboratory (Revised)Documento54 pagineList of Experiments: Ee2207 Electronic Devices and Circuits Laboratory (Revised)prakashkumarNessuna valutazione finora

- 21BCE5419 Exp2Documento9 pagine21BCE5419 Exp2Anshika RaiNessuna valutazione finora

- Lab ManualDocumento8 pagineLab Manualbond 777Nessuna valutazione finora

- Online - Bai 2 - Mach Ban DanDocumento15 pagineOnline - Bai 2 - Mach Ban DanThất VọngNessuna valutazione finora

- Lab Manual: Electrical Engineering Materials & Semiconductor Devices Lab (EC-317-F)Documento41 pagineLab Manual: Electrical Engineering Materials & Semiconductor Devices Lab (EC-317-F)Ilavarasan TamizhNessuna valutazione finora

- Lab Manual: Power ElectronicsDocumento23 pagineLab Manual: Power Electronicsprakhar yadavNessuna valutazione finora

- Ec0221 Ed Lab ManualDocumento68 pagineEc0221 Ed Lab ManualGoutham ShanNessuna valutazione finora

- Lab ManualDocumento56 pagineLab ManualMy JaanNessuna valutazione finora

- SD Lab Manual 17.3.22Documento67 pagineSD Lab Manual 17.3.22ParthaSarathyNessuna valutazione finora

- Lab Task Exp-1,2,3Documento9 pagineLab Task Exp-1,2,3Ashish patelNessuna valutazione finora

- Analogue-Practicals (29.11.2023)Documento11 pagineAnalogue-Practicals (29.11.2023)ryanhazo47Nessuna valutazione finora

- AE Lab Manual For EeeDocumento53 pagineAE Lab Manual For EeeSRUJANA VNessuna valutazione finora

- Experiment-No 2Documento5 pagineExperiment-No 2carloNessuna valutazione finora

- Eee 111 Lab Manual 2-8 (Latest)Documento32 pagineEee 111 Lab Manual 2-8 (Latest)Ismot Jahan MoniNessuna valutazione finora

- Exp 45Documento11 pagineExp 45tanmay sonawaneNessuna valutazione finora

- Microsoft Word - BM0110 Devices Lab Manual FinalDocumento54 pagineMicrosoft Word - BM0110 Devices Lab Manual FinalAnupma KumariNessuna valutazione finora

- Electric Circuits and Electron Device Lab ManualDocumento24 pagineElectric Circuits and Electron Device Lab ManualSuganthan Dboss100% (1)

- C Programming NotesDocumento12 pagineC Programming NotesAshritaNessuna valutazione finora

- Projectreport17 170714011541Documento35 pagineProjectreport17 170714011541AshritaNessuna valutazione finora

- 5 2 Wattmeter Method1Documento3 pagine5 2 Wattmeter Method1Luwani LinoNessuna valutazione finora

- "Automatic Power Factor Detection and Correction": Project ReportDocumento84 pagine"Automatic Power Factor Detection and Correction": Project ReportAshritaNessuna valutazione finora

- Projectreport17 170714011541Documento35 pagineProjectreport17 170714011541AshritaNessuna valutazione finora

- bNSG9000 Datasheet 2Documento3 paginebNSG9000 Datasheet 2RobertNessuna valutazione finora

- Coulomb's Law and Electric Field Intensity: Engineering ElectromagneticsDocumento24 pagineCoulomb's Law and Electric Field Intensity: Engineering ElectromagneticsKenn SenadosNessuna valutazione finora

- Content (SG)Documento88 pagineContent (SG)Kusuma Cakra WardayaNessuna valutazione finora

- STAN Statistika 12 PDFDocumento25 pagineSTAN Statistika 12 PDFPembelajaran Jarak JauhNessuna valutazione finora

- AdsfatreewerwertgdsfDocumento1 paginaAdsfatreewerwertgdsfJhonel AguilarNessuna valutazione finora

- StringTokenizer in JavaDocumento11 pagineStringTokenizer in JavaNeha saxena Neha saxenaNessuna valutazione finora

- Lenskart Solutions PVT LTD Company ProfileDocumento13 pagineLenskart Solutions PVT LTD Company ProfileAnujaNessuna valutazione finora

- Bearing Solutions and Service For Wind TurbinesDocumento16 pagineBearing Solutions and Service For Wind TurbinesDrZEIDINessuna valutazione finora

- Ap Art and Design Drawing Sustained Investigation Samples 2019 2020 PDFDocumento102 pagineAp Art and Design Drawing Sustained Investigation Samples 2019 2020 PDFDominic SandersNessuna valutazione finora

- Hibon - SN Ingersoll Rand BlowerDocumento7 pagineHibon - SN Ingersoll Rand BlowermarquezsiemNessuna valutazione finora

- Report On RoboticsDocumento40 pagineReport On Roboticsangelcrystl4774Nessuna valutazione finora

- Unit II Construction PracticesDocumento61 pagineUnit II Construction PracticesiploguNessuna valutazione finora

- Unit-3: Grid FrameworkDocumento44 pagineUnit-3: Grid FrameworkMUKESH KUMAR P 2019-2023 CSENessuna valutazione finora

- A Very Old MachineDocumento20 pagineA Very Old MachineSwathi G. SalemNessuna valutazione finora

- The Limited City - Building Height Regulations in The City of Melbourne, 1890-1955 by Peter Mills 1997Documento75 pagineThe Limited City - Building Height Regulations in The City of Melbourne, 1890-1955 by Peter Mills 1997tismdblNessuna valutazione finora

- CMR ArtifactDocumento51 pagineCMR ArtifactAdel SALLAMNessuna valutazione finora

- A MCQ: Si - No Sub Topics NameDocumento2 pagineA MCQ: Si - No Sub Topics NameInzamamul Haque ShihabNessuna valutazione finora

- Final Cor 011 Reviewer PDFDocumento104 pagineFinal Cor 011 Reviewer PDFMary JuneNessuna valutazione finora

- Osteointegration of Bioactive Glass-Coated Zirconia in Healthy Bone: An in Vivo EvaluationDocumento9 pagineOsteointegration of Bioactive Glass-Coated Zirconia in Healthy Bone: An in Vivo EvaluationMario Misael Machado LòpezNessuna valutazione finora

- CPHL 214 Assignment 6Documento2 pagineCPHL 214 Assignment 6NazNessuna valutazione finora

- Buku Murid Bahasa Inggris - Student's Book My Next Word For Elementary School Unit 10 - Fase BDocumento8 pagineBuku Murid Bahasa Inggris - Student's Book My Next Word For Elementary School Unit 10 - Fase BKeni KenizaNessuna valutazione finora

- Slidex StrepDocumento9 pagineSlidex StrepLizeth Daniela RojasNessuna valutazione finora

- Architect As An Environmental PlannerDocumento14 pagineArchitect As An Environmental PlannerJames Adrian MoralNessuna valutazione finora

- 365-M - City Bus Route & Timings, Bangalore (BMTC) Map, First & Last BusDocumento10 pagine365-M - City Bus Route & Timings, Bangalore (BMTC) Map, First & Last BusER Aditya DasNessuna valutazione finora