Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Implementation of Inter-Integrated Circuit (I2C) Multiple Bus Controller On FPGA Using VHDL

Caricato da

Kumars tiwariTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Implementation of Inter-Integrated Circuit (I2C) Multiple Bus Controller On FPGA Using VHDL

Caricato da

Kumars tiwariCopyright:

Formati disponibili

Implementation of Inter-Integrated Circuit(I2C) Multiple Bus Controller on FPGA Using

VHDL

Mrs. Jaya Malviya Mr. Arif Mohammad

M Tech (VLSI Design) Dept. of Electronics and Co mmunicat ions

Gyan Ganga Institute of Technology and Sciences Gyan Ganga Institute of Technology and Sciences

Jabalpur,Madhya Pradesh Jabalpur,Madhya Pradesh

E-mail jayamalviyachaturvedi@gmail.co m E-mail arif@ggits.org

Abstract— The Inter - Integrated Circuit bus

commonly called as I2C (I squared C) or I2C bus is • Compatible with Philips I2 C standard

a serial bus invented by Philips Semiconductors • Works with up to 16 distinct I2 C buses

during early 80’s for interconnecting integrated • Statically configurable system bus clock

circuits. In this paper, the design and frequency

implementation of a I2C Multiple Bus Controller

(IICMB) core is presented. • Statically configurable desired clock

frequencies of I2 C buses

Keywords—I2CMB, I2C Protocol, Avalon Memory mapped • Multi- master clock synchronization

Interfaces, I2C Communication (key words)

• Multi- master arbitration

I. INTRODUCTION • Clock stretching

• Digital filtering of SCL and SDA inputs

I2C bus was developed by Philips Semiconductors • Standard (up to 100 kHz) and Fast (up to

during 1980’s for connecting computer peripherals 400 kHz) mode operation

together using a common protocol.This

• Connects as 8-bit slave on Wishbone bus

specification defines the architecture, hardware

interface and parameterization options • Connects as 32-bit slave on Avalon-MM bus

for the I2 C Multiple Bus Controller (IICMB) core.

Architecture

The IICMB core provides a low-speed, two-wire, The core is provided with three examples of its top

bidirectional serial bus interfaces compliant to level (iicmb_m_wb.vhd, iicmb_m_av.vhd and

industry standard I2 C protocol. The key feature of iic_m_sq.vhd). Two of them are designed for

the core is its ability to control several connected Wishbone and Avalon-MM buses, while third

I2 C buses effectively reducing complexity of version is a sequencer based one for deeply

system. embedded applications without any system bus at

At any given moment the IICMB core works with a all.

single I2 C bus chosen from the range of connected In the center of the IICMB core is iicmb_m.vhd

buses (throughout this document such bus is called module which integrates byte- and bit level master

selected bus). When work with a particular selected mode FSMs together with I2 C bus multiplexer

bus is finished, user can switch to another one to functionality. It is controlled with byte- level

continue configuring other peripherals. Every commands sent through the so-called Generic

connected I2 C bus is recognized by its number, or Interface.

bus ID.

Note: The current version of the core supports

master only functionality. Slave mode is under

development.

Proposed Features:

The key feature of the core is its ability to

effectively reducing complexity of the system

and control several connected I2C buses.

Signal Name I/O Description

Clk Input Avalon-MM clock. M ain clock for

the controller.

s_rst Input Synchronous reset. Active high.

waitrequest Output Wait request.

readdata[31:0] Output Data output.

readdatavalid Output Data validity indication.

writedata[31:0] Input Data input.

Write Input Indicates a write transfer.

Read Input Indicates a read transfer.

byteenable[3:0] Input Enables specific byte lane(s) during

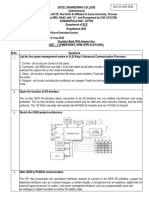

Fig. Block diagram of the Wishbone version of the transfer

top level

The wishbone.vhd module connects Wishbone bus Keeping in mind all the above specifications the key

to register block (regblock.vhd), which converts features of our design are

system bus accesses to byte- level commands of the

Generic Interface. SCL and SDA inputs are Works with up to 16 distinct I2C buses

digitally filtered to suppress unwanted spikes and Statically configurable system bus clock

to cope with long rising time of the I2C bus frequency

signals. The bus_state.vhd modules independently Statically configurable desired clock frequencies

monitor busy states of all connected buses. of I2C buses

The conditioner_mux.vhd module, controlled by Multi- master clock synchronization

bus_id input, performs switching between Multi- master arbitration

connected I2C buses. Clock stretching

The mbit.vhd and mbyte.vhd implement bit-level Digital filtering of SCL and SDA inputs

and byte- level FSMs, generating appropriate SCL Standard (up to 100 kHz) and Fast (up to 400

and SDA waveforms in accordance to I2C Bus kHz) mode operation

Specification Example connection as 32-bit slave on Avalon-

MM bus

Ope ration

Some of the basic features on which have been Byte-level FSM

implemented are as follows. The byte-level FSM module (mbyte.vhd)

communicates with upper level through so called

Implementation of IICMB core which provides Generic Interface. It accepts several byte- level

low-speed, two-wire, bidirectional serial bus commands listed in the Table 1 below.

interfaces compliant to industry standard I2C

protocol. After completion, each command is answered with

“Manchester encoded UART” which enables an appropriate response. The main responsibility of

running small peripherals with parasitic power the mbyte.vhd module is to translate byte- level

derived from the TXD line, and allowing large commands to one or more commands for bit- level

clock differences typical of RC oscillators. FSM (mbit.vhd).

Reception of a response is a mark of completion of

the previously issued command. It is

an error to send next command before previous

command is responded. Such a command is

ignored. The following diagram depicts the byte- level FSM

Comma Code Para Description

nd meter

Start “100” – If bus is not captured yet: issue

Start Condition and capture

selected bus. If bus captured:

issue Repeated Start Condition.

Stop “101” – Issue Stop Condition and free

selected bus.

Read “010” – Receive a byte with

With acknowledge.

Ack

Read “011” – Receive a byte with not-

With acknowledge.

Nak

Write “001” Byte Transmit the byte given as a

of data parameter.

Set Bus “110” Bus Connect to the specified bus Byte- level FSM

numbe (select bus).

r (ID)

Bit-level FSM

Wait “000” Millise Do nothing for specified Bit-level commands and responses are hidden from

conds amount of time. the user of the core, but listed here for better

understanding of how the two FSMs interact with

Byte- level commands each other.

Bit-level commands and responses have no

Respons Code Para Description parameters.

e mete

r

Done “000” – Command completed.

Arbitrati “010” – Arbitration lost. Selected bus is

on Lost freed, FSMs are set to their idle

states.

No “001” – Byte written got no

Acknow acknowledge.

ledge

Byte “100” Byte Byte of data received.

of

data

Error “011” – Something went wrong.

Byte- level responses level FSM

Implementation Results master and slave interfaces connected by an

interconnect fabric. Avalon-MM interfaces can

Setup 1 describe a wide variety of component interfaces,

Top level module: iicmb_m_wb.vhd. from SRAM interfaces which support simple, fixed-

Number of I2C buses (g_num_bus) = 1. cycle read and write transfers to more complex,

System clock frequency (g_f_clk) = 100 MHz. pipelined interfaces capable of burst transfers.

I2C bus clock frequency (g_f_scl_0) = 100 kHz.

Family Device Fmax Register Logics

Virtex-6 xc6vcx75t- 290MHz 649 757

2-ff484

Setup 2

Top level module: iicmb_m_wb.vhd.

Number of I2 C buses (g_num_bus) = 16.

System clock frequency (g_f_clk) = 100 MHz.

Example Slave Component

I2 C bus clock frequencies:

g_f_scl_0 = 100 kHz, g_f_scl_1 = 120 kHz,

Each signal in an Avalon-MM slave corresponds to

g_f_scl_2 = 130 kHz, g_f_scl_3 =

exactly one Avalon-MM signal role. An Avalon-

200 kHz, g_f_scl_4 = 50 kHz, others = 30 kHz.

MM port can use only one instance of each signal

role.

Family Device Fmax Register Logics

3.0 Inte rfaces with our design

Virtex-6 xc6vcx75t- 325MHz 154 264LUT

2-ff484 Avalon-MM version of the core top level has the

following signals:

Some of the basic features on which we are working There is no address signal in this group. This is

to implement in our design will be as follows, because we have only 4 bytes of registers and all of

them can be accessed in one single read or write.

Implementation of IICMB core which provides The frequency of clk clock (in kHz) should be

low-speed, two-wire, bidirectional serial bus indicated in g_f_clk parameter. For more

interfaces compliant to industry standard I2C information about Avalon-MM signals please refer

protocol. to Avalon Interface Specifications.

“Manchester encoded UART” which enables

running small peripherals with parasitic power

derived from the TXD line, and allowing large

clock differences typical of RC oscillators.

The key feature of the core is its ability to

effectively reducing complexity of the system

and control several connected I2C buses.

Avalon Memory-Mapped Inte rfaces

Avalon Memory-Mapped (Avalon-MM) interfaces

are used for read and write interfaces on master and

slave components in a memory- mapped system.

These components include microprocessors,

memories, UARTs, DMAs, and timers which have Top Level Entity for Avalon Interface

Implementation Results

Device Utilization Summary

Utiliz-

Slice Logic Utilization

Used Available ation

Number of Slice Registers 182 12,480 1%

Number used as Flip Flops 182

Number of Slice LUTs 318 12,480 2%

Number used as logic 307 12,480 2%

Number using O6 output only 280

Number using O5 output only 7

Number using O5 and O6 20

Number used as exclusive route-thru 11

Number of route-thrus 18

Number using O6 output only 17

Number using O5 and O6 1

Number of occupied Slices 147 3,120 4%

Number of LUT Flip Flop pairs used 375

Number with an unused Flip Flop 193 375 51%

Number with an unused LUT 57 375 15%

Number of fully used LUT-FF pairs 125 375 33%

Number of unique control sets 15

Number of slice register sites lost 22 12,480 1%

to control set restrictions

Number of bonded IOBs 59 172 34%

IOB Flip Flops 1

Internal Structure for Avalon Interfaces with our Number of BUFG/BUFGCTRLs 1 32 3%

design of I2CMB Number used as BUFGs 1

Average Fanout of Non-Clock Nets 4.36

Hierarchy Of Modules

Hierarchy of modules with Avalon-MM top level:

iicmb_pkg.vhd

Conclusion

iicmb_int_pkg.vhd

iicmb_m_av.vhd In this project work, the multi- master facility of I2C

o avalon_mm.vhd protocol is implemented successfully. Address

o regblock.vhd resolution is the major concern while using multiple

o iicmb_m.vhd masters in I2C bus. Arbitration procedure must be

mbyte.vhd perfect for the bus to work properly when dual

mbit.vhd masters are present. A dual master I2C bus

conditioner_mux.vhd controller system with an EEPROM 24CXX series

conditioner.vhd as the slave devices has been developed for

o filter.vhd realizing both the read and write cycles of the I2C

o bus_state.vhd bus and tested. The design has got successfully

implemented in Spartan 3A FPGA and the outputs

are verified. Also DS1307 RTC is connected as the [11] Spartan-3A/3AN FPGA Starter Kit Board

slave device and performed the WRITE and READ User Guide, Xilinx, version1.1, 2008.

operations following I2C protocol. This design can [12] Vincent Himpe, “Historical background of

be used in systems where multiple devices needs to I2C,” in Mastering the I2C Bus, Aachen,

be interconnected by ensuring with low complexity Germany: Elektor Verlag publications, 2011.

and efficient resource utilization. [13] Interfacing of digital TPH sensors with

FPGA using I2C interface. Muhammed Raees

References, PC, Anand Lokapure, Saraf Mandar N,

B.Satyanarayana. 2016 IEEE Bombay Section

[1] I2C Bus Specification, Philips Semiconductor, Symposium.

version 2.1, January 2000. [14] BMP280 Digital Pressure Sensor Data sheet,

[2] DS1307 64 x 8, Serial, I2C Real Time Clock, Bosch Sensortec, October 15th, 2015.

Maxim integrated, 2008. [15] AN10216-01 I2C Manual, Philips

[3] E. Allier, G. Sicard, L. Fesquet, and M. Semiconductor, March 2003.

Renaudin, “A new class of asynchronous A/D [16] Frank Vahid, “Hardware Description

converters based on time quantization,” in Language,” in Digital Design with RTL Design,

Proceedings of International Symposium on Verilog and VHDL, 2nd Ed. Katie Singleton Ed.

Asynchronous Circuits and Systems, May 2003, Hoboken, New Jersey: VP and Executive

pp. 196–205.. publisher, 2010, pp 487-532.

[4] Prototyping of Dual Master I2C Bus Controller,

Anagha A , M. Mathurakani, International

Conference on Communication and Signal

Processing, April 6-8, 2016, India.

[5] Prof. Jai Karan Singh et al “Design and

Implementation of I2C master controller on

FPGA using VHDL,” IJET, Aug-Sep 2012.

[6] Raj Kamal, “Devices and Communication Buses

for Devices Network,” in Embedded system:

Architecture programming and Design, Shalini

Jha Ed. New Delhi, India: Tata McGraw-Hill

Education, 2008, pp.160- 165.

[7] Implementation of I2C Master Bus Controller

on FPGA, Bollam Eswari, N.Ponmagal,

K.Preethi, S.G.Sreejeesh, International

conference on Communication and Signal

Processing, April 3-5, 2013, India

[8] I2C Hardware Master Serial Interface for

Asynchronous ADCs. Wojciech Andrysiewicz,

Dariusz Ko´scielnik, Marek Mi´skowicz AGH

University of Science and Technology. 2015

IEEE.

[9] A.P.Godse, D.A.Godse, “Bus Standards,” in

Microprocessors and its Applications, 3rd Ed.

Pune, India: Technical publications, 2008.

[10] Systems with PIC Microcontrollers:

Principles and Applications, 2nd Ed.Burlinton:

Newnes, 2009, pp.307-327.

Potrebbero piacerti anche

- Implementation of Inter-Integrated Circuit (I2C) Multiple Bus ControllerDocumento5 pagineImplementation of Inter-Integrated Circuit (I2C) Multiple Bus ControllerKumars tiwariNessuna valutazione finora

- Serial Interfaces PDFDocumento55 pagineSerial Interfaces PDFGaurav GrimReaper Roy100% (1)

- A Seminar On: Deekshith D PDocumento20 pagineA Seminar On: Deekshith D PmanjunathNessuna valutazione finora

- Inter Integrated CircuitDocumento14 pagineInter Integrated CircuitSurya ChandraNessuna valutazione finora

- FSM Implementation of I2C Protocol and Its Verification Using VerilogDocumento3 pagineFSM Implementation of I2C Protocol and Its Verification Using Verilogyogiyogi7474Nessuna valutazione finora

- Comunication With I2C Serial EEPROMDocumento25 pagineComunication With I2C Serial EEPROMEdwin Jhefren BlancoNessuna valutazione finora

- RD 1046Documento12 pagineRD 1046hxrxr880Nessuna valutazione finora

- I C Master With WISHBONE Bus Interface: FeaturesDocumento12 pagineI C Master With WISHBONE Bus Interface: FeaturesArley CortésNessuna valutazione finora

- Inter Integrated Circuit Implementation and ApplicationDocumento34 pagineInter Integrated Circuit Implementation and ApplicationAshokSiri100% (1)

- I2C Protocol Implementation: Guided By: MR .Y.V. Joshi Mr. Vaibbhav TaraateDocumento52 pagineI2C Protocol Implementation: Guided By: MR .Y.V. Joshi Mr. Vaibbhav TaraateOmprasad RathodNessuna valutazione finora

- Computing Machinery: Chapter 10: MicrocontrollersDocumento51 pagineComputing Machinery: Chapter 10: MicrocontrollersAkanksha SrivastavaNessuna valutazione finora

- Datasheet Interface I C PhilipsDocumento101 pagineDatasheet Interface I C PhilipsClovis Rodrigues100% (1)

- Section 19. Inter-Integrated Circuit™ (I C™) : HighlightsDocumento54 pagineSection 19. Inter-Integrated Circuit™ (I C™) : HighlightsAnkit GoyalNessuna valutazione finora

- I2C Interfacing To XC3S400 FPGADocumento14 pagineI2C Interfacing To XC3S400 FPGAMahesh BhatkalNessuna valutazione finora

- Serial InterfacesDocumento31 pagineSerial InterfacesNishanthNessuna valutazione finora

- Inter Integrated Circuit TrainingDocumento26 pagineInter Integrated Circuit Trainingsai saiNessuna valutazione finora

- EE6008 Unit 3Documento8 pagineEE6008 Unit 3TakeItEasyDude TIEDNessuna valutazione finora

- Aplicación de I Fpga C Bus Protocolo SobreDocumento4 pagineAplicación de I Fpga C Bus Protocolo Sobrecarlos huamanNessuna valutazione finora

- GC1000 GS Modbus 04 PDFDocumento6 pagineGC1000 GS Modbus 04 PDFmhafizanNessuna valutazione finora

- Inter-Integrated Circuit (I2C) : Karthik Hemmanur ECE 480-Design Team 3 Fall 2009Documento8 pagineInter-Integrated Circuit (I2C) : Karthik Hemmanur ECE 480-Design Team 3 Fall 2009gluciferNessuna valutazione finora

- I2c Bus Master PIC 16FXXDocumento61 pagineI2c Bus Master PIC 16FXXCamilo A. InfanteNessuna valutazione finora

- Philips I2c HandbookDocumento16 paginePhilips I2c HandbookEmílio Ferro100% (3)

- Lab 8 - I2CDocumento7 pagineLab 8 - I2CNhi MẫnNessuna valutazione finora

- Network Embedded 1631332270319Documento31 pagineNetwork Embedded 1631332270319neelakandan venkatramanNessuna valutazione finora

- DB I2c MS Avln DS V1 - 1Documento4 pagineDB I2c MS Avln DS V1 - 1duplicate accountNessuna valutazione finora

- Asic Implementation of I2c Master Bus Controller Firm Ip CoreDocumento13 pagineAsic Implementation of I2c Master Bus Controller Firm Ip CoreAnonymous e4UpOQEPNessuna valutazione finora

- I C Master With WISHBONE Bus Interface: FeaturesDocumento12 pagineI C Master With WISHBONE Bus Interface: FeaturessindNessuna valutazione finora

- Synchronous Serial IO: - Send A Separate Clock Line With DataDocumento42 pagineSynchronous Serial IO: - Send A Separate Clock Line With DataGigi KentNessuna valutazione finora

- Serial Communication Protocols Part 2: Nasif MDocumento26 pagineSerial Communication Protocols Part 2: Nasif MnobodyNessuna valutazione finora

- How To Use IIC Module On M68HC08, HCS08, and HCS12 Mcus: Application NoteDocumento18 pagineHow To Use IIC Module On M68HC08, HCS08, and HCS12 Mcus: Application NoteJuan CarlosNessuna valutazione finora

- Modem Roteado Guia de ConexãoDocumento12 pagineModem Roteado Guia de Conexãocaah.nliimaNessuna valutazione finora

- Design and Functional Verification of I2C Master Core Using OVMDocumento6 pagineDesign and Functional Verification of I2C Master Core Using OVMPraveen Kumar100% (1)

- I2c ProtocolDocumento28 pagineI2c Protocolishapatil86Nessuna valutazione finora

- 07 Comms Posted2Documento29 pagine07 Comms Posted2nirmaljohn1920Nessuna valutazione finora

- Es 2Documento31 pagineEs 2sanjay.sampath.kNessuna valutazione finora

- Debugging Low-Speed Serial Buses in Embedded System DesignsDocumento16 pagineDebugging Low-Speed Serial Buses in Embedded System Designstennis5luvNessuna valutazione finora

- Microcontroller Bootcamp (7) : The I C BusDocumento8 pagineMicrocontroller Bootcamp (7) : The I C BusMikko FagerlundNessuna valutazione finora

- ARM Question Bank Unit - 5Documento14 pagineARM Question Bank Unit - 5sakthivelv.eecNessuna valutazione finora

- Aardvark v3.30Documento62 pagineAardvark v3.30Agustín RamírezNessuna valutazione finora

- CC2500 Serial Transreceiver Wireless ModuleDocumento12 pagineCC2500 Serial Transreceiver Wireless ModuleadNessuna valutazione finora

- I2C Bus Specifications V2 0Documento13 pagineI2C Bus Specifications V2 0Gasthim KiranNessuna valutazione finora

- I2C TutorialDocumento9 pagineI2C TutorialLuis Angel Nina Sánchez100% (3)

- Chapter 5 Serial IO InterfaceDocumento51 pagineChapter 5 Serial IO InterfacetesfayebbNessuna valutazione finora

- SPI I2C Interface AnDocumento13 pagineSPI I2C Interface AnNivin PaulNessuna valutazione finora

- ELK455E Application-2018Documento36 pagineELK455E Application-2018Melek KüçükNessuna valutazione finora

- Power SequencerDocumento31 paginePower SequencerVenkatGollaNessuna valutazione finora

- Unit 3Documento56 pagineUnit 3TakeItEasyDude TIEDNessuna valutazione finora

- Computer Interfacinglecture3Documento20 pagineComputer Interfacinglecture3mohamed faragNessuna valutazione finora

- 006 I2C Bus ProtocolDocumento16 pagine006 I2C Bus Protocolcoolkunal77100% (1)

- CapstoneDocumento16 pagineCapstoneHarsh ShahNessuna valutazione finora

- A Good Dac DesignDocumento11 pagineA Good Dac DesignBhavin DesaiNessuna valutazione finora

- Aim of The Project: FeaturesDocumento4 pagineAim of The Project: FeaturesYeshoda MallikarjunaNessuna valutazione finora

- No3109 Datasheet TS8-32GEMC210 Formal Version V10Documento22 pagineNo3109 Datasheet TS8-32GEMC210 Formal Version V10Jhon Geimar Ortiz RodriguezNessuna valutazione finora

- Introduction To Microprocessor-Based ControlDocumento42 pagineIntroduction To Microprocessor-Based ControlAhdan FawwazNessuna valutazione finora

- Application Example: Data Logger With WWW ServerDocumento2 pagineApplication Example: Data Logger With WWW ServerahmedalgaloNessuna valutazione finora

- 20 C++ ATmega I2C Serial CommDocumento14 pagine20 C++ ATmega I2C Serial CommAnatronics LabNessuna valutazione finora

- General 2. SpecificationsDocumento8 pagineGeneral 2. SpecificationsapisituNessuna valutazione finora

- 4.1. Starting A SwitchDocumento34 pagine4.1. Starting A SwitchQuân Lâm MinhNessuna valutazione finora

- ES 2023 L7b Embedded System Interfacing Serial IO LIN Bus Lecture 8Documento16 pagineES 2023 L7b Embedded System Interfacing Serial IO LIN Bus Lecture 8Samkelo MavimbelaNessuna valutazione finora

- Natraj Servlet2015Documento148 pagineNatraj Servlet2015Prasad100% (1)

- ConvateDocumento23 pagineConvateConvate100% (2)

- Informatica PowerCenter 9.0 Mapping Architect For Visio GuideDocumento74 pagineInformatica PowerCenter 9.0 Mapping Architect For Visio GuideDipankarNessuna valutazione finora

- Understanding End-To-End 5G Transport NetworksDocumento32 pagineUnderstanding End-To-End 5G Transport NetworksTrịnhVạnPhướcNessuna valutazione finora

- A60d2c7f01f192 - 1624426480.a60d2c7f01eff2.suraj - D BHAT - CVDocumento1 paginaA60d2c7f01f192 - 1624426480.a60d2c7f01eff2.suraj - D BHAT - CVKunal NagNessuna valutazione finora

- Google Cloud Analytics LakehouseDocumento47 pagineGoogle Cloud Analytics LakehouseJavierNessuna valutazione finora

- BOPF Sample CodeDocumento10 pagineBOPF Sample CodeRakesh RaparthiNessuna valutazione finora

- ck7w User and Installation GuideDocumento112 pagineck7w User and Installation GuideAleksandar KondićNessuna valutazione finora

- RAD Ethernet OAM GuideDocumento7 pagineRAD Ethernet OAM GuidesgunjkarNessuna valutazione finora

- Unit 2 Use and Access Business Tools and TechnologyDocumento9 pagineUnit 2 Use and Access Business Tools and TechnologyPeterson Angelo DuterteNessuna valutazione finora

- Terms & Conditions GeneratorDocumento23 pagineTerms & Conditions GeneratorTermsFeedNessuna valutazione finora

- Jagran Lakecity University, Bhopal: Course Code: BCAC402 Course Name: Operating SystemDocumento2 pagineJagran Lakecity University, Bhopal: Course Code: BCAC402 Course Name: Operating Systemritika nigadeNessuna valutazione finora

- Seeing Cities Through Big Data - Research, Methods and Applications in Urban InformaticsDocumento553 pagineSeeing Cities Through Big Data - Research, Methods and Applications in Urban InformaticsGilang Muhammad RamadhanNessuna valutazione finora

- TLE Computer System Servicing: Quarter 1 - Module 3: Performing Computer Operations (Part 2)Documento33 pagineTLE Computer System Servicing: Quarter 1 - Module 3: Performing Computer Operations (Part 2)George Garcia100% (1)

- Mtorrent: A Multicast Enabled Bittorrent ProtocolDocumento63 pagineMtorrent: A Multicast Enabled Bittorrent ProtocolTuyet TamNessuna valutazione finora

- Major Project ReportDocumento31 pagineMajor Project Reportdejeme8956Nessuna valutazione finora

- A Seminar Report On Real Time Operating PDFDocumento24 pagineA Seminar Report On Real Time Operating PDFAsfiya syedaNessuna valutazione finora

- Online Blood Donation Database Management SystemDocumento27 pagineOnline Blood Donation Database Management SystemRaj Bangalore44% (9)

- h323 Isdn CallfailureDocumento4 pagineh323 Isdn Callfailureapi-19663123Nessuna valutazione finora

- CS8791 Cloud ComputingDocumento52 pagineCS8791 Cloud Computingankur881120Nessuna valutazione finora

- UD22321B Baseline User-Manual-of-NVR V4.30.210 20201208Documento96 pagineUD22321B Baseline User-Manual-of-NVR V4.30.210 20201208Mahmoud AhmedNessuna valutazione finora

- 3161 OverlayDocumento9 pagine3161 Overlayapi-3788255Nessuna valutazione finora

- Intro To Adobe Character AnimatorDocumento8 pagineIntro To Adobe Character AnimatorBistirna HaldarNessuna valutazione finora

- RPOS Training March 2015 1Documento159 pagineRPOS Training March 2015 1Clement StanislausNessuna valutazione finora

- Balakrishna Java Lab ManualDocumento45 pagineBalakrishna Java Lab ManualchandukaturiNessuna valutazione finora

- Cisco TAC Entry Training - 11 - Enhanced Interior Gateway Protocol (EIGRP)Documento53 pagineCisco TAC Entry Training - 11 - Enhanced Interior Gateway Protocol (EIGRP)FerasHamdanNessuna valutazione finora

- 47ESS - Assignment Manager ConfigurationDocumento26 pagine47ESS - Assignment Manager ConfigurationAkhamiePatrickOshiokeNessuna valutazione finora

- Test Cscu: AnswersDocumento5 pagineTest Cscu: AnswersBédjé Roy Willy AbossanNessuna valutazione finora

- Top Down Modeling and Test Bench Development: Verification Case Study: Pipeline ADCDocumento54 pagineTop Down Modeling and Test Bench Development: Verification Case Study: Pipeline ADChariprasad12345Nessuna valutazione finora

- MCP S10 Read04 ReadersWritersDocumento2 pagineMCP S10 Read04 ReadersWritersFirzhan NaqashNessuna valutazione finora