Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

High Swing Power Amplifier

Caricato da

Syed AfzalTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

High Swing Power Amplifier

Caricato da

Syed AfzalCopyright:

Formati disponibili

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 27, NO. 7.

JULY 1992 1089

Special Brief Papers

Class-AB High-Swing CMOS Power Amplifier

F . Mistlberger and R. Koch

Abstract-For power amplifiers there is a need to combine 11. PSEUDO-SOURCE-FOLLOWER OUTPUT

small area and low quiescent power consumption with large

peak currents and high output voltage swing. For a single 5-V The maximum possible output voltage swing of CMOS

supply, drain-coupled near class-A output stages are the best operational amplifiers is achieved with drain-coupled

solution to this. These stages, however, suffer from large quies- complementary output transistors. However, simple

cent current variations and/or crossover distortion. A power structures of this type suffer from the additional pole in-

amplifier for a loudspeaker and, in a smaller version, for the troduced in this stage and from load-dependent gain of the

earpiece of a telephone are presented, where new solutions have

been implemented to solve these problems. The amplifier has output stage. Source-follower stages, on the other hand,

1.2-mA quiescent current, 64-mA peak current, and >60 dB have insufficient voltage swing. One structure frequently

WTHD with 3.2-V output swing into a 2 5 4 load. used [3], [4] to overcome this problem is the pseudo

source follower (PSF) comprising a complementary drain-

connected output pair and one so-called error amplifier

I. INTRODUCTION per transistor (Fig. 2 ) . The complete structure operates in

D RIVEN by the requirement to reduce costs and to

achieve a maximum amount of flexibility, it is nec-

essary to integrate power amplifiers in telecom CMOS

unity-gain configuration. The error amplifiers are able to

drive the gates of the output transistors with a large dy-

namic voltage swing so these can be reduced in area. For

chips. These amplifiers often have to fulfill contradictory moderate distortion requirements the output transistors can

requirements like low quiescent current for minimum even be driven into the triode region. The major drawback

power consumption, large signal currents, high output of the PSF in its basic form is the sensitivity of the quies-

swing, and low distortion. In the following pages a power cent current and consequently of the standby power con-

amplifier for a loudspeaker and the earpiece of a telephone sumption to the offset voltage mismatch of the two error

subset, integrated in the codec chip ARCOFI-SP (Audio amplifiers. The quiescent current varies proportionally to

Ringing Codec Filter featuring Speakerphone Function), the product of offset voltage mismatch and gain of the

are presented. The ARCOFI-SP is part of a subscriber PSF stage. Taking into account that the offset voltages are

telephone chip set. The analog section of the receive path in the range of a few millivolts and using a small-signal

(Fig. 1) comprises a low-noise (105-dB SNR) program- model, the quiescent current variation calculates to

mable gain microphone amplifier with a maximum gain

I=g; VGS for one output transistor

of 30 dB followed by a 16-b second-order sigma-delta

A/D converter. The analog section of the transmit path VGS = U V,, for one output transistor

consists of two 16-b second-order sigma-delta D/A con-

verters, one driving a pair of handset amplifiers for 200-Q I= U g, 1/2 V,, since V,, averages

differential load and the other one a pair of loudspeaker with both branches assumed to have equal values of open-

amplifiers for 5 0 4 differential load. The loudspeaker am- loop gain of each error amplifier ( U ) , transconductance of

plifier is described below. A digital signal processor cal- each output transistor (g,), gate-to-source voltage of each

culates the filter functions and handles frequency and tone output transistor (V,,), and offset voltage difference of the

generation. error amplifiers (V,, ) .

The target specifications for the power amplifier are To keep the quiescent current variation reasonably low,

given in Table 1. The moderate requirements for the signal- only an open-loop gain of around 20 dB or less is allowed.

to-noise ratio allowed optimization of current and area Therefore, a high-gain preamplifier stage is necessary to

consumption at the cost of increased harmonic distortion. get enough loop gain for S/THD, PSR, etc. requirements.

A common extension of the PSF approach adds an ad-

Manuscript received December 9, 1991; revised March 17, 1992.

The authors are with Siemens AG, W-8000 Munich 80, Germany.

ditional complementary source-follower (SF) stage with

IEEE Log Number 9200845. relatively small transistor size and current consumption

0018-92001’92$03.000 1992 IEEE

1090 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 21, NO. I, JULY 1992

XlNP

XlNN

MIP

MIN

' FHM

LSP

LSN

D-- HOP

HON

1 VREF +1wnF 1 DCUCLK RS SP2

FSC SPl

1

VSSP VSSA VSSD

Fig. 1. ARCOFI-SP block diagram. AMI: microphone amplifier; ALS: loudspeaker amplifier; AHO: handset earpiece ampli-

fier.

TABLE I Preamp Preamp din control Pseudo source-follower

POWERAMPLIFIER

PERFORMANCE

DATA output stages stage source

follower

Specification Measured

Supply voltage 5V+5% 5 v

Diff voltage swing 32VPP 4VPP

Peak current 64 mA 80 mA

Power into load 102 mW 160mW

Load 25 0 25 0 OUT

S/N +THD 55 dBm 70 dBm

Quiescent power dissipation 20 mW 6 mW

Signal frequency range 34kHz 34kHz

Slew rate 15V/p

Area 1 mm2

Technology 2-pm CMOS double metal,

double polysilicon

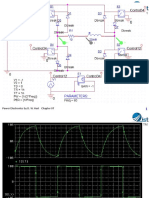

Fig. 3 . Simplified power amplifier schematic.

Preamp Preamp Pseudo-source-follower

output stages SOYrCe

However, a new problem arises with this type of cir-

cuit. To minimize takeover distortion the two output

stages have to track. This can be achieved when the two

preamplifier outputs are connected, so that the SF and PSF

are driven by the same node [ 5 ] . The voltage swing of the

SF-related output (Ml-M4), however, is limited by the

number of stacked transistors. Since both preamp outputs

are connected, the distortion level of the output driving

the PSF ( M 5 , M 6 ) starts to increase as soon as the

SF-related output is driven into triode region and the out-

put swing of the PSF output is then limited.

A better solution can be achieved when SF- and PSF-

Fig. 2. Pseudo source follower plus standard source follower. related preamp outputs are not directly coupled. It is,

however, necessary to guarantee tracking of both outputs.

to the output (Fig. 2). For small output voltages the PSF By implementation of an additional amplifier as shown in

stage is turned off, e.g., by an intentionally built-in offset Fig. 3 , tracking of the low-swing SF driving output to the

voltage, and only the standard SF is active. By this means high-swing PSF driving output of the preamplifier can be

a quiescent current of zero is possible for the large PSF achieved. The functional principle is similar to that often

output transistors and the problem of variation due to off- used in single-ended-to-differential conversion. The ad-

set mismatch is solved. For larger output voltages the PSF ditional amplifier-in our case a differential stage-mon-

output transistors take over. itors both preamp outputs and controls the SF-related out-

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 27, NO. 7, JULY 1992 1091

put by means of the additional current source (M11). The

size of transistor M4 has to be reduced accordingly. For

low and medium output voltages, the SF output tracks the

PSF output voltage with small error. For large output

swings, transistor M1 or M4, depending on the sign, is

pushed into the triode region and causes the correspond-

ing SF output transistor to be turned off. Then only the

PSF output is active.

111. ERRORAMPLIFIERS

An often-used topology for the error amplifiers is a

standard differential stage with current mirror load as

shown in Fig. 4 together with the corresponding n-channel

output transistor. For the upper branch of the output the L - - - - - - _ - - . - - - - - - -

same structure is used with n and p transistors exchanged. Fig. 4. Standard error amplifier.

The maximum voltage swing on the gate of the output

transistor of the structure shown can be approximately de- ~ . . . . . . . . .. . . . . . . . . . . ,

rived as follows: 1 : I

VGSM10 - VGSMl - vD\atMI

with

VGSMI = VTMI+ I/GSeffMI

and

vGSeffM1 - VDsatM1

we get

VGSMIO= Vin

With V,,, = Vi, and the condition V,,,

- VTM,.

-

VDsatMI0we get

the maximum voltage swing on the gate of M10, which

. _ _ . _ _ . . . . . . . _ _ _ _ _ _ _ _ _ _

1

Fig. 5. Improved error amplifier for NMOS output transistor.

1 , l

evidently occurs for the minimum value of V,,,, to be

VGSrnax = VDsatM1O - VTMl - v. where

. For low values of Vi, a large VGSM10is needed but only a I/DsatM5 - vGSeffM5

low value is possible. The limited common-mode range

of the error amplifier versus V,, also limits the output volt- and

age swing of the whole amplifier. VGSeffM5 = VDD - - VGSM7 - V G S M 2 .

An improved version of an error amplifier is shown in

Fig. 5 . The additional current mirror stage M5,M 6 in- Assuming VGSM7and VGsM2equal in value (but opposite

troduces the phase inversion needed to tie the gate of out- in sign) we get

put transistor M10 to the noninverting output of the dif- VDtatM5 = VDD -

ferential stage. Now the buffer output voltage and the

differential-stage output voltage have the same sign and which shows that VDsatM5 can nearly reach the supply

move more or less in parallel. With the differential stage voltage. To ensure a high gate voltage swing for M10,

of Fig. 4, however, the negative output swing would be however, VDsatM5 should be smaller than V / 2 leaving

DD I

limited to about one threshold voltage above ground. With more than vDD/2 for VGSMIO,e.g., VDsatM5 = 71/00 gives

the addition of the source followers the common-mode VGSM,, = VDD 2/3 - 3.3 V

range of the differential stage is extended to ground. The

asymmetrical loads in the differential stage of Fig. 5 de- which is about twice the value achieved with the standard

liver the built-in offset voltage needed to ensure zero configuration.

quiescent current in the output transistor M10.

The maximum gate voltage on the gate of the output IV. MEASURED RESULTS

transistor of M10 now calculates to: A schematic of the complete power amplifier is shown

in Fig. 6. The amplifier is fabricated in a 2-pm double-

VGSM,O = VGSM6

polysilicon, double-metal-layer process. Fig. 7 is a pho-

VGSM6 = VDD - VDsat M 5 tomicrograph of two amplifiers in bridge configuration.

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 21, NO. 7 . JULY 1992

3 ,

out

’ OTA ’ PSF ’ ’ SF ’ Erroramp ’ Erroramp ’

PSF Output , S F Output

Bias ’ Preamp ’ drive ’ s , = ~ e d r l v y for PMOS ’ tor NMOS ’

Fig. 6. Schematic of the complete power amplifier.

8.0 1.6 2.0 3.0 4.0 5.6 6.0 7.8 9.0 9.6 18.8

F r e q u e n z CkHzl

Fig. 8. Output spectrum for 7.4-V, output signal at 1 kHz into 50-n load.

The amplifier is in the bridge configuration ( V = 4.5 dB).

Fig. 7. Photomicrograph of two power amplifiers in bridge configuration.

ACKNOWLEDGMENT

Low-resistive connections via double bonding must be The authors wish to thank E. Engelhardt for the layout

provided for the high currents of up to k64 mA. In the of the amplifier and J. Feldmann for helpful discussions.

complete ARCOFI circuit the power amplifiers have their

own power supplies separated from the other chip sup- REFERENCES

plies. The width of the supply lines is 100 pm maximum. [ l ] J. A. Fisher and R . Koch, “A highly linear buffer amplifier,” IEEE

The measured results summarized in Table I were taken J . Solid-Stare Circuits, vol. SC-22, pp. 330-334, June 1987.

from two amplifiers set up in bridge connection. The dif- [2] L. Tomasini et al., “A low-voltage high-drive differential amplifier

for ISDN applications, ” in Proc. ESSCIRC’88.

ferential load consisted of a 5 0 4 resistor in parallel with [3] J. A . Fisher, “A high performance CMOS power amplifier,” IEEE J .

a 300-pF capacitor. Fig. 8 shows the distortion of the am- Solid-state Circuits, vol. SC-20, pp. 1200-1205, Dec. 1983.

plifier at 1 kHz with an output voltage of 7.4 Vp.p. The [4] K . E. Brehmer and J. B. Wieser, “Large swing CMOS power arnpli-

fier,” IEEE J . Solid-State Circuits, vol. SC-18, pp. 624-629, Dec.

second and third harmonic coefficients are below 75 dB, 1983.

which is far better than specified so that further optimi- [5] K. Nagaraj, “Large-swing CMOS buffer amplifier,” IEEE J . Solid-

zation of the circuit towards reduced area and current con- State Circuits, vol. 24, pp. 181-183, Feb. 1989.

[6] D. M. Monticelli, “A quad CMOS single-supply op amp with rail-to-

sumption is possible. The measured differential PSRR at rail output swing,” IEEEJ. Solid-state Circuits, vol. SC-21, pp. 1026-

1 kHz is better than 80 dB and at 1 MHz it is still 35 dB. 1034, Dec. 1986.

Potrebbero piacerti anche

- 169 T562 PDFDocumento5 pagine169 T562 PDFYulian Deni AdhitamaNessuna valutazione finora

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesDa EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesValutazione: 5 su 5 stelle5/5 (1)

- Power Amplifier - Research PaperDocumento5 paginePower Amplifier - Research PaperIsmail DarNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- ECE3204 D2013 Lab2Documento9 pagineECE3204 D2013 Lab2Khalil2097Nessuna valutazione finora

- Application Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Documento16 pagineApplication Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Nagendra ChaitanyaNessuna valutazione finora

- Telescopic Amplifier ProjectDocumento6 pagineTelescopic Amplifier ProjectSucharitha ReddyNessuna valutazione finora

- Current Feedback Amplifiers Benefit High Speed Designs Franco EDN 010589Documento10 pagineCurrent Feedback Amplifiers Benefit High Speed Designs Franco EDN 010589Pedro LimaNessuna valutazione finora

- ARF440Documento14 pagineARF440Kiri ScalesNessuna valutazione finora

- Design and Simulation of High-Swing Fully Differential Telescopic Op-AmpDocumento9 pagineDesign and Simulation of High-Swing Fully Differential Telescopic Op-AmpCSIT iaesprimeNessuna valutazione finora

- 2-15-1381147174-25 .Design of 1 V.FULL PDFDocumento10 pagine2-15-1381147174-25 .Design of 1 V.FULL PDFABHILASH RAINessuna valutazione finora

- Design of CMOS Fully Differential Operational Transconductance AmplifierDocumento24 pagineDesign of CMOS Fully Differential Operational Transconductance AmplifierAbhijit Kuvar100% (2)

- Single Stage and Two Stage OP-AMP Design in 180NM CMOS TechnologyDocumento7 pagineSingle Stage and Two Stage OP-AMP Design in 180NM CMOS TechnologyIJSTE0% (1)

- OpampDocumento51 pagineOpampMitesh BhagoraNessuna valutazione finora

- Transformer-Coupled Front-End For Wideband A/D Converters: Primary SecondaryDocumento4 pagineTransformer-Coupled Front-End For Wideband A/D Converters: Primary SecondaryAvinash SharmaNessuna valutazione finora

- Am Am: QRP QRPDocumento6 pagineAm Am: QRP QRPagama1188Nessuna valutazione finora

- Qbank Edc PTT1 Ao3iDocumento12 pagineQbank Edc PTT1 Ao3iOTHEOZ NFTNessuna valutazione finora

- HG DS1Documento6 pagineHG DS1moonofvuNessuna valutazione finora

- Telescopic PDFDocumento8 pagineTelescopic PDFdemodemo321123Nessuna valutazione finora

- Output 2Documento10 pagineOutput 2abdul shaggyNessuna valutazione finora

- A Rail-To-Rail Constant Gain Buffered Op-Amp For Real Time Video ApplicationsDocumento8 pagineA Rail-To-Rail Constant Gain Buffered Op-Amp For Real Time Video Applicationskvpk_vlsiNessuna valutazione finora

- Lic May-June 2017Documento15 pagineLic May-June 2017santhosh sekarNessuna valutazione finora

- Am Am: QRP QRPDocumento6 pagineAm Am: QRP QRPagama1188Nessuna valutazione finora

- Amplifier A PrelabDocumento7 pagineAmplifier A Prelabatomking73Nessuna valutazione finora

- Analog Circuits-II Answer KeyDocumento30 pagineAnalog Circuits-II Answer KeyreneeshczNessuna valutazione finora

- V/F Converter Ics Handle Frequency-To-Voltage Needs: The Art of CompromiseDocumento8 pagineV/F Converter Ics Handle Frequency-To-Voltage Needs: The Art of CompromiseAlim SheikhNessuna valutazione finora

- Design of 16 Channel R.F. Mixer: Olawoye T. O. and Stephen-Lemo O. KDocumento6 pagineDesign of 16 Channel R.F. Mixer: Olawoye T. O. and Stephen-Lemo O. KDelos Santos JojoNessuna valutazione finora

- LAB Purpose and Background: Crossover Distortion, Results When The Base Emitter Junctions of Both The TransistorsDocumento4 pagineLAB Purpose and Background: Crossover Distortion, Results When The Base Emitter Junctions of Both The TransistorsTi NaNessuna valutazione finora

- CT LMDocumento44 pagineCT LMNikhil KolheNessuna valutazione finora

- Cascading Precision Op Amp Stages For Optimal AC and DC PerformanceDocumento9 pagineCascading Precision Op Amp Stages For Optimal AC and DC PerformanceNur CaatoNessuna valutazione finora

- Slyt155 - An Audio Circuit Collection 1Documento6 pagineSlyt155 - An Audio Circuit Collection 1EduardoSánchezNessuna valutazione finora

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDocumento4 pagineA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinNessuna valutazione finora

- UNIT-1 Basics of Operational Amplifiers: EC8453-Linear Integrated Circuits Dept of ECE/PECDocumento16 pagineUNIT-1 Basics of Operational Amplifiers: EC8453-Linear Integrated Circuits Dept of ECE/PECIniyan RaviNessuna valutazione finora

- Design of Two Stage Op-AmpDocumento4 pagineDesign of Two Stage Op-AmpWARSE JournalsNessuna valutazione finora

- The Ovation E-Amp: A 180 W High-Fidelity Audio Power AmplifierDocumento61 pagineThe Ovation E-Amp: A 180 W High-Fidelity Audio Power AmplifierNini Farribas100% (1)

- Ie CepDocumento11 pagineIe Cepabdul shaggyNessuna valutazione finora

- New Lab Manual (ECA)Documento50 pagineNew Lab Manual (ECA)Shrinivas SaptalakarNessuna valutazione finora

- Amplificatore Audio AMDocumento5 pagineAmplificatore Audio AMEchizen KinichiNessuna valutazione finora

- Ee410 Final Design ProjectDocumento4 pagineEe410 Final Design Projectapi-294954225Nessuna valutazione finora

- Application of Transistor As AnDocumento16 pagineApplication of Transistor As AnSudhagar KingNessuna valutazione finora

- Module 2 Op-AmpDocumento26 pagineModule 2 Op-AmpSTUDENTS OF DOE CUSATNessuna valutazione finora

- MWRDocumento11 pagineMWRDhananjaya DhanuNessuna valutazione finora

- How To Build Linear FM 50watt With BLY90 (Circuit Diagram)Documento7 pagineHow To Build Linear FM 50watt With BLY90 (Circuit Diagram)mohamed lamine elbiskriNessuna valutazione finora

- Lic QBDocumento17 pagineLic QBsujaganesan2009Nessuna valutazione finora

- 19ec401 - Ec1 - 2021 - 2022 Lab Manual PDFDocumento53 pagine19ec401 - Ec1 - 2021 - 2022 Lab Manual PDFKarthi&coNessuna valutazione finora

- Experiment #3 Buffer Amplifier: R8 22K U1 LM318 C6 0.1 Uf C5 0.1 Uf C7 0.1 UfDocumento9 pagineExperiment #3 Buffer Amplifier: R8 22K U1 LM318 C6 0.1 Uf C5 0.1 Uf C7 0.1 UfDaniel Cafu100% (1)

- Lab 2 Basic CMOS AmplifiersDocumento5 pagineLab 2 Basic CMOS AmplifiersJatinKumarNessuna valutazione finora

- Controlling Switch-Node Ringing in Synchronous Buck ConvertersDocumento5 pagineControlling Switch-Node Ringing in Synchronous Buck ConvertersDmytro RakNessuna valutazione finora

- A High Gain, Fully Differential Single Stage Folded Cascade Op-Amp With 1GHZ BandwidthDocumento5 pagineA High Gain, Fully Differential Single Stage Folded Cascade Op-Amp With 1GHZ BandwidthJournal of Telecommunications0% (1)

- FJRX 84 EngDocumento22 pagineFJRX 84 EngPalade LiviuNessuna valutazione finora

- Advanced 80m-ARDF Receiver: - Version 4 Nick Roethe, DF1FODocumento22 pagineAdvanced 80m-ARDF Receiver: - Version 4 Nick Roethe, DF1FOPalade LiviuNessuna valutazione finora

- Motorola High Fidelity Amplifer 200WDocumento24 pagineMotorola High Fidelity Amplifer 200Wregelemar100% (2)

- 100 and 200 Watt High Fidelity Audio Amplifiers Utilizing A Widebandćlow Feedback Design An1308Documento24 pagine100 and 200 Watt High Fidelity Audio Amplifiers Utilizing A Widebandćlow Feedback Design An1308alvarodellanaveNessuna valutazione finora

- 300 Watt Fet Amp Apt9801Documento6 pagine300 Watt Fet Amp Apt9801Stephen Dunifer100% (9)

- A-20v eDocumento4 pagineA-20v eJorge EtcheverriaNessuna valutazione finora

- Advanced Electronics Lab ManualDocumento88 pagineAdvanced Electronics Lab ManualsmganorkarNessuna valutazione finora

- Mechnotes: Electrical and Electronics EngineeringDocumento17 pagineMechnotes: Electrical and Electronics EngineeringRanchuNessuna valutazione finora

- 1985 IssccDocumento3 pagine1985 IssccfrostyfoleyNessuna valutazione finora

- LicaDocumento215 pagineLicaEnoch TonyNessuna valutazione finora

- Power Electronics by D. W. Hart Chapter 07Documento25 paginePower Electronics by D. W. Hart Chapter 07Syed AfzalNessuna valutazione finora

- Power Electronics by D. W. Hart Chapter 03Documento20 paginePower Electronics by D. W. Hart Chapter 03Syed AfzalNessuna valutazione finora

- Chapter 2 SignalsDocumento53 pagineChapter 2 SignalsSyed AfzalNessuna valutazione finora

- 2 PerceptionGDocumento37 pagine2 PerceptionGSyed AfzalNessuna valutazione finora

- 1 IntroductioDocumento16 pagine1 IntroductioSyed AfzalNessuna valutazione finora

- Pspice Simulation of Feedback Control: Power Electronics by D. W. Hart Chapter 07Documento19 paginePspice Simulation of Feedback Control: Power Electronics by D. W. Hart Chapter 07Syed AfzalNessuna valutazione finora

- 7.13 Power Supply Control Input Voltage and Duty Ratio.: Power Electronics by D. W. Hart Chapter 07Documento12 pagine7.13 Power Supply Control Input Voltage and Duty Ratio.: Power Electronics by D. W. Hart Chapter 07Syed AfzalNessuna valutazione finora

- Power Electronics by D. W. Hart Chapter 07Documento25 paginePower Electronics by D. W. Hart Chapter 07Syed AfzalNessuna valutazione finora

- Power Electronics by D. W. Hart Chapter 07Documento18 paginePower Electronics by D. W. Hart Chapter 07Syed AfzalNessuna valutazione finora

- Be Less Than The DC Term (Average Value)Documento28 pagineBe Less Than The DC Term (Average Value)Syed AfzalNessuna valutazione finora

- Power Electronics by D. W. Hart Chapter 06Documento19 paginePower Electronics by D. W. Hart Chapter 06Syed AfzalNessuna valutazione finora

- Power Electronics by D. W. Hart Chapter 03Documento15 paginePower Electronics by D. W. Hart Chapter 03Syed AfzalNessuna valutazione finora

- Creating A DC Voltage From An AC Source: Power Electronics by D. W. Hart Chapter 03Documento41 pagineCreating A DC Voltage From An AC Source: Power Electronics by D. W. Hart Chapter 03Syed AfzalNessuna valutazione finora

- Power Electronics by D. W. Hart Chapter 06Documento10 paginePower Electronics by D. W. Hart Chapter 06Syed AfzalNessuna valutazione finora

- Continuous-Current Case: Power Electronics by D. W. Hart Chapter 06Documento20 pagineContinuous-Current Case: Power Electronics by D. W. Hart Chapter 06Syed AfzalNessuna valutazione finora

- Power Electronics by Daniel W. Hart Chapter 04Documento4 paginePower Electronics by Daniel W. Hart Chapter 04Syed AfzalNessuna valutazione finora

- Pe 36 Ee17Documento21 paginePe 36 Ee17Syed AfzalNessuna valutazione finora

- For Different Values of ALPHA: Power Electronics by D. W. Hart Chapter 03Documento16 pagineFor Different Values of ALPHA: Power Electronics by D. W. Hart Chapter 03Syed AfzalNessuna valutazione finora

- Power Electronics by D. W. Hart Chapter 07Documento13 paginePower Electronics by D. W. Hart Chapter 07Syed AfzalNessuna valutazione finora

- Power Electronics by Daniel W. Hart Chapter 05Documento20 paginePower Electronics by Daniel W. Hart Chapter 05Syed AfzalNessuna valutazione finora

- Pe 26 Ee17Documento23 paginePe 26 Ee17Syed AfzalNessuna valutazione finora

- Assignment #02 - 15 Oct To 22 Oct 2021Documento21 pagineAssignment #02 - 15 Oct To 22 Oct 2021Syed AfzalNessuna valutazione finora

- Power Electronics by Daniel W. Hart Chapter 01Documento19 paginePower Electronics by Daniel W. Hart Chapter 01Syed AfzalNessuna valutazione finora

- Full-Wave Rectifier With RL-Source Load-Continuous Current: Power Electronics by D.W.Hart Chapter 04Documento20 pagineFull-Wave Rectifier With RL-Source Load-Continuous Current: Power Electronics by D.W.Hart Chapter 04Syed AfzalNessuna valutazione finora

- Power Electronics by D.W.Hart Chapter 04Documento12 paginePower Electronics by D.W.Hart Chapter 04Syed AfzalNessuna valutazione finora

- Power Electronics by Daniel W. Hart Chapter 04Documento13 paginePower Electronics by Daniel W. Hart Chapter 04Syed AfzalNessuna valutazione finora

- Reducing Load Current Harmonics: Power Electronics by D. W. Hart Chapter 03Documento5 pagineReducing Load Current Harmonics: Power Electronics by D. W. Hart Chapter 03Syed AfzalNessuna valutazione finora

- Circuit For Forced Response From Ac Source : Power Electronics by D. W. Hart Chapter 03Documento21 pagineCircuit For Forced Response From Ac Source : Power Electronics by D. W. Hart Chapter 03Syed AfzalNessuna valutazione finora

- Resistive Load Creating A DC Component Using An Electronic SwitchDocumento22 pagineResistive Load Creating A DC Component Using An Electronic SwitchSyed AfzalNessuna valutazione finora

- Fourier Series For A Periodic Function F (T) : Power Electronics by D. W. Hart Chapter 02Documento43 pagineFourier Series For A Periodic Function F (T) : Power Electronics by D. W. Hart Chapter 02Syed AfzalNessuna valutazione finora

- Edc Lab Manuals Third SemesterDocumento56 pagineEdc Lab Manuals Third SemesterSprout GigsNessuna valutazione finora

- Electronic Devices and Amplifiers RevDocumento12 pagineElectronic Devices and Amplifiers RevHash FalahiNessuna valutazione finora

- Assignment 1 - LaurenteDocumento2 pagineAssignment 1 - LaurenteMiguel LaurenteNessuna valutazione finora

- 32W Hi-Fi Audio Power Amplifier: DescriptionDocumento13 pagine32W Hi-Fi Audio Power Amplifier: Descriptionlaluzul hadiNessuna valutazione finora

- EC1001 Course HandoutDocumento7 pagineEC1001 Course HandoutKaushik kumarNessuna valutazione finora

- Electronic Devices Lab - Exp - 7 - Student - Manual (Summer 18-19)Documento4 pagineElectronic Devices Lab - Exp - 7 - Student - Manual (Summer 18-19)MD MONIM ISLAMNessuna valutazione finora

- Ldic-2 Eee PDFDocumento249 pagineLdic-2 Eee PDFTarun PrasadNessuna valutazione finora

- Analog Lab ManualDocumento57 pagineAnalog Lab ManualMukesh Sahu100% (1)

- GO THROUGH ONCE Basics of Digital ElectronicsDocumento12 pagineGO THROUGH ONCE Basics of Digital ElectronicscanilreddyNessuna valutazione finora

- BEEE 2333 - Lab 3 Common Source JFET AmplifierDocumento9 pagineBEEE 2333 - Lab 3 Common Source JFET AmplifierDammahom LuriahkNessuna valutazione finora

- Analogy Digital Electronics Q&ADocumento8 pagineAnalogy Digital Electronics Q&AShivansh KulpehraNessuna valutazione finora

- LT1766 LinearTechnology Elenota - PLDocumento28 pagineLT1766 LinearTechnology Elenota - PLfenix1233Nessuna valutazione finora

- JFET AC Equivalent CircuitsDocumento42 pagineJFET AC Equivalent Circuitssakuntala barikNessuna valutazione finora

- Amp. de InstrumentacionDocumento11 pagineAmp. de InstrumentacionArciniega GuillermoNessuna valutazione finora

- Last Lab ReportDocumento9 pagineLast Lab ReportPearl ArcamoNessuna valutazione finora

- Activity 6Documento10 pagineActivity 6Ultima_SarinNessuna valutazione finora

- EEEB273 N05 - Diff Amp BJT x6 PDFDocumento7 pagineEEEB273 N05 - Diff Amp BJT x6 PDFNur AdhiraaNessuna valutazione finora

- Dsa 529802Documento56 pagineDsa 529802Ananda KrishnaNessuna valutazione finora

- slvt145hDocumento77 pagineslvt145hgubiliNessuna valutazione finora

- Canon 7161 Service ManuelDocumento346 pagineCanon 7161 Service ManuelkopisanNessuna valutazione finora

- Handling of Sensor Bridge OffsetDocumento6 pagineHandling of Sensor Bridge OffsetAsdrubale Mancupacapa ArrivoNessuna valutazione finora

- A Design Methodology Using The Inversion Coefficient For Low-Voltage Low-Power CMOS Voltage ReferencesDocumento11 pagineA Design Methodology Using The Inversion Coefficient For Low-Voltage Low-Power CMOS Voltage ReferencesVenkatesh DonepudiNessuna valutazione finora

- PSpice - A Tutorial - L.H. Fenical (1992)Documento364 paginePSpice - A Tutorial - L.H. Fenical (1992)Suyuk MadikNessuna valutazione finora

- 6.775 Midterm Project 65nm CMOS Op Amp Design: Monroe@mit - EduDocumento21 pagine6.775 Midterm Project 65nm CMOS Op Amp Design: Monroe@mit - EduAc Logic GP1Nessuna valutazione finora

- SpectreRF OhioDocumento110 pagineSpectreRF OhioPratap P PratapNessuna valutazione finora

- What Is PNP Transistor - Construction, Working & ApplicationsDocumento34 pagineWhat Is PNP Transistor - Construction, Working & ApplicationsgezahegnNessuna valutazione finora

- AN148Documento10 pagineAN148Sherwin CruzNessuna valutazione finora

- Iramx 16 Up 60 ADocumento17 pagineIramx 16 Up 60 AJandfor Tansfg ErrottNessuna valutazione finora

- DTB113ZKT146 PDFDocumento6 pagineDTB113ZKT146 PDFshezad shezadNessuna valutazione finora

- Lab Mannual PDFDocumento26 pagineLab Mannual PDFssptc Magazine100% (1)

- Digital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosDa EverandDigital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosValutazione: 5 su 5 stelle5/5 (1)

- Retro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsDa EverandRetro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsNessuna valutazione finora

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDa EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionValutazione: 4.5 su 5 stelle4.5/5 (543)

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesDa EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesValutazione: 5 su 5 stelle5/5 (1)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeDa EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeValutazione: 4.5 su 5 stelle4.5/5 (10)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tDa EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tValutazione: 4.5 su 5 stelle4.5/5 (27)

- Practical Electrical Wiring: Residential, Farm, Commercial, and IndustrialDa EverandPractical Electrical Wiring: Residential, Farm, Commercial, and IndustrialValutazione: 3.5 su 5 stelle3.5/5 (3)

- Analog Design and Simulation Using OrCAD Capture and PSpiceDa EverandAnalog Design and Simulation Using OrCAD Capture and PSpiceNessuna valutazione finora

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersDa Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersValutazione: 5 su 5 stelle5/5 (1)

- A Mind at Play: How Claude Shannon Invented the Information AgeDa EverandA Mind at Play: How Claude Shannon Invented the Information AgeValutazione: 4 su 5 stelle4/5 (53)

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonDa EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonValutazione: 5 su 5 stelle5/5 (2)

- Heat Transfer Engineering: Fundamentals and TechniquesDa EverandHeat Transfer Engineering: Fundamentals and TechniquesValutazione: 4 su 5 stelle4/5 (1)

- Build Your Own Electronics WorkshopDa EverandBuild Your Own Electronics WorkshopValutazione: 3.5 su 5 stelle3.5/5 (3)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsDa EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsValutazione: 3.5 su 5 stelle3.5/5 (2)

- Current Interruption Transients CalculationDa EverandCurrent Interruption Transients CalculationValutazione: 4 su 5 stelle4/5 (1)

- Beginner's Guide to Reading Schematics, Third EditionDa EverandBeginner's Guide to Reading Schematics, Third EditionNessuna valutazione finora

- Teach Yourself Electricity and Electronics, 6th EditionDa EverandTeach Yourself Electricity and Electronics, 6th EditionValutazione: 3.5 su 5 stelle3.5/5 (15)