Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Frequency Dependent Negative Resistance Implementation - Theingjit Et Al

Caricato da

John Bofarull GuixCopyright

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Frequency Dependent Negative Resistance Implementation - Theingjit Et Al

Caricato da

John Bofarull GuixCopyright:

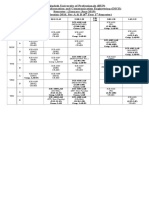

Proceedings of the International MultiConference of Engineers and Computer Scientists 2016 Vol II,

IMECS 2016, March 16 - 18, 2016, Hong Kong

FDNC Realization and Its Application to

FDNR and Filter Realizations

Sasitaporn Theingjit, Tattaya Pukkalanun, Worapong Tangsrirat, Member, IAENG

transconductance amplifier). They are used in interface

Abstract— A simple circuit for the realization of the circuits, instrumentation amplifiers, and continuous-time-

frequency-dependent negative conductance (FDNC) using filters. Since the transconductance gain is electronically

active transconductance (Gm) elements is discussed. Based on variable, they can also be applied in automatic, gain control

the realized FDNC as fundamental circuit element, the

frequency-dependent negative resistances (FDNR) can also be

circuits, and analog multipliers. Considering these facts, the

obtained. The equivalent value of the realized D element can be realizations of FDNC and FDNR based on the use of only

adjusted electronically by means of the transconductance Gm-cells as basic circuit elements has been described in this

parameters. Both simulator circuits do not require the study. The circuits are realizable by using only Gm-cells and

component-matching condition , and enjoy employing only Gm- grounded capacitors, without needing passive resistors. It

cells together with two grounded capacitors; accordingly, they has been shown that the D-element values of the realized

are canonical structures and convenient for integration.

Simulation results with TSMC 0.35-µm CMOS technology are

simulators are controllable electronically through the

presented to validate the characteristics of the realized external biasing currents. In addition, the simulator is tested

simulator circuits and application. in an active realization of the third-order Butterworth

lowpass ladder filter. To demonstrate the practical

Keywords— transconductance cell (Gm-cell), Frequency- workability of the proposed circuits and its applications,

Dependent Negative Conductance (FDNC), Frequency- simulation results based on TSMC 0.35-µm CMOS process

Dependent Negative Resistance (FDNR), immittance function

parameters have been provided.

I. INTRODUCTION +V

REQUENCY-dependent negative conductance (FDNC)

F and frequency-dependent negative resistances (FDNR)

are useful active elements in the synthesis and design active

IB

M3 M4 IB

ladder filters [1]. They can also be used in the realization of io

v+ + io

chaotic oscillator circuits [2]. Several realizations of FDNC v+ v- Gm

and FDNR simulators using various types of active building v- -

M1 M2

blocks were proposed in the literature [3]-[8]. The circuit of

[4] uses three current conveyors, and requires component

IB

matching condition. The FDNR simulators in [5]-[6] require

at least four passive components. Moreover, they also -V

require matching component. In [7]-[8], floating resistors

(a) (b)

and capacitors were employed that are not preferable for

integrated circuit (IC) implementation point of view. Fig.1 Basic Gm cell.

In literature, it is widely accepted that the (a) circuit implementation (b) circuit symbol.

transconductances cell or Gm-cells are fundamental circuit

elements for the realization of many analog active circuits

and systems, especially in the design of modern electronic II. BASIC GM-CELL REALIZATION

circuit building blocks, such as CDTA (current differencing A particularly simple CMOS realization and the symbol

transconductance amplifier), CFTA (current follower of the tunable Gm -cell, which will be used as a fundamental

transconductance amplifier), VDTA (voltage differencing circuit for implementing the proposed circuit, are shown in

transconductance amplifier), and CCTA (current conveyor Fig.1(a) and 1(b), respectively. The circuit is mainly

composed of two Arbel-Goldminz transconductances [9].

Manuscript received August 28, 2015; revised January 19, 2016. For this element, the transconductance value can be

Sasitaporn Theingjit, Tattaya Pukkalanun, Worapong Tangsrirat, are determined by the output transistor transconductance, which

with the Faculty of Engineering, King Mongkut’s Institute of can be approximated as:

TechnologyLadkrabang (KMITL), Chalongkrung road, Ladkrabang,

Bangkok 10520, Thailand. (e-mail : sasitaporn.t@gmail.com ,

tattap@yahoo.com , worapong.ta@kmitl.ac.th)

ISBN: 978-988-14047-6-3 IMECS 2016

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Proceedings of the International MultiConference of Engineers and Computer Scientists 2016 Vol II,

IMECS 2016, March 16 - 18, 2016, Hong Kong

g g g g IV. SIMULATION RESULTS

Gm ≅ m1 m 2 + m3 m 4 (1)

g m1 + g m 2 g m3 + g m 4 To evaluate the behavior of the FDNC circuit in Fig.2,

PSPICE simulation has been performed using TSMC 0.35-

µm CMOS process model parameters. In simulations, the

where gmi = [Kn(p)IB]1/2 (i = 1, 2, 3, 4) and Kn(p) is the dimensions W(µm)/L(µm) of the MOS transistors are set to

transconductance parameter of NMOS (PMOS) transistor be 16.1/0.7 for M1-M2, and 28/0.7 for M3-M4. The supply

and IB is an external DC bias current of this element, voltages used for the proposed simulator circuit are +V = -V

respectively. Note that in eq.(1), the value of Gm is = 1.5 V. According to Fig.1, the bias currents (IBs) used in

electronically tunable by changing the bias current IB. simulations are realized by the simple current mirrors.

The impedance-frequency characteristics of the proposed

FDNC circuit of Fig.2 for various bias currents are shown in

III. FDNC REALIZATION Fig.3. The results were obtained by setting the following

passive and active components : C1 = C2 = 1 nF and IB = IB1

vin s 2C1C2 = IB2 = IB3 (Gm = Gm1 = Gm2 = Gm3). By tuning IB = 40 µA,

Z in = = = s2D (2)

100 µA, and 200 µA, thus the FDNC with D = 18.2 nF/s, 4.7

iin Gm1Gm 2Gm3

nF/s and 1.9 nF/s are obtained respectively. It confirms

from Fig.3 that the impedance values can be adjusted

where the D-element value is given by : precisely by changing the biasing current IB. Also, from

Fig.3, the circuit works correctly along the range 20 kHz to

300 kHz, approximately.

C1C2

D= (3)

Gm1Gm 2Gm3

10M

Simulation

1M

From above relation, it is evident that the FDNC is Theory

IB = 200µA

realized, which is electronically controllable by adjusting 100k

Magnitude (Ω)

Gm1, Gm2 and Gm3. The circuit comprises only Gm-cell and 10k IB = 100 µA

grounded capacitors; hence, it is suitable for IC fabrication.

1k IB = 40 µA

Moreover, no component matching constraint is required in

100

this realization.

10

1

1k 10k 100k 1M 10M

IB1 Frequency(Hz)

iin

IB2

+ + (a)

IB3

vin Gm1 +

270

- - C1 Gm2 - Simulation

Zin - C2 Gm3 Theory

IB = 40 µA

+

IB = 100 µA

Phase (degree)

IB = 200 µA

180

Fig.2 FDNC realization with Gm-cells.

The active and passive sensitivities of the FDNC are

obtained as : 90

1k 10k 100k 1M 10M

Frequency (Hz)

(b)

SGDm1 = SGDm 2 = SGDm 3 = −1 (4)

Fig.3 Theory and simulated frequency characteristics for the FDNC circuit

of Fig.2.

and SCD1 = SCD2 = 1 (5) (a) magnitude responses (b) phase responses

All sensitivity figures are not higher than unity in

magnitude. Therefore, the FDNC of Fig.2 exhibits low

active and passive sensitivities.

ISBN: 978-988-14047-6-3 IMECS 2016

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Proceedings of the International MultiConference of Engineers and Computer Scientists 2016 Vol II,

IMECS 2016, March 16 - 18, 2016, Hong Kong

10M

V. APPLICATION TO FDNR REALIZATION

Simulation

1M

In this section, the generalized circuit topology suitable IBA = 200 µA

Theory

for grounded FDNR realization is introduced. The 100k

IBA = 100 µA

Magnitude (Ω)

introduced topology is depicted in Fig.4. It is based on the

10k

FDNC realization shown in Fig.2, where the Gm4 and Gm5 IBA = 50 µA

behave the variable impedance converter. The circuit has 1k

the advantage of using all-grounded capacitors, which 100

enables easy implementation in IC form. The input

10

admittance (Yin) of the circuit is expressed by :

1

1k 10k 100k 1M 10M

Frequency (Hz)

2

iin s C1C2Gm 4Gm 5

Yin = = (6) (a)

vin Gm1Gm 2Gm 3 0

IBA = 200 µA Simulation

Theory

IBA = 100 µA

-90

Thus, the circuit of Fig.4 simulates a grounded FDNR IBA = 50 µA

Phase (degree)

whose its value is obtained as :

-180

C1C2Gm 4Gm 5

D= (7) -270

Gm1Gm 2Gm 3

-360

1k 10k 100k 1M 10M

Frequency (Hz)

IB4 (b)

iin

IB5 Fig.5 Theory and simulated frequency characteristics for the FDNR

+ +

circuit of Fig.4.

vin Gm4 -

- - Gm5 (a) magnitude responses (b) phase responses

Zin +

VI. APPLICATION TO FILTER REALIZATION

IB1

To illustrate another application of the FDNC realization,

IB2

+ the third-order Butterworth lowpass filter was designed and

IB3 simulated. The normalized RLC passive prototype is shown

Gm1 +

- C1 Gm2 - in Fig.6(a), where Rs = RL = 3.18 kΩ, L1 = L3 = 5 mH, and

- C2 Gm3 C2 = 1 nF [10]. The voltage transfer function of the circuit

+ in Fig.6(a) is given by :

VL ( s ) 1

Fig.4 FDNR realization based on FDNC of Fig.2. =

VS ( s ) L1 L3C 2 2 RS L3C 2 L +L R

s 3

+ s + L1C 2 + s RS C 2 + 1 3 + S + 1

R L R L RL RL

In order to demonstrate the performance of the FDNR in (8)

Fig.4, it was designed with C1 = C2 = 1 nF, IBA = IB1 = IB2 =

IB3 (GmA = Gm1 = Gm2 = Gm3) and IBB = IB4 = IB5 (GmB = Gm4 By applying Bruton transformation [1] and using variable

= Gm5). In simulations, the circuit was simulated by keeping impedance scaling method with magnitude scaling constant

IBB = 200 µA and varying IBA = 50 µA, 100 µA, and 200 µA, (km = 1.59×103) and frequency scaling constant (kf =

resulting in Deq = 8.34 fF/s, 3.05 fF/s, and 1.24 fF/s, 628×103), the RLC passive filter of Fig.6(a) then will have a

respectively. Fig.5 shows the theory and simulated cutoff frequency of fc = 100 kHz. As a results, the filter is

frequency characteristics of the FDNR simulator of Fig.4 for converted into CRD filter as shown in Fig.6(b), where the

various IBA values. As demonstrated in both figures, the FDNR is realized using the realized circuit of Fig.4. In

realized FDNR works perfectly between 20 kHz and 300 Fig.6(b), the resulting circuit components are obtained as :

kHz. Also note that the simulation results are in close

CRS = CRL = 1 nF, RL1 = RL3 = 1.59 kΩ and D2 = 3.18 fFs.

agreement with the prediction values, and confirm that the

The results of PSPICE simulation of the example filters are

D–element value can be adjusted electronically by the Gm

also given, verifying the porper operation. Fig.7 shows the

biasing currents.

magnitude and phase characteristics of the filters in Fig.6. It

is seen from Fig.7 that simulation results agree very well

with the expectation ones.

ISBN: 978-988-14047-6-3 IMECS 2016

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Proceedings of the International MultiConference of Engineers and Computer Scientists 2016 Vol II,

IMECS 2016, March 16 - 18, 2016, Hong Kong

Rs L1 L3 VII. CONCLUSIONS

+ + The simple realization scheme of an electronically tunable

vs RL vL FDNC based on Gm-cell technique has been described. The

C2

FDNC realization circuit is constructed by only two

- - grounded capacitors as passive elements, resulting in a

resistorless structure and suitable for integration. No

(a) component matching is needed for its realization. The D-

element value of the realized FDNC can be tuned

CRS RL1 RL3 electronically through the external bias currents. The

+ + described FDNC circuit has been shown to be useful in

realizing a FDNR and active ladder filter, respectively. The

vs D2 CRL vL

workability of the realized FDNR is demonstrated on the

- - third-order Butterworth lowpass filter. Simulation results

with TSMC 0.35-µm CMOS technology have been provided

(b) and the obtained results confirm well the theory.

Fig.6 Third-order Butterworth lowpass filter.

(a) RLC passive prototype (b) equivalent CDR circuit with FDNR. ACKNOWLEDGMENT

This research work is supported by Faculty of

0

Engineering, King Mongkut’s Institute of Technology

Ladkrabang (KMITL), Thailand.

-20

REFERENCES

Gain (dB)

[1] L. T. Bruton, “Network transfer functions using the concept of

-40 frequency dependent negative resistance”, IEEE Trans. Circuit

Theory, vol.CT-16, pp.406-408, 1969.

[2] A. S. Elwakil, M. P. Kennedy, “Chaotic oscillator configuration using

-60 a frequency dependent negative resistor”, J. Circuits Syst. Comp.,

CDR circuit of Fig.6(b)

vol.9, no.3-4, pp.229-242, 1999.

RLC passive prototype of Fig.6(a) [3] A. Toker, O. Cicekoglu, H. Kuntman, “New active gyrator circuit

-80 suiable for frequency-dependent negative resistor implementation”,

1k 10k 100k 1M 10M Microelectron. J., vol.30, pp.59-62, 1999.

Frequency (Hz)

[4] M. T. Abuelma’atti, N. A. Tasadduq, “Electronically tunable

(a) capacitance multiplier and frequency dependent negative resistance

simulator using the current-controlled current conveyor”,

0 Microelectron. J., vol.30, pp.869-873, 1999.

CDR circuit of Fig.6(b) [5] E. Yuce, “Floating inductance, FDNR and capacitance simulation

RLC passive prototype of Fig.6(a) circuit employing only grounded passive elements”, Int. J. Electron.,

vol93, no.10, pp.679-688, 2006.

-90 [6] C. Psychalinosa, K. Pal, S. Vlassisa, “A floating generalized

Phase (degree)

impedance converter with current feedback operational amplifiers”,

Int. J. Electron. Commun. (AEU), vol. 62, pp.81-85, 2008.

[7] A. M. Soliman, R. A. Saad, “Two new families of floating FDNR

-180 circuits”, J. Electrical Comp. Eng., vol.2010, Article ID 563761, 7

pages, 2010.

[8] A. Gupta, R. Senani, D. R. Bhaskar, A. K. Singh, “OTRA-based

grounded-FDNR and grounded-inductance simulators and their

applications”, Circuits Syst. Signal Process., vol.31, pp.489-499,

-270

1k 10k 100k 1M 10M 2012.

Frequency (Hz) [9] A. F. Arbel, L. Goldminz, “Output stage for current-mode feedback

amplifiers, theory and applications”, Analog Integr. Circ. Sig.

(b) Process., vol.2, no.3, pp.243–255, 1992.

Fig.7 Simulated frequency responses of the filters in Fig.6. [10] L. P. Huelman, P. E. Allen, Introduction to the Theory and Design of

Active Filters, McGraw-Hill, New York, 1980.

(a) gain responses (b) phase responses.

ISBN: 978-988-14047-6-3 IMECS 2016

ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online)

Potrebbero piacerti anche

- Number CardsDocumento21 pagineNumber CardsCachipún Lab CreativoNessuna valutazione finora

- Formulae HandbookDocumento60 pagineFormulae Handbookmgvpalma100% (1)

- William Ury Power of A Positive No Bantam - 2007Documento227 pagineWilliam Ury Power of A Positive No Bantam - 2007Tam Jeopardy100% (1)

- ResumeDocumento3 pagineResumeAstig Kuging63% (8)

- Keysight - Radar Electromagnetic Spectrum OperatiomsDocumento315 pagineKeysight - Radar Electromagnetic Spectrum OperatiomsJohn Bofarull Guix100% (1)

- Storage Tanks Overfill Prevention Better PracticesDocumento2 pagineStorage Tanks Overfill Prevention Better PracticesRicardo Bec100% (1)

- FPGA Implementation of Unipolar SPWM For Single Phase InverterDocumento6 pagineFPGA Implementation of Unipolar SPWM For Single Phase InverterMalay BhuniaNessuna valutazione finora

- Lesson Exemplar Math 7Documento6 pagineLesson Exemplar Math 7Pablo Jimenea100% (2)

- MATLAB Solution To Microwave Engineering Pozar 4th Ed. Example 1.5Documento5 pagineMATLAB Solution To Microwave Engineering Pozar 4th Ed. Example 1.5John Bofarull GuixNessuna valutazione finora

- Admission: North South University (NSU) Question Bank Summer 2019Documento10 pagineAdmission: North South University (NSU) Question Bank Summer 2019Mahmoud Hasan100% (7)

- Square Root Domain Filter Design and PerformanceDocumento13 pagineSquare Root Domain Filter Design and Performanceaakriti chhabraNessuna valutazione finora

- An Ultra Low-Voltage Ultra Low-Power Memristor: Şuayb Çağrı YENER, Atilla UYGUR, H. Hakan KUNTMANDocumento5 pagineAn Ultra Low-Voltage Ultra Low-Power Memristor: Şuayb Çağrı YENER, Atilla UYGUR, H. Hakan KUNTMANBüşra AkyıldızNessuna valutazione finora

- Transformer Windings' RLC Parameters Calculation and Lightning Impulse Voltage Distribution SimulationDocumento4 pagineTransformer Windings' RLC Parameters Calculation and Lightning Impulse Voltage Distribution SimulationOscar PieruzziniNessuna valutazione finora

- Low Power Ramp Generator With MOSFET and CNTFET TransistorsDocumento3 pagineLow Power Ramp Generator With MOSFET and CNTFET TransistorsBhargav BhatNessuna valutazione finora

- All Inversion RegionDocumento4 pagineAll Inversion RegionAshwin BhatNessuna valutazione finora

- A 1.82.6GHz RF CMOS Up-Conversion Mixer For Wideband ApplicationsDocumento4 pagineA 1.82.6GHz RF CMOS Up-Conversion Mixer For Wideband ApplicationsJyotirmay SarkarNessuna valutazione finora

- High-Performance CMOS Current Mirrors: Application To Linear Voltage-to-Current Converter Used For Two-Stage Operational AmplifierDocumento6 pagineHigh-Performance CMOS Current Mirrors: Application To Linear Voltage-to-Current Converter Used For Two-Stage Operational AmplifierShaheer DurraniNessuna valutazione finora

- On The Design and Optimization of Cmos Active Inductor For RF ApplicationsDocumento13 pagineOn The Design and Optimization of Cmos Active Inductor For RF Applicationsjanapaneni ramadeviNessuna valutazione finora

- CMOS Realization Voltage Differencing Transconductance Amplifier and Based Tow-Thomas FilterDocumento4 pagineCMOS Realization Voltage Differencing Transconductance Amplifier and Based Tow-Thomas FilterijsretNessuna valutazione finora

- A 0.18 M CMOS DDCCII For Portable LV-LP Filters: Vincenzo STORNELLI, Giuseppe FERRIDocumento6 pagineA 0.18 M CMOS DDCCII For Portable LV-LP Filters: Vincenzo STORNELLI, Giuseppe FERRIHamid BoualiNessuna valutazione finora

- CMOS Implemented VDTA Based Colpitt OscillatorDocumento4 pagineCMOS Implemented VDTA Based Colpitt OscillatorijsretNessuna valutazione finora

- Voltage - Current Converter For A Memory Current Cell Using Floating Gate TransistorsDocumento6 pagineVoltage - Current Converter For A Memory Current Cell Using Floating Gate TransistorsAram ShishmanyanNessuna valutazione finora

- V3i513 PDFDocumento6 pagineV3i513 PDFIJCERT PUBLICATIONSNessuna valutazione finora

- EEE 1303 015 Determination Study MOSFET Technology CurrentDocumento8 pagineEEE 1303 015 Determination Study MOSFET Technology CurrentWestern777Nessuna valutazione finora

- Cmos Inverter As A ComparatorDocumento5 pagineCmos Inverter As A ComparatorAnonymous TPVfFif6TONessuna valutazione finora

- Compact and Wide-Band Efficiency Improved RF Differential Rectifier For Wireless Energy HarvestingDocumento4 pagineCompact and Wide-Band Efficiency Improved RF Differential Rectifier For Wireless Energy HarvestingLukas BalciusNessuna valutazione finora

- Design of Low-Power and High-Speed Opamp Integrated Circuits Using Silicon Nanowire TransistorsDocumento13 pagineDesign of Low-Power and High-Speed Opamp Integrated Circuits Using Silicon Nanowire Transistorsdeepak pandeyNessuna valutazione finora

- Characteristics of Double Planar Micro-Inductor With Patterned Nife Thin-Films For DC/DC IntegrationDocumento9 pagineCharacteristics of Double Planar Micro-Inductor With Patterned Nife Thin-Films For DC/DC Integrationliton_kabirNessuna valutazione finora

- OTA Based On CMOS Inverters and Application in The Design of Tunable Bandpass Filter PDFDocumento10 pagineOTA Based On CMOS Inverters and Application in The Design of Tunable Bandpass Filter PDFGenetic JohnNessuna valutazione finora

- Singh 2018Documento5 pagineSingh 2018Tshering Sangmoo SherpaNessuna valutazione finora

- Ref 26 Fully Coupled 3-D Device Simulation of Negative Capacitance FinFETs For Sub 10 NM IntegrationDocumento4 pagineRef 26 Fully Coupled 3-D Device Simulation of Negative Capacitance FinFETs For Sub 10 NM IntegrationM. Ashikuzzaman KowshikNessuna valutazione finora

- Comparing The Performance of Bipolar and Unipolar Switching Frequency To Drive DC-AC Inverter PDFDocumento6 pagineComparing The Performance of Bipolar and Unipolar Switching Frequency To Drive DC-AC Inverter PDFMiguel C.M.Nessuna valutazione finora

- 60 GHZ Transmitter Circuits in 65Nm Cmos: Rtuif-18Documento4 pagine60 GHZ Transmitter Circuits in 65Nm Cmos: Rtuif-18Ganagadhar CHNessuna valutazione finora

- Microelectronics Journal: Habib Rastegar, Jee-Youl RyuDocumento8 pagineMicroelectronics Journal: Habib Rastegar, Jee-Youl RyuRAJAMOHANNessuna valutazione finora

- Expt 01 Cmos InverterDocumento2 pagineExpt 01 Cmos InverterShameem ShaikNessuna valutazione finora

- Ponencia - Filter - BodyDriven Gonzalez CarvajalDocumento4 paginePonencia - Filter - BodyDriven Gonzalez CarvajalFernando JarixNessuna valutazione finora

- Microwave Capacitor and Inductor Analysis Using Wave Iterative ComputationDocumento2 pagineMicrowave Capacitor and Inductor Analysis Using Wave Iterative ComputationNattapong IntarawisetNessuna valutazione finora

- Internship PresentationDocumento41 pagineInternship PresentationNIKHILNessuna valutazione finora

- Paper Publish 1 PDFDocumento5 paginePaper Publish 1 PDFSupriya Tenny SamNessuna valutazione finora

- High Speed & Low Power Comparator Using Double-Gate MOSFET Scalable To 20nmDocumento5 pagineHigh Speed & Low Power Comparator Using Double-Gate MOSFET Scalable To 20nmSupriya Tenny SamNessuna valutazione finora

- Fast Prediction For Conducted EMI in Flyback Converters: AbstractDocumento3 pagineFast Prediction For Conducted EMI in Flyback Converters: AbstractTung ThanhNessuna valutazione finora

- Design of A 2.4 GHZ High-Performance Up-Conversion Mixer With Current Mirror TopologyDocumento6 pagineDesign of A 2.4 GHZ High-Performance Up-Conversion Mixer With Current Mirror TopologyAkhendra KumarNessuna valutazione finora

- Finfet Based Flash Adc PDFDocumento4 pagineFinfet Based Flash Adc PDFJam 234Nessuna valutazione finora

- Analysis of Transformerless UPFC With FFM Phase ShiftingDocumento4 pagineAnalysis of Transformerless UPFC With FFM Phase ShiftingVinay BagaliNessuna valutazione finora

- 2014 APEC Thermal Analysis of A SubmodulDocumento7 pagine2014 APEC Thermal Analysis of A SubmodulNAM PHẠM LÊNessuna valutazione finora

- 25 NehaDocumento6 pagine25 NehaKingNessuna valutazione finora

- Single-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeDocumento12 pagineSingle-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeZhongpeng LiangNessuna valutazione finora

- Design of Low Power 6-Bit Digitally-Controlled Oscillator (DCO)Documento9 pagineDesign of Low Power 6-Bit Digitally-Controlled Oscillator (DCO)AtulNessuna valutazione finora

- Realization of A Compact Reconfigurable Antenna For Mobile CommunicationsDocumento4 pagineRealization of A Compact Reconfigurable Antenna For Mobile CommunicationsyenifferNessuna valutazione finora

- 10 1109@siitme 2018 8599271Documento4 pagine10 1109@siitme 2018 8599271Dr. P Akhendra KumarNessuna valutazione finora

- 1996 - JSSC - A gmID Based Methodology For The Design of CMOS Analog Circuits and Application To The Synthesis of A SOI Micropower OTADocumento6 pagine1996 - JSSC - A gmID Based Methodology For The Design of CMOS Analog Circuits and Application To The Synthesis of A SOI Micropower OTALuật TrầnNessuna valutazione finora

- Ehv Gis SubstationDocumento6 pagineEhv Gis SubstationelectricalrakeshNessuna valutazione finora

- Design of Parallel Coupled Microstrip Bandpass Filter For FM Wireless ApplicationsDocumento5 pagineDesign of Parallel Coupled Microstrip Bandpass Filter For FM Wireless ApplicationsrqfkypprjtNessuna valutazione finora

- Traductoare de ProximitateDocumento13 pagineTraductoare de ProximitateIulia GhiocNessuna valutazione finora

- ICISC Coimbatore (2019)Documento5 pagineICISC Coimbatore (2019)Dr. D. V. KamathNessuna valutazione finora

- A Single Stage CCM Zeta Microinverter For Solar Photovoltaic AC ModuleDocumento9 pagineA Single Stage CCM Zeta Microinverter For Solar Photovoltaic AC ModuleChristian EmenikeNessuna valutazione finora

- The Two-Winding Transformer: An Experimental Method To Obtain A Wide Frequency Range Equivalent CircuitDocumento8 pagineThe Two-Winding Transformer: An Experimental Method To Obtain A Wide Frequency Range Equivalent Circuitjeos20132013Nessuna valutazione finora

- 2022 Sforum Comparador JL OkDocumento4 pagine2022 Sforum Comparador JL OkVictor Matheus LimaNessuna valutazione finora

- Lect 4Documento10 pagineLect 4ngupta999Nessuna valutazione finora

- Modeling of Coplanar Waveguide Meander-LineInductorsDocumento10 pagineModeling of Coplanar Waveguide Meander-LineInductorsalisazidNessuna valutazione finora

- Design and Implementation of 2 Bit Loaded Line Phase ShifterDocumento5 pagineDesign and Implementation of 2 Bit Loaded Line Phase ShifterdhvbkhnNessuna valutazione finora

- Saturation Analysis On Current Transformer: Abstract - Current Transformer (CT) Is One of TheDocumento8 pagineSaturation Analysis On Current Transformer: Abstract - Current Transformer (CT) Is One of TheDipankar KhutiaNessuna valutazione finora

- Cntfet Technology Based Precision Full-Wave Rectifier Using DDCCDocumento8 pagineCntfet Technology Based Precision Full-Wave Rectifier Using DDCCresearchinventyNessuna valutazione finora

- A Low Power Schmitt Trigger Design Using SBT Technique in 180nm CMOS TechnologyDocumento4 pagineA Low Power Schmitt Trigger Design Using SBT Technique in 180nm CMOS TechnologySowmya ReddyNessuna valutazione finora

- Study of Very Fast Transient Overvoltages and Mitigation Techniques of A Gas Insulated SubstationDocumento6 pagineStudy of Very Fast Transient Overvoltages and Mitigation Techniques of A Gas Insulated SubstationThyago De Moura JorgeNessuna valutazione finora

- Design of Double Balanced Gilbert Cell Mixer For WBAN ApplicationsDocumento4 pagineDesign of Double Balanced Gilbert Cell Mixer For WBAN ApplicationsAhmed MaGdyNessuna valutazione finora

- Novel ForwardFlyback Hybrid Bidirectional DCDC ConverterDocumento7 pagineNovel ForwardFlyback Hybrid Bidirectional DCDC ConverterHsekum RamukNessuna valutazione finora

- High-Performance D/A-Converters: Application to Digital TransceiversDa EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNessuna valutazione finora

- Heterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionDa EverandHeterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionNessuna valutazione finora

- Microwave Engineering Chapter 2 Example 1Documento16 pagineMicrowave Engineering Chapter 2 Example 1John Bofarull GuixNessuna valutazione finora

- Microwave Engineering 02 Example 04Documento5 pagineMicrowave Engineering 02 Example 04John Bofarull GuixNessuna valutazione finora

- Microwave Engineering Chapter 2 Example 3Documento21 pagineMicrowave Engineering Chapter 2 Example 3John Bofarull GuixNessuna valutazione finora

- HP Prime Calc - 87-29 Slope TestDocumento1 paginaHP Prime Calc - 87-29 Slope TestJohn Bofarull GuixNessuna valutazione finora

- HP Prime Calc 85 27 Chi Square Test 2 Way TablesDocumento1 paginaHP Prime Calc 85 27 Chi Square Test 2 Way TablesJohn Bofarull GuixNessuna valutazione finora

- PCAAD7 ManualDocumento120 paginePCAAD7 ManualJohn Bofarull GuixNessuna valutazione finora

- Beamflex Roaming Problems in Warehouse - RUCKUSDocumento8 pagineBeamflex Roaming Problems in Warehouse - RUCKUSJohn Bofarull GuixNessuna valutazione finora

- MATLAB Solution To Microwave Engineering Pozar 4th Ed. Example 1.3Documento13 pagineMATLAB Solution To Microwave Engineering Pozar 4th Ed. Example 1.3John Bofarull GuixNessuna valutazione finora

- MATLAB Solution To Microwave Engineering Pozar 4th Ed. Example 1.2Documento8 pagineMATLAB Solution To Microwave Engineering Pozar 4th Ed. Example 1.2John Bofarull GuixNessuna valutazione finora

- Answer To Pozar Exercise 1-1Documento11 pagineAnswer To Pozar Exercise 1-1John Bofarull GuixNessuna valutazione finora

- MATLAB Solution To Microwave Engineering Pozar 4th Ed. Example 1.1Documento26 pagineMATLAB Solution To Microwave Engineering Pozar 4th Ed. Example 1.1John Bofarull GuixNessuna valutazione finora

- Solution To Microwave Engineering Pozar Chapter 14 Exercise 23 With MATLABDocumento4 pagineSolution To Microwave Engineering Pozar Chapter 14 Exercise 23 With MATLABJohn Bofarull GuixNessuna valutazione finora

- Solution To Microwave Engineering Pozar Chapter 14 Exercise 17 With MATLABDocumento3 pagineSolution To Microwave Engineering Pozar Chapter 14 Exercise 17 With MATLABJohn Bofarull GuixNessuna valutazione finora

- Solution To Microwave Engineering Pozar Chapter 14 Exercise 22 With MATLABDocumento4 pagineSolution To Microwave Engineering Pozar Chapter 14 Exercise 22 With MATLABJohn Bofarull GuixNessuna valutazione finora

- Updated WorksheetDocumento5 pagineUpdated WorksheetJohn Ramer Lazarte InocencioNessuna valutazione finora

- Make Yeast StarterDocumento2 pagineMake Yeast StarterAlexandraNessuna valutazione finora

- TOEFL-Reading Question Type Definitions and ExplanationDocumento5 pagineTOEFL-Reading Question Type Definitions and ExplanationSamara SampaioNessuna valutazione finora

- Measures of Indicator 1Documento2 pagineMeasures of Indicator 1ROMMEL BALAN CELSONessuna valutazione finora

- Noth PicturesDocumento17 pagineNoth PicturesJana AssaNessuna valutazione finora

- WSI - Catalogue of O-Ring PDFDocumento37 pagineWSI - Catalogue of O-Ring PDFyearetg100% (1)

- Group 4 - When Technology and Humanity CrossDocumento32 pagineGroup 4 - When Technology and Humanity CrossJaen NajarNessuna valutazione finora

- HP Scanjet Pro 2500 F1 Flatbed Scanner: Boost Productivity With Fast, Versatile ScanningDocumento2 pagineHP Scanjet Pro 2500 F1 Flatbed Scanner: Boost Productivity With Fast, Versatile ScanningParesh BabariaNessuna valutazione finora

- TransistorDocumento3 pagineTransistorAndres Vejar Cerda0% (1)

- Manish Kumar: Desire To Work and Grow in The Field of MechanicalDocumento4 pagineManish Kumar: Desire To Work and Grow in The Field of MechanicalMANISHNessuna valutazione finora

- Hume 100 ReviewerDocumento7 pagineHume 100 ReviewerShai GaviñoNessuna valutazione finora

- Concept of Lokmitra Kendra in Himachal PradeshDocumento2 pagineConcept of Lokmitra Kendra in Himachal PradeshSureshSharmaNessuna valutazione finora

- I. Objectives Ii. Content Iii. Learning ResourcesDocumento13 pagineI. Objectives Ii. Content Iii. Learning ResourcesZenia CapalacNessuna valutazione finora

- 02 Lab 1.HCIDocumento2 pagine02 Lab 1.HCILopao SerojemNessuna valutazione finora

- GE Uno Downlight Backlit BLDocumento2 pagineGE Uno Downlight Backlit BLChen KengloonNessuna valutazione finora

- Ab 2023Documento5 pagineAb 2023Cristelle Estrada-Romuar JurolanNessuna valutazione finora

- Be and Words From The List.: 6B Judging by Appearance Listening and ReadingDocumento3 pagineBe and Words From The List.: 6B Judging by Appearance Listening and ReadingVale MontoyaNessuna valutazione finora

- Class Routine Final 13.12.18Documento7 pagineClass Routine Final 13.12.18RakibNessuna valutazione finora

- CadburyDocumento21 pagineCadburyramyarayeeNessuna valutazione finora

- Chemical Engineering & Processing: Process Intensi Fication: ArticleinfoDocumento9 pagineChemical Engineering & Processing: Process Intensi Fication: Articleinfomiza adlinNessuna valutazione finora

- 1st Unseen Passage For Class 5 in EnglishDocumento7 pagine1st Unseen Passage For Class 5 in EnglishVibhav SinghNessuna valutazione finora

- Pascal Die Casting Machine SystemDocumento20 paginePascal Die Casting Machine Systemenascimento32Nessuna valutazione finora

- Mathematics4 q4 Week4 v4Documento11 pagineMathematics4 q4 Week4 v4Morales JinxNessuna valutazione finora