Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Laboratorio de Circuitos Digitales 5.1 (El Chusco No Me Va A Jalar)

Caricato da

koro joroTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Laboratorio de Circuitos Digitales 5.1 (El Chusco No Me Va A Jalar)

Caricato da

koro joroCopyright:

Formati disponibili

Laboratorio de circuitos digitales

UNIVERSIDAD NACIONAL

MAYOR DE SAN MARCOS

(Universidad del Perú, DECANA DE AMÉRICA)

FACULTAD DE ELECTRONICA

PROFESOR: ALARCON MATUTTI, RUBEN

CURSO: CIRCUITOS DIGITALES

TRABAJO: INFORME Nª 5 (PRIMERA PARTE)

TURNO: MIERCOLES (16-18)

CICLO: QUINTO

ALUMN: PICON RAMIREZ EDGAR PABLO

CODIGO: 16190080

2018

Laboratorio n|°5 Página 1

Laboratorio de circuitos digitales

LABORATORIO N° 5:

A) Diseñar usando DOS multiplexores CI 74151 y algunas puertas

adicionales, diseñar un multiplexor 16 a 1. Se pide:

Re sumen de la hoja de datos técnicos del CI. Buscar en internet el “data

sheet”- entender su funcionamiento lógico.

Descripción general:

Este selector / multiplexor de datos contiene decodificación completa en el chip.

Para seleccionar la fuente de datos deseada. El DM74LS151.

Selecciona una de ocho fuentes de datos. El DM74LS151 tiene una

Entrada estroboscópica que debe estar a un nivel lógico bajo para

Estos dispositivos. Un alto nivel en el estroboscópico fuerza la salida W

ALTO, y la salida Y BAJA.

El DM74LS151 ofrece salidas complementarias de W e Y.

Diagrama de conexión y tabla de verdad:

Laboratorio n|°5 Página 2

Laboratorio de circuitos digitales

Diagramas lógicos

Laboratorio n|°5 Página 3

Laboratorio de circuitos digitales

Simular el equivalente lógico del CI y definirlo como símbolo. Incluir el pin

de Vcc y GND con la misma distribución de pines del “data sheet”.

FIG. “Ejemplo A.1”

Laboratorio n|°5 Página 4

Laboratorio de circuitos digitales

Símbolo del CI 74151

Figura. “ejemplo A.1.1”

Mostrar el conexionado y simular el diseño usando el símbolo del CI. El

conexionado debe ser tal como se haría en un protoboard real

Fig. “ejemplo A.2”

Laboratorio n|°5 Página 5

Laboratorio de circuitos digitales

B) Usando dos decodificadores CI 74138, diseñar un circuito decodificador

4 a 16. Se pide:

Re sumen de la hoja de datos técnicos del CI. Buscar en internet el

“data sheet”- entender su funcionamiento lógico.

Descripción general:

El DM74LS138 decodifica uno de ocho líneas, basado en Las tres entradas de selección

binarias y las Tres entradas de habilitación. Dos bajas activas y una alta activa Permiten

reducir la necesidad de puertas o inversores externos Cuando se expande. Se puede

implementar un decodificador de 24 líneas Sin inversores externos, y un decodificador de

32 líneas Requiere sólo un inversor. Una entrada de habilitación se puede utilizar como Una

entrada de datos para aplicaciones de demultiplexación.

Diagrama de conexión:

Laboratorio n|°5 Página 6

Laboratorio de circuitos digitales

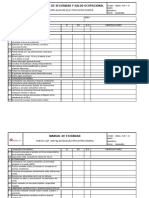

Tabla de verdad:

Diagramas lógicos

Laboratorio n|°5 Página 7

Laboratorio de circuitos digitales

Simular el equivalente lógico del CI y definirlo como símbolo. Incluir el pin

de Vcc y GND con la misma distribución de pines del “data sheet”.

Figura: ejemplo B.1

Laboratorio n|°5 Página 8

Laboratorio de circuitos digitales

Símbolo del CI 74138

Figura. “ejemplo B.1.1”

Mostrar el conexionado y simular el diseño usando el símbolo del CI. El

conexionado debe ser tal como se haría en un protoboard real

Fig. “ejemplo B.2”

Laboratorio n|°5 Página 9

Laboratorio de circuitos digitales

C) Usando el CI 7447 y LEDs simples, diseñe una pantalla de colores

numérico hexadecimal de 7 segmentos. Se pide:

Re sumen de la hoja de datos técnicos del CI. Buscar en internet el “data

sheet”- entender su funcionamiento lógico.

Descripción general:

Los modelos 46A y 47A ofrecen salidas de baja activa diseñadas para

Conduciendo LED de ánodo común o indicadores incandescentes directamente.

Todos los circuitos tienen entradas / salidas de ondulación completa

Controles y una entrada de prueba de la lámpara. Identificación de segmentos

Y las pantallas resultantes se muestran en una página siguiente. Monitor

Patrones para BCD entrada cuenta por encima de nueve son únicos

Símbolos para autenticar las condiciones de entrada.

Todos los circuitos incorporan sistemas automáticos de dirección y / o de arrastre,

Control de supresión cero (RBI y RBO). Prueba de la lámpara

(LT) de estos dispositivos se puede realizar en cualquier momento cuando

El nodo BI / RBO se encuentra en un nivel lógico alto. Todos los tipos contienen

Una entrada de borrado (BI) que se puede utilizar para controlar

La intensidad de la lámpara (pulsando) o para inhibir las salidas.

Características:

- Todos los tipos de circuitos cuentan con la modulación de intensidad de la lámpara

Capacidad

- Salidas de colector abierto indicadores de accionamiento directamente

- Disposición de prueba de lámpara

- Supresión de cero de arrastre / final

Laboratorio n|°5 Página 10

Laboratorio de circuitos digitales

1: BI / RBO es una lógica wire-AND que sirve como entrada de borrado (BI) y / o salida de

ondulación (RBO).

2: La entrada de borrado (BI) debe estar abierta o mantenida a un nivel lógico alto cuando se

desean las funciones de salida 0 a 15. La entrada de supresión de ondulación (RBI) debe

Ser abierto o alto si no se desea borrar un decimal cero.

3: Cuando se aplica un nivel lógico bajo directamente a la entrada de borrado (BI), todas las salidas

de segmento son altas independientemente del nivel de cualquier otra entrada.

4: Cuando la entrada de borrado de ondulación (RBI) y las entradas A, B, C y D están a un nivel

bajo con la entrada de prueba de la lámpara alta, todas las salidas de segmento salen H y la

ondulación

Salida (RBO) va a un nivel bajo (condición de respuesta).

5: Cuando la salida de blanking / blanking (BI / RBO) está abierta o se mantiene alta y baja se

aplica a la entrada de prueba de lámpara, todas las salidas de segmento son L.

H e Nivel alto, L e Nivel bajo, X e Do Not Care

Laboratorio n|°5 Página 11

Laboratorio de circuitos digitales

Diagrama lógico:

Simular el equivalente lógico del CI y definirlo como símbolo. Incluir el pin

de Vcc y GND con la misma distribución de pines del “data sheet”.

Laboratorio n|°5 Página 12

Laboratorio de circuitos digitales

Figura: “ejemplo 5.1”

Laboratorio n|°5 Página 13

Laboratorio de circuitos digitales

Figura: “CI 2”: lm 7447

Mostrar el conexionado y simular el diseño usando el símbolo del CI. El

conexionado debe ser tal como se haría en un protoboard real

Figura: “ejemplo 6”

Laboratorio n|°5 Página 14

Laboratorio de circuitos digitales

F) Realizar la función 𝑭 = 𝝅𝑴(𝟎, 𝟐, 𝟒, 𝟔) mediante:

𝑓(𝑥1 , 𝑥2 , 𝑥3 ) = 𝜋𝑀(0,2,4,6)

𝑓(𝑥1 , 𝑥2 , 𝑥3 ) = (𝑚0 )𝑥(𝑚2 )𝑥(𝑚4 )𝑥(𝑚6 )

𝑓(𝑥1 , 𝑥2 , 𝑥3 ) = (𝐴 + 𝐵 + 𝐶)(𝐴 + 𝐵̅ + 𝐶)(𝐴̅ + 𝐵 + 𝐶)(𝐴̅ + 𝐵̅ + 𝐶)

Operando se tiene lo siguiente:

𝑓(𝑥1 , 𝑥2 , 𝑥3 ) = 𝐶

Laboratorio n|°5 Página 15

Laboratorio de circuitos digitales

Tabla de verdad:

A B C F

0 0 0 1 D0

0 0 1 0 D1

0 1 0 1 D2

0 1 1 0 D3

1 0 0 1 D4

1 0 1 0 D5

1 1 0 1 D6

1 1 1 0 D7

Multiplexores 8:1

Figura: “ejemplo F”

Laboratorio n|°5 Página 16

Laboratorio de circuitos digitales

Multiplexores 4:1

Decodificadores 3:8 y puertas OR

TABLA DE VERDAD PARA EL DECODIFICADOR:

C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 F

0 0 0 0 1 1 1 1 1 1 1 1

0 0 1 1 0 1 1 1 1 1 1 0

0 1 0 1 1 0 1 1 1 1 1 1

0 1 1 1 1 1 0 1 1 1 1 0

1 0 0 1 1 1 1 0 1 1 1 1

1 0 1 1 1 1 1 1 0 1 1 0

1 1 0 1 1 1 1 1 1 0 1 1

1 1 1 1 1 1 1 1 1 1 0 0

Operando mini términos se llega a obtener lo siguiente:

Laboratorio n|°5 Página 17

Laboratorio de circuitos digitales

𝑭 = 𝒀𝟏 𝒀𝟑 𝒀𝟒 𝒀𝟓 𝒀𝟔 𝒀𝟕 (𝒀𝟎 𝜽𝒀𝟐 ) + 𝒀𝟎 𝒀𝟏 𝒀𝟐 𝒀𝟑 𝒀𝟓 𝒀𝟕 (𝒀𝟒 𝜽𝒀𝟎 )

Figura: “ejemplo F.2”

G) Analizar el circuito dado y hallar la expresión booleana de salida F en

función de las entradas (X, Y, Z0, Z1)

X Y Z0 Z1 F

0 0 0 0 0

0 0 0 1 1

0 0 1 0 0

0 0 1 1 1

Laboratorio n|°5 Página 18

Laboratorio de circuitos digitales

0 1 0 0 1

0 1 0 1 1

0 1 1 0 1

0 1 1 1 0

1 0 0 0 1

1 0 0 1 1

1 0 1 0 1

1 0 1 1 1

1 1 0 0 0

1 1 0 1 0

1 1 1 0 1

1 1 1 1 0

Función Booleana

𝐹 = (𝑋̅𝑌 + 𝑋𝑌̅)(𝑍

̅̅̅1 )(𝑍

̅̅̅𝑂̅) + (𝑋 + 𝑌)(𝑍

̅̅̅1 )(𝑍𝑂 ) + (𝑋𝑌

̅̅̅̅)(𝑍1 )(𝑍

̅̅̅𝑂̅) + (𝑌̅)(𝑍1 )(𝑍𝑂 )

Tabla de Verdad

Z1 Z0 F

0 0 𝑋̅𝑌 + 𝑋𝑌̅

0 1 𝑋+𝑌

1 0 ̅̅̅̅

𝑋𝑌

1 1 𝑌̅

Laboratorio n|°5 Página 19

Laboratorio de circuitos digitales

Figura: “ejemplo G”

Figura:” ejemplo G.1”

Laboratorio n|°5 Página 20

Potrebbero piacerti anche

- S-Fi - para Tu EntretenimientoDocumento8 pagineS-Fi - para Tu Entretenimientokoro joroNessuna valutazione finora

- Informefinalguia N°2Documento6 pagineInformefinalguia N°2koro joroNessuna valutazione finora

- Diodo LedDocumento4 pagineDiodo Ledkoro joroNessuna valutazione finora

- DIODODocumento10 pagineDIODOkoro joroNessuna valutazione finora

- El Transistor de UnijunturaDocumento4 pagineEl Transistor de Unijunturakoro joroNessuna valutazione finora

- Diodo ZenerDocumento3 pagineDiodo Zenerkoro joroNessuna valutazione finora

- Radio AmDocumento18 pagineRadio Amkoro joroNessuna valutazione finora

- VHDL - Final Digitales - Almenos Entiendan Lo Que Uno Hace No?Documento31 pagineVHDL - Final Digitales - Almenos Entiendan Lo Que Uno Hace No?koro joroNessuna valutazione finora

- Informev FISICAII-EXP3Documento18 pagineInformev FISICAII-EXP3Jose LuisNessuna valutazione finora

- Apunte FiltrosDocumento8 pagineApunte FiltrosTomás CabadoNessuna valutazione finora

- TC 20 29G11A P MS PanasonicDocumento36 pagineTC 20 29G11A P MS Panasoniccamarena_luisNessuna valutazione finora

- EXPERIMENTACION FÍSCA II Corriente Alterna Fin1Documento8 pagineEXPERIMENTACION FÍSCA II Corriente Alterna Fin1andresdelrojoNessuna valutazione finora

- Convertidores de Frecuencia ACS480Documento154 pagineConvertidores de Frecuencia ACS480RodrigoOrtegaPerochenaNessuna valutazione finora

- Cuestiones sobre antenas y propagaciónDocumento7 pagineCuestiones sobre antenas y propagaciónfulanito100% (3)

- Diseño de circuito de fuente de alimentación en ProteusDocumento9 pagineDiseño de circuito de fuente de alimentación en ProteusAlfonzo TorresNessuna valutazione finora

- Medidor de aislamiento GM-3125 hasta 5000V 1TGΩDocumento2 pagineMedidor de aislamiento GM-3125 hasta 5000V 1TGΩCesar Augusto Arias CastroNessuna valutazione finora

- Manual Control PunteadoraDocumento150 pagineManual Control PunteadoraodysseoNessuna valutazione finora

- Seccion 4 Simbología de Los Elementos Del Sistema de DistribuciónDocumento32 pagineSeccion 4 Simbología de Los Elementos Del Sistema de DistribuciónJesus Jaime BaezNessuna valutazione finora

- I.E.S. HIMILCE LINARES - Departamento de Electricidad-Electrónica Profesor - José María Hurtado Torres PDFDocumento35 pagineI.E.S. HIMILCE LINARES - Departamento de Electricidad-Electrónica Profesor - José María Hurtado Torres PDFAntoni Alfonso Chilón CabanillasNessuna valutazione finora

- Proyecto de Ondas MecanicasDocumento11 pagineProyecto de Ondas MecanicasLuis MartinezNessuna valutazione finora

- Informe 9 DigitalesDocumento9 pagineInforme 9 DigitalesJhoselin Heredia IchotaNessuna valutazione finora

- 4 - Circuitos Corriente Alterna PDFDocumento90 pagine4 - Circuitos Corriente Alterna PDFmelo16rlNessuna valutazione finora

- Check List Tablero + Equipos Electricos + Equipos PortatilesDocumento6 pagineCheck List Tablero + Equipos Electricos + Equipos PortatilesJulian FavaroNessuna valutazione finora

- Rectificador trifásico medición AC DCDocumento11 pagineRectificador trifásico medición AC DCmiyixpNessuna valutazione finora

- Taller Higiene IV Campos ElectromagniticoDocumento6 pagineTaller Higiene IV Campos ElectromagniticoIngrid ForyNessuna valutazione finora

- Reporte de Práctica (Mediciones Eléctricas)Documento4 pagineReporte de Práctica (Mediciones Eléctricas)lolitoNessuna valutazione finora

- TEMA 1 - InterrupcionesDocumento14 pagineTEMA 1 - InterrupcionesIrán TrujilloNessuna valutazione finora

- White Paper - InCTRL para Documentar Fallas Electricas (Lineas de Distribución)Documento19 pagineWhite Paper - InCTRL para Documentar Fallas Electricas (Lineas de Distribución)Joel Parra ZambranoNessuna valutazione finora

- Datasheet - Rectificador ETP48200Documento4 pagineDatasheet - Rectificador ETP48200Jaime Yarihuaman QuispeNessuna valutazione finora

- 3.9 Módulos Analógicos: Microcontroladores PIC - Programación en C Con EjemplosDocumento24 pagine3.9 Módulos Analógicos: Microcontroladores PIC - Programación en C Con EjemplosJuanJValenciaCruzNessuna valutazione finora

- SistemaTeleprocesoDocumento8 pagineSistemaTeleprocesoCarlos Eduardo PáezNessuna valutazione finora

- Cubicación de MaterialesDocumento11 pagineCubicación de MaterialesJoseAhumadaNessuna valutazione finora

- Sistema de Control Mi ParteDocumento14 pagineSistema de Control Mi PartesnayderNessuna valutazione finora

- Tarea #1 SubestacionesDocumento3 pagineTarea #1 SubestacionesMichael Steeven Ojeda DelgadoNessuna valutazione finora

- ProtocolosMMOOyFODocumento17 pagineProtocolosMMOOyFOmauricio6464Nessuna valutazione finora

- Aplicaciones básicas de amplificadores operacionalesDocumento5 pagineAplicaciones básicas de amplificadores operacionalesANDRES WLADIMIR NARANJO PEREZNessuna valutazione finora

- Manual Caragador BMWDocumento24 pagineManual Caragador BMWRaul BermudezNessuna valutazione finora

- Sistema de ArranqueDocumento17 pagineSistema de ArranqueIsrrael Fábrica QuispeNessuna valutazione finora

- Visualización de Códigos de Diagnóstico Moto Johnn DeereDocumento33 pagineVisualización de Códigos de Diagnóstico Moto Johnn DeereFrancisco Alvarado HuenquiaoNessuna valutazione finora