Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

MCZ33399 Freescale Semiconductor

Caricato da

goguCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

MCZ33399 Freescale Semiconductor

Caricato da

goguCopyright:

Formati disponibili

Freescale Semiconductor

www.DataSheet4U.com Document Number: MC33399

Advance Information Rev. 8.0, 10/2006

Local Interconnect Network

(LIN) Physical Interface 33399

Local Interconnect Network (LIN) is a serial communication

protocol designed to support automotive networks in conjunction with

Controller Area Network (CAN). As the lowest level of a hierarchical

LIN PHYSICAL INTERFACE

network, LIN enables cost-effective communication with sensors and

actuators when all the features of CAN are not required.

The 33399 is a Physical Layer component dedicated to automotive

sub-bus applications. It offers speed communication from 1.0 kbps to

20 kbps, and up to 60 kbps for Programming Mode. It has two

operating modes: Normal and Sleep.

The 33399 supports LIN Protocol Specification 1.3.

Features

• Nominal Operation from VSUP 7.0 V to 18 V DC, Functional up to

27 V DC Battery Voltage and Capable of Handling 40 V During

Load Dump D SUFFIX

EF SUFFIX (PB-FREE)

• Active Bus Waveshaping to Minimize Radiated Emission 98ASB42564B

• ± 5.0 kV ESD on LIN Bus Pin, ± 4.0 kV ESD on Other Pins 8 PIN SOICN

• 30 kΩ Internal Pullup Resistor

• Ground Shift Operation and Ground Disconnection Fail-Safe at

Module Level

• An Unpowered Node Does Not Disturb the Network ORDERING INFORMATION

• 20 µA in Sleep Mode Temperature

Device Package

• Wake-Up Capability from LIN Bus, MCU Command and Dedicated Range (TA)

High Voltage Wake-Up Input (Interface to External Switch)

MC33399D/R2

• Interface to MCU with CMOS-Compatible I/O Pins - 40°C to 125°C 8 SOICN

• Control of External Voltage Regulator MCZ33399EF/R2

• Pb-FREE packaging designated by package code EF

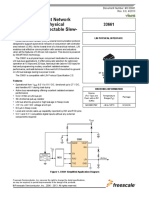

V PWR

Regulator

12 V

5.0 V 33399

VSUP WAKE

INH

GND

EN

MCU TXD

RXD LIN LIN Bus

Figure 1. 33399 Simplified Application Diagram

* This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2006. All rights reserved.

INTERNAL BLOCK DIAGRAM

INTERNAL BLOCK DIAGRAM

WAKE VSUP

INF Wake-Up

VREG

EN Control VREF

30 kΩ

Bias

Logic

RXD Receiver

LIN

Protection

TXD Driver

GND

Figure 2. 33399 Simplified Internal Block Diagram

33399

Analog Integrated Circuit Device Data

2 Freescale Semiconductor

PIN CONNECTIONS

PIN CONNECTIONS

RXD 1 8 INH

EN 2 7 VSUP

WAKE 3 6 LIN

TXD 4 5 GND

Figure 3. 33399 8-SOICN Pin Connections

Table 1. 8-SOICN Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 10.

Pin Pin Name Formal Name Definition

1 RXD Data Output MCU interface that reports the state of the LIN bus voltage.

2 EN Enable Control Controls the operation mode of the interface.

3 WAKE Wake Input High voltage input used to wake up the device from the Sleep mode.

4 TXD Data Input MCU interface that controls the state of the LIN output.

5 GND Ground Device ground pin.

6 LIN LIN Bus Bidirectional pin that represents the single-wire bus transmitter and receiver.

7 VSUP Power Supply Device power supply pin.

8 INH Inhibit Output Controls an external switchable voltage regulator having an inhibit input.

33399

Analog Integrated Circuit Device Data

Freescale Semiconductor 3

ELECTRICAL CHARACTERISTICS

MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

MAXIMUM RATINGS

Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or

permanent damage to the device.

Rating Symbol Value Unit

ELECTRICAL RATINGS

Power Supply Voltage VSUP V

Continuous Supply Voltage 27

Transient Voltage (Load Dump) 40

WAKE DC and Transient Voltage (Through a 33 kΩ Serial Resistor) VWAKE - 18 to 40 V

Logic Voltage (RXD, TXD, EN Pins) VLOG - 0.3 to 5.5 V

LIN Pin VBUS V

DC Voltage - 18 to 40

Transient (Coupled Through 1.0 nF Capacitor) - 150 to 100

INH Voltage / Current

DC Voltage VINH - 0.3 to VSUP + 0.3 V

ESD Voltage, Human Body Model (1) V ESD1 V

All Pins ± 4000

LIN Bus Pin with Respect to Ground ± 5000

ESD Voltage, Machine Model V ESD2 V

All Pins ± 200

THERMAL RATINGS

Operating Temperature °C

Ambient TA - 40 to 125

Junction TJ - 40 to 150

Storage Temperature TSTG - 55 to 165 °C

Thermal Resistance, Junction to Ambient RθJA 150 °C/W

(2) (3) °C

Peak Package Reflow Temperature During Reflow , TPPRT Note 3.

Thermal Shutdown TSHUT 150 to 200 °C

Thermal Shutdown Hysteresis THYST 8.0 to 20 °C

Notes

1. ESD1 testing is performed in accordance with the Human Body Model (CZAP = 100 pF, RZAP = 1500 Ω), ESD2 testing is performed in

accordance with the Machine Model (CZAP = 220 pF, RZAP = 0 Ω).

2. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may

cause malfunction or permanent damage to the device.

3. Freescale’s Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow

Temperature and Moisture Sensitivity Levels (MSL),

Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e.

MC33xxxD enter 33xxx), and review parametrics.

33399

Analog Integrated Circuit Device Data

4 Freescale Semiconductor

ELECTRICAL CHARACTERISTICS

STATIC ELECTRICAL CHARACTERISTICS

STATIC ELECTRICAL CHARACTERISTICS

Table 3. Static Electrical Characteristics

Characteristics noted under conditions 7.0 V ≤ VSUP ≤ 18 V, -40°C ≤ TA ≤ 125°C, GND = 0 V unless otherwise noted. Typical

values noted reflect the approximate parameter means at TA = 25°C under nominal conditions unless otherwise noted.

Characteristic Symbol Min Typ Max Unit

VSUP PIN (DEVICE POWER SUPPLY)

Supply Voltage Range VSUP 7.0 13.5 18 V

Supply Current in Sleep Mode µA

VLIN > VSUP - 0.5 V, VSUP < 14 V IS1 — 20 50

14 V < VSUP < 18 V IS2 — — 150

Supply Current in Normal Mode mA

Recessive State IS(REC) — — 2.0

Dominant State, Total Bus Load > 500 Ω IS(DOM) — — 3.0

Supply Undervoltage Threshold VSUP_UV 5.5 6.4 6.8 V

RXD OUTPUT PIN (LOGIC)

Low-Level Output Voltage VOL V

IIN ≤ 1.5 mA 0.0 — 0.9

High-Level Output Voltage VOH V

IOUT ≤ 250 µΑ 3.75 — 5.25

TXD INPUT PIN (LOGIC)

Low-Level Input Voltage VIL — — 1.5 V

High-Level Input Voltage VIH 3.5 — — V

Input Voltage Threshold Hysteresis VINHYST 100 550 800 mV

Pullup Current Source IPU µA

1.0 V < VTXD < 4.0 V, VEN = 5.0 V - 50 — - 25

EN INPUT PIN (LOGIC)

Low-Level Input Voltage VIL — — 1.5 V

High-Level Input Voltage VIH 3.5 — — V

Input Voltage Threshold Hysteresis VINHYST 100 480 800 mV

EN Low-Level Input Current IIL µA

VIN = 1.0 V 5.0 20 30

High-Level Input Current IIH µA

VIN = 4.0 V — 20 40

Pulldown Current IPD µA

1.0 V < EN < 4.0 V — 20 —

33399

Analog Integrated Circuit Device Data

Freescale Semiconductor 5

ELECTRICAL CHARACTERISTICS

STATIC ELECTRICAL CHARACTERISTICS

Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions 7.0 V ≤ VSUP ≤ 18 V, -40°C ≤ TA ≤ 125°C, GND = 0 V unless otherwise noted. Typical

values noted reflect the approximate parameter means at TA = 25°C under nominal conditions unless otherwise noted.

Characteristic Symbol Min Typ Max Unit

LIN PIN (VOLTAGE EXPRESSED VERSUS VSUP VOLTAGE)

Low-Level Bus Voltage (Dominant State) VDOM V

TXD LOW, VLIN = 40 mA 0.0 — 1.4

High-Level Voltage (Recessive State) VREC V

TXD HIGH, IOUT = 1.0 µA 0.85 VSUP — —

Internal Pullup Resistor to VSUP (4) RPU kΩ

- 40°C ≤ TA ≤ 70°C 20 30 47

70°C < TA ≤ 125°C 35 49 60

Current Limitation I LIM mA

TXD LOW, VLIN = VSUP 50 150 200

Leakage Current to GND I LEAK µA

Recessive State, VSUP - 0.3 V ≤ VLIN ≤ VSUP (4) 0.0 — 10

VSUP Disconnected, -18 V ≤ VLIN ≤ 18 V (Excluding Internal Pullup - 40 — 40

Source)

VSUP Disconnected, VLIN = -18 V (Including Internal Pullup Source) — - 600 —

VSUP Disconnected, VLIN = +18 V (Including Internal Pullup Source) — 15 —

LIN Receiver, Low-Level Input Voltage V LINL V

TXD HIGH, RXD LOW 0 VSUP — 0.4 VSUP

LIN Receiver, High-Level Input Voltage V LINH V

TXD HIGH, RXD HIGH 0.6 VSUP — VSUP

LIN Receiver Threshold Center V LINTH V

(VLINH - VLINL) / 2 — VSUP/2 —

LIN Receiver Input Voltage Hysteresis V LINHYS V

VLINH - VLINL 0.05 VSUP — 0.15 VSUP

LIN Wake-Up Threshold Voltage V LINWU 3.5 4.5 6.0 V

INH OUTPUT PIN

High-Level Voltage (Normal Mode) VWUH VSUP - 0.8 — VSUP V

Leakage Current (Sleep Mode) I LEAK µA

0 < VINH < VSUP 0 — 5.0

WAKE INPUT PIN

Typical Wake-Up Threshold (EN = 0 V, 7.0 V ≤ VSUP ≤ 18 V) (5) VWUTH V

HIGH-to-LOW Transition 0.3 VSUP 0.43 VSUP 0.55 VSUP

LOW-to-HIGH Transition 0.4 VSUP 0.55 VSUP 0.65 VSUP

Wake-Up Threshold Hysteresis VWUHYS 0.1 VSUP 0.16 VSUP 0.2 VSUP V

WAKE Input Current I WU µA

VWAKE ≤ 14 V — 1.0 5.0

VWAKE > 14 V — — 100

Notes

4. A diode structure is inserted with the pullup resistor to avoid parasitic current path from LIN to VSUP.

5. When VSUP is greater than 18 V, the wake-up voltage thresholds remain identical to the wake-up thresholds at 18 V.

33399

Analog Integrated Circuit Device Data

6 Freescale Semiconductor

ELECTRICAL CHARACTERISTICS

DYNAMIC ELECTRICAL CHARACTERISTICS

DYNAMIC ELECTRICAL CHARACTERISTICS

Table 4. Dynamic Electrical Characteristics

Characteristics noted under conditions 7.0 V ≤ VSUP ≤ 18 V, -40°C ≤ TA ≤ 125°C, GND = 0 V unless otherwise noted. Typical

values noted reflect the approximate parameter means at TA = 25°C under nominal conditions unless otherwise noted.

Characteristic Symbol Min Typ Max Unit

DIGITAL INTERFACE TIMING

LIN Slew Rate (6) , (7) V/µs

Falling Edge t FALL 0.75 2.0 3.0

Rising Edge t RISE 0.75 2.0 3.0

LIN Rise/Fall Symmetry (t RISE - t FALL) t SYM - 2.0 — 2.0 µs

(8) , (9)

Driver Propagation Delay µs

TXD LOW-to-LIN LOW t TXDLINL 0.0 — 4.0

TXD HIGH-to-LIN HIGH t TXDLINH 0.0 — 4.0

(9) , (10)

Receiver Propagation Delay µs

LIN LOW to RXD LOW t RXDLINL 2.0 4.0 6.0

LIN HIGH to RXD HIGH t RXDLINH 2.0 4.0 6.0

Receiver Propagation Delay Symmetry t RECSYM - 2.0 — 2.0 µs

Transmitter Propagation Delay Symmetry t TRSYM - 2.0 — 2.0 µs

(11)

Propagation Delay t PROPWL µs

LIN Bus Wake-Up to INH HIGH 45 70 130

Notess

6. Measured between 20 and 80 percent of bus signal for 10 V < VSUP < 18 V. Between 30 and 70 percent of signal for

7.0 V < VSUP < 10 V.

7. See Figure 5, page 8.

8. t TXDLINL is measured from TXD (HIGH-to-LOW) and LIN (VREC - 0.2 V). t TXDLINH is measured from TXD (LOW-to-HIGH) and LIN

(VDOM + 0.2 V).

9. See Figure 4, page 8.

10. Measured between LIN receiver thresholds and RXD pin.

11. See Figure 6, page 8.

33399

Analog Integrated Circuit Device Data

Freescale Semiconductor 7

ELECTRICAL CHARACTERISTICS

TIMING DIAGRAMS

TIMING DIAGRAMS

TXD

Recessive State

Recessive State

VREC

VREC - 0.2 V

t TXDLINL 0.6 VSUP

LIN

0.4 VSUP

VDOM VDOM + 0.2 V

Dominant State

RXD

t RXDLINH t TXDLINH t RXDLINL

Figure 4. Normal Mode Bus Timing Characteristics

t FALL

0.8 VSUP

Recessive State

0.2 VSUP VSUP

t RISE LIN

0.4 VSUP

Dominant State

0.8 VSUP

INH

t PROPWL

0.2 VSUP

Figure 5. LIN Rise and Fall Time Figure 6. LIN Bus Wake-Up

33399

Analog Integrated Circuit Device Data

8 Freescale Semiconductor

FUNCTIONAL DIAGRAMS

TIMING DIAGRAMS

FUNCTIONAL DIAGRAMS

WAKE State Change

LIN Bus

High

INH Low or Floating

High

INH Low or Floating

WAKE Filtering Time

Bus Wake-Up Filtering Time ( t PROGWL)

Voltage On State

Voltage On State Off State

Regulator

Regulator Node in

Off State

Node in

Regulator Wake-Up Time Delay Operation

Regulator Wake-Up Time Delay Operation

EN EN High EN EN High

Node in Sleep State Node in Sleep State

MCU Startup Time Delay MCU Startup Time Delay

Figure 7. LIN Wake-Up with INH Option Figure 8. LIN Wake-Up from Wake-Up Switch

LIN Bus

INH

(previous Wake-Up) Low or Floating High

Wake-Up Filtering Time (t PROGWL)

Voltage Reg On State

Wake-Up from Stop Mode

EN State Node In Operation

MCU in Stop Mode EN High

MCU Stop Mode Recovery/Startup Time Delay

I/O(2)

High Impedance / I/O in Input State Low

IRQ High Low High

Figure 9. LIN Wake-Up with MCU in Stop Mode

33399

Analog Integrated Circuit Device Data

Freescale Semiconductor 9

FUNCTIONAL DESCRIPTION

TIMING DIAGRAMS

FUNCTIONAL DESCRIPTION

INTRODUCTION

The 33399 is a Physical Layer component dedicated to The device offers three different wake-up capabilities:

automotive LIN sub-bus applications. wake-up from LIN bus, wake-up from the MCU command,

The 33399 features include speed communication from and dedicated high voltage wake-up input.

1.0 kbps to 20 kbps, up to 60 kbps for Programming Mode, The INH output may be used to control an external voltage

and active bus waveshaping to minimize radiated emission. regulator.

FUNCTIONAL PIN DESCRIPTION

POWER SUPPLY PIN (VSUP) This charge-up is achieved by the total system pullup current

The VSUP power supply pin is connected to a battery resistors. In order to guarantee that the rise time is within

through a serial diode for reverse battery protection. The DC specification, maximum bus capacitance should not exceed

operating voltage is from 7.0 V to 27 V. This pin sustains 10 nF with bus total pullup resistance less than 1.0 kΩ.

standard automotive voltage conditions such as 27 V DC

during jump-start conditions and 40 V during load dump. To Receiver Characteristics

avoid a false bus message, an undervoltage reset circuitry The receiver thresholds are ratiometric with the device

disables the transmission path (from TXD to LIN) when VSUP supply pin. Typical threshold is 50%, with a hysteresis

falls below 7.0 V. Supply current in the Sleep mode is between 5% and 10% of VSUP.

typically 20 µA.

DATA INPUT PIN (TXD)

GROUND PIN (GND) The TXD input pin is the MCU interface that controls the

In case of a ground disconnection at the module level, the state of the LIN output. When TXD is LOW, LIN output is

33399 does not have significant current consumption on the LOW; when TXD is HIGH, the LIN output transistor is turned

LIN bus pin when in the recessive state. (Less than 100 µA is OFF.

sourced from LIN bus pin, which creates 100 mV drop This pin has an internal 5.0 V internal pullup current

voltage from the 1.0 kΩ LIN bus pullup resistor.) For the source to set the bus in a recessive state in case the MCU is

dominant state, the pullup resistor should always be active. not able to control it; for instance, during system power-up/

The 33399 handles a ground shift up to 3.0 V when power-down. During the Sleep mode, the pullup current

VSUP > 9.0 V. Below 9.0 V VSUP, a ground shift can reduce source is turned OFF.

VSUP value below the minimum VSUP operation of 7.0 V.

DATA OUTPUT PIN (RXD)

LIN BUS PIN (LIN) The RXD output pin is the MCU interface that reports the

The LIN bus pin represents the single-wire bus transmitter state of the LIN bus voltage. LIN HIGH (recessive) is reported

and receiver. by a high level on RXD; LIN LOW (dominant) is reported by a

low voltage on RXD. RXD output structure is a CMOS-type

Transmitter Characteristics push-pull output stage.

The LIN driver is a low-side MOSFET with internal current

limitation and thermal shutdown. An internal pullup resistor ENABLE INPUT PIN (EN)

with a serial diode structure is integrated so no external The EN pin controls the operation mode of the interface. If

pullup components are required for the application in a slave EN = logic [1], the interface is in normal mode, with the

node. An additional pullup resistor of 1.0 kΩ must be added transmission path from TXD to LIN and from LIN to RXD both

when the device is used in the master node. active. If EN = logic [0], the device is in Sleep mode or low

Voltage can go from - 18 V to 40 V without current other power mode, and no transmission is possible.

than the pullup resistance. The LIN pin exhibits no reverse In Sleep mode, the LIN bus pin is held at VSUP through the

current from the LIN bus line to VSUP, even in the event of bus pullup resistors and pullup current sources. The device

GND shift or VPWR disconnection. LIN thresholds are can transmit only after being awakened. Refer to the INHIBIT

compatible with the LIN protocol specification. OUTPUT PIN (INH) description on page 11.

The fall time from recessive to dominant and the rise time During Sleep mode, the device is still supplied from the

from dominant to recessive are controlled to typically battery voltage (through VSUP pin). Supply current is 20 µA

2.0 V/µs. The symmetry between rise and fall time is also typical. Setting the EN pin to LOW will turn the INH to high

guaranteed. impedance. The EN pin has an internal 20 µA pulldown

When going from dominant to recessive, the bus current source to ensure the device is in Sleep mode if EN

impedance parasitic capacitor must be charged up to VSUP. floats.

33399

Analog Integrated Circuit Device Data

10 Freescale Semiconductor

FUNCTIONAL DESCRIPTION

TIMING DIAGRAMS

INHIBIT OUTPUT PIN (INH)

The INH pin controls an external switchable voltage

regulator having an inhibit input. This pin is a high-side switch

structure to VSUP. When the device is in the Normal mode,

the inhibit high-side switch is turned ON and the external

voltage regulator is activated. When the device is in Sleep

mode, the inhibit switch is turned OFF and disables the

voltage regulator (if this feature is used).

A wake-up event on the LIN bus line will switch the INH pin

to VSUP level. Wake-up output current capability is limited to

280 µA. INH can also drive an external MOSFET connected

to an MCU IRQ or XIRQ input to generate an interrupt. See

the typical application illustrated in Figure 13, page 15.

WAKE INPUT PIN (WAKE)

The WAKE pin is a high-voltage input used to wake up the

device from Sleep mode. WAKE is usually connected to an

external switch in the application. The typical WAKE

thresholds are VSUP / 2.

The WAKE pin has a special design structure and allows

wake-up from both HIGH-to-LOW or LOW-to-HIGH

transitions. When entering the Sleep mode, the LIN monitors

the state of the WAKE pin and stores it as a reference state.

The opposite state of this reference state will be the wake-up

event used by the device to re-enter Normal mode.

An internal filter is implemented (50 µs typical filtering time

delay). The WAKE pin input structure exhibits a high

impedance with extremely low input current when voltage at

this pin is below 14 V. When voltage at the WAKE pin

exceeds 14 V, input current starts to sink into the device. A

series resistor should be inserted in order to limit the input

current, mainly during transient pulses. Recommended

resistor value is 33 kΩ.

Important The WAKE pin should not be left open. If the

wake-up function is not used, WAKE should be connected to

GND to avoid false wake-up.

33399

Analog Integrated Circuit Device Data

Freescale Semiconductor 11

FUNCTIONAL DEVICE OPERATION

OPERATIONAL MODES

FUNCTIONAL DEVICE OPERATION

OPERATIONAL MODES

As described below and depicted in Figure 10 and Table 5 • LIN bus activity

on page 13, the 33399 has two operational modes, normal • Internal node wake-up (EN pin)

and sleep, and one transitional mode, Awake. • Wake-up from WAKE pin

Figures 7, 8, and 9 on page 9 show device application

NORMAL MODE circuit and detail of wake-up operations.

This is the normal transmitting and receiving mode. All

features are available. Wake-Up from LIN Bus (Awake Transitional Mode)

A wake-up from the LIN pin switching from recessive to

SLEEP MODE dominant state (switch from VSUP to GND) can occur. This is

In this mode the transmission path is disabled and the achieved by a node sending a wake-up frame on the bus.

device is in low power mode. Supply current from VSUP is This condition internally wakes up the interface, which

20 µA typical. Wake-up can occur from LIN bus activity, as switches the INH pin to a HIGH level to enable the voltage

well as from node internal wake-up through the EN pin and regulator. The device switches into the Awake mode. The

the WAKE input pin. microcontroller and the complete application power up. The

microcontroller must switch the EN pin to a HIGH level to

DEVICE POWER-UP (AWAKE TRANSITIONAL allow the device to leave the Awake mode and turn it into

MODE) Normal mode in order to allow communication on the bus.

At system power-up (VSUP rises from zero), the 33399

Wake-Up from Internal Node Activity (Normal Mode)

automatically switches into the “Awake” mode (refer to

Figure 10 below and Table 5 on page 13. It switches the INH The application can internally wake up. In this case the

pin in HIGH state to VSUP level. The microcontroller of the microcontroller of the application sets the EN pin in the HIGH

application then confirms the Normal mode by setting the EN state. The device switches into Normal mode.

pin HIGH.

Wake-Up from WAKE Pin (Awake Transitional Mode)

DEVICE WAKE-UP EVENTS The application can wake up with the activation of an

The device can be awakened from Sleep mode by three external switch. Refer to Table 1, 8-SOICN Pin Definitions on

wake-up events: page 3.

Power-Up/

Down

VPWR < 7.0 V VPWR < 7.0 V

VPWR > 7.0 V VPWR < 7.0 V

LIN Bus or WAKE Pin

Wake-Up EN HIGH Normal

Sleep Awake 1.0 to 20

kbps

EN HIGH (Local Wake-Up Event)

EN LOW

Note Refer to Table 5 for explanation.

Figure 10. Operational and Transitional Modes State Diagram

33399

Analog Integrated Circuit Device Data

12 Freescale Semiconductor

FUNCTIONAL DEVICE OPERATION

PROTECTION AND DIAGNOSIS FEATURES

Table 5. Explanation of Operational and Transitional Modes State Diagram

Operational/

LIN INH EN TXD RXD

Transitional

Sleep Mode Recessive state, driver off. LOW LOW X High impedance.

20 µA pullup current source.

Awake Recessive state, driver off. HIGH LOW X LOW.

Normal Mode Driver active. 30 kΩ pullup active. HIGH HIGH LOW to drive LIN bus in Report LIN bus level:

dominant. • LOW LIN bus dominant

HIGH to drive LIN bus in • HIGH LIN bus recessive

recessive.

X = Don’t care.

PROTECTION AND DIAGNOSIS FEATURES

ELECTROSTATIC DISCHARGE (ESD)

The 33399 has two Human Body Model ESD values. All

pins can handle ± 4.0 kV. The LIN bus pin, with respect to

ground, can handle ± 5.0 kV.

ELECTROMAGNETIC COMPATIBILITY

RADIATED EMISSION ON LIN BUS OUTPUT LINE On the WAKE input pin, an internal filter is implemented to

Radiated emission level on the LIN bus output line is reduce false wake-up during external disturbance.

internally limited and reduced by active slew rate control of

the output bus driver. Figure 11 shows the results in the NOISE FILTERING

frequency range 100 kHz to 2.0 MHz. Noise filtering is used to protect the electronic module

against illegal wake-up spikes on the bus. Integrated receiver

ELECTROMAGNETIC IMMUNITY (EMI) filters suppress any high-frequency (HF) noise induced into

On the LIN bus pin, the 33399 offers high EMI level from the bus wires. The cut-off frequency of these filters is a

external disturbance occurring at the LIN bus pin in order to compromise between propagation delay and HF

guarantee communication during external disturbance. suppression.

Figure 11. Radiated Emission in Normal Mode

33399

Analog Integrated Circuit Device Data

Freescale Semiconductor 13

TYPICAL APPLICATIONS

TYPICAL APPLICATIONS

The 33399 can be configured in several applications. Figures 12 and 13 show slave and master node applications. An

additional pullup resistor of 1.0 kΩ in series with a diode must be added when the device is used in the master node.

External Switch

VPWR

VREG

Regulator

12V INH WAKE 33399 VSUP

5.0V

5.0 V

Wake-Up

INH

Regulator

LIN Bus

EN Control VREF 30

VDD I/O

Bias kΩ

MCU Logic

Actuator RXD

M Driver Receiver LIN

Protection

SCI

TXD

Driver

GND

Figure 12. Slave Node Typical Application with WAKE Input Switch and INH

(Switchable 5.0 V Regulator)

33399

Analog Integrated Circuit Device Data

14 Freescale Semiconductor

TYPICAL APPLICATIONS

External Switch

VPWR

Master Node

Pullup

Regulator

1.0

5.0 V 33399

12V WAKE VSUP kΩ

5.0V

INH Wake-Up

Regulator

LIN Bus

5.0 V VDD IRQ Control VREF 30

EN

I/O Bias kΩ

I/O(2)

MCU Logic

Actuator RXD

M Driver Receiver LIN

SCI Protection

TXD

Driver

GND

Figure 13. Master Node Typical Device Application with MCU Wake-Up from Stop Mode

(Non-Switchable 5.0 V Regulator, MCU Stop Mode)

33399

Analog Integrated Circuit Device Data

Freescale Semiconductor 15

REFERENCE DOCUMENTS

REFERENCE DOCUMENTS

Table 6. Reference Documents

Title LIterature Order Number

Local Interconnect Network (LIN) Physical Interface: Difference Between MC33399 and MC33661 EB215

33399

Analog Integrated Circuit Device Data

16 Freescale Semiconductor

PACKAGING

PACKAGE DIMENSIONS

PACKAGING

PACKAGE DIMENSIONS

Important For the most current revision of the package, visit www.freescale.com and do a keyword search on the 98A

drawing number below.

D SUFFIX

EF SUFFIX (Pb-FREE)

8-PIN SOIC NARROW BODY

PLASTIC PACKAGE

98ASB42564B

ISSUE U

33399

Analog Integrated Circuit Device Data

Freescale Semiconductor 17

REVISION HISTORY

REVISION HISTORY

REVISION DATE DESCRIPTION OF CHANGES

7.0 7/2006 • Implemented Revision History page

• Added Pb-Free suffix code EF

• Added EPP ordering part number MCZ33399EF/R2

• Adjusted to the Freescale prevailing form and style

8.0 10/2006 • Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter

from MAXIMUM RATINGS on page 4. Added note with instructions to obtain this

information from www.freescale.com.

33399

Analog Integrated Circuit Device Data

18 Freescale Semiconductor

How to Reach Us:

Home Page:

www.freescale.com RoHS-compliant and/or Pb-free versions of Freescale products have the functionality

and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free

Web Support: counterparts. For further information, see http://www.freescale.com or contact your

http://www.freescale.com/support Freescale sales representative.

USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. For information on Freescale’s Environmental Products program, go to http://

Technical Information Center, EL516 www.freescale.com/epp.

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center Information in this document is provided solely to enable system and software

Schatzbogen 7 implementers to use Freescale Semiconductor products. There are no express or

81829 Muenchen, Germany implied copyright licenses granted hereunder to design or fabricate any integrated

+44 1296 380 456 (English) circuits or integrated circuits based on the information in this document.

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French) Freescale Semiconductor reserves the right to make changes without further notice to

www.freescale.com/support any products herein. Freescale Semiconductor makes no warranty, representation or

guarantee regarding the suitability of its products for any particular purpose, nor does

Japan: Freescale Semiconductor assume any liability arising out of the application or use of any

Freescale Semiconductor Japan Ltd. product or circuit, and specifically disclaims any and all liability, including without

Headquarters limitation consequential or incidental damages. “Typical” parameters that may be

ARCO Tower 15F provided in Freescale Semiconductor data sheets and/or specifications can and do vary

1-8-1, Shimo-Meguro, Meguro-ku,

in different applications and actual performance may vary over time. All operating

Tokyo 153-0064

Japan parameters, including “Typicals”, must be validated for each customer application by

0120 191014 or +81 3 5437 9125 customer’s technical experts. Freescale Semiconductor does not convey any license

support.japan@freescale.com under its patent rights nor the rights of others. Freescale Semiconductor products are

not designed, intended, or authorized for use as components in systems intended for

Asia/Pacific: surgical implant into the body, or other applications intended to support or sustain life,

Freescale Semiconductor Hong Kong Ltd. or for any other application in which the failure of the Freescale Semiconductor product

Technical Information Center could create a situation where personal injury or death may occur. Should Buyer

2 Dai King Street purchase or use Freescale Semiconductor products for any such unintended or

Tai Po Industrial Estate unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and

Tai Po, N.T., Hong Kong

its officers, employees, subsidiaries, affiliates, and distributors harmless against all

+800 2666 8080

support.asia@freescale.com claims, costs, damages, and expenses, and reasonable attorney fees arising out of,

directly or indirectly, any claim of personal injury or death associated with such

For Literature Requests Only: unintended or unauthorized use, even if such claim alleges that Freescale

Freescale Semiconductor Literature Distribution Center Semiconductor was negligent regarding the design or manufacture of the part.

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140 Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

Fax: 303-675-2150 All other product or service names are the property of their respective owners.

LDCForFreescaleSemiconductor@hibbertgroup.com © Freescale Semiconductor, Inc., 2006. All rights reserved.

MC33399

Rev. 8.0

10/2006

Potrebbero piacerti anche

- Automotive ISO 9141 Serial Link Driver: Technical DataDocumento18 pagineAutomotive ISO 9141 Serial Link Driver: Technical DataP GlNessuna valutazione finora

- SONOACE R5 v1.02.00 Vol1 EDocumento172 pagineSONOACE R5 v1.02.00 Vol1 Engocbienk56Nessuna valutazione finora

- Local Interconnect Network (LIN) Enhanced Physical Interface With Selectable Slew-RateDocumento22 pagineLocal Interconnect Network (LIN) Enhanced Physical Interface With Selectable Slew-RateDanny Alexander Bodegas pinedaNessuna valutazione finora

- Controlador CAN MC33389Documento49 pagineControlador CAN MC33389Jorge Martinez PerezNessuna valutazione finora

- MC33742 PDFDocumento72 pagineMC33742 PDFfraurNessuna valutazione finora

- AD5662Documento24 pagineAD5662mar_barudjNessuna valutazione finora

- SC900Documento23 pagineSC900Robert PNessuna valutazione finora

- MC33897 (SWC)Documento19 pagineMC33897 (SWC)bettinemed2023Nessuna valutazione finora

- Si4021 Universal ISM Band FSK TransmitterDocumento35 pagineSi4021 Universal ISM Band FSK TransmitterViccRaNessuna valutazione finora

- LIN System Basis Chip With DC Motor Pre-Driver: Advance InformationDocumento45 pagineLIN System Basis Chip With DC Motor Pre-Driver: Advance InformationPanagiotis PanagosNessuna valutazione finora

- LIN J2602 Transceiver: Features DescriptionDocumento32 pagineLIN J2602 Transceiver: Features DescriptionMoez MizouNessuna valutazione finora

- 5.0 A Throttle Control H-BridgeDocumento26 pagine5.0 A Throttle Control H-Bridgerumellemur59Nessuna valutazione finora

- CYG2111Documento5 pagineCYG2111mendezp2410Nessuna valutazione finora

- Tps 40056Documento34 pagineTps 40056cristian cendejasNessuna valutazione finora

- Nxpusainc Mc33926pnb Datasheets 8993Documento35 pagineNxpusainc Mc33926pnb Datasheets 8993Nooragha TanhaNessuna valutazione finora

- ISO K Line Serial Link Interface: Technical DataDocumento12 pagineISO K Line Serial Link Interface: Technical DataSergPodoprigoraNessuna valutazione finora

- Onsm S A0013302101 1Documento16 pagineOnsm S A0013302101 1123Nessuna valutazione finora

- Nb679a MpsDocumento19 pagineNb679a MpswarkeravipNessuna valutazione finora

- MCP 14628Documento24 pagineMCP 14628Hưng ĐứcNessuna valutazione finora

- MAX15021Documento24 pagineMAX15021Phong Phan CôngNessuna valutazione finora

- Power Power: Designer DesignerDocumento8 paginePower Power: Designer DesignerNeha JainNessuna valutazione finora

- Iso Serial Link Interface: Semiconductor Technical DataDocumento4 pagineIso Serial Link Interface: Semiconductor Technical Datawramadhani65Nessuna valutazione finora

- Data Sheet: LIN TransceiverDocumento22 pagineData Sheet: LIN TransceiverBo MinnNessuna valutazione finora

- LTC3612Documento30 pagineLTC3612Alexandr IvanovNessuna valutazione finora

- MAX2753Documento6 pagineMAX2753Moha'dNessuna valutazione finora

- MC33390Documento16 pagineMC33390bettinemed2023Nessuna valutazione finora

- NCP45790 D-2317241Documento13 pagineNCP45790 D-2317241SuBaRu GTNessuna valutazione finora

- MC33290Documento12 pagineMC33290Harris RaoNessuna valutazione finora

- Microcontroller and Triacs ON THE 110/240V MAINS: Application NoteDocumento12 pagineMicrocontroller and Triacs ON THE 110/240V MAINS: Application NoteMaha SoeNessuna valutazione finora

- A5984 DatasheetDocumento28 pagineA5984 DatasheetIndraz NilNessuna valutazione finora

- Quad High-Side and Octal Low-Side Switch For Automotive: Advance InformationDocumento40 pagineQuad High-Side and Octal Low-Side Switch For Automotive: Advance InformationDavid MendezNessuna valutazione finora

- Tsop 752 WDocumento13 pagineTsop 752 WMatias RendonNessuna valutazione finora

- High Performance, Triple-Output, Auto-Tracking Combo ControllerDocumento15 pagineHigh Performance, Triple-Output, Auto-Tracking Combo ControllerrolandseNessuna valutazione finora

- Multiple Switch Detection Interface With Suppressed Wake-Up: Technical DataDocumento32 pagineMultiple Switch Detection Interface With Suppressed Wake-Up: Technical Datakatty cumbeNessuna valutazione finora

- HIP6302CBDocumento18 pagineHIP6302CBrjbordaNessuna valutazione finora

- Power Factor Corrector: 1 FeaturesDocumento13 paginePower Factor Corrector: 1 Featuresdeilyn rivasNessuna valutazione finora

- Sc900a PDFDocumento23 pagineSc900a PDFgoguNessuna valutazione finora

- LT 8364Documento32 pagineLT 8364gtcv805Nessuna valutazione finora

- MAX77533 14V Input, 1.5A High-Efficiency Buck Converter with 9μA IDocumento32 pagineMAX77533 14V Input, 1.5A High-Efficiency Buck Converter with 9μA Ijohn doewrNessuna valutazione finora

- MC33886Documento28 pagineMC33886abel manuel chico oleceNessuna valutazione finora

- Adf4351 PDFDocumento28 pagineAdf4351 PDFEyeVeeNessuna valutazione finora

- SN65HVD1050DR Texas InstrumentsDocumento21 pagineSN65HVD1050DR Texas InstrumentsMoises HernandezNessuna valutazione finora

- A4960 A Automotive DatasheetDocumento34 pagineA4960 A Automotive DatasheetCanerNessuna valutazione finora

- SYFgtj MZ2 Ds X6 TRXC ZSog 91 Yk JZW 30 IUBtl 8 JAb JDocumento34 pagineSYFgtj MZ2 Ds X6 TRXC ZSog 91 Yk JZW 30 IUBtl 8 JAb Jccpsf4fkhtNessuna valutazione finora

- Silergy-Corp-SY8286ARAC C178251Documento16 pagineSilergy-Corp-SY8286ARAC C178251ziya tutuNessuna valutazione finora

- TJA1020TDocumento24 pagineTJA1020TJose RojasNessuna valutazione finora

- Datasheet 2021 PDFDocumento47 pagineDatasheet 2021 PDFLuisEduardoPeñalverNessuna valutazione finora

- High Frequency Switch Mode Li-Ion Battery Charger ADP3806: Features General DescriptionDocumento16 pagineHigh Frequency Switch Mode Li-Ion Battery Charger ADP3806: Features General DescriptionPourya EskandariNessuna valutazione finora

- Receptor UHF T5743P6Documento41 pagineReceptor UHF T5743P6Jorge Martinez PerezNessuna valutazione finora

- LTC 15389 FDocumento32 pagineLTC 15389 FEdson HenriqueNessuna valutazione finora

- Single Intelligent High-Current Self-Protected Silicon High-Side Switch (2.0 MDocumento24 pagineSingle Intelligent High-Current Self-Protected Silicon High-Side Switch (2.0 MElectronica Ave FenixNessuna valutazione finora

- Programmable DC/DC Controller For Advanced Microprocessors: Device Package Temp Range (T)Documento6 pagineProgrammable DC/DC Controller For Advanced Microprocessors: Device Package Temp Range (T)ibrahim başderNessuna valutazione finora

- ACS37800 DatasheetDocumento41 pagineACS37800 DatasheetSunil Kumar ThakurNessuna valutazione finora

- Dual Voltage Comparator LM393: FeaturesDocumento4 pagineDual Voltage Comparator LM393: FeaturesSteven ChowNessuna valutazione finora

- MC33879Documento26 pagineMC33879AENessuna valutazione finora

- APX9131A: Features General DescriptionDocumento12 pagineAPX9131A: Features General DescriptionChek OmarovNessuna valutazione finora

- Industry's Lowest-Power Ambient Light Sensor With ADC: General Description FeaturesDocumento20 pagineIndustry's Lowest-Power Ambient Light Sensor With ADC: General Description Featuresabraham samadNessuna valutazione finora

- Industry's Lowest-Power Ambient Light Sensor With ADC: General Description FeaturesDocumento20 pagineIndustry's Lowest-Power Ambient Light Sensor With ADC: General Description FeaturesMamat RahmatNessuna valutazione finora

- DVPDNET-SL Instruction enDocumento2 pagineDVPDNET-SL Instruction enMauro Sebastián AlvarizaNessuna valutazione finora

- 5975 Series MSD Troubleshooting and Maintenance Manual G3170-90037Documento276 pagine5975 Series MSD Troubleshooting and Maintenance Manual G3170-90037Adolfo AlvarezNessuna valutazione finora

- CV-X400/X300 Series: Intuitive Vision SystemDocumento20 pagineCV-X400/X300 Series: Intuitive Vision Systemeduardo.juarezNessuna valutazione finora

- Installation Instructions: 256 Series Paralleling & Reverse Power Protector Trip RelayDocumento2 pagineInstallation Instructions: 256 Series Paralleling & Reverse Power Protector Trip RelaySreekanth SunkeNessuna valutazione finora

- Fender Princeton 65 DSPDocumento8 pagineFender Princeton 65 DSPMiniEscortNessuna valutazione finora

- ZCS300Manual PDFDocumento24 pagineZCS300Manual PDFمهندس الكترونيNessuna valutazione finora

- Hitachi Cdh-Le24fd04 CH 8m35s SvcmnlsDocumento39 pagineHitachi Cdh-Le24fd04 CH 8m35s SvcmnlsCarlosClarosNessuna valutazione finora

- Radiodetection Rd8000 Operation ManualDocumento52 pagineRadiodetection Rd8000 Operation ManualOriginal BrazilianNessuna valutazione finora

- L7 Users ManualDocumento241 pagineL7 Users ManualKike GuevaraNessuna valutazione finora

- Manual Inversor QseriesDocumento76 pagineManual Inversor QseriesOscar MarkelNessuna valutazione finora

- Operating Instructions and Installation Information Mettler Toledo Multirange ID7xx-Base Weighing TerminalDocumento116 pagineOperating Instructions and Installation Information Mettler Toledo Multirange ID7xx-Base Weighing Terminalmariusz sNessuna valutazione finora

- Jayanth Seminar Report FINDocumento40 pagineJayanth Seminar Report FINVineth RaoNessuna valutazione finora

- CW60 Manual Ver1.1 ENG 140210Documento37 pagineCW60 Manual Ver1.1 ENG 140210Ivan LauNessuna valutazione finora

- XTV 9 Operation ManualDocumento12 pagineXTV 9 Operation ManualpowerliftermiloNessuna valutazione finora

- Motorola U9Documento92 pagineMotorola U9crysti_reyes4314Nessuna valutazione finora

- Cube Stex OmDocumento16 pagineCube Stex Omjames choNessuna valutazione finora

- Hctx-Manual (Eng) - 10 05 25Documento14 pagineHctx-Manual (Eng) - 10 05 25onlylovetdNessuna valutazione finora

- XN-9000 Ifu Na (1211)Documento498 pagineXN-9000 Ifu Na (1211)CARLOSNessuna valutazione finora

- LMVM2085 TrainingManualDocumento86 pagineLMVM2085 TrainingManualequus43100% (1)

- Instruction Manual: Multiple Shot Reclosing Relay BE1-79MDocumento74 pagineInstruction Manual: Multiple Shot Reclosing Relay BE1-79Mbaosyle9201Nessuna valutazione finora

- 009 11253 General DescriptionDocumento259 pagine009 11253 General DescriptionSalvador FayssalNessuna valutazione finora

- Appusb300h2 Quick User GuideDocumento37 pagineAppusb300h2 Quick User GuideJorge MerinoNessuna valutazione finora

- Lubricant Es 2Documento296 pagineLubricant Es 2Rafael CardenasNessuna valutazione finora

- NorsokDocumento26 pagineNorsokOchie RomeroNessuna valutazione finora

- GPFC250 Commercial/GPFM250 Medical: 250 Watt Global Performance SwitchersDocumento2 pagineGPFC250 Commercial/GPFM250 Medical: 250 Watt Global Performance SwitchersmohammedNessuna valutazione finora

- FLEXmaster User Manual 4 02Documento302 pagineFLEXmaster User Manual 4 02Felix GalanNessuna valutazione finora

- DLL Radio Waves 8 14 17Documento4 pagineDLL Radio Waves 8 14 17Helen Grace Llemos CabalagNessuna valutazione finora

- Operating Instructions: PT-LC76U PT-LC56UDocumento69 pagineOperating Instructions: PT-LC76U PT-LC56UOscar Mauricio Coronel MoralesNessuna valutazione finora

- BestView Handheld Color Video MonitorDocumento12 pagineBestView Handheld Color Video MonitorjkohnNessuna valutazione finora

- R4-2106868 PerfEnh2 IRC Intra-Cell Inter-UserDocumento7 pagineR4-2106868 PerfEnh2 IRC Intra-Cell Inter-UsergrasspackingNessuna valutazione finora