Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Ec 206 Computer Organisation

Caricato da

Justin Saju0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

28 visualizzazioni2 pagineKTU sylabus

Copyright

© © All Rights Reserved

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoKTU sylabus

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

28 visualizzazioni2 pagineEc 206 Computer Organisation

Caricato da

Justin SajuKTU sylabus

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 2

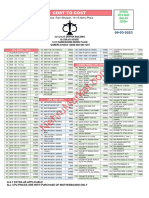

Course Course Name L-T-P - Year of

code Credits Introduction

EC206 COMPUTER ORGANISATION 3-0-0-3 2016

Prerequisite: EC207 Logic Circuit Design

Course Objectives

To impart knowledge in computer architecture.

To impart knowledge in machine language programming.

To develop understanding on I/O accessing techniques and memory structures.

Syllabus

Functional units of a computer, Arithmetic circuits, Processor architecture, Instructions and

addressing modes, Execution of program, Micro architecture design process, Design of data path

and control units, I/O accessing techniques, Memory concepts, Memory interface, Cache and

Virtual memory concepts.

Expected outcome .

The students will be able to:

i. Understand the functional units of a computer

ii. Identify the different types of instructions

iii. Understand the various addressing modes

iv. Understand the I/O addressing system

v. Categorize the different types of memories

Text Book:

1. David A. Patterson and John L. Hennessey, Computer Organisation and Design, Fourth

Edition, Morgan Kaufmann

2. David Money Harris, Sarah L Harris, Digital Design and Computer Architecture,Morgan

Kaufmann – Elsevier, 2009

References:

1. Carl Hamacher : “Computer Organization ”, Fifth Edition, Mc Graw Hill

2. John P Hayes: “Computer Architecture and Organisation”, Mc Graw Hill

3. William Stallings: “Computer Organisation and Architecture”, Pearson Education

4. Andrew S Tanenbaum: “Structured Computer Organisation”, Pearson Education

5. Craig Zacker: “PC Hardware : The Complete Reference”, TMH

Course Plan

Sem.

Module Contents Hours Exam

Marks

Functional units of a computer

Arithmetic Circuits: Adder-carry propagate adder, Ripple carry

4

adder, Basics of carry look ahead and prefix adder, Subtractor,

I Comparator, ALU 15%

Shifters and rotators, Multiplication, Division 3

Number System: Review of Fixed point & Floating point number

1

system

Architecture : Assembly Language, Instructions, Operands,

2

Registers, Register set, Memory, Constants

II 15%

Machine Language: R-Type, I-Type, J-Type Instructions,

3

Interpreting machine language code

FIRST INTERNAL EXAMINATION

MIPS Addressing modes – Register only, Immediate, Base, PC-

III 3 15%

relative, Pseudo - direct

MIPS memory map, Steps for executing a program - Compilation,

3

Assembling, Linking, Loading

Pseudoinstuctions, Exceptions, Signed and Unsigned instructions,

3

Floating point instructions

MIPS Microarchitectures – State elements of MIPS processor 1

Design process and performance analysis of Single cycle

processor, Single cycle data path, Single cycle control for R – type 3

IV arithmetic/logical instructions. 15%

Design process and performance analysis of multi cycle processor,

Multi cycle data path, Multi cycle control for R – type 3

arithmetic/logical instructions.

SECOND INTERNAL EXAMINATION

I/O system – Accessing I/O devices, Modes of data transfer, 20%

Programmed I/O, Interrupt driven I/O, Direct Memory Access,

3

Standard I/O interfaces – Serial port, Parallel port, PCI, SCSI, and

USB.

V

Memory system – Hierarchy, Characteristics and Performance

analysis, Semiconductor memories (RAM, ROM, EPROM),

4

Memory Cells – SRAM and DRAM, internal organization of a

memory chip, Organization of a memory unit.

Cache Memory – Concept/principle of cache memory, Cache size, 20%

mapping methods – direct, associated, set associated, Replacement 3

VI algorithms, Write policy- Write through, Write back.

Virtual Memory – Memory management, Segmentation, Paging,

3

Address translation, Page table, Translation look aside buffer.

END SEMESTER EXAM

Question Paper Pattern

The question paper shall consist of three parts. Part A covers I and II module, Part B covers

III and IV module, Part C covers V and VI module. Each part has three questions, which may

have maximum four subdivisions. Among the three questions, one will be a compulsory

question covering both modules and the remaining from each module, of which one to be

answered. Part A & Part B questions shall carry 15 marks each and Part C questions shall

carry 20 marks each with maximum 80 % for theory and 20% for logical/numerical

problems, derivation and proof.

Potrebbero piacerti anche

- Fy BSC Computer ScienceDocumento7 pagineFy BSC Computer ScienceHemlata GuptaNessuna valutazione finora

- Foundations of Computing: Essential for Computing Studies, Profession And Entrance Examinations - 5th EditionDa EverandFoundations of Computing: Essential for Computing Studies, Profession And Entrance Examinations - 5th EditionNessuna valutazione finora

- Project Computer Sales and Service CentreDocumento20 pagineProject Computer Sales and Service CentreDil Muhammad87% (23)

- Prerequisite: EC207 Logic Circuit DesignDocumento2 paginePrerequisite: EC207 Logic Circuit DesignplbonifusNessuna valutazione finora

- 4 Ece CaoDocumento69 pagine4 Ece CaoAnandu KumarNessuna valutazione finora

- To Introduce The Concepts of Processor Logic Design and Control Logic DesignDocumento27 pagineTo Introduce The Concepts of Processor Logic Design and Control Logic DesignJessel CherianNessuna valutazione finora

- Coa, Com, Co Lam SyllabusDocumento4 pagineCoa, Com, Co Lam Syllabusnaga sitaram mNessuna valutazione finora

- COAVITDocumento3 pagineCOAVITnikshithNessuna valutazione finora

- Agenda Item 65/39 - Annexure - 35Documento2 pagineAgenda Item 65/39 - Annexure - 35Nandhika RavuriNessuna valutazione finora

- II B.Tech I Semester: Academic Dairy For Computer OrganizationDocumento8 pagineII B.Tech I Semester: Academic Dairy For Computer OrganizationmmvprasadNessuna valutazione finora

- Agenda Item 65/39 - Annexure - 35 Proceedings of The 65th Academic Council (17.03.2022) 979Documento2 pagineAgenda Item 65/39 - Annexure - 35 Proceedings of The 65th Academic Council (17.03.2022) 979vorirNessuna valutazione finora

- Module Part1Documento21 pagineModule Part1Charan ChowdaryNessuna valutazione finora

- SYLLABUSDocumento2 pagineSYLLABUSHardik PandyaNessuna valutazione finora

- Subject Code Subject Name Credits: Overview of Computer Architecture & OrganizationDocumento4 pagineSubject Code Subject Name Credits: Overview of Computer Architecture & Organizationanon_71491248Nessuna valutazione finora

- Computer Organization DFDocumento3 pagineComputer Organization DFIMRAN PATELNessuna valutazione finora

- 17EC2504A SyllabusDocumento2 pagine17EC2504A SyllabusMmk ReddyNessuna valutazione finora

- Computer OrganizationDocumento67 pagineComputer OrganizationDani RaniNessuna valutazione finora

- BScCSIT III Semester Micro SyllabusDocumento4 pagineBScCSIT III Semester Micro SyllabusBijay MishraNessuna valutazione finora

- CS202 Computer Organisation and Architecture KTU S4 SyllabusDocumento3 pagineCS202 Computer Organisation and Architecture KTU S4 SyllabusRishabh100% (1)

- Computer Organizationand Architecture SyllabusDocumento3 pagineComputer Organizationand Architecture SyllabuskrupeshNessuna valutazione finora

- 18BCS109MICROPROCESSORS AND ITS APPLICATIONS4 0 0 4-SyllabusDocumento2 pagine18BCS109MICROPROCESSORS AND ITS APPLICATIONS4 0 0 4-SyllabusEmma WatsonNessuna valutazione finora

- Computer OrganizationDocumento4 pagineComputer Organizationudit_mca_blyNessuna valutazione finora

- Bca Major Syllabus - 2ND SemDocumento7 pagineBca Major Syllabus - 2ND Sempradipta.sarkarNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitectureShiv Kumar100% (1)

- The Night Before ExamsDocumento10 pagineThe Night Before ExamsPrashanth AcharNessuna valutazione finora

- Microprocessor and Interfacing: Course Contents (Uec Scheme)Documento7 pagineMicroprocessor and Interfacing: Course Contents (Uec Scheme)Arpit SinghNessuna valutazione finora

- CS202 Computer Organisation and ArchitectureDocumento3 pagineCS202 Computer Organisation and ArchitectureGokul Krishna MNessuna valutazione finora

- Scheme of Examination For Master of Computer APPLICATIONS (M.C.A.) W.E.F. Academic Session 2014-15Documento11 pagineScheme of Examination For Master of Computer APPLICATIONS (M.C.A.) W.E.F. Academic Session 2014-15Siddharth JainNessuna valutazione finora

- Module 1Documento31 pagineModule 1KUMAR RISHAVNessuna valutazione finora

- Computer System ArchitectureDocumento6 pagineComputer System ArchitectureSona SimonNessuna valutazione finora

- EC308 Embedded SystemsDocumento3 pagineEC308 Embedded SystemsSujith ThomasNessuna valutazione finora

- Computer Organization: Course ObjectivesDocumento2 pagineComputer Organization: Course Objectivesರಘು ಕಟಗಲ್ಲNessuna valutazione finora

- Cse2001 Computer-Architecture-And-Organization TH 1.0 37 Cse2001Documento2 pagineCse2001 Computer-Architecture-And-Organization TH 1.0 37 Cse2001devipriyaNessuna valutazione finora

- FYCSDocumento10 pagineFYCSrehan shaikhNessuna valutazione finora

- Cao SyllabusDocumento2 pagineCao SyllabuskrishnavadlamudiNessuna valutazione finora

- SyllabusDocumento2 pagineSyllabussdm321Nessuna valutazione finora

- JNTUH MCA Syllabus 2013Documento107 pagineJNTUH MCA Syllabus 2013SRINIVASA RAO GANTANessuna valutazione finora

- Comp Arch Syllabus 6-29-2017Documento4 pagineComp Arch Syllabus 6-29-2017Karthikeya MamillapalliNessuna valutazione finora

- Programing in C ComDocumento245 paginePrograming in C ComElite GroupNessuna valutazione finora

- SyllabusDocumento1 paginaSyllabusgdeepthiNessuna valutazione finora

- Computer ArchitectureDocumento2 pagineComputer ArchitectureMubasheerNessuna valutazione finora

- It4t5 PDFDocumento2 pagineIt4t5 PDFVyshnavi ThottempudiNessuna valutazione finora

- Complement and R's Complement), Fixed Point RepresentationDocumento7 pagineComplement and R's Complement), Fixed Point RepresentationBishal ShahiNessuna valutazione finora

- Cu 3rd SemDocumento7 pagineCu 3rd SemCOMPUTER SCIENCE BGCNessuna valutazione finora

- CADocumento4 pagineCAOneirosVasNessuna valutazione finora

- Priniciples of Embedded SystemsDocumento2 paginePriniciples of Embedded Systemsveeramaniks408Nessuna valutazione finora

- Ec 53Documento2 pagineEc 53Prince DevarajNessuna valutazione finora

- Microcontroller Architecture and Organization: Unit IDocumento6 pagineMicrocontroller Architecture and Organization: Unit IhemanthdreamzNessuna valutazione finora

- CAP208 (Artitchure)Documento2 pagineCAP208 (Artitchure)Sadik AmbaniNessuna valutazione finora

- Information Technology: Syllabus of Undergraduate Degree CourseDocumento32 pagineInformation Technology: Syllabus of Undergraduate Degree CoursehimanshutakNessuna valutazione finora

- HDocumento2 pagineH;(Nessuna valutazione finora

- 1st Sem MCADocumento6 pagine1st Sem MCArohietsharmaaNessuna valutazione finora

- Ec2303 Computer Architecture and OrganizationDocumento2 pagineEc2303 Computer Architecture and Organizationsujaganesan2009Nessuna valutazione finora

- Ec2303 Computer Architecture and OrganizationDocumento2 pagineEc2303 Computer Architecture and OrganizationVivek Sidharth CNessuna valutazione finora

- Computer Organization and Architecture (ECE2002)Documento20 pagineComputer Organization and Architecture (ECE2002)Madhav Rav TripathiNessuna valutazione finora

- D55d7course Handout CADocumento5 pagineD55d7course Handout CAanurag6866Nessuna valutazione finora

- Information Technology: Computer Organization and ArchitectureDocumento5 pagineInformation Technology: Computer Organization and ArchitectureAkash DasNessuna valutazione finora

- Bca Cs 232022Documento32 pagineBca Cs 232022ishagm795Nessuna valutazione finora

- Course Outline (MP)Documento2 pagineCourse Outline (MP)hamimNessuna valutazione finora

- EC208 AC Modelqn PDFDocumento2 pagineEC208 AC Modelqn PDFJustin SajuNessuna valutazione finora

- Ec 407 Computer CommunicationDocumento97 pagineEc 407 Computer CommunicationJustin SajuNessuna valutazione finora

- ND ElectivesDocumento4 pagineND ElectivesKrishnaraj VenugopalNessuna valutazione finora

- S6 EC SyllabusDocumento28 pagineS6 EC SyllabusJustin SajuNessuna valutazione finora

- Ec 467 Pattern RecognitionDocumento2 pagineEc 467 Pattern RecognitionJustin SajuNessuna valutazione finora

- S6 EC SyllabusDocumento28 pagineS6 EC SyllabusJustin SajuNessuna valutazione finora

- EC201 Netwok TheoryDocumento2 pagineEC201 Netwok TheoryBonifus Parambaloth LeenusNessuna valutazione finora

- MA201 Linear Algebra and Complex AnalysisDocumento3 pagineMA201 Linear Algebra and Complex AnalysisJustin SajuNessuna valutazione finora

- Acer Iconia Tab A100 - SchematicsDocumento35 pagineAcer Iconia Tab A100 - SchematicsEdgar Jose Aranguibel MorilloNessuna valutazione finora

- CPPC 10 Lecture Notes 2 Process ManagementDocumento16 pagineCPPC 10 Lecture Notes 2 Process ManagementBlessious Joseph LandoyNessuna valutazione finora

- Apache Traffic Server - More Than Just A ProxyDocumento50 pagineApache Traffic Server - More Than Just A ProxygamezzzzNessuna valutazione finora

- EMU10K1Documento9 pagineEMU10K1Uruk HaiNessuna valutazione finora

- MFDLink PDFDocumento12 pagineMFDLink PDFLautaro AyoroaNessuna valutazione finora

- Cost To Cost Pricelist March 2023Documento8 pagineCost To Cost Pricelist March 2023Nipun SaxenaNessuna valutazione finora

- J3ME and Bluetooth Enabled Mobile Based Full Duplex Automation System - Computer Science Project TopicsDocumento3 pagineJ3ME and Bluetooth Enabled Mobile Based Full Duplex Automation System - Computer Science Project TopicsSareeya ShreNessuna valutazione finora

- Operating Systems NotesDocumento6 pagineOperating Systems Notesishtiaq hussainNessuna valutazione finora

- Synopsis Online EducationDocumento23 pagineSynopsis Online Educationsunny60% (5)

- PRAM ModelsDocumento6 paginePRAM ModelsjazzNessuna valutazione finora

- Tr-4515 Best Practices For AFF Business-ProcessingDocumento39 pagineTr-4515 Best Practices For AFF Business-ProcessingJames ZhangNessuna valutazione finora

- Desktop Support Interview Questions and Answers 1261Documento17 pagineDesktop Support Interview Questions and Answers 1261munavar kNessuna valutazione finora

- Instruction Set Part 1Documento3 pagineInstruction Set Part 1Vivek Kumar100% (1)

- IntSec2 SmartCardsDocumento31 pagineIntSec2 SmartCardsGeorgeous MasterNessuna valutazione finora

- SM J200G Eplis 11Documento10 pagineSM J200G Eplis 11Abi Firnan WijayantoNessuna valutazione finora

- Overwatch 106172 Retailx64 enUS 28060 10-09-22 15.08.44 ErrorLogDocumento40 pagineOverwatch 106172 Retailx64 enUS 28060 10-09-22 15.08.44 ErrorLogBondriedNessuna valutazione finora

- Datalogic Powerscan 9500 MANUAL ENGDocumento348 pagineDatalogic Powerscan 9500 MANUAL ENGskomodopeoNessuna valutazione finora

- VPS - Cloud Comparision SheetDocumento4 pagineVPS - Cloud Comparision SheetJagdish EmmehattiNessuna valutazione finora

- SM331 Getting Started Teil3 eDocumento70 pagineSM331 Getting Started Teil3 eTrung MaiNessuna valutazione finora

- 04.huawei Atlas Data Center AI TrainingDocumento22 pagine04.huawei Atlas Data Center AI TrainingESG NOMANNessuna valutazione finora

- CH02 Solution-1 PDFDocumento10 pagineCH02 Solution-1 PDFAli AhmedNessuna valutazione finora

- Salahaddin University College of Engineering Geomatics DepartmentDocumento6 pagineSalahaddin University College of Engineering Geomatics DepartmentDaneal SofiNessuna valutazione finora

- Click and Play Intuitively, Make Your Media Alive: NSA221 NSA221Documento4 pagineClick and Play Intuitively, Make Your Media Alive: NSA221 NSA221FranzzNessuna valutazione finora

- TCA Sidestick X AE User ManualDocumento730 pagineTCA Sidestick X AE User ManualVicenç CNessuna valutazione finora

- Operations Manual GP429W - USB ARINC-429 Transmitter/Receiver and Data Recorder For WindowsDocumento121 pagineOperations Manual GP429W - USB ARINC-429 Transmitter/Receiver and Data Recorder For WindowswithmerohanNessuna valutazione finora

- William Stallings Computer Organization and Architecture 10 EditionDocumento43 pagineWilliam Stallings Computer Organization and Architecture 10 EditionSomya AgrawalNessuna valutazione finora

- Ata 45Documento10 pagineAta 45Guntur EkoNessuna valutazione finora

- Dell Laptop Sample ProposalDocumento4 pagineDell Laptop Sample ProposaltanNessuna valutazione finora

- Lesson 4Documento27 pagineLesson 4Niña Mae C. QuiambaoNessuna valutazione finora