Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Simulation of 16 Bit ALU Using Verilog-Hdl

Caricato da

Editor IJTSRDTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Simulation of 16 Bit ALU Using Verilog-Hdl

Caricato da

Editor IJTSRDCopyright:

Formati disponibili

International Journal of Trend in Scientific

Research and Development (IJTSRD)

International Open Access Journal

ISSN No: 2456 - 6470 | www.ijtsrd.com | Volume - 2 | Issue – 1

Simulation of 16 bit ALU using Verilog

Verilog-hdl

hdl

Mr. Mayank Mittal

Student, Department

epartment of Electronics and Telecommunication,

Bhilai Institute

nstitute of Technology Durg, Chhattisgarh

ABSTRACT

In many digital circuits ALU is a basic building block.

It can be used in integer arithmetic computations and

as Complex operation. This research paper is based on

the simulation of 16 bit ALU using VHDL. The

design was implemented using VHDL Xilinx

Synthesis tool ISE and targeted for Spartan device.

An ALU performs following operations – Addition,

subtraction, multiplication, Not, logical shift right,

logical shift left,

t, rotate right, rotate left, OR, AND,

XOR, NAND, NOR, XNOR and comparison between

two signals.

INTRODUCTION

An arithmetic logic unit (ALU) is a Table for different operation-

combinational digital electronic circuit that performs

arithmetic and bitwise operations. It represents the Option operation

fundamental building block of the central processing 0000 Addition

unit (CPU) of a computer. Modern CPUs contain very 0001 Subtraction

powerful and complex ALUs. An ALU performs 0010 Multiplication

basic arithmetic and logic operations. Examples of 0011 Not

arithmetic operations are addition, subtrac subtraction, 0100 Logical shift left

multiplication, and division. Examples of logic 0101 Logical shift right

operations are NOT, AND, and OR. All operations 0110 Rotate left

perform in a computer is in form of binary number i.e.

0 or 1. The logical operations are given below

below- 0111 Rotate right

1000 And

1001 Or

1010 Xor

1011 Nor

1100 Nand

1101 xnor

1110 Greater comparison

1111 Equal comparison

Table 2.1

@ IJTSRD | Available Online @ www.ijtsrd.com | Volume – 2 | Issue – 1 | Nov-Dec

Dec 2017 Page: 114

International Journal of Trend in Scientific Research and Development (IJTSRD) ISSN: 2456-6470

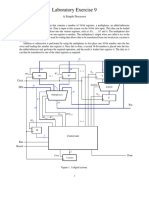

RTL schematic of ALU The time delay and memory usage is given in table

no. 3.2

Delay 12.339ns

Memory usage 235436 kilobyte

Table 3.2

CONCLUSION

Figure: 2.1

The simulation of 16 bit ALU is presented. This

design is implemented using Verilog hdl and Xilinx

ise and targeted for Spartan 3e family. The time delay

is 12.339ns and memory usage is 235436 kilobyte.

REFERENCE

1) Suchita Kamble, Prof .N. N. Mhala-VHDL

Implementation of 8-Bit ALU IOSR Journal of

Electronics and Communication Engineering

(IOSRJECE) ISSN : 2278-2834 Volume 1, Issue 1

(May-June 2012), PP 07-11

2) Shikha Khurana , Kanika Kaur-

Figure: 2.2 IMPLEMENTATION OF ALU USING FPGA

International Journal of Emerging Trends &

Result Technology in Computer Science (IJETTCS)

Volume 1, Issue 2, July – August 2012 ISSN

Verilog hdl implementation of ALU was done using 2278-6856

Xilinx ise. Detailed report is given below in table no.

3.1. 3) Prakash R Tonse, Siddalingesh S. Navalgund-

Design, Development and Implementation of

Logic utilization used Available utilization ALU, RAM and ROM for 8051 Microcontroller

on FPGA using VHDL International Journal of

Number of Slices 102 2448 4% Computer Applications (0975 – 8887) Volume 80

– No1, October 2013

Number of 4 input

192 4896 3%

LUTs

Number of bonded

68 108 62%

IOBs

Number of

1 12 8%

MULT18X18SIOs

Table: 3.1

@ IJTSRD | Available Online @ www.ijtsrd.com | Volume – 2 | Issue – 1 | Nov-Dec 2017 Page: 115

Potrebbero piacerti anche

- AluDocumento10 pagineAluAbhishek PatraNessuna valutazione finora

- ALU ReportDocumento11 pagineALU ReportAzad Kiyal100% (2)

- 0 - MPMC Lab Manual A.Y. 2020-21 R-18Documento53 pagine0 - MPMC Lab Manual A.Y. 2020-21 R-18Karthik BoggarapuNessuna valutazione finora

- A Complete 8-Bit Microcontroller in VHDLDocumento29 pagineA Complete 8-Bit Microcontroller in VHDLSidney O. EbotNessuna valutazione finora

- Hand Gesture-Controlled Robotic Arm With All-Terrain Surveillance CarDocumento7 pagineHand Gesture-Controlled Robotic Arm With All-Terrain Surveillance CarIJRASETPublicationsNessuna valutazione finora

- Accelerometer Based Hand Gesture Controlled Robot Using ArduinoDocumento10 pagineAccelerometer Based Hand Gesture Controlled Robot Using ArduinoRaj AryanNessuna valutazione finora

- Hand Gesture Controlled RobotDocumento65 pagineHand Gesture Controlled RobotFaheem RaoNessuna valutazione finora

- 8 Bit Alu Using Gdi TechniqueDocumento7 pagine8 Bit Alu Using Gdi TechniqueTADIBOINA PAVAN KUMARNessuna valutazione finora

- Starfast-A Wireless Wearable EEG Biometric System Based On The ENOBIO SensorDocumento8 pagineStarfast-A Wireless Wearable EEG Biometric System Based On The ENOBIO SensorMohammed Suleman Ashraf100% (2)

- Project Report - VHDL MUXDocumento4 pagineProject Report - VHDL MUXMsdmsd Msd100% (1)

- D Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALDocumento41 pagineD Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALArrnaav Singh RathoreeNessuna valutazione finora

- 8085 Microprocessor-BCA VIDocumento113 pagine8085 Microprocessor-BCA VIMarieFernandesNessuna valutazione finora

- Design of 16 Bit Alu: Prepared By: - Chandana - Mamatha - Praneeth ReddyDocumento22 pagineDesign of 16 Bit Alu: Prepared By: - Chandana - Mamatha - Praneeth ReddyChandanaNessuna valutazione finora

- Arduino Cheat Sheet: Basics 1: Using Digital I/O, Analog Reading, Serial As Output, Basic TimerDocumento3 pagineArduino Cheat Sheet: Basics 1: Using Digital I/O, Analog Reading, Serial As Output, Basic TimerSriHariKalyanBNessuna valutazione finora

- DELD Lab Manual 2020Documento120 pagineDELD Lab Manual 2020shinchan noharaNessuna valutazione finora

- Unit 1-EsiotDocumento46 pagineUnit 1-EsiotSonia BajajNessuna valutazione finora

- Project ReportDocumento27 pagineProject ReportMdjamal MohiuddinNessuna valutazione finora

- Programming Practices With SimulatorsDocumento11 pagineProgramming Practices With Simulatorsarun0% (2)

- Arm MC Lab ManualDocumento30 pagineArm MC Lab ManualVENKATA SUBBA REDDY NANDALURUNessuna valutazione finora

- 21-06-2021-1624264403-6-.-2. Engg - Voltage Based Control of Induction Motor Using Advanced Voice Recognition & Command SystemDocumento6 pagine21-06-2021-1624264403-6-.-2. Engg - Voltage Based Control of Induction Motor Using Advanced Voice Recognition & Command SystemImpact JournalsNessuna valutazione finora

- ALU 8 BIT Group NaminDocumento23 pagineALU 8 BIT Group NaminChrisEmilsonHernaezNessuna valutazione finora

- DLD Lab 1Documento5 pagineDLD Lab 1گيدوڙو ماڇيNessuna valutazione finora

- 8086 Lab FileDocumento15 pagine8086 Lab FileISHAAN TAKKARNessuna valutazione finora

- On DTHDocumento23 pagineOn DTHAkash Tyagi100% (2)

- 8085 Complete ArchitectureDocumento39 pagine8085 Complete ArchitectureSana KhanNessuna valutazione finora

- Ec - 501 - Microprocessor and Its ApplicationDocumento41 pagineEc - 501 - Microprocessor and Its ApplicationDr Nikita ShivhareNessuna valutazione finora

- NW Lab Manual R2017 - PrintDocumento70 pagineNW Lab Manual R2017 - PrintsaiNessuna valutazione finora

- Draw The Block Diagram of Simple Microprocessor-Based System and Explain The Function of Each Block (You Can Use MS Word or Google Docs)Documento8 pagineDraw The Block Diagram of Simple Microprocessor-Based System and Explain The Function of Each Block (You Can Use MS Word or Google Docs)Riza Pahama MananaongNessuna valutazione finora

- Design of Binary Multiplier Using Adders-3017 PDFDocumento5 pagineDesign of Binary Multiplier Using Adders-3017 PDFAdrian Walter JavierNessuna valutazione finora

- Microcontroller Lab Manual With Arduino Programe PDFDocumento63 pagineMicrocontroller Lab Manual With Arduino Programe PDFTejasaiNessuna valutazione finora

- Project Report VlsiDocumento33 pagineProject Report VlsiDhruv RastogiNessuna valutazione finora

- MPMC Lab ManualDocumento107 pagineMPMC Lab ManualReena RajNessuna valutazione finora

- IOT Lab Exp-4Documento9 pagineIOT Lab Exp-4Desta Yakob Doda 18BML0121Nessuna valutazione finora

- Lab9 VHDLDocumento8 pagineLab9 VHDLFasli CoolNessuna valutazione finora

- SP HW5Documento3 pagineSP HW5omar taradehNessuna valutazione finora

- Assignment1 PDFDocumento5 pagineAssignment1 PDFpristo sellerNessuna valutazione finora

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentDocumento43 pagineECE3003 M A 2018: Icrocontroller and Its Applications SsignmentAayoshi DuttaNessuna valutazione finora

- DCP ManualDocumento96 pagineDCP ManualSiva KumarNessuna valutazione finora

- Digital Electronics: Answer: D Explanation: The Expression For Associative Property Is Given by A+ (B+C) (A+B) +C &Documento51 pagineDigital Electronics: Answer: D Explanation: The Expression For Associative Property Is Given by A+ (B+C) (A+B) +C &Rajesh KumarNessuna valutazione finora

- 7442 BCD To DecimalDocumento1 pagina7442 BCD To DecimalHafis FauzanNessuna valutazione finora

- 8051 Microcontroller FAQDocumento160 pagine8051 Microcontroller FAQkranthi633Nessuna valutazione finora

- NI Tutorial 3115 enDocumento3 pagineNI Tutorial 3115 enajith.ganesh2420Nessuna valutazione finora

- IoT Lab REPORT CSEDocumento20 pagineIoT Lab REPORT CSECaptains PlayNessuna valutazione finora

- Design and Implementation of Pulse Code Modulation Using Matlab SimulinkDocumento4 pagineDesign and Implementation of Pulse Code Modulation Using Matlab SimulinkAprialdy StreetfootballNessuna valutazione finora

- Exclusive or Gate and It's ApplicationsDocumento6 pagineExclusive or Gate and It's ApplicationsRohit PatilNessuna valutazione finora

- IOT Based Air Quality MonitoringDocumento43 pagineIOT Based Air Quality MonitoringakashlogicNessuna valutazione finora

- Embedded Systems and Real-Time SystemsDocumento9 pagineEmbedded Systems and Real-Time SystemsMOUNI VARMANessuna valutazione finora

- AC58-AT58 Computer OrganizationDocumento26 pagineAC58-AT58 Computer OrganizationSaqib KamalNessuna valutazione finora

- Chapter 8 - PipeliningDocumento38 pagineChapter 8 - Pipeliningnagpal3Nessuna valutazione finora

- Jigjiga University Department of Electrical & Computer Engineering Stream Electronics and Communication Engineering Project Proposal ForDocumento9 pagineJigjiga University Department of Electrical & Computer Engineering Stream Electronics and Communication Engineering Project Proposal ForYaredNessuna valutazione finora

- DSP - Mod 6 PPT 1Documento37 pagineDSP - Mod 6 PPT 1oxygen oxygenNessuna valutazione finora

- Implementation of A Logic Circuit From 8x3 Encoder and A Multiplexer.Documento4 pagineImplementation of A Logic Circuit From 8x3 Encoder and A Multiplexer.Mohayminul Al-HamimNessuna valutazione finora

- Report On 4x1 MultiplexerDocumento17 pagineReport On 4x1 MultiplexerPRAVEEN KUMAWATNessuna valutazione finora

- Verify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)Documento8 pagineVerify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)sonalibhagwatkar100% (1)

- Microcontrollers and Embedded SystemsDocumento35 pagineMicrocontrollers and Embedded SystemsTarek BarhoumNessuna valutazione finora

- DSDV MODULE 3 Implementation FabricsDocumento17 pagineDSDV MODULE 3 Implementation Fabricssalman shariffNessuna valutazione finora

- Ee8551 8085 NotesDocumento31 pagineEe8551 8085 NotesKUMARANSCRNessuna valutazione finora

- Interfacing Relay With 8051Documento6 pagineInterfacing Relay With 8051Pantech ProLabs India Pvt Ltd100% (2)

- Design of 32 Bit Alu Ijert PaperDocumento5 pagineDesign of 32 Bit Alu Ijert Papergollapudi vamsikrishnaNessuna valutazione finora

- Design Simulation and Hardware Construction of An Arduino Microcontroller Based DC DC High Side Buck Converter For Standalone PV SystemDocumento6 pagineDesign Simulation and Hardware Construction of An Arduino Microcontroller Based DC DC High Side Buck Converter For Standalone PV SystemEditor IJTSRDNessuna valutazione finora

- Differential Equations Third Order Inhomogeneous Linear With Boundary ConditionsDocumento6 pagineDifferential Equations Third Order Inhomogeneous Linear With Boundary ConditionsEditor IJTSRDNessuna valutazione finora

- Activating Geospatial Information For Sudans Sustainable Investment MapDocumento13 pagineActivating Geospatial Information For Sudans Sustainable Investment MapEditor IJTSRDNessuna valutazione finora

- Educational Unity Embracing Diversity For A Stronger SocietyDocumento6 pagineEducational Unity Embracing Diversity For A Stronger SocietyEditor IJTSRDNessuna valutazione finora

- Sustainable EnergyDocumento8 pagineSustainable EnergyEditor IJTSRDNessuna valutazione finora

- Women Before and After Islam With Special Reference To ArabDocumento3 pagineWomen Before and After Islam With Special Reference To ArabEditor IJTSRDNessuna valutazione finora

- Challenges Faced by The Media in An Attempt To Play Their Roles in Public Awareness On Waste Management in Buea and DoualaDocumento18 pagineChallenges Faced by The Media in An Attempt To Play Their Roles in Public Awareness On Waste Management in Buea and DoualaEditor IJTSRDNessuna valutazione finora

- Deconstructing The Hijra Narrative Reimagining Trans Identities Through Literary PerspectivesDocumento6 pagineDeconstructing The Hijra Narrative Reimagining Trans Identities Through Literary PerspectivesEditor IJTSRDNessuna valutazione finora

- International Journal of Trend in Scientific Research and Development (IJTSRD)Documento13 pagineInternational Journal of Trend in Scientific Research and Development (IJTSRD)Editor IJTSRDNessuna valutazione finora

- Collective Bargaining and Employee Prosocial Behaviour in The Hospitality Sector in Port HarcourtDocumento10 pagineCollective Bargaining and Employee Prosocial Behaviour in The Hospitality Sector in Port HarcourtEditor IJTSRDNessuna valutazione finora

- Evan Syndrome A Case ReportDocumento3 pagineEvan Syndrome A Case ReportEditor IJTSRDNessuna valutazione finora

- An Investigation of The Temperature Effect On Solar Panel Efficiency Based On IoT TechnologyDocumento7 pagineAn Investigation of The Temperature Effect On Solar Panel Efficiency Based On IoT TechnologyEditor IJTSRDNessuna valutazione finora

- An Analysis On The Use of Image Design With Generative AI TechnologiesDocumento4 pagineAn Analysis On The Use of Image Design With Generative AI TechnologiesEditor IJTSRDNessuna valutazione finora

- Artificial Intelligence A Boon in Expanding Online Education Through Social Media and Digital Marketing Post Covid 19Documento9 pagineArtificial Intelligence A Boon in Expanding Online Education Through Social Media and Digital Marketing Post Covid 19Editor IJTSRDNessuna valutazione finora

- To Assess The Knowledge and Attitude of Non Professionals Regarding COVID 19 Vaccination A Descriptive StudyDocumento4 pagineTo Assess The Knowledge and Attitude of Non Professionals Regarding COVID 19 Vaccination A Descriptive StudyEditor IJTSRDNessuna valutazione finora

- Sustainable Development A PrimerDocumento9 pagineSustainable Development A PrimerEditor IJTSRDNessuna valutazione finora

- Consumers' Impulsive Buying Behavior in Social Commerce PlatformsDocumento5 pagineConsumers' Impulsive Buying Behavior in Social Commerce PlatformsEditor IJTSRDNessuna valutazione finora

- A Pharmaceutical Review On Kaanji and Its Wide Range of ApplicabilityDocumento6 pagineA Pharmaceutical Review On Kaanji and Its Wide Range of ApplicabilityEditor IJTSRDNessuna valutazione finora

- A Study To Assess The Effectiveness of Art Therapy To Reduce Depression Among Old Age Clients Admitted in Saveetha Medical College and Hospital, Thandalam, ChennaiDocumento5 pagineA Study To Assess The Effectiveness of Art Therapy To Reduce Depression Among Old Age Clients Admitted in Saveetha Medical College and Hospital, Thandalam, ChennaiEditor IJTSRDNessuna valutazione finora

- Role of Dashamooladi Niruha Basti Followed by Katibasti in The Management of "Katigraha" W.R.S To Lumbar Spondylosis A Case StudyDocumento3 pagineRole of Dashamooladi Niruha Basti Followed by Katibasti in The Management of "Katigraha" W.R.S To Lumbar Spondylosis A Case StudyEditor IJTSRDNessuna valutazione finora

- Effectiveness of Video Teaching Program On Knowledge Regarding 5Fs of Disease Transmission Food, Finger, Fluid, Fomite, Faces Among Children at Selected Setting, ChennaiDocumento3 pagineEffectiveness of Video Teaching Program On Knowledge Regarding 5Fs of Disease Transmission Food, Finger, Fluid, Fomite, Faces Among Children at Selected Setting, ChennaiEditor IJTSRDNessuna valutazione finora

- H1 L1 Boundedness of Rough Toroidal Pseudo Differential OperatorDocumento8 pagineH1 L1 Boundedness of Rough Toroidal Pseudo Differential OperatorEditor IJTSRDNessuna valutazione finora

- Concept of Shotha W.S.R To Arishta LakshanaDocumento3 pagineConcept of Shotha W.S.R To Arishta LakshanaEditor IJTSRDNessuna valutazione finora

- Knowledge Related To Diabetes Mellitus and Self Care Practice Related To Diabetic Foot Care Among Diabetic PatientsDocumento4 pagineKnowledge Related To Diabetes Mellitus and Self Care Practice Related To Diabetic Foot Care Among Diabetic PatientsEditor IJTSRDNessuna valutazione finora

- Importance of Controlled CreditDocumento3 pagineImportance of Controlled CreditEditor IJTSRDNessuna valutazione finora

- Financial Risk, Capital Adequacy and Liquidity Performance of Deposit Money Banks in NigeriaDocumento12 pagineFinancial Risk, Capital Adequacy and Liquidity Performance of Deposit Money Banks in NigeriaEditor IJTSRDNessuna valutazione finora

- A Study To Assess The Knowledge Regarding Iron Deficiency Anemia Among Reproductive Age Women in Selected Community ThrissurDocumento4 pagineA Study To Assess The Knowledge Regarding Iron Deficiency Anemia Among Reproductive Age Women in Selected Community ThrissurEditor IJTSRDNessuna valutazione finora

- Challenges in Pineapple Cultivation A Case Study of Pineapple Orchards in TripuraDocumento4 pagineChallenges in Pineapple Cultivation A Case Study of Pineapple Orchards in TripuraEditor IJTSRDNessuna valutazione finora

- An Approach To The Diagnostic Study On Annavaha Srotodusti in Urdwaga Amlapitta WSR To Oesophagogastroduodenoscopic ChangesDocumento4 pagineAn Approach To The Diagnostic Study On Annavaha Srotodusti in Urdwaga Amlapitta WSR To Oesophagogastroduodenoscopic ChangesEditor IJTSRDNessuna valutazione finora

- A Study On Human Resource AccountingDocumento3 pagineA Study On Human Resource AccountingEditor IJTSRDNessuna valutazione finora

- How Can You Store Data Forever?: Larye Parkins, Building, Troubleshooting, and Repairing Computers Since 65Documento17 pagineHow Can You Store Data Forever?: Larye Parkins, Building, Troubleshooting, and Repairing Computers Since 65Sachin AnandNessuna valutazione finora

- La-C611p R10 PDFDocumento60 pagineLa-C611p R10 PDFMelky LiwutNessuna valutazione finora

- Ultra FXDocumento17 pagineUltra FXmanikumar0Nessuna valutazione finora

- Wiring DiagramDocumento4 pagineWiring Diagramivo rodriguesNessuna valutazione finora

- Tutorial 2 - 3Documento2 pagineTutorial 2 - 3Ahan TejaswiNessuna valutazione finora

- Easynote lj65Documento220 pagineEasynote lj65n0c0deNessuna valutazione finora

- Acer LaptopDocumento13 pagineAcer LaptoprickNessuna valutazione finora

- Quotation of 25sqm P4 Indoor Fixed LED Display-20201106Documento3 pagineQuotation of 25sqm P4 Indoor Fixed LED Display-20201106wilmer juarezNessuna valutazione finora

- 714U0301 Rev 22 Blastware Instalacion ManualDocumento9 pagine714U0301 Rev 22 Blastware Instalacion ManualjohanNessuna valutazione finora

- Vdx-6358D / Vdx-6358D-512: DM&P Vortex86Dx 800Mhz Pc/104 Cpu ModuleDocumento41 pagineVdx-6358D / Vdx-6358D-512: DM&P Vortex86Dx 800Mhz Pc/104 Cpu ModuleVertaNessuna valutazione finora

- MELSEC-A&QnA Series Transition Guide - L08077ehDocumento36 pagineMELSEC-A&QnA Series Transition Guide - L08077ehAym BrNessuna valutazione finora

- Huawei g630 Repair Manual PDFDocumento65 pagineHuawei g630 Repair Manual PDFUmar MajeedNessuna valutazione finora

- Impulse 6000D/7000DP: Sending Test Data To A PC: Application NoteDocumento2 pagineImpulse 6000D/7000DP: Sending Test Data To A PC: Application NoteMarielena ZabalaNessuna valutazione finora

- GD TroubleshootingGuide ENGLISHDocumento62 pagineGD TroubleshootingGuide ENGLISHEst Ast-MonestNessuna valutazione finora

- Ax3000-Autocad Setup EngDocumento18 pagineAx3000-Autocad Setup EngDamir DrkNessuna valutazione finora

- Thass CSA CS3 CASE STUDY 3 - QuestionDocumento4 pagineThass CSA CS3 CASE STUDY 3 - QuestionThasswhin ManimaranNessuna valutazione finora

- Zebra GC420tDocumento2 pagineZebra GC420treginaldo2005100% (1)

- MPMC Lab - Expt1 Introduction To TasmDocumento7 pagineMPMC Lab - Expt1 Introduction To Tasmsanti santillano100% (1)

- TSM Oce TDS320 - SDSDocumento204 pagineTSM Oce TDS320 - SDSCesar CamachoNessuna valutazione finora

- Cs101 Introduction To Computing: Most Repeated Mcqs MidtermDocumento40 pagineCs101 Introduction To Computing: Most Repeated Mcqs MidtermSocial ShoutNessuna valutazione finora

- Honeywell - Icon ConsolesDocumento4 pagineHoneywell - Icon ConsolesBouazzaNessuna valutazione finora

- GEZE 3D Modeli 1156651Documento2.465 pagineGEZE 3D Modeli 1156651Cansu GumusNessuna valutazione finora

- Cache OptimizationsDocumento23 pagineCache Optimizationstouqir fatimaNessuna valutazione finora

- 6 BCP-DCPDocumento19 pagine6 BCP-DCPWriter CourseNessuna valutazione finora

- Lab 5 Submission - Programming PIC18 CountersDocumento7 pagineLab 5 Submission - Programming PIC18 CountersShreyash Ankam100% (1)

- CAI DescriptionDocumento2 pagineCAI DescriptionJoan BandojoNessuna valutazione finora

- Jesd209 3CDocumento158 pagineJesd209 3Csanjeevsoni64Nessuna valutazione finora

- Verilog - FPGA QP - 3Documento4 pagineVerilog - FPGA QP - 3Mohsin Khan ANessuna valutazione finora

- Lenovo Thinkplus Livepods lp7 en 95506 Locked NavodDocumento4 pagineLenovo Thinkplus Livepods lp7 en 95506 Locked Navodrociw55202Nessuna valutazione finora

- A Project Report On AppleDocumento32 pagineA Project Report On ApplePawanJariwalaNessuna valutazione finora