Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Mini-360 Ic PDF

Caricato da

hemanthwashereTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Mini-360 Ic PDF

Caricato da

hemanthwashereCopyright:

Formati disponibili

MP2307

3A, 23V, 340KHz Synchronous Rectified

Step-Down Converter

The Future of Analog IC Technology

DESCRIPTION FEATURES

The MP2307 is a monolithic synchronous buck • 3A Continuous Output Current

regulator. The device integrates 100mΩ 4A Peak Output Current

MOSFETS that provide 3A of continuous load • Wide 4.75V to 23V Operating Input Range

current over a wide operating input voltage of • Integrated 100mΩ Power MOSFET Switches

4.75V to 23V. Current mode control provides • Output Adjustable from 0.925V to 20V

fast transient response and cycle-by-cycle • Up to 95% Efficiency

current limit. • Programmable Soft-Start

An adjustable soft-start prevents inrush current • Stable with Low ESR Ceramic Output Capacitors

at turn-on and in shutdown mode, the supply • Fixed 340KHz Frequency

current drops below 1µA. • Cycle-by-Cycle Over Current Protection

This device, available in an 8-pin SOIC • Input Under Voltage Lockout

package, provides a very compact system • Thermally Enhanced 8-Pin SOIC Package

solution with minimal reliance on external APPLICATIONS

components.

• Distributed Power Systems

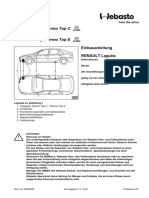

EVALUATION BOARD REFERENCE • Networking Systems

Board Number Dimensions • FPGA, DSP, ASIC Power Supplies

EV2307DN-00A 2.0”X x 1.5”Y x 0.5”Z • Green Electronics/Appliances

• Notebook Computers

“MPS” and “The Future of Analog IC Technology” are Registered Trademarks of

Monolithic Power Systems, Inc.

TYPICAL APPLICATION

C5

10nF Efficiency vs

INPUT Load Current

4.75V to 23V

100

VIN = 5V

95

VIN = 12V

2 1 90

OUTPUT

EFFICIENCY (%)

IN BS 85

7 3

EN SW 3.3V

3A 80 VIN = 23V

MP2307

8

SS FB

5 75

GND COMP 70

4 6 65

C3 60

3.9nF

55

50

0.1 1.0 10

LOAD CURRENT (A)

MP2307_EC01

MP2307_TAC01

MP2307 Rev. 1.9 www.MonolithicPower.com 1

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

PACKAGE REFERENCE ABSOLUTE MAXIMUM RATINGS (1)

Supply Voltage VIN ....................... –0.3V to +26V

Switch Voltage VSW ................. –1V to VIN + 0.3V

TOP VIEW Boost Voltage VBS ..........VSW – 0.3V to VSW + 6V

All Other Pins................................. –0.3V to +6V

BS 1 8 SS Junction Temperature...............................150°C

IN 2 7 EN

Lead Temperature ....................................260°C

Storage Temperature .............–65°C to +150°C

SW 3 6 COMP

(2)

GND 4 5 FB Recommended Operating Conditions

Input Voltage VIN ............................ 4.75V to 23V

EXPOSED PAD MP2307_PD01_SOIC8N

Output Voltage VOUT .................... 0.925V to 20V

ON BACKSIDE

Ambient Operating Temp .............. –40°C to +85°C

(3)

Thermal Resistance θJA θJC

SOIC8N .................................. 50 ...... 10... °C/W

Part Number* Package Temperature

SOIC8N Maximum Power Dissipation Operating

MP2307DN

(Exposed Pad)

–40° to +85°C (TA=25°C)

(4)

* For Tape & Reel, add suffix –Z (eg. MP2307DN–Z) SOIC8N , POUT ....................... .......... ........ 2W

For Lead Free, add suffix –LF (eg. MP2307DN–LF–Z)

Notes:

1) Exceeding these ratings may damage the device.

2) The device is not guaranteed to function outside of its operating conditions.

3) Measured on approximately 1” square of 1 oz copper.

4) Derating 20mW/°C at TA > 25°C

ELECTRICAL CHARACTERISTICS

VIN = 12V, TA = +25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

Shutdown Supply Current VEN = 0V 0.3 3.0 µA

Supply Current VEN = 2.0V, VFB = 1.0V 1.3 1.5 mA

Feedback Voltage VFB 4.75V ≤ VIN ≤ 23V 0.900 0.925 0.950 V

Feedback Overvoltage Threshold 1.1 V

Error Amplifier Voltage Gain (5) AEA 400 V/V

Error Amplifier Transconductance GEA ∆IC = ±10µA 820 µA/V

(5)

High-Side Switch On-Resistance RDS(ON)1 100 mΩ

Low-Side Switch On-Resistance (5) RDS(ON)2 100 mΩ

High-Side Switch Leakage Current VEN = 0V, VSW = 0V 0 10 µA

Upper Switch Current Limit Minimum Duty Cycle 4.0 5.8 A

Lower Switch Current Limit From Drain to Source 0.9 A

COMP to Current Sense

GCS 5.2 A/V

Transconductance

Oscillation Frequency Fosc1 300 340 380 KHz

Short Circuit Oscillation Frequency Fosc2 VFB = 0V 110 KHz

Maximum Duty Cycle DMAX VFB = 1.0V 90 %

Minimum On Time (5) TON 220 ns

EN Shutdown Threshold Voltage VEN Rising 1.1 1.5 2.0 V

EN Shutdown Threshold Voltage

220 mV

Hysterisis

MP2307 Rev. 1.9 www.MonolithicPower.com 2

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

ELECTRICAL CHARACTERISTICS (continued)

VIN = 12V, TA = +25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

EN Lockout Threshold Voltage 2.2 2.5 2.7 V

EN Lockout Hysterisis 210 mV

Input Under Voltage Lockout

VIN Rising 3.80 4.05 4.40 V

Threshold

Input Under Voltage Lockout

210 mV

Threshold Hysteresis

Soft-Start Current VSS = 0V 6 µA

Soft-Start Period CSS = 0.1µF 15 ms

Thermal Shutdown (5) 160 °C

Note:

5) Guaranteed by design, not tested.

MP2307 Rev. 1.9 www.MonolithicPower.com 3

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

C1 = 2 x 10µF, C2 = 2 x 22µF, L= 10µH, CSS= 0.1µF, TA = +25°C, unless otherwise noted.

Steady State Test Steady State Test Startup through

Waveforms Waveforms Enable Waveforms

VIN = 12V, VOUT = 3.3V, IOUT = 0A VIN = 12V, VOUT = 3.3V, IOUT = 3A VIN = 12V, VOUT = 3.3V, No Load

VIN VIN VEN

20mV/div. 200mV/div. 5V/div.

VOUT VOUT

20mV/div. 20MV/div. VOUT

2V/div.

VSW VSW

10V/div. V/div.

IL IL

1A/div. IL 1A/div.

2A/div.

VSW

10V/div.

2ms/div.

MP2307-TPC01 MP2307-TPC02 MP2307-TPC03

Startup Through Shutdown Through Shutdown Through

Enable Waveforms Enable Waveforms Enable Waveforms

VIN = 12V, VOUT = 3.3V, VIN = 12V, VOUT = 3.3V,

IOUT = 3A (Resistance Load) VIN = 12V, VOUT = 3.3V, No Load IOUT = 3A (Resistance Load)

VEN

VEN VEN 5V/div.

5V/div. 5V/div.

VOUT

2V/div.

VOUT VOUT

2V/div. 2V/div.

IL IL

1A/div. 2A/div.

IL

2A/div.

VSW VSW

10V/div. 10V/div.

VSW

10V/div.

2ms/div. 2ms/div.

MP2307-TP04 MP2307-TPC05 MP2307-TPC06

Load Transient Test Short Circuit Test Short Circuit Recovery

Waveforms Waveforms Waveforms

VIN = 12V, VOUT = 3.3V,

IOUT = 1A to 2A step VIN = 12V, VOUT = 3.3V VIN = 12V, VOUT = 3.3V

VOUT

200mV/div. VOUT

VOUT 2V/div.

2V/div.

IL

1A/div.

ILOAD IL

1A/div. 2A/div. IL

2A/div.

MP2307 -TPC07 MP2307-TPC08 MP2307-TPC09

MP2307 Rev. 1.9 www.MonolithicPower.com 4

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

PIN FUNCTIONS

Pin # Name Description

High-Side Gate Drive Boost Input. BS supplies the drive for the high-side N-Channel MOSFET

1 BS

switch. Connect a 0.01µF or greater capacitor from SW to BS to power the high side switch.

Power Input. IN supplies the power to the IC, as well as the step-down converter switches.

2 IN Drive IN with a 4.75V to 23V power source. Bypass IN to GND with a suitably large capacitor

to eliminate noise on the input to the IC. See Input Capacitor.

Power Switching Output. SW is the switching node that supplies power to the output. Connect

3 SW the output LC filter from SW to the output load. Note that a capacitor is required from SW to

BS to power the high-side switch.

4 GND Ground (Connect the exposed pad to Pin 4).

Feedback Input. FB senses the output voltage and regulates it. Drive FB with a resistive

5 FB voltage divider connected to it from the output voltage. The feedback threshold is 0.925V. See

Setting the Output Voltage.

Compensation Node. COMP is used to compensate the regulation control loop. Connect a

6 COMP series RC network from COMP to GND. In some cases, an additional capacitor from COMP to

GND is required. See Compensation Components.

Enable Input. EN is a digital input that turns the regulator on or off. Drive EN high to turn on

7 EN

the regulator; low to turn it off. Attach to IN with a 100kΩ pull up resistor for automatic startup.

Soft-Start Control Input. SS controls the soft-start period. Connect a capacitor from SS to GND

8 SS to set the soft-start period. A 0.1µF capacitor sets the soft-start period to 15ms. To disable the

soft-start feature, leave SS unconnected.

MP2307 Rev. 1.9 www.MonolithicPower.com 5

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

OPERATION

FUNCTIONAL DESCRIPTION The converter uses internal N-Channel

The MP2307 regulates input voltages from MOSFET switches to step-down the input

4.75V to 23V down to an output voltage as low voltage to the regulated output voltage. Since

as 0.925V, and supplies up to 3A of load the high side MOSFET requires a gate voltage

current. greater than the input voltage, a boost capacitor

connected between SW and BS is needed to

The MP2307 uses current-mode control to drive the high side gate. The boost capacitor is

regulate the output voltage. The output voltage charged from the internal 5V rail when SW is low.

is measured at FB through a resistive voltage

divider and amplified through the internal When the FB pin voltage exceeds 20% of the

transconductance error amplifier. The voltage at nominal regulation value of 0.925V, the over

the COMP pin is compared to the switch current voltage comparator is tripped and the COMP

(measured internally) to control the output pin and the SS pin are discharged to GND,

voltage. forcing the high-side switch off.

+

CURRENT 2 IN

OVP SENSE

-- AMPLIFIER +

1.1V

RAMP 5V

OSCILLATOR

FB 5 + --

CLK

110/340KHz 1 BS

0.3V --

-- S Q

-- R Q 3 SW

SS 8 + + CURRENT

ERROR COMPARATOR

0.925V + AMPLIFIER

COMP 6

-- 4 GND

EN 7

EN OK 1.2V OVP

IN < 4.10V

LOCKOUT

2.5V + COMPARATOR

IN

7V +

Zener INTERNAL

REGULATORS

1.5V -- SHUTDOWN

COMPARATOR MP2307_BD01

Figure 1—Functional Block Diagram

MP2307 Rev. 1.9 www.MonolithicPower.com 6

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

APPLICATIONS INFORMATION

COMPONENT SELECTION The inductance value can be calculated by:

Setting the Output Voltage VOUT ⎛ V ⎞

The output voltage is set using a resistive L= × ⎜⎜1 − OUT ⎟⎟

f S × ∆I L ⎝ VIN ⎠

voltage divider connected from the output

voltage to FB. The voltage divider divides the Where VOUT is the output voltage, VIN is the

output voltage down to the feedback voltage by input voltage, fS is the switching frequency, and

the ratio: ∆IL is the peak-to-peak inductor ripple current.

R2 Choose an inductor that will not saturate under

VFB = VOUT

R1 + R2 the maximum inductor peak current, calculated

Thus the output voltage is: by:

R1 + R2 VOUT ⎛ V ⎞

VOUT = 0.925 × ILP = ILOAD + × ⎜1 − OUT ⎟⎟

R2 2 × f S × L ⎜⎝ VIN ⎠

R2 can be as high as 100kΩ, but a typical value Where ILOAD is the load current.

is 10kΩ. Using the typical value for R2, R1 is

determined by: The choice of which style inductor to use mainly

depends on the price vs. size requirements and

R1 = 10.81 × ( VOUT − 0.925 ) (kΩ) any EMI constraints.

For example, for a 3.3V output voltage, R2 is Optional Schottky Diode

10kΩ, and R1 is 26.1kΩ. Table 1 lists During the transition between the high-side

recommended resistance values of R1 and R2 switch and low-side switch, the body diode of

for standard output voltages. the low-side power MOSFET conducts the

inductor current. The forward voltage of this

Table 1—Recommended Resistance Values

body diode is high. An optional Schottky diode

VOUT R1 R2 may be paralleled between the SW pin and

1.8V 9.53kΩ 10kΩ GND pin to improve overall efficiency. Table 2

lists example Schottky diodes and their

2.5V 16.9kΩ 10kΩ

Manufacturers.

3.3V 26.1kΩ 10kΩ

5V 44.2kΩ 10kΩ

Table 2—Diode Selection Guide

12V 121kΩ 10kΩ Voltage/Current

Part Number Vendor

Rating

Inductor

B130 30V, 1A Diodes, Inc.

The inductor is required to supply constant

current to the load while being driven by the SK13 30V, 1A Diodes, Inc.

switched input voltage. A larger value inductor International

MBRS130 30V, 1A

will result in less ripple current that will in turn Rectifier

result in lower output ripple voltage. However, Input Capacitor

the larger value inductor will have a larger The input current to the step-down converter is

physical size, higher series resistance, and/or discontinuous, therefore a capacitor is required

lower saturation current. A good rule for to supply the AC current while maintaining the

determining inductance is to allow the peak-to- DC input voltage. Use low ESR capacitors for

peak ripple current to be approximately 30% of the best performance. Ceramic capacitors are

the maximum switch current limit. Also, make preferred, but tantalum or low-ESR electrolytic

sure that the peak inductor current is below the capacitors will also suffice. Choose X5R or

maximum switch current limit. X7R dielectrics when using ceramic capacitors.

MP2307 Rev. 1.9 www.MonolithicPower.com 7

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

Since the input capacitor (C1) absorbs the input When using tantalum or electrolytic capacitors,

switching current, it requires an adequate ripple the ESR dominates the impedance at the

current rating. The RMS current in the input switching frequency. For simplification, the

capacitor can be estimated by: output ripple can be approximated to:

VOUT ⎛⎜ VOUT ⎞⎟ VOUT ⎛ V ⎞

I C1 = ILOAD × × 1− ∆VOUT = × ⎜1 − OUT ⎟⎟ × R ESR

VIN ⎜⎝ VIN ⎟⎠ f S × L ⎜⎝ VIN ⎠

The worst-case condition occurs at VIN = 2VOUT, The characteristics of the output capacitor also

where IC1 = ILOAD/2. For simplification, use an affect the stability of the regulation system. The

input capacitor with a RMS current rating MP2307 can be optimized for a wide range of

greater than half of the maximum load current. capacitance and ESR values.

The input capacitor can be electrolytic, tantalum Compensation Components

or ceramic. When using electrolytic or tantalum MP2307 employs current mode control for easy

capacitors, a small, high quality ceramic compensation and fast transient response. The

capacitor, i.e. 0.1µF, should be placed as close system stability and transient response are

to the IC as possible. When using ceramic controlled through the COMP pin. COMP is the

capacitors, make sure that they have enough output of the internal transconductance error

capacitance to provide sufficient charge to amplifier. A series capacitor-resistor

prevent excessive voltage ripple at input. The combination sets a pole-zero combination to

input voltage ripple for low ESR capacitors can govern the characteristics of the control system.

be estimated by: The DC gain of the voltage feedback loop is

ILOAD V ⎛ V ⎞ given by:

∆VIN = × OUT × ⎜⎜1 − OUT ⎟⎟

C1 × fS VIN ⎝ VIN ⎠ VFB

A VDC = R LOAD × G CS × A EA ×

VOUT

Where C1 is the input capacitance value.

Output Capacitor Where VFB is the feedback voltage (0.925V),

The output capacitor (C2) is required to AVEA is the error amplifier voltage gain, GCS is

maintain the DC output voltage. Ceramic, the current sense transconductance and RLOAD

tantalum, or low ESR electrolytic capacitors are is the load resistor value.

recommended. Low ESR capacitors are The system has two poles of importance. One

preferred to keep the output voltage ripple low. is due to the compensation capacitor (C3) and

The output voltage ripple can be estimated by: the output resistor of the error amplifier, and the

⎞ ⎛ ⎞

other is due to the output capacitor and the load

VOUT ⎛ V 1

∆VOUT = × ⎜⎜1 − OUT ⎟⎟ × ⎜ R ESR + ⎟ resistor. These poles are located at:

fS × L ⎝ VIN ⎜ 8 × f S × C2 ⎟⎠

⎠ ⎝

GEA

Where C2 is the output capacitance value and fP1 =

2π × C3 × A VEA

RESR is the equivalent series resistance (ESR)

value of the output capacitor. 1

fP2 =

When using ceramic capacitors, the impedance 2π × C2 × R LOAD

at the switching frequency is dominated by the Where GEA is the error amplifier transconductance.

capacitance which is the main cause for the

output voltage ripple. For simplification, the

output voltage ripple can be estimated by:

VOUT ⎛ V ⎞

∆VOUT = 2

× ⎜⎜1 − OUT ⎟⎟

8 × fS × L × C2 ⎝ VIN ⎠

MP2307 Rev. 1.9 www.MonolithicPower.com 8

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

The system has one zero of importance, due to the 2. Choose the compensation capacitor (C3) to

compensation capacitor (C3) and the compensation achieve the desired phase margin. For

resistor (R3). This zero is located at: applications with typical inductor values, setting

the compensation zero (fZ1) below one-forth of

1 the crossover frequency provides sufficient

f Z1 =

2π × C3 × R3 phase margin.

The system may have another zero of Determine C3 by the following equation:

importance, if the output capacitor has a large

4

capacitance and/or a high ESR value. The zero, C3 >

due to the ESR and capacitance of the output 2π × R3 × f C

capacitor, is located at: Where R3 is the compensation resistor.

1 3. Determine if the second compensation

fESR =

2π × C2 × R ESR capacitor (C6) is required. It is required if the

ESR zero of the output capacitor is located at

In this case, a third pole set by the

less than half of the switching frequency, or the

compensation capacitor (C6) and the

following relationship is valid:

compensation resistor (R3) is used to

compensate the effect of the ESR zero on the 1 f

< S

loop gain. This pole is located at: 2π × C2 × R ESR 2

1 If this is the case, then add the second

fP 3 =

2π × C6 × R3 compensation capacitor (C6) to set the pole fP3

The goal of compensation design is to shape at the location of the ESR zero. Determine C6

the converter transfer function to get a desired by the equation:

loop gain. The system crossover frequency C2 × R ESR

where the feedback loop has the unity gain is C6 =

R3

important. Lower crossover frequencies result

in slower line and load transient responses, PCB Layout Guide

while higher crossover frequencies could cause PCB layout is very important to achieve stable

system instability. A good standard is to set the operation. It is highly recommended to duplicate

crossover frequency below one-tenth of the EVB layout for optimum performance.

switching frequency.

If change is necessary, please follow these

To optimize the compensation components, the guidelines and take Figure2 for reference.

following procedure can be used.

1) Keep the path of switching current short

1. Choose the compensation resistor (R3) to set and minimize the loop area formed by Input

the desired crossover frequency. cap., high-side MOSFET and low-side

Determine R3 by the following equation: MOSFET.

2π × C2 × fC VOUT 2π × C2 × 0.1 × fS VOUT 2) Bypass ceramic capacitors are suggested

R3 = × < × to be put close to the Vin Pin.

GEA × GCS VFB GEA × GCS VFB

Where fC is the desired crossover frequency 3) Ensure all feedback connections are short

which is typically below one tenth of the and direct. Place the feedback resistors

switching frequency. and compensation components as close to

the chip as possible.

4) ROUT SW away from sensitive analog areas

such as FB.

MP2307 Rev. 1.9 www.MonolithicPower.com 9

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

5) Connect IN, SW, and especially GND External Bootstrap Diode

respectively to a large copper area to cool An external bootstrap diode may enhance the

the chip to improve thermal performance efficiency of the regulator, the applicable

and long-term reliability. conditions of external BS diode are:

z VOUT is 5V or 3.3V; and

VOUT

z Duty cycle is high: D= >65%

VIN

In these cases, an external BS diode is

recommended from the output of the voltage

regulator to BS pin, as shown in Figure3

External BST Diode

IN4148

BS

CBST

MP2307

SW 5V or 3.3V

L

COUT

Figure 3—Add Optional External Bootstrap

Diode to Enhance Efficiency

The recommended external BS diode is IN4148,

and the BS cap is 0.1~1µF.

TOP Layer

Bottom Layer

Figure 2―PCB Layout (Double Layer)

MP2307 Rev. 1.9 www.MonolithicPower.com 10

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

TYPICAL APPLICATION CIRCUIT

C5

10nF

INPUT

4.75V to 23V

2 1

7

IN BS

3

OUTPUT

EN SW 3.3V

MP2307 3A

8 5

SS FB

GND COMP

4 6

D1

C3 B130

C6 3.9nF (optional)

(optional)

MP2307_F03

Figure 4—MP2307 with 3.3V Output, 22uF/6.3V Ceramic Output Capacitor

MP2307 Rev. 1.9 www.MonolithicPower.com 11

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

MP2307 – 3A, 23V, 340KHz SYNCHRONOUS RECTIFIED STEP-DOWN CONVERTER

PACKAGE INFORMATION

SOIC8N (EXPOSED PAD)

0.189(4.80) 0.124(3.15)

0.197(5.00) 0.136(3.45)

8 5

0.150(3.80) 0.228(5.80) 0.089(2.26)

PIN 1 ID 0.157(4.00) 0.244(6.20) 0.101(2.56)

1 4

TOP VIEW BOTTOM VIEW

SEE DETAIL "A"

0.051(1.30)

0.067(1.70)

0.0075(0.19)

SEATING PLANE

0.0098(0.25)

0.000(0.00)

0.013(0.33) 0.006(0.15)

0.020(0.51) SIDE VIEW

0.050(1.27)

BSC

FRONT VIEW 0.010(0.25)

x 45o

0.020(0.50)

GAUGE PLANE

0.010(0.25) BSC

0.024(0.61) 0.050(1.27)

0.016(0.41)

0o-8o 0.050(1.27)

0.063(1.60)

DETAIL "A"

0.103(2.62) 0.213(5.40)

NOTE:

1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN

BRACKET IS IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS.

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH

0.138(3.51) OR PROTRUSIONS.

4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING)

SHALL BE 0.004" INCHES MAX.

RECOMMENDED LAND PATTERN 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

6) DRAWING IS NOT TO SCALE.

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third

party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not

assume any legal responsibility for any said applications.

MP2307 Rev. 1.9 www.MonolithicPower.com 12

5/28/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2008 MPS. All Rights Reserved.

Potrebbero piacerti anche

- Abc der Power Module: Funktionsweise, Aufbau und Handling eines Power ModulsDa EverandAbc der Power Module: Funktionsweise, Aufbau und Handling eines Power ModulsWürth ElektronikNessuna valutazione finora

- Parts List Catalog Kubota RG058-8129-0 - KX016-4 PDFDocumento177 pagineParts List Catalog Kubota RG058-8129-0 - KX016-4 PDFЖеня Стець100% (1)

- Parts List Catalog Kubota RG038-8128-0 - KX36-3 PDFDocumento160 pagineParts List Catalog Kubota RG038-8128-0 - KX36-3 PDFЖеня Стець100% (1)

- 03 IM3131rev02 - GERDocumento19 pagine03 IM3131rev02 - GERAlejandro Pino GomezNessuna valutazione finora

- Manual MVC-60V REV BDocumento12 pagineManual MVC-60V REV Bmauri lopezNessuna valutazione finora

- Mikrowechselrichter: HM-1000 / HM-1200 / HM-1500Documento2 pagineMikrowechselrichter: HM-1000 / HM-1200 / HM-1500No ViewNessuna valutazione finora

- Manuale Samil SR TL DDocumento84 pagineManuale Samil SR TL DVilmos OpraNessuna valutazione finora

- BA BLR CM deDocumento8 pagineBA BLR CM deLeonel FloresNessuna valutazione finora

- Mikrowechselrichter: HM-600 / HM-700 / HM-800Documento2 pagineMikrowechselrichter: HM-600 / HM-700 / HM-800No ViewNessuna valutazione finora

- VM237Documento2 pagineVM237hammad rehmanNessuna valutazione finora

- 7PA23Documento2 pagine7PA23Arun KumarNessuna valutazione finora

- DB de Mini Power 24v 4a 5107908 02Documento8 pagineDB de Mini Power 24v 4a 5107908 02jesus.alonsoNessuna valutazione finora

- HUAWEI SUN2000 MA - 3-10KTL-M0 Datenblatt DDocumento2 pagineHUAWEI SUN2000 MA - 3-10KTL-M0 Datenblatt DRayen GarierNessuna valutazione finora

- TD rwg4020 deDocumento1 paginaTD rwg4020 deDiego FernandesNessuna valutazione finora

- 24V DC Primärschaltregler - Netzgeräte, Serie NEK 24V DC Primary Switch Mode Power Supplies, Series NEKDocumento1 pagina24V DC Primärschaltregler - Netzgeräte, Serie NEK 24V DC Primary Switch Mode Power Supplies, Series NEKARTMehr Eng. GroupNessuna valutazione finora

- De Bc5004 DFFDocumento2 pagineDe Bc5004 DFFMawupemon AdzivonNessuna valutazione finora

- PowerMaster S PDFDocumento2 paginePowerMaster S PDFscrollock0428Nessuna valutazione finora

- 11 5 ECOVARIO 114 DDocumento4 pagine11 5 ECOVARIO 114 DalinupNessuna valutazione finora

- Absolutdrucksensoren: Medienresistent, MikromechanikDocumento4 pagineAbsolutdrucksensoren: Medienresistent, Mikromechanikolivia-backNessuna valutazione finora

- Leaflet - UG ZS1 - RevB - 2012 - 09 - deDocumento2 pagineLeaflet - UG ZS1 - RevB - 2012 - 09 - deArtur FiduraNessuna valutazione finora

- Ba - 6ep1961 3ba20 5Documento8 pagineBa - 6ep1961 3ba20 5MAnhNessuna valutazione finora

- Siemens 3UA66 - Relé TérmicoDocumento8 pagineSiemens 3UA66 - Relé TérmicoCleber MachadoNessuna valutazione finora

- 11 7 ECOVARIO 414 DDocumento4 pagine11 7 ECOVARIO 414 DalinupNessuna valutazione finora

- ScriptDocumento20 pagineScriptJan BeckerNessuna valutazione finora

- IS WAVE CMA CMR MonitorDocumento52 pagineIS WAVE CMA CMR MonitorPvalpNessuna valutazione finora

- 1.3.14 / 15 Elektrotechnik Basiskenntnisse: Physiologische Wirkung Des Stromes (Strom Durch Lebewesen)Documento43 pagine1.3.14 / 15 Elektrotechnik Basiskenntnisse: Physiologische Wirkung Des Stromes (Strom Durch Lebewesen)Goncalo SousaNessuna valutazione finora

- Panou Fotovoltaic BS.400 410.M10HB GermaniaDocumento2 paginePanou Fotovoltaic BS.400 410.M10HB GermaniaVoicila CosminNessuna valutazione finora

- 2SD880 WeitronDocumento3 pagine2SD880 WeitronVenu Gopal Rao AggressNessuna valutazione finora

- Solarmax C-Series Data ST DeuDocumento2 pagineSolarmax C-Series Data ST Deuhitzero2003Nessuna valutazione finora

- Dcu 2aDocumento9 pagineDcu 2aIván SulbaranNessuna valutazione finora

- Rcma420 D00059 Q DeenDocumento8 pagineRcma420 D00059 Q Deen王磊(KissYourToes)Nessuna valutazione finora

- 2-252F4-252Fb-252Fa-8c82032fce46 DB Ivh Hu Sun2000 3 10ktl m1 deeRKPCgqc0ttwiDocumento2 pagine2-252F4-252Fb-252Fa-8c82032fce46 DB Ivh Hu Sun2000 3 10ktl m1 deeRKPCgqc0ttwirsbp89v2rnNessuna valutazione finora

- memodo-solaredge-wechselrichter-dreiphasenwechselrichter-mit-synergie-datenblatt_0e2b3096f027119Documento3 paginememodo-solaredge-wechselrichter-dreiphasenwechselrichter-mit-synergie-datenblatt_0e2b3096f027119Marian MardareNessuna valutazione finora

- S22DEDocumento18 pagineS22DEaNessuna valutazione finora

- Europäische Bauform / European Standard: SQB 1 Din 110Documento2 pagineEuropäische Bauform / European Standard: SQB 1 Din 110Anand DudejaNessuna valutazione finora

- CR0403 CanDocumento18 pagineCR0403 CanvladimirpessoaNessuna valutazione finora

- 7PA26Documento2 pagine7PA26alexhandercgNessuna valutazione finora

- 3WL91110BA140AA0 Datasheet deDocumento3 pagine3WL91110BA140AA0 Datasheet devolimo.b87Nessuna valutazione finora

- Prop Vent Il TechnikDocumento40 pagineProp Vent Il Technikrafael alvarezNessuna valutazione finora

- 2261V102 UkDocumento18 pagine2261V102 UkPrabhu DevNessuna valutazione finora

- Manual Mld3Documento160 pagineManual Mld3Miguel Benitez CardonaNessuna valutazione finora

- S5037-0-DDocumento18 pagineS5037-0-DGiovas SandovalNessuna valutazione finora

- PanelmeterDocumento10 paginePanelmetervintagekikiNessuna valutazione finora

- Electronicon CapacitorDocumento6 pagineElectronicon CapacitorionutNessuna valutazione finora

- 6SL3210-5BB21-1BV1_datasheet_de_enDocumento2 pagine6SL3210-5BB21-1BV1_datasheet_de_enastNessuna valutazione finora

- AntvioDocumento11 pagineAntvioMIguel Angel CorralesNessuna valutazione finora

- AnapwmDocumento3 pagineAnapwmMIguel Angel CorralesNessuna valutazione finora

- 42,0410,2610Documento8 pagine42,0410,2610edou mawudoudjiNessuna valutazione finora

- 2030 - Anleitung - Operating Instructions - ManuelDocumento76 pagine2030 - Anleitung - Operating Instructions - ManuelNeryNessuna valutazione finora

- bc846 SMD 1FpDocumento2 paginebc846 SMD 1FpidnuejdbflxmynpkrnNessuna valutazione finora

- Trennverstaerker vm130Documento2 pagineTrennverstaerker vm130Isaac SidibeNessuna valutazione finora

- Logik Modul AC010Documento8 pagineLogik Modul AC010Oreonnyr SouzaNessuna valutazione finora

- CR0411Documento25 pagineCR0411Marcos González FernándezNessuna valutazione finora

- Instruction 11027205 Eiw-C18 230vac 2we. Atch-107835.en - TRDocumento6 pagineInstruction 11027205 Eiw-C18 230vac 2we. Atch-107835.en - TRkadir kayaNessuna valutazione finora

- AE Refusol Datasheet - AE - 3TL - 40-46 - DEDocumento4 pagineAE Refusol Datasheet - AE - 3TL - 40-46 - DEHilal HazaaNessuna valutazione finora

- Planos VemagDocumento22 paginePlanos VemagDiego Nicolas Izeta GenovaNessuna valutazione finora

- Bax 4647 deDocumento51 pagineBax 4647 dePedro GutmanNessuna valutazione finora

- 2CDC120059M0102Documento338 pagine2CDC120059M0102Adam RoguszczakNessuna valutazione finora

- Altivar 312 - ATV312H075N4410Documento4 pagineAltivar 312 - ATV312H075N4410PeteNessuna valutazione finora

- Calibration BoxDocumento16 pagineCalibration BoxSamy FouadNessuna valutazione finora

- Catalog Sheet APAQ-L deDocumento1 paginaCatalog Sheet APAQ-L deVictor GutierrezNessuna valutazione finora

- GLR Adc de PDFDocumento7 pagineGLR Adc de PDFYiris MorenoNessuna valutazione finora

- B2 Olvasás 1 Zimmerpflanzen FeladatDocumento2 pagineB2 Olvasás 1 Zimmerpflanzen FeladatGabriella Molnárné MagyarNessuna valutazione finora

- Adjektive Mit Präpositionen PDFDocumento6 pagineAdjektive Mit Präpositionen PDFSafeer SefiNessuna valutazione finora

- Renault 02 Laguna Benzin EBVDocumento43 pagineRenault 02 Laguna Benzin EBVHerbert AnglbergerNessuna valutazione finora