Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

6-Phase PWM Controller With 8-Bit DAC Code For VR10 and VR11

Caricato da

Anak PulauTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

6-Phase PWM Controller With 8-Bit DAC Code For VR10 and VR11

Caricato da

Anak PulauCopyright:

Formati disponibili

MP2932

6-Phase PWM Controller

with 8-Bit DAC Code for VR10 and VR11

The Future of Analog IC Technology

DESCRIPTION FEATURES

The MP2932 is a 6-phase, synchronous buck 2-, 3-, 4-, 5- or 6-phase Operation

switching regulator controller for regulating Channel-Current Balancing

microprocessor core voltage. MP2932 also uses Voltage Droop vs. Load Current

dual edge PWM mode to realize fast load Precision Resistor or DCR Current Sensing

transient with fewer capacitors. Adjustable Switching Frequency

For meeting the requirement of microprocessor Over Current Protection

output voltage drops tightly as load current Available in a 48-pin QFN6x6 Package

increases, output current is sensed to realize

voltage droop function. Accurate current APPLICATIONS

balancing is included in MP2932 to provide Power Modules

current balance for each channel. Desktop, Server, Core Voltage

8-bit ID input with selectable VR11 code and POLs (Memory)

extended VR10 code can set output voltage All MPS parts are lead-free and adhere to the RoHS directive. For MPS green

status, please visit MPS website under Quality Assurance. “MPS” and “The

dynamically. Future of Analog IC Technology” are Registered Trademarks of Monolithic

Power Systems, Inc.

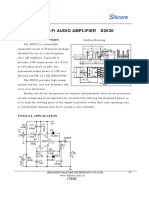

TYPICAL APPLICATION (6-PHASE BUCK CONVERTER)

5V Vin Intelli-phase

Vin BST

PWM SW

FB COMP VCC DAC EN 5V

REF VCC

IDROOP GND

VDIFF

VSEN PWM1

RGND Vin Intelli-phase

ISEN1-

VTT EN_VTT Vin BST

ISEN1+

VR_ RDY PWM SW

ID7 5V

EN

ID6

PWM2 GND VCC

ID5

ISEN2-

ID4

ISEN2+

ID3 Intelli-phase

Vin

ID2 SD

MP2932 Vin BST

ID1

ID0 PWM3 PWM SW

VRSEL EN 5V

ISEN3-

OVP VCC

GND

ISEN3+

IOUT

ROUT

PWM4 Vin Intelli-phase

ISEN4- Vin BST

VR_ FAN

ISEN4+ PWM SW

EN 5V

VR_HOT

PWM5 VCC

GND

ISEN5-

Vin

ISEN5+ Vin Intelli-phase

Vin BST

PWM6

EN_PWR

ISEN6- PWM SW

ISEN6+ EN 5V

GND

5V GND VCC

TM OFS FS SS

Intelli-phase

Vin BST

PWM SW

EN 5V

GND VCC

MP2932 Rev.1.02 www.MonolithicPower.com 1

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

ORDERING INFORMATION

Part Number* Package Top Marking Free Air Temperature (TA)

MP2932GQK QFN (6 x 6mm) MP2932 –40C to +85C

* For Tape & Reel, add suffix –Z (e.g. MP2932GQK–Z);

For RoHS compliant packaging, add suffix –LF; (e.g. MP2932GQK –LF–Z).

PACKAGE REFERENCE

(4)

ABSOLUTE MAXIMUM RATINGS (1) Thermal Resistance θJA θJC

Supply Voltage VCC ..................................... 6V QFN48 (6mm x 6mm) ............. 32 ...... 3.5 .. C/W

All Other Pins ..................... -0.3V to VCC + 0.3V Notes:

Continuous Power Dissipation (TA = +25°C) (2) 1) Exceeding these ratings may damage the device.

............................................................. 3.9W 2) The maximum allowable power dissipation is a function of the

maximum junction temperature TJ (MAX), the junction-to-

Junction Temperature ...............................150C ambient thermal resistance θJA, and the ambient temperature

Storage Temperature .............. –65C to +150C TA. The maximum allowable continuous power dissipation at

any ambient temperature is calculated by PD (MAX) = (TJ (MAX)-

ESD Rating TA) /θJA. Exceeding the maximum allowable power dissipation

Human Body Model .................................... 2kV will cause excessive die temperature, and the regulator will

go into thermal shutdown. Internal thermal shutdown circuitry

Machine Model .......................................... 200V protects the device from permanent damage.

Charged Device Model ............................. 1.5kV 3) The device is not guaranteed to function outside of its

operating conditions.

(3)

Recommended Operating Conditions 4) Measured on JESD51-7, 4-layer PCB.

Supply Voltage VCC ........................... +5V ±5%

Operating Junction Temp. (TJ). -40°C to +125°C

MP2932 Rev.1.02 www.MonolithicPower.com 2

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

ELECTRICAL CHARACTERISTICS

Operating conditions: VCC = 5V, unless otherwise noted.

Parameter Test conditions Min Typ Max Units

VCC Supply Current

VCC=5VDC; EN_PWR=5VDC;

RT=100kΩ,

Nominal Supply 18 26 mA

ISEN1=ISEN2=ISEN3=ISEN4= ISEN5=

ISEN6=-70μA

VCC=5VDC; EN_PWR=0VDC;

Shutdown Supply 14 21 mA

RT=100kΩ

Power-on Reset and Enable

VCC Rising 4.3 4.5 4.7 V

POR Threshold

VCC Falling 3.7 3.9 4.2 V

Rising 0.850 0.88 0.910 V

EN_PWR Threshold Hysteresis 130 mV

Falling 0.71 0.745 0.78 V

Rising 0.850 0.88 0.910 V

EN_VTT Threshold Hysteresis 130 mV

Falling 0.71 0.745 0.78 V

Reference Voltage and DAC

System Accuracy of MP2932

-0.5 0.5 ℅ID

(ID =1V to 1.6V, TJ=0C to +70C)

System Accuracy of MP2932

-0.9 0.9 ℅ID

(ID =0.5V to 1V, TJ=0C to +70C)

ID Pull-Up -60 -40 -20 μA

ID Input Low Level 0.4 V

ID Input High Level 0.8 V

VRSEL Input Low Level 0.4 V

VRSEL High Low Level 0.8 V

DAC Source Current 4 7 mA

DAC Sink Current 320 μA

Pin-adjustable Offset

Offset resistor connected to

380 400 420 mV

ground

Voltage at OFS Pin

Voltage below VCC, offset resistor

1.55 1.600 1.65 V

connected to VCC

Oscillators

Accuracy of Switching Frequency

RT=100kΩ 225 250 275 kHz

setting

Adjustment Range of Switching

0.08 1.0 MHz

Frequency

Soft-Start Ramp Rate RS=150kΩ 1.563 mV/μs

Adjustment Range of Soft-Start

0.625 6.25 mV/μs

Ramp Rage

MP2932 Rev.1.02 www.MonolithicPower.com 3

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

ELECTRICAL CHARACTERISTICS (continued)

Operating conditions: VCC = 5V, unless otherwise noted.

Parameter Test conditions Min Typ Max Units

Error Amplifier

Maximum Output Voltage 3.8 4.2 4.6 V

Output High Voltage @ 2mA 3.6 V

Output Low Voltage @ 2mA 1.8 V

Remote-sense Amplifier

Bandwidth 20 MHz

Output High Current VSEN-RGND=2.5V -100 100 μA

Output High Current VSEN-RGND=0.6 -100 100 μA

PWM Output

PWM Output Voltage Low Threshold ILOAD=±500μA 0.5 V

PWM Output Voltage High Threshold ILOAD=±500μA 4.3 V

Current Sense and Over-current Protection

ISEN1=ISEN2=ISEN3=ISEN4=

Sensed Current Tolerance(IDROOP) 47 50 53 μA

ISEN5=ISEN6=50μA

Overcurrent Trip level for Average

72 85 98 μA

Current

Peak Current Limit for Individual

120 μA

Channel

Maximum Voltage at IDROOP and

1.98 2.01 2.04 V

IOUT Pins

Thermal Monitoring and Fan Control

TM Input Voltage for VR_FAN TRIP 1.55 1.65 1.75 V

TM Input Voltage for VR_FAN Reset 1.85 1.95 2.05 V

TM Input Voltage for VR_HOT Trip 1.3 1.4 1.5 V

TM Input Voltage for VR_HOT Reset 1.55 1.65 1.75 V

With externally pull-up resistor

Leakage current of VR_FAN 30 μA

connected to VCC

VR_RAN Low Voltage IVR_FAN=4mA 0.4 V

With externally pull-up resistor

Leakage Current of VR_HOT 30 μA

connected to VCC

VR_HOT Low Voltage IVR_HOT=4mA 0.4 V

VR Ready and Protection Monitors

With externally pull-up resistor

Leakage Current of VR_RDY 30 μA

connected to VCC

VR_RDY Low Voltage IVR_RDY=4mA 0.4 V

Undervoltage Threshold VDIFF Falling 48 50 52 ℅ID

VR_RDY Reset Voltage VDIFF Rising 58 60 62 ℅ID

Before Valid ID 1.250 1.275 1.300 V

Overvoltage Protection Threshold After valid ID, the voltage above

150 175 200 Mv

ID

Overvoltage Protection Reset

100 mV

Hysteresis

MP2932 Rev.1.02 www.MonolithicPower.com 4

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

PIN FUNCTIONS

Pin # Name Description

1 ID7

2 ID6

3 ID5

4 ID4

ID inputs from microprocessor. These codes determine output regulation voltage.

5 ID3

6 ID2

7 ID1

8 ID0

Select internal ID code. When it is tied to GND, the extended VR10 is selected. When

9 VRSEL

it’s floated or tied to high, VR11 code is selected.

Offset between REF and DAC program pin. The OFS pin can be used to program a

DC offset current which will generate a DC offset voltage between the REF and DAC

10 OFS

pins. The polarity of the offset is selected by connecting the resistor to GND or VCC.

For no offset, the OFS pin should be left unconnected.

A resistor needs to be placed between IOUT and GND to ensure the proper operation.

11 IOUT

The voltage at IOUT pin will be proportional to the load current.

12 DAC Internal DAC reference output determined by ID codes

Error amplifier input. A capacitor 0.1uF is used between REF and GND to smooth the

13 REF

voltage transition during Dynamic ID operations.

14 COMP Error amplifier output pin. Tie to compensation network

15 FB Output voltage feedback pin.

16 IDROOP Current proportional to load current is flowed out through this pin

17 VDIFF Remote sense amplifier output. VDIFF-GND=VSEN-RGND

18 RGND Remote sense amplifier input. Remote output GND

19 VSEN Remote sense amplifier input. Remote output.

Shutdown Intelli-phase @ Hiz state. MP2932 cooperates with MPS Intelli-phase and

20 SD

SD pin is connected to the EN of Intelli-phase.

21 VCC Power supply. Connect this pin directly to a +5V supply.

22 ISEN5-

Phase 5 current sense amplifier differential inputs.

23 ISEN5+

24 PWM5 Phase 5 PWM output.

25 PWM2 Phase 2 PWM output.

26 ISEN2+

Phase 2 current sense amplifier differential input.

27 ISEN2-

28 ISEN4-

Phase 4 current sense amplifier differential input.

29 ISEN4+

30 PWM4 Phase 4 PWM output.

31 PWM1 Phase 1 PWM output.

32 ISEN1+

Phase 1 current sense amplifier differential input.

33 ISEN1-

MP2932 Rev.1.02 www.MonolithicPower.com 5

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

PIN FUNCTIONS (continued)

Pin # Name Description

34 ISEN3-

Phase 3 current sense amplifier differential input.

35 ISEN3+

36 PWM3 Phase 3 PWM output.

37 PWM6 Phase 6 PWM output.

38 ISEN6+

Phase 6 current sense amplifier differential input

39 ISEN6-

Enable pin. It is used to synchronize power-up of the controller and MOSFET driver

40 EN_PWR

ICs.

41 EN_VTT Enable pin. It is controlled by output of VTT voltage regulator in the mother board.

42 FS PWM frequency set pin. A resistor from FS to GND will set the switching frequency.

Soft start oscillator frequency set pin. A resistor from SS to GND will set up the soft-

43 SS

start ramp rate.

Overvoltage protection output indication pin. It can be pulled to VCC and is latched

44 OVP

when an overvoltage condition is detected.

Open drain logic output. When soft start completed and output voltage is regulated in

45 VR_RDY

the value determined by ID setting, VR_RDY is logic high.

46 VR_FAN Open drain logic output. It is open when VR temperature reaches certain value

47 VR_HOT Open drain logic output. It is open when VR temperature reaches certain value

NTC resistor in this pin is used to monitor inductor temperature. Connect this pin

48 TM through an NTC thermistor to GND and a resistor to VCC of the controller. The voltage

at this pin is reverse proportional to the VR temperature.

MP2932 Rev.1.02 www.MonolithicPower.com 6

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

TYPICAL PERFORMANCE CHARACTERISTICS

VIN=12V, VID=1.2V, L=0.3µH, FSW=600kHz, 6-Phase Operation, TA = +25ºC, unless otherwise noted.

Normal Supply Current Shutdown Supply Current Switching Frequency

vs. VCC vs. VCC vs. RT

IOUT=0A

19 17 1200

SHUTDOWN SUPPLY CURRENT (mA)

NORMAL SUPPLY CURRENT (mA)

18 1000

FREQUENCY (kHz)

16

17 800

16 15 600

15 400

14

14 200

13 13 0

3.5 4 4.5 5 5.5 6 6.5 3.5 4 4.5 5 5.5 6 6.5 20 60 100 140 180 220 260 300 340

V CC (V) V CC (V)

Line Regulation

IOUT=60A

NORMALIZED OUTPUT VOLTAGE (%)

1.22 2.0 120

1.5 110

1.20

OUTPUT VOLTAGE (V)

100

1.0

90

1.18

0.5 80

IOCP (A)

1.16 0.0 70

-0.5 60

1.14 50

-1.0

40

1.12

-1.5 30

1.10 -2.0 20

0 10 20 30 40 50 60 70 80 90 5 7 9 11 13 15 17 19 21 20 30 40 50 60 70 80 90

OUTPUT CURRENT (A) INPUT VOLTAGE (V)

95

90

85

EFFICIENCY (%)

80

75

70

65

60

55

50

0 20 40 60 80 100 120

OUTPUT CURRENT (A)

MP2932 Rev.1.02 www.MonolithicPower.com 7

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN=12V, VID=1.2V, L=0.3µH, FSW=600kHz, 6-Phase Operation, TA = +25ºC, unless otherwise noted.

MP2932 Rev.1.02 www.MonolithicPower.com 8

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

BLOCK DIAGRAM

OVP VDIFF VR_RDY FS VCC

S 0.875

OVP R CLOCK AND POWER-ON

DRIVE RAMP GENETATOR RESET ( POR)

RGND EN_ VTT

Q

X1

VSEN

0.875

EN_PWR

SOFT- START

OVP AND

FAULT LOGIC

PWM

MODULATOR

+175mV PWM1

PWM

SS MODULATOR

PWM2

VRSEL

PWM

ID7 MODULATOR

PWM3

ID6

ID5

DYNAMIC PWM

ID4

VID MODULATOR

PWM4

ID3 DVA

ID2

ID1 PWM

MODULATOR

ID0 PWM5

DAC PWM

MODULATOR

PWM6

OFS OFFSET

REF

E /A CHANNEL

FB CURRENT

CHANNEL

BALANCE

DETECT

AND PEAK

COMP CURRENT LIMIT

ISEN1+

2V I_TRIP

OC2 ISEN1-

OC1 ISEN2+

ISEN2-

IOUT

1 ISEN3+

N

S

I_TOT ISEN3-

CHANNEL

ISEN4+

CURRENT

SENSE ISEN4-

IDROOP ISEN5+

THERMAL S HUTDOWN

MONITOR DRIVER MOS @ ISEN5-

Hiz STATE

ISEN6+

ISEN6-

TM VR_ FAN VR_HOT SD GND

Figure 1—Functional Block Diagram

MP2932 Rev.1.02 www.MonolithicPower.com 9

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

OPERATION

Multiphase Power Conversion Current Sensing

The MP2932 is a multiphase VR controller for MP2932 has cycle by cycle current sense for fast

Intel VR11 or VR10. It can be programmed for 2-, response. MP2932 adopts inductor DCR sensing,

3-, 4-, 5- or 6 channel operation for micro- or resistive sensing techniques. The sense

processor core supply power converters with current, ISEN, is proportional to the inductor

interleaved switching. The interleaving work of current. The sensed current is used for current

each phase can help to reduce of ripple current balance, load-line regulation, and overcurrent

amplitude in the multiphase circuit and to reduce protection.

input ripple current.

Inductor DCR Sensing

The MP2932 control system is based on Dual- The MP2932 can adopt a lossless current

Edge PWM providing the fastest load response. sensing scheme, commonly referred to as

inductor DCR sensing, as shown in Figure 2.

Under load transition condition, the MP2932 can

turn on all phase together to improve the load Intelli-Phase IL(s)

Vin

transient. It can achieve excellent transient L DCR VOUT

Vin

performance and reduce the demand on the SW

GND

output capacitors. VL COUT

PWM VC(s)

Number of Phases

R C

The number of operational phases is determined PWM(n)

by internal circuitry that monitors the PWM

outputs. Normally, the MP2932 operates as a 6- MP2932 INTERNAL CIRCUIT

R ISEN(n)

phase controller. The number of active channels

In

is determined by the state of PWM3, PWM4,

PWM5, and PWM6. For 2-phase operation,

CURRENT

connect PWM3 to VCC; similarly, PWM4 for 3- SENSE ISEN-(n)

phase, PWM5 for 4-phase, and PWM6 for 5-

phase operation. Table 1 shows the phase firing ISEN+(n)

sequence.

CT

Table 1—Phase firing sequence I DCR

SEN =IL R

ISEN

Configuration Phase Sequence

6-Phase 1-2-3-4-5-6 Figure 2—DCR Sensing Configuration

5-Phase 1-2-3-4-5 Equation (2) shows the s-domain equivalent

4-Phase 1-3-4-2 voltage across the inductor VL.

3-Phase 1-2-3 VL IL s L DCR (2)

2-Phase 1-2

A simple RC network across the inductor extracts

Switching Frequency the DCR voltage, as shown in Figure 2.

The clock frequency is set by an external resistor

RT connected from the FS pin to GND. The voltage on the capacitor VC, can be shown to

be proportional to the channel current IL, see

The resistor RT can be estimated by Equation (1). Equation (3).

2.5 1010

RT

FSW

600 (1)

s

L

DCR

1 DCR IL

VC (3)

Where FSW is the switching frequency of each s RC 1

phase.

MP2932 Rev.1.02 www.MonolithicPower.com 10

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

If the RC network components are selected adjustment to the PWM duty cycle of each

such that the RC time constant (=R*C) matches channel.

the inductor time constant (=L/DCR), the

Output Voltage and Load-Line Regulation

voltage across the capacitor VC is equal to the

The MP2932 uses an internal differential

voltage drop across the DCR, i.e., proportional

remote-sense amplifier as shown in Figure 4.

to the channel current.

The microprocessor voltage is sensed between

Therefore, the current out of ISEN+ pin (ISEN), is the VSEN and RGND pins.

proportional to the inductor current and it can

The output of the error amplifier (VCOMP) is

be seen form Equation (4).

compared to sawtooth waveforms to generate

DCR

ISEN IL (4) the PWM signals. The typical open-loop gain of

RISEN error amplifier is no less than 80dB, and the

typical open-loop bandwidth is no less than

Resistive Sensing

20MHz. The PWM signals control the timing of

For accurate current sense, a current-sense

the MPS Intelli-phase and regulate the

resistor RSENSE in series with each output

converter output to the specified reference

inductor can also be adopted (see Figure 3).

voltage.

This technique reduces overall converter

efficiency due to the additional power loss on EXTERNAL CIRCUIT MP2932 INTERNAL CIRCUIT

RSENSE. COMP

RC CC

Equation (5) shows the relationship between DAC

the channel current to the sensed current ISEN. R REF

REF

CREF

R

ISEN IL SENSE (5) VCOMP

RISEN FB

IAVG ERROR AMPLIFIER

IDROOP

IL R FB VDROOP

L RSENSE VOUT VDIFF

COUT VSEN

VOUT+

MP2932 INTERNAL CIRCUIT

VOUT- RGND

In RISEN(n) DIFFERENTIAL

REMOTE-SENSE

AMPLIFIER

CURRENT

SENSE ISEN-(n) Figure 4—Output Voltage and Load-line

ISEN+(n)

Regulation

CT The load-line is realized by a resistor RFB

R

ISEN =I L SENSE

connected between FB pin and the remote

R ISEN sense output (VDIFF). As shown in Figure 4,

the average current of all active channels (IAVG)

Figure 3—Sense Resistor in Series with flows from FB through the load-line regulation

Inductors resistor RFB. The resulting voltage drop across

Channel-Current Balance RFB can be seen form Equation (6):

The sensed current from each active channel is VDROOP I AVGRFB (6)

summed together and divided by the number of

active channels. The resulting average current The output voltage is reduced by the droop

(IAVG) provides a measure of the total load voltage VDROOP, and it is a function a load

current. Channel current balance is achieved by current. It’s derived by combining Equation (6)

comparing the sensed current of each channel with the appropriate sensing current expression

to the average current to make an appropriate defined by the current sense method.

MP2932 Rev.1.02 www.MonolithicPower.com 11

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

I RX 0.4 R

VOUT VREF VOFS OUT R FB (7) V REF (10)

N R OFFSET R

ISEN OFS

Where VREF is the reference voltage, VOFS is the Enable and Disable

programmed offset voltage, IOUT is the total While in shutdown mode, the PWM outputs are

output current of the converter, RISEN is the held in a Hi-Z state, and the SD signal is pulled

sense resistor connected to the ISEN+ pin, and low to assure the Intelli-phase remain off. The

RFB is the feedback resistor, N is the active following input conditions must be met to start

channel number, and RX is the DCR, or RSENSE MP2932.

depending on the sensing method.

1. VCC must reach the internal power-on reset

Therefore, the loadline is defined as: (POR) rising threshold.

R FB RX 2. EN_PWR is used to coordinate the power

R LL (8)

N RISEN sequencing between VCC and another

voltage rail. The enable comparator holds

Output Voltage Offset Programming the MP2932 in shutdown until the voltage at

In Figure 5, OFS pin is used to generate no- EN_PWR rises above 0.875V.

load offset. A resistor RREF between DAC and

REF is selected, and the product (IOFS x ROFS) is 3. The voltage on EN_VTT must be higher than

equal to the desired offset voltage. 0.875V to enable the controller. This pin is

FB

typically connected to the output of VTT VR.

MP2932 INTERNAL CIRCUIT EXTERNAL CIRCUIT

DYNAMIC DAC +12V

ID D/A VCC

RREF

E/A REF POR ENABLE 10kO

CIRCUIT COMPARATOR

C REF EN_PWR

910O

VCC 0.875V

OR

GND

EN_VTT

1.6V R OFS

0.4V

OFS

MP2932

0.875V

VCC GND

SOFT-START

Figure 5—Offset Voltage Programming AND

FAULT LOGIC

Connect a resistor ROFS between OFS to VCC 4.

to generate a positive offset. The voltage Figure 6—Power Sequencing Using

across it is regulated to 1.6V. This causes a Threshold Sensitive Enable (EN) Function

proportional current (IOFS) to flow into OFS. The

When all conditions are satisfied, MP2932

positive offset is:

1.6 R begins the soft-start and ramps the output

V REF (9) voltage to 1.1V first. After remaining at 1.1V for

OFFSET R

OFS some time, MP2932 reads the ID code at ID

input pins. If the ID code is valid, MP2932 will

Connect a resistor ROFS between OFS to GND regulate the output to the final ID setting. If the

to generate a negative offset. The voltage ID code is OFF code, MP2932 will shutdown,

across it is regulated to 0.4V, and IOFS flows out and cycling VCC, EN_PWR or EN_VTT is

of OFS. The negative offset is: needed to restart.

MP2932 Rev.1.02 www.MonolithicPower.com 12

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

Soft-Start

MP2932 has 4 periods during soft-start as t

2 V VID 1.1 R SS

(us) (13)

d4 3 6.25 25

shown in Figure 7. After VCC, EN_VTT and

EN_PWR reach their POR/enable thresholds, For example, when ID is set to 1.5V and the

the controller will have fixed delay period td1 RSS is set at 100kΩ, the first soft-start ramp time

1.36ms. After the delay period, the VR will td2 will be 469µs and the second soft-start ramp

begin first soft-start ramp until the output time td4 will be 171µs.

voltage reaches 1.1V. Then, the controller will

regulate the VR voltage at 1.1V for another After the DAC voltage reaches the final ID

fixed period td3. At the end of td3 period, MP2932 setting, VR_RDY will be set to high with the

reads the ID signals. If the ID code is valid, fixed delay td5, it’s about 85µs.

MP2932 will initiate the second soft-start ramp VR_RDY Signal

until the voltage reaches the ID voltage minus The VR_RDY pin is an open-drain logic output.

offset voltage. It is pulled low during shutdown and releases

high after a successful soft-start. VR_RDY will

be pulled low when an under-voltage or over-

voltage condition is detected, or the controller is

1.1V

disabled by a reset from EN_PWR, EN_VTT,

POR, or ID OFF-code.

VOUT Under-voltage Detection

td1 td2 td3 td4 td5 The under-voltage threshold is set at 50% of

EN_VTT

the ID code. When the output voltage at VSEN

is below the under-voltage threshold, VR_RDY

is pulled low.

VR_RDY

Over-voltage Protection (OVP)

500us/DIV

Regardless of the VR being enabled or not, the

Figure 7—Soft-Start Waveforms MP2932 OVP circuit will be active after its POR.

The OVP thresholds are different at different

The soft-start time is the sum of the 4 periods, operation conditions. When VR is not enabled

as shown in Equation (11): and during the soft-start intervals td1, td2 and td3,

tSS t d1 t d2 t d3 t d4 (11) the OVP threshold is 1.275V. Once the

controller detects valid ID input, the OVP trip

td1 is about 1.36ms. td3 is determined by the point will be changed to DAC + 175mV.

fixed 85µs plus the time to obtain valid ID

voltage. If the ID is valid before the output VR_RDY

reaches the 1.1V, the minimum time to validate

the ID input is 500ns. Therefore the minimum

UV

td3 is about 86µs.

During td2 and td4, MP2932 digitally controls the 50%

85uA

DAC voltage change at 6.25mV per step. The SOFT-START, FAULT

OC

time for each step is determined by the AND CONTROL LOGIC

IAVG

DAC

frequency of the soft-start oscillator which is

defined by the resistor RSS from SS pin to GND. VDIFF

The second soft-start ramp time td2 and td4 can OV

be calculated based on Equations (12) and (13):

2 1.1 R SS VID + 0.175V

t

d2

(us) (12)

3 6.25 25

Figure 8—VR_RDY and Protection Circuitry

MP2932 Rev.1.02 www.MonolithicPower.com 13

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

At the beginning of an over-voltage event, all

PWM outputs are commanded low instantly OUTPUT CURRENT

(>20ns). The Intelli-phase LS-FET is turned on.

When the VDIFF voltage falls below the DAC +

75mV, PWM signals enter a Hi-Z state, and the

SD pin is pulled low to turn off the Intelli-phase. 0A

If the over-voltage condition reoccurs, the

MP2932 will again command the LS-FET to OUTPUT VOLTAGE

turn on. The MP2932 will continue to protect the

load in this way as long as the over-voltage

condition occurs.

0V

Once an over-voltage condition is detected,

normal PWM operation ceases until the Figure 9—Over-current Behavior in HICCUP

MP2932 is reset. Cycling the voltage on Mode. Fsw = 600kHz

EN_PWR, EN_VTT or VCC below the POR-

falling threshold will reset the controller. Cycling For the individual channel over-current

the ID codes will not reset the controller. protection, the MP2932 continuously compares

the sensed current signal of each channel with

Over-current Protection (OCP) the 120µA reference current. If one channel

MP2932 has two levels of over-current current exceeds the reference current, MP2932

protection. Each phase is protected from a will pull PWM signal of this channel to low for

sustained over-current condition by limiting its the rest of the switching cycle. This PWM signal

peak current, while the combined phase can be turned on next cycle if the sensed

currents are protected on an instantaneous channel current is less than the 120µA

basis. reference current. The peak current limit of

In instantaneous protection mode, the MP2932 individual channel will not trigger the converter

adopts the sensed average current IAVG to to shutdown.

detect an over-current condition. The IAVG is Thermal Monitoring (VR_HOT/VR_FAN)

compared with a constant 85µA reference There are two thermal signals to indicate the

current, as shown in Figure 8. Once IAVG temperature status of the voltage regulator:

exceeds 85µA, a comparator triggers the VR_HOT and VR_FAN. Both VR_FAN and

converter to shutdown. At the beginning of VR_HOT pins are open-drain outputs, and

over-current shutdown, the controller places all external pull-up resistors are required. Those

PWM signals in a Hi-Z state within 20ns to turn signals are valid only after the controller is

off the Intelli-phase. The system remains in this enabled.

state about 12ms. If the controller is still

enabled at the end of this wait period, it will The VR_FAN signal indicates that the

attempt a soft-start. If the fault remains, the temperature of the voltage regulator is high and

hiccup mode will continue indefinitely until more cooling airflow is needed. The VR_HOT

either controller is disabled or the fault is signal can be used to inform the system that the

cleared. temperature of the voltage regulator is too high

and the CPU should reduce its power

consumption.

MP2932 Rev.1.02 www.MonolithicPower.com 14

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

Current Sense Output

VCC The MP2932 has 2 current sense output pins

VR_FAN IDROOP and IOUT, they are identical. In typical

application, IDROOP pin is connected to FB pin

for the application where load line is required.

R TM1 IOUT pin was designed for load current

0.33VCC

measurement.

TM VR_HOT

The current from the IDROOP pin is the sensed

°C R REF average current. In typical application, the

0.28VCC

IDROOP pin is connected to the FB pin for the

application where load line is required. Load

Figure 10—Block Diagram of Thermal current information can be obtained by

Monitoring Function measuring the voltage at IOUT pin with a

resistor connecting IOUT pin to the ground.

Figure 10 shows the diagram of thermal

monitoring function block. One NTC resistor When load line function is not needed, the

should be placed close to the power stage of IDROOP pin can be used to obtain the load

the voltage regulator to sense the temperature, current information: with one resistor from the

and one pull-up resistor is needed to form the IDROOP pin to GND, the voltage at the

voltage divider for the TM pin. As the IDROOP pin will be proportional to the load

temperature of the power stage increases, the current in Equation (14):

resistance of the NTC will reduce, resulting in R RX

the reduced voltage at the TM pin. VIDROOP IDROOP I (14)

N RISEN LOAD

There are two comparators with hysteresis to

compare the TM pin voltage to the fixed Where VIDROOP is the voltage at the IDROOP pin,

thresholds for VR_FAN and VR_HOT signals RIDROOP is the resistor between the IDROOP pin

respectively. The VR_FAN signal is set to high and GND, ILOAD is the total output current of the

when the TM voltage is lower than 33% of VCC converter, RISEN is the sense resistor connected

voltage, and is pulled to GND when the TM to the ISEN+ pin, N is the active channel

voltage increases to above 39% of VCC voltage. number, and RX is the resistance of the current

The VR_FAN signal is set to high when the TM sense element, either the DCR of the inductor

voltage goes below 28% of VCC voltage, and is or RSENSE depending on the sensing method.

pulled to GND when the TM voltage goes back The resistor from the IDROOP pin to GND

to above 33% of VCC voltage. Figure 11 shows should be chosen to ensure that the voltage at

the operation of those signals. the IDROOP pin is less than 2V under the

maximum load current.

TM

If the IDROOP pin is not used, tie it to GND.

0.39*VCC

0.33*VCC

0.28*VCC

VR_FAN

VR_HOT TEMPERATURE

T1 T2 T3

Figure 11—VR_HOT and VR_FAN Signal vs.

TM Voltage

MP2932 Rev.1.02 www.MonolithicPower.com 15

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

APPLICATION INFORMATION

Current Sensing Resistor Compensation

The resistors connected to the ISEN+ pins There are two distinct methods for achieving

determine the gains in the load-line regulation the compensation.

loop and the channel-current balance loop as

Compensating Load-Line Regulated

well as setting the overcurrent trip point. Select

Converter

values for these resistors by using Equation

The load-line regulated converter behaves in a

(15):

similar manner to a peak-current mode

R

X

I

OCP controller because the two poles at the output-

R

ISEN

(15) filter L-C resonant frequency split with the

85 10 6 N

introduction of current information into the

Where RISEN is the sense resistor connected to control loop. The final location of these poles is

the ISEN+ pin, N is the active channel number, determined by the system function, the gain of

RX is the resistance of the current sense the current signal, and the value of the

element, either the DCR of the inductor or compensation components, RC and CC.

RSENSE depending on the sensing method, and

Treating the system as though it were a

IOCP is the desired overcurrent trip point.

voltage-mode regulator by compensating the L-

Typically, IOCP can be chosen to be 1.3x the

C poles and the ESR zero of the voltage-mode.

maximum load current of the specific

application. C 2 (OPTIONAL )

Load-Line Regulation Resistor CC

RC

The load-line regulation resistor is labeled RFB COMP

in Figure 4. Its value depends on the desired

load-line requirement of the application. FB

MP2932

The desired load-line can be calculated by

using Equation (16): R FB VDROOP

IDROOP

V

R DROOP (16) VDIFF

LL I

FL

Where IFL is the full load current of the specific

Figure 12— Compensation Circuit for

application, and VRDROOP is the desired voltage

MP2932 with Load-line Regulation

droop under the full load condition.

The feedback resistor, RFB, has already been

Based on the desired load-line RLL, the load-line

chosen as outlined in “Load-Line Regulation

regulation resistor can be calculated by using

Resistor”. Select a target bandwidth for the

Equation (17):

compensated system, f0. The target bandwidth

NR R

ISEN LL must be large enough to assure adequate

R (17)

FB R transient performance, but smaller than 1/3 of

X

the per-channel switching frequency. The

Where N is the active channel number, RISEN is values of the compensation components

the sense resistor connected to the ISEN+ pin, depend on the relationships of f0 to the L-C pole

and RX is the resistance of the current sense, frequency and the ESR zero frequency.

either the DCR of the inductor or RSENSE

The optional capacitor C2, (22pF to 150pF) is

depending on the sensing method.

sometimes needed to bypass noise away from

the PWM comparator (see Figure 12).

MP2932 Rev.1.02 www.MonolithicPower.com 16

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

characterized according to their capacitance,

Compensation without Load-Line

ESR, and ESL (equivalent series inductance).

Regulation

The non load-line regulated converter is At the beginning of the load transient, the

accurately modeled as a voltage-mode output capacitors supply all of the transient

regulator with two poles at the L-C resonant current. The output voltage will initially deviate

frequency and a zero at the ESR frequency. A by an amount approximated by the voltage drop

type-III controller, as shown in Figure 13, across the ESL. As the load current increases,

provides the necessary compensation. the voltage drop across the ESR increases

C2 linearly until the load current reaches its final

value. The capacitors selected must have

RC CC sufficiently low ESL and ESR so that the total

COMP

output voltage deviation is less than the

allowable maximum. Neglecting the contribution

FB

MP2932

of inductor current and regulator response, the

C1

output voltage initially deviates by an amount in

Equation (18):

RFB IDROOP

R1 di

ΔV ESL ESR ΔI (18)

VDIFF dt

The filter capacitor must have sufficiently low

ESL and ESR so that ΔV < ΔVMAX.

Figure 13—Compensation Circuit for

MP2932 without Load-line Regulation The ESR of the bulk capacitors also creates the

majority of the output voltage ripple. As the bulk

The first step is to choose the desired

capacitors sink and source the inductor AC

bandwidth, f0, of the compensated system.

ripple current, a voltage develops across the

Choose a frequency high enough to assure

bulk-capacitor ESR. Thus, once the output

adequate transient performance but not higher

capacitors are selected, the maximum

than 1/3 of the switching frequency. The type-III

allowable ripple voltage, VP-P(MAX) determines

compensator has an extra high-frequency pole,

the lower limit on the inductance.

fHF. A good general rule is to choose fHF=10f0,

but it can be higher if desired. Choosing fHF to

V - NV

L ESR IN

V

OUT OUT

(19)

be lower than 10f0 can cause problems with too

s IN P - PMAX

f V V

much phase shift below the system bandwidth.

Since the capacitors are supplying a decreasing

Output Inductor

portion of the load current while the regulator

The output inductors and the output capacitor

recovers from the transient, the capacitor

bank together to form a low-pass filter

voltage becomes slightly depleted. The output

responsible for smoothing the pulsating voltage

inductors must be capable of assuming the

at the phase nodes. The output filter also must

entire load current before the output voltage

provide the transient energy until the regulator

decreases more than ΔVMAX. This places an

can respond.

upper limit on inductance.

In high-speed converters, the output capacitor

Input Capacitor

bank is usually the most costly (and often the

The input capacitors are responsible for

largest) part of the circuit. The critical load

sourcing the AC component of the input current

parameters in choosing the output capacitors

flowing into the upper MOSFETs. Their RMS

are the maximum size of the load step, ΔI; the

current capacity must be sufficient to handle the

load-current slew rate, di/dt; and the maximum

AC component of the current drawn by the

allowable output voltage deviation under

upper MOSFETs which is related to duty cycle

transient loading, ΔVMAX. Capacitors are

and the number of active phases.

MP2932 Rev.1.02 www.MonolithicPower.com 17

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

Low capacitance, high-frequency ceramic

capacitors are needed in addition to the bulk

capacitors to suppress leading and falling edge

voltage spikes. Select low ESL ceramic

capacitors and place one as close as possible

to each upper MOSFET drain to minimize board

parasitic impedances and maximize

suppression.

PC Board Layout

For best performance of the MP2932, the

following guidelines should be strictly followed:

Within the allotted implementation area, place

the switching components first. Switching

component placement should take into account

power dissipation. Align the output inductors

and MOSFETs such that space between the

components is minimized while creating the

PHASE plane. If possible, duplicate the same

placement of these components for each phase.

Next, place the input and output capacitors.

Position one high frequency ceramic input

capacitor next to each upper MOSFET drain.

Place the input capacitors as close to the upper

MOSFET drains as dictated by the component

size and dimensions. Locate the output

capacitors between the inductors and the load,

while keeping them in close proximity to the

microprocessor socket.

MP2932 Rev.1.02 www.MonolithicPower.com 18

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

Table 2—VR10 ID Table (with 6.25mV Table 2—VR10 ID Table (with 6.25mV

Extension) Extension) continued

ID4 ID3 ID2 ID1 ID0 ID5 ID6 VOLTAGE ID4 ID3 ID2 ID1 ID0 ID5 ID6 VOLTAGE

400mV 200mV 100mV 50mV 25mV 12.5mV 6.25mV (V) 400mV 200mV 100mV 50mV 25mV 12.5mV 6.25mV (V)

0 1 0 1 0 1 1 1.60000 1 0 1 0 0 0 0 1.35625

0 1 0 1 0 1 0 1.59375 1 0 1 0 0 1 1 1.35000

0 1 0 1 1 0 1 1.58750 1 0 1 0 0 1 0 1.34375

0 1 0 1 1 0 0 1.58125 1 0 1 0 1 0 1 1.33750

0 1 0 1 1 1 1 1.57500 1 0 1 0 1 0 0 1.33125

0 1 0 1 1 1 0 1.56875 1 0 1 0 1 1 1 1.32500

0 1 1 0 0 0 1 1.56250 1 0 1 0 1 1 0 1.31875

0 1 1 0 0 0 0 1.55625 1 0 1 1 0 0 1 1.31250

0 1 1 0 0 1 1 1.55000 1 0 1 1 0 0 0 1.30625

0 1 1 0 0 1 0 1.54375 1 0 1 1 0 1 1 1.30000

0 1 1 0 1 0 1 1.53750 1 0 1 1 0 1 0 1.29375

0 1 1 0 1 0 0 1.53125 1 0 1 1 1 0 1 1.28750

0 1 1 0 1 1 1 1.52500 1 0 1 1 1 0 0 1.28125

0 1 1 0 1 1 0 1.51875 1 0 1 1 1 1 1 1.27500

0 1 1 1 0 0 1 1.51250 1 0 1 1 1 1 0 1.26875

0 1 1 1 0 0 0 1.50625 1 1 0 0 0 0 1 1.26250

0 1 1 1 0 1 1 1.50000 1 1 0 0 0 0 0 1.25625

0 1 1 1 0 1 0 1.49375 1 1 0 0 0 1 1 1.25000

0 1 1 1 1 0 1 1.4875 1 1 0 0 0 1 0 1.24375

0 1 1 1 1 0 0 1.48125 1 1 0 0 1 0 1 1.23750

0 1 1 1 1 1 1 1.47500 1 1 0 0 1 0 0 1.23125

0 1 1 1 1 1 0 1.46875 1 1 0 0 1 1 1 1.22500

1 0 0 0 0 0 1 1.46250 1 1 0 0 1 1 0 1.21875

1 0 0 0 0 0 0 1.45625 1 1 0 1 0 0 1 1.21250

1 0 0 0 0 1 1 1.45000 1 1 0 1 0 0 0 1.20625

1 0 0 0 0 1 0 1.44375 1 1 0 1 0 1 1 1.20000

1 0 0 0 1 0 1 1.43750 1 1 0 1 0 1 0 1.19375

1 0 0 0 1 0 0 1.43125 1 1 0 1 1 0 1 1.18750

1 0 0 0 1 1 1 1.42500 1 1 0 1 1 0 0 1.18125

1 0 0 0 1 1 0 1.41875 1 1 0 1 1 1 1 1.17500

1 0 0 1 0 0 1 1.41250 1 1 0 1 1 1 0 1.16875

1 0 0 1 0 0 0 1.40625 1 1 1 0 0 0 1 1.16250

1 0 0 1 0 1 1 1.40000 1 1 1 0 0 0 0 1.15625

1 0 0 1 0 1 0 1.39375 1 1 1 0 0 1 1 1.15000

1 0 0 1 1 0 1 1.38750 1 1 1 0 0 1 0 1.14375

1 0 0 1 1 0 0 1.38125 1 1 1 0 1 0 1 1.13750

1 0 0 1 1 1 1 1.37500 1 1 1 0 1 0 0 1.13125

1 0 0 1 1 1 0 1.36875 1 1 1 0 1 1 1 1.12500

1 0 1 0 0 0 1 1.36250 1 1 1 0 1 1 0 1.11875

MP2932 Rev.1.02 www.MonolithicPower.com 19

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

Table 2—VR10 ID Table (with 6.25mV Table 2—VR10 ID Table (with 6.25mV

Extension) continued Extension) continued

ID4 ID3 ID2 ID1 ID0 ID5 ID6 VOLTAGE ID4 ID3 ID2 ID1 ID0 ID5 ID6 VOLTAGE

400mV 200mV 100mV 50mV 25mV 12.5mV 6.25mV (V) 400mV 200mV 100mV 50mV 25mV 12.5mV 6.25mV (V)

1 1 1 1 0 0 1 1.11250 0 0 1 1 1 1 0 0.89375

1 1 1 1 0 0 0 1.10625 0 1 0 0 0 0 1 0.88750

1 1 1 1 0 1 1 1.10000 0 1 0 0 0 0 0 0.88125

1 1 1 1 0 1 0 1.09375 0 1 0 0 0 1 1 0.87500

1 1 1 1 1 0 1 OFF 0 1 0 0 0 1 0 0.86875

1 1 1 1 1 0 0 OFF 0 1 0 0 1 0 1 0.86250

1 1 1 1 1 1 1 OFF 0 1 0 0 1 0 0 0.85625

1 1 1 1 1 1 0 OFF 0 1 0 0 1 1 1 0.85000

0 0 0 0 0 0 1 1.08750 0 1 0 0 1 1 0 0.84375

0 0 0 0 0 0 0 1.08125 0 1 0 1 0 0 1 0.83750

0 0 0 0 0 1 1 1.07500 0 1 0 1 0 0 0 0.83125

0 0 0 0 0 1 0 1.06875

0 0 0 0 1 0 1 1.06250 Table 3—VR11 ID 8-BIT

0 0 0 0 1 0 0 1.05625

ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0 VOLTAGE

0 0 0 0 1 1 1 1.05000

0 0 0 0 0 0 0 0 OFF

0 0 0 0 1 1 0 1.04375

0 0 0 0 0 0 0 1 OFF

0 0 0 1 0 0 1 1.03750

0 0 0 0 0 0 1 0 1.60000

0 0 0 1 0 0 0 1.03125

0 0 0 0 0 0 1 1 1.59375

0 0 0 1 0 1 1 1.02500

0 0 0 0 0 1 0 0 1.58750

0 0 0 1 0 1 0 1.01875

0 0 0 0 0 1 0 1 1.58125

0 0 0 1 1 0 1 1.01250

0 0 0 0 0 1 1 0 1.57500

0 0 0 1 1 0 0 1.00625

0 0 0 0 0 1 1 1 1.56875

0 0 0 1 1 1 1 1.00000

0 0 0 0 1 0 0 0 1.56250

0 0 0 1 1 1 0 0.99375

0 0 0 0 1 0 0 1 1.55625

0 0 1 0 0 0 1 0.9875

0 0 0 0 1 0 1 0 1.55000

0 0 1 0 0 0 0 0.98125

0 0 0 0 1 0 1 1 1.54375

0 0 1 0 0 1 1 0.97500

0 0 0 0 1 1 0 0 1.53750

0 0 1 0 0 1 0 0.96875

0 0 0 0 1 1 0 1 1.53125

0 0 1 0 1 0 1 0.9625

0 0 0 0 1 1 1 0 1.52500

0 0 1 0 1 0 0 0.95625

0 0 0 0 1 1 1 1 1.51875

0 0 1 0 1 1 1 0.95000

0 0 1 0 1 1 0 0.94375 0 0 0 1 0 0 0 0 1.51250

0 0 1 1 0 0 1 0.93750 0 0 0 1 0 0 0 1 1.50625

0 0 1 1 0 0 0 0.93125 0 0 0 1 0 0 1 0 1.50000

0 0 1 1 0 1 1 0.92500 0 0 0 1 0 0 1 1 1.49375

0 0 1 1 0 1 0 0.91875 0 0 0 1 0 1 0 0 1.48750

0 0 1 1 1 0 1 0.91250 0 0 0 1 0 1 0 1 1.48125

0 0 1 1 1 0 0 0.90625 0 0 0 1 0 1 1 0 1.47500

0 0 1 1 1 1 1 0.90000

MP2932 Rev.1.02 www.MonolithicPower.com 20

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

Table 3—VR11 ID 8-BIT continued Table 3—VR11 ID 8-BIT continued

ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0 VOLTAGE ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0 VOLTAGE

0 0 0 1 0 1 1 1 1.46875 0 0 1 1 1 1 1 1 1.21875

0 0 0 1 1 0 0 0 1.46250 0 1 0 0 0 0 0 0 1.21250

0 0 0 1 1 0 0 1 1.45625 0 1 0 0 0 0 0 1 1.20625

0 0 0 1 1 0 1 0 1.45000 0 1 0 0 0 0 1 0 1.20000

0 0 0 1 1 0 1 1 1.44375 0 1 0 0 0 0 1 1 1.19375

0 0 0 1 1 1 0 0 1.43750 0 1 0 0 0 1 0 0 1.18750

0 0 0 1 1 1 0 1 1.43125 0 1 0 0 0 1 0 1 1.18125

0 0 0 1 1 1 1 0 1.42500 0 1 0 0 0 1 1 0 1.17500

0 0 0 1 1 1 1 1 1.41875 0 1 0 0 0 1 1 1 1.16875

0 0 1 0 0 0 0 0 1.41250 0 1 0 0 1 0 0 0 1.16250

0 0 1 0 0 0 0 1 1.40625 0 1 0 0 1 0 0 1 1.15625

0 0 1 0 0 0 1 0 1.40000 0 1 0 0 1 0 1 0 1.15000

0 0 1 0 0 0 1 1 1.39375 0 1 0 0 1 0 1 1 1.14375

0 0 1 0 0 1 0 0 1.38750 0 1 0 0 1 1 0 0 1.13750

0 0 1 0 0 1 0 1 1.38125 0 1 0 0 1 1 0 1 1.13125

0 0 1 0 0 1 1 0 1.37500 0 1 0 0 1 1 1 0 1.12500

0 0 1 0 0 1 1 1 1.36875 0 1 0 0 1 1 1 1 1.11875

0 0 1 0 1 0 0 0 1.36250 0 1 0 1 0 0 0 0 1.11250

0 0 1 0 1 0 0 1 1.35625 0 1 0 1 0 0 0 1 1.10625

0 0 1 0 1 0 1 0 1.35000 0 1 0 1 0 0 1 0 1.10000

0 0 1 0 1 0 1 1 1.34375 0 1 0 1 0 0 1 1 1.09375

0 0 1 0 1 1 0 0 1.33750 0 1 0 1 0 1 0 0 1.08750

0 0 1 0 1 1 0 1 1.33125 0 1 0 1 0 1 0 1 1.08125

0 0 1 0 1 1 1 0 1.32500 0 1 0 1 0 1 1 0 1.07500

0 0 1 0 1 1 1 1 1.31875 0 1 0 1 0 1 1 1 1.06875

0 0 1 1 0 0 0 0 1.31250 0 1 0 1 1 0 0 0 1.06250

0 0 1 1 0 0 0 1 1.30625 0 1 0 1 1 0 0 1 1.05625

0 0 1 1 0 0 1 0 1.30000 0 1 0 1 1 0 1 0 1.05000

0 0 1 1 0 0 1 1 1.29375 0 1 0 1 1 0 1 1 1.04375

0 0 1 1 0 1 0 0 1.28750 0 1 0 1 1 1 0 0 1.03750

0 0 1 1 0 1 0 1 1.28125 0 1 0 1 1 1 0 1 1.03125

0 0 1 1 0 1 1 0 1.27500 0 1 0 1 1 1 1 0 1.02500

0 0 1 1 0 1 1 1 1.26875 0 1 0 1 1 1 1 1 1.01875

0 0 1 1 1 0 0 0 1.26250 0 1 1 0 0 0 0 0 1.01250

0 0 1 1 1 0 0 1 1.25625 0 1 1 0 0 0 0 1 1.00625

0 0 1 1 1 0 1 0 1.25000 0 1 1 0 0 0 1 0 1.00000

0 0 1 1 1 0 1 1 1.24375 0 1 1 0 0 0 1 1 0.99375

0 0 1 1 1 1 0 0 1.23750 0 1 1 0 0 1 0 0 0.98750

0 0 1 1 1 1 0 1 1.23125 0 1 1 0 0 1 0 1 0.98125

0 0 1 1 1 1 1 0 1.22500

MP2932 Rev.1.02 www.MonolithicPower.com 21

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

Table 3—VR11 ID 8-BIT continued Table 3—VR11 ID 8-BIT continued

ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0 VOLTAGE ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0 VOLTAGE

0 1 1 0 0 1 1 0 0.97500 1 0 0 0 1 1 1 0 0.72500

0 1 1 0 0 1 1 1 0.96875 1 0 0 0 1 1 1 1 0.71875

0 1 1 0 1 0 0 0 0.96250 1 0 0 1 0 0 0 0 0.71250

0 1 1 0 1 0 0 1 0.95625 1 0 0 1 0 0 0 1 0.70625

0 1 1 0 1 0 1 0 0.95000 1 0 0 1 0 0 1 0 0.70000

0 1 1 0 1 0 1 1 0.94375 1 0 0 1 0 0 1 1 0.69375

0 1 1 0 1 1 0 0 0.93750 1 0 0 1 0 1 0 0 0.68750

0 1 1 0 1 1 0 1 0.93125 1 0 0 1 0 1 0 1 0.68125

0 1 1 0 1 1 1 0 0.92500 1 0 0 1 0 1 1 0 0.67500

0 1 1 0 1 1 1 1 0.91875 1 0 0 1 0 1 1 1 0.66875

0 1 1 1 0 0 0 0 0.91250 1 0 0 1 1 0 0 0 0.66250

0 1 1 1 0 0 0 1 0.90625 1 0 0 1 1 0 0 1 0.65625

0 1 1 1 0 0 1 0 0.90000 1 0 0 1 1 0 1 0 0.65000

0 1 1 1 0 0 1 1 0.89375 1 0 0 1 1 0 1 1 0.64375

0 1 1 1 0 1 0 0 0.88750 1 0 0 1 1 1 0 0 0.63750

0 1 1 1 0 1 0 1 0.88125 1 0 0 1 1 1 0 1 0.63125

0 1 1 1 0 1 1 0 0.87500 1 0 0 1 1 1 1 0 0.62500

0 1 1 1 0 1 1 1 0.86875 1 0 0 1 1 1 1 1 0.61875

0 1 1 1 1 0 0 0 0.86250 1 0 1 0 0 0 0 0 0.61250

0 1 1 1 1 0 0 1 0.85625 1 0 1 0 0 0 0 1 0.60625

0 1 1 1 1 0 1 0 0.85000 1 0 1 0 0 0 1 0 0.60000

0 1 1 1 1 0 1 1 0.84375 1 0 1 0 0 0 1 1 0.59375

0 1 1 1 1 1 0 0 0.83750 1 0 1 0 0 1 0 0 0.58750

0 1 1 1 1 1 0 1 0.83125 1 0 1 0 0 1 0 1 0.58125

0 1 1 1 1 1 1 0 0.82500 1 0 1 0 0 1 1 0 0.57500

0 1 1 1 1 1 1 1 0.81875 1 0 1 0 0 1 1 1 0.56875

1 0 0 0 0 0 0 0 0.81250 1 0 1 0 1 0 0 0 0.56250

1 0 0 0 0 0 0 1 0.80625 1 0 1 0 1 0 0 1 0.55625

1 0 0 0 0 0 1 0 0.80000 1 0 1 0 1 0 1 0 0.55000

1 0 0 0 0 0 1 1 0.79375 1 0 1 0 1 0 1 1 0.54375

1 0 0 0 0 1 0 0 0.78750 1 0 1 0 1 1 0 0 0.53750

1 0 0 0 0 1 0 1 0.78125 1 0 1 0 1 1 0 1 0.53125

1 0 0 0 0 1 1 0 0.77500 1 0 1 0 1 1 1 0 0.52500

1 0 0 0 0 1 1 1 0.76875 1 0 1 0 1 1 1 1 0.51875

1 0 0 0 1 0 0 0 0.76250 1 0 1 1 0 0 0 0 0.51250

1 0 0 0 1 0 0 1 0.75625 1 0 1 1 0 0 0 1 0.50625

1 0 0 0 1 0 1 0 0.75000 1 0 1 1 0 0 1 0 0.50000

1 0 0 0 1 0 1 1 0.74375 1 1 1 1 1 1 1 0 OFF

1 0 0 0 1 1 0 0 0.73750 1 1 1 1 1 1 1 1 OFF

1 0 0 0 1 1 0 1 0.73125

MP2932 Rev.1.02 www.MonolithicPower.com 22

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

MP2932 - 6-PHASE PWM CONTROLLER WITH 8-BIT ADC CODE

PACKAGE INFORMATION

QFN48 (6 x 6mm)

5.90 4.50

6.10 4.70

37 48 PIN 1 ID

PIN 1 ID SEE DETAIL A

MARKING

36 1

0.40

BSC

PIN 1 ID 5.90 4.50

INDEX AREA 6.10 4.70

0.15

0.25

25 12

24 13

0.35

0.45

TOP VIEW BOTTOM VIEW

PIN 1 ID OPTION A PIN 1 ID OPTION B

0.30x45º TYP. R0.25 TYP.

0.80

1.00

0.20 REF

0.00

0.05

SIDE VIEW DETAIL A

5.90 NOTE:

4.60

1) ALL DIMENSIONS ARE IN MILLIMETERS.

0.70 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

0.20 4) DRAWING CONFORMS TO JEDEC MO-220, VARIATION VJJE-1.

5) DRAWING IS NOT TO SCALE.

0.40

RECOMMENDED LAND PATTERN

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third

party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not

assume any legal responsibility for any said applications.

MP2932 Rev. 1.02 www.MonolithicPower.com 23

4/30/2012 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

Potrebbero piacerti anche

- Infineon ILD2111 DS v01 - 00 ENDocumento66 pagineInfineon ILD2111 DS v01 - 00 ENИван КумбровNessuna valutazione finora

- Features: Digital Dual Output 7-Phase AMD PWM ControllerDocumento3 pagineFeatures: Digital Dual Output 7-Phase AMD PWM ControllertututNessuna valutazione finora

- AP8269 AiTSemiconductorDocumento11 pagineAP8269 AiTSemiconductorAlexandre Marido de AluguelNessuna valutazione finora

- A6211 Datasheet PDFDocumento18 pagineA6211 Datasheet PDFNestor GlezNessuna valutazione finora

- XT2063Documento8 pagineXT2063betty delaNessuna valutazione finora

- Data Sheet: Beyond Innovation Technology Co., LTDDocumento6 pagineData Sheet: Beyond Innovation Technology Co., LTDOlivier OuinaNessuna valutazione finora

- Data SheetDocumento1 paginaData Sheetcelestino secundinoNessuna valutazione finora

- Bit 3260Documento1 paginaBit 3260Iader Salgado100% (1)

- Bit3260 PDFDocumento1 paginaBit3260 PDFSteven Orozco100% (1)

- Read/Write Base Station U2270B: FeaturesDocumento18 pagineRead/Write Base Station U2270B: FeaturesJuan CarlosNessuna valutazione finora

- Training Material of MS09A and MS09L ChassisDocumento47 pagineTraining Material of MS09A and MS09L Chassisبوند بوندNessuna valutazione finora

- Embedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorDocumento9 pagineEmbedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorHILLNessuna valutazione finora

- Multi-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocumento24 pagineMulti-Phase PWM Controller With PWM-VID Reference: General Description FeaturesSurendra SharmaNessuna valutazione finora

- Advance Reparining by Gaurav - PPSXDocumento7 pagineAdvance Reparining by Gaurav - PPSXMamaZote TechNessuna valutazione finora

- RT8800APQV Datasheet (PDF) Download - Richtek Technology CorporationDocumento21 pagineRT8800APQV Datasheet (PDF) Download - Richtek Technology Corporationlucas sousaNessuna valutazione finora

- CY320 Product InfoDocumento6 pagineCY320 Product InfoRogério MorenoNessuna valutazione finora

- Ds3607ce 00 PDFDocumento69 pagineDs3607ce 00 PDFZezo FrpNessuna valutazione finora

- Datasheet Isl6262Documento27 pagineDatasheet Isl6262Jhones CAMNessuna valutazione finora

- ISL6324 Hybrid SVI/PVI With I C: FeaturesDocumento38 pagineISL6324 Hybrid SVI/PVI With I C: FeaturesDavid J. Pinto ApazaNessuna valutazione finora

- UP6281 uPISemiconductorDocumento10 pagineUP6281 uPISemiconductorВячеслав ЗагвоцкийNessuna valutazione finora

- Single-Slot Pcmcia/Cardbus Power Controllers: Global Mixed-Mode Technology IncDocumento11 pagineSingle-Slot Pcmcia/Cardbus Power Controllers: Global Mixed-Mode Technology Incnik56vNessuna valutazione finora

- AP8263Documento10 pagineAP8263SamerNessuna valutazione finora

- Driver Backlight PSP 2000Documento12 pagineDriver Backlight PSP 2000Jhonny GuillermoNessuna valutazione finora

- Bd9423efv e 1223519 PDFDocumento61 pagineBd9423efv e 1223519 PDFVươngNessuna valutazione finora

- BD9423EFVDocumento61 pagineBD9423EFVIoan TivgaNessuna valutazione finora

- Designing The VEML6070 UV Light Sensor Into Applications: Optical SensorsDocumento14 pagineDesigning The VEML6070 UV Light Sensor Into Applications: Optical SensorsLjubisa DjordjevicNessuna valutazione finora

- 2.7V-To-15V, 700ma, Bipolar Stepper-Motor Driver With Integrated MosfetsDocumento18 pagine2.7V-To-15V, 700ma, Bipolar Stepper-Motor Driver With Integrated MosfetsAna Flavia KohlrauchNessuna valutazione finora

- Ic Driver LCD HP G5121 5121M PDFDocumento9 pagineIc Driver LCD HP G5121 5121M PDFBudi PrayitnoNessuna valutazione finora

- A4960 A Automotive DatasheetDocumento34 pagineA4960 A Automotive DatasheetCanerNessuna valutazione finora

- DP9127V DPDocumento11 pagineDP9127V DPGustavo AlonsoNessuna valutazione finora

- Switched Capacitor Voltage Converter With Regulated Output ADP3604Documento8 pagineSwitched Capacitor Voltage Converter With Regulated Output ADP3604Luís GuerreiroNessuna valutazione finora

- Sensorless BLDC Controller A4960: Description Features and BenefitsDocumento34 pagineSensorless BLDC Controller A4960: Description Features and BenefitsadilNessuna valutazione finora

- MP28167GQ ADocumento32 pagineMP28167GQ AHamouda MahmodNessuna valutazione finora

- CR6842 ChipRail PDFDocumento9 pagineCR6842 ChipRail PDFAlvaro Salazar RiveraNessuna valutazione finora

- RT3661AB-RichTek Sau AS3661AB PDFDocumento36 pagineRT3661AB-RichTek Sau AS3661AB PDFeduardskNessuna valutazione finora

- Redboard (Dev-12757) : ISP HeaderDocumento1 paginaRedboard (Dev-12757) : ISP HeaderVengatesh VelusamyNessuna valutazione finora

- Multi-Phase DC/DC Controller For CPU Core Power Supply: General Description FeaturesDocumento14 pagineMulti-Phase DC/DC Controller For CPU Core Power Supply: General Description FeaturesTeles SilvaNessuna valutazione finora

- PixArt PMW3310DH PDFDocumento41 paginePixArt PMW3310DH PDFfooobarNessuna valutazione finora

- 152 01246 0 RX 8025NBDocumento2 pagine152 01246 0 RX 8025NBkolesikNessuna valutazione finora

- NCP5395TDocumento25 pagineNCP5395Tterry panNessuna valutazione finora

- gm07652r PDFDocumento21 paginegm07652r PDFjose luisNessuna valutazione finora

- Datasheet DMO565RDocumento21 pagineDatasheet DMO565RSteve Bravo83% (6)

- ISL6263C IntersilDocumento18 pagineISL6263C IntersilCer CerNessuna valutazione finora

- High Voltage Ignition Coil Driver Power I.C.: VB027BSPDocumento8 pagineHigh Voltage Ignition Coil Driver Power I.C.: VB027BSPedinson corzoNessuna valutazione finora

- Ait Semiconductor Inc.: Description FeaturesDocumento11 pagineAit Semiconductor Inc.: Description FeaturesSamerNessuna valutazione finora

- MST9220B: General Description FeaturesDocumento8 pagineMST9220B: General Description FeaturespepenitoNessuna valutazione finora

- Hx712 English Datasheet PDFDocumento9 pagineHx712 English Datasheet PDFkibriaNessuna valutazione finora

- TB6641FG ToshibaDocumento23 pagineTB6641FG ToshibalucianassisNessuna valutazione finora

- Data Sheet: APDS-9500Documento37 pagineData Sheet: APDS-9500anasNessuna valutazione finora

- Ds3602ac 01Documento49 pagineDs3602ac 01Charles PNessuna valutazione finora

- TB67H400AHG: PWM Chopper-TypeDocumento23 pagineTB67H400AHG: PWM Chopper-Typegeneric111Nessuna valutazione finora

- Map3511 828Documento14 pagineMap3511 828riyad abdulhafeedNessuna valutazione finora

- Dual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocumento21 pagineDual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesДмитрий НичипоровичNessuna valutazione finora

- DS8816ADocumento21 pagineDS8816AAgustin AyalaNessuna valutazione finora

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocumento21 pagineRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85Nessuna valutazione finora

- F405-WTE Manual PDFDocumento5 pagineF405-WTE Manual PDFBlockFace08Nessuna valutazione finora

- Features: Two-Phase Core Controller For Amd Mobile Turion CpusDocumento23 pagineFeatures: Two-Phase Core Controller For Amd Mobile Turion CpusSanthosh SanthuNessuna valutazione finora

- MT7860 MaxicTechnologyDocumento7 pagineMT7860 MaxicTechnologySatishNessuna valutazione finora

- Gate Drive Design For Large Mosfet Apt9302Documento10 pagineGate Drive Design For Large Mosfet Apt9302Grzegorz WegnerNessuna valutazione finora

- Switches and Universal Amplifiers: DescriptionDocumento5 pagineSwitches and Universal Amplifiers: DescriptionKiss IstvánNessuna valutazione finora

- DMC M3 AssignmentDocumento14 pagineDMC M3 AssignmentHannanNessuna valutazione finora

- Lecture 1 - Mesh and Nodal AnalysisDocumento50 pagineLecture 1 - Mesh and Nodal AnalysisCindy KoechNessuna valutazione finora

- Section 1 Simple Circuits: Practice Problems: SolutionDocumento5 pagineSection 1 Simple Circuits: Practice Problems: SolutionGULOED Jama JosopHNessuna valutazione finora

- RF CMOS Comes of AgeDocumento13 pagineRF CMOS Comes of AgechenlunNessuna valutazione finora

- Inductor SimulatorDocumento17 pagineInductor SimulatorwindfocusNessuna valutazione finora

- Adc PDFDocumento18 pagineAdc PDFAshfaaq OchatoyaNessuna valutazione finora

- Assignment #1Documento46 pagineAssignment #1Héctor Manuel Rodríguez FelicianoNessuna valutazione finora

- View Answer Discuss in Forum Workspace View Answer Discuss in Forum WorkspaceDocumento18 pagineView Answer Discuss in Forum Workspace View Answer Discuss in Forum WorkspaceEj ParañalNessuna valutazione finora

- Notch Filter LMF90 - DS010354Documento23 pagineNotch Filter LMF90 - DS010354Asbah AshfaqNessuna valutazione finora

- Mixer Design Overview: Q Q Q QDocumento39 pagineMixer Design Overview: Q Q Q Qayal gezeNessuna valutazione finora

- Hoja Caracteristicas 7474 PDFDocumento6 pagineHoja Caracteristicas 7474 PDFArun UpadhyayaNessuna valutazione finora

- AC Phase ControlDocumento6 pagineAC Phase ControlRaymond HartonoNessuna valutazione finora

- Laboratory 6 - VCODocumento2 pagineLaboratory 6 - VCOAriana Ribeiro LameirinhasNessuna valutazione finora

- Basic Digital Electronics - Unit 1Documento12 pagineBasic Digital Electronics - Unit 1Soni Mishra TiwariNessuna valutazione finora

- Chapter06-2UP (4 23 02)Documento79 pagineChapter06-2UP (4 23 02)Nelor Jane Robles LagunaNessuna valutazione finora

- Graphic EqualizerDocumento19 pagineGraphic Equalizerpapagiano35100% (1)

- AN8806SB: Three-Beam Method Head Amplifier IC For CD PlayerDocumento10 pagineAN8806SB: Three-Beam Method Head Amplifier IC For CD PlayeraldoNessuna valutazione finora

- Current Dumping Audio Amplifier A EN2 920 QUADocumento3 pagineCurrent Dumping Audio Amplifier A EN2 920 QUAdodifirmanNessuna valutazione finora

- Lab Session 02 Nand - Nor Gates: ObjectiveDocumento6 pagineLab Session 02 Nand - Nor Gates: ObjectiveAnb BajwaNessuna valutazione finora

- Sem1 1314 SolutionDocumento16 pagineSem1 1314 SolutionThinesh StNessuna valutazione finora

- Bike Turning Signal Indicator Circuit Using 555 TimerDocumento7 pagineBike Turning Signal Indicator Circuit Using 555 Timerkaarthik KNessuna valutazione finora

- Ilicore: 14W Hi-Fi Audio Amplifier D2030Documento5 pagineIlicore: 14W Hi-Fi Audio Amplifier D2030Mirna Consuelo BuezoNessuna valutazione finora

- 70 Interesting CircuitsDocumento21 pagine70 Interesting CircuitsHasitha Suneth100% (4)

- WWW Rapidtables ComDocumento7 pagineWWW Rapidtables ComIttyNessuna valutazione finora

- Matlab Program: 1 Response of First Order System To Unit Step InputDocumento6 pagineMatlab Program: 1 Response of First Order System To Unit Step InputMartin De Boras PragashNessuna valutazione finora

- Study of Flip Flops Using ICsDocumento5 pagineStudy of Flip Flops Using ICssaravanan_12aNessuna valutazione finora

- 546a2 Usb Power MagnagementDocumento1 pagina546a2 Usb Power MagnagementJavierNessuna valutazione finora