Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Examen Parcial 2017-1 - DISEÑO DIGITAL - FIEE - UNMSM

Caricato da

Elmer525Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Examen Parcial 2017-1 - DISEÑO DIGITAL - FIEE - UNMSM

Caricato da

Elmer525Copyright:

Formati disponibili

UNIVERSIDAD NACIONAL MAYOR DE

SAN MARCOSCiclo Académico 2017 - I

FACULTAD DE INGENIERÍA

ELÉCTRONICA Y ELECTRICA

Fecha: 06-06-2017

ESCUELAS ACADEMICO

PROFESIONALES Duración:

2 Horas

CURSO: ________DISEÑO

DIGITAL__________________________________

COD. CURSO:

TIPO DE PRUEBA: PRACTICA No. Ex.

PARCIAL X EX. FINAL

EX. SUST.

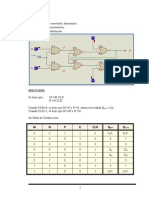

PREGUNTA 1: Implemente el circuito que genere la siguiente señal de salida (5 puntos):

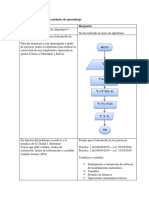

PREGUNTA 2: Implementar el siguiente contador (5 puntos):

◦ La señal MIN sirve para establecer el valor inicial (si no se activa por defecto es 0).

◦ La señal MAX sirve para establecer el valor final (si no se activa por defecto es F).

◦ La entrada A (4 bits) determina el valor inicial sólo cuando se activa MIN.

◦ La entrada B (4 bits) determina el valor final sólo cuando se activa MAX.

PREGUNTA 3: Implementar el siguiente circuito en VHDL (6 puntos):

Cuando no se presiona ningún botón (las entradas por defecto son 0s) deben estar apagados los 4

display. Cuando se presiona HALT se muestra en los display (mientras se mantenga pulsado). Lo mismo

pasa con las otras entradas. La entrada con mayor prioridad es HALT y la de menor es FULL.

PREGUNTA 4: (4 puntos) Implementar un comparador de dos números de 4 bits teniendo en cuenta el

bit de signo. Las salidas de este circuito debe indicar si:

• MAY = 1 si (A > B).

• IGUAL = 1 si (A = B).

• MEN = 1 ( A < B).

EL PROFESOR

Solucion No1:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity pregunta1 is

port(clk : in std_logic;

z: out std_logic);

end pregunta1;

architecture solucion of pregunta1 is

signal contador: std_logic_vector(3 downto 0);

begin

process(clk)

begin

if rising_edge(clk) then

contador <= contador + 1;

if contador = 13 then

contador <= (others=>'0');

end if;

end if;

end process;

z <= '0' when contador=4 else

'0' when contador=8 else

'0' when contador=11 else

'0' when contador=13 else '1';

end solucion;

Solucion No2:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity pregunta2 is

port(clk,min,max: in std_logic;

A,B: in std_logic_vector(3 downto 0);

Q: out std_logic_vector(3 downto 0));

end pregunta2;

architecture solucion of pregunta2 is

begin

process(clk)

variable CONTADOR,MINIMO,MAXIMO:

std_logic_vector(3 downto 0);

begin

if rising_edge(clk) then

if min = '1' then

MINIMO := A;

end if;

if max = '1' then

MAXIMO := B+1;

end if;

CONTADOR := CONTADOR + 1;

if CONTADOR = MAXIMO then

CONTADOR := MINIMO;

end if;

end if;

Q <= CONTADOR;

end process;

end solucion;

Solucion No3:

Potrebbero piacerti anche

- TPSC 2Documento23 pagineTPSC 2javirv19Nessuna valutazione finora

- Pr3 - Radio - Pérdidas y GananciasDocumento8 paginePr3 - Radio - Pérdidas y Gananciaspastor17bnlNessuna valutazione finora

- Realización Del Sistema de Control de Temperatura y HumedadDocumento6 pagineRealización Del Sistema de Control de Temperatura y HumedadJose CordobaNessuna valutazione finora

- Informefinal 5 Sistemas Digitales Ee635Documento15 pagineInformefinal 5 Sistemas Digitales Ee635juan ramos ruizNessuna valutazione finora

- Etn-506 Circuito RLC Axl Aparicio PDFDocumento7 pagineEtn-506 Circuito RLC Axl Aparicio PDFaxlhellfish666Nessuna valutazione finora

- Informe 3Documento4 pagineInforme 3Michael JiménezNessuna valutazione finora

- 2019-1 PC1Documento3 pagine2019-1 PC1Javier CruzNessuna valutazione finora

- Lab Nº3 - Corte y Saturación - 2011-IDocumento2 pagineLab Nº3 - Corte y Saturación - 2011-IBruno Adolfo Castillo SoteloNessuna valutazione finora

- Astables y Monostables-Informe Final 2Documento13 pagineAstables y Monostables-Informe Final 2Michael AlexanderNessuna valutazione finora

- LAB 6 - Análisis y Síntesis de Circuitos Lógicos Secuenciales (Prof. Casimiro)Documento3 pagineLAB 6 - Análisis y Síntesis de Circuitos Lógicos Secuenciales (Prof. Casimiro)Elmer525Nessuna valutazione finora

- Acitividad 1 DecibelesDocumento3 pagineAcitividad 1 DecibelesForbiddenLove PeñaNessuna valutazione finora

- Mmparte11 PDFDocumento12 pagineMmparte11 PDFJano Jesus AlexNessuna valutazione finora

- Guia Practica 1Documento5 pagineGuia Practica 1Jorge Luis HuaracaNessuna valutazione finora

- Diseño de Amplificadores de Una Etapa BJTDocumento21 pagineDiseño de Amplificadores de Una Etapa BJTPablo Jiménez MendizábalNessuna valutazione finora

- Mapa P10Documento2 pagineMapa P10Jose Luis PalemonteNessuna valutazione finora

- MonografiaDocumento30 pagineMonografiaxxzagaxxNessuna valutazione finora

- Problemas Diseño Combinacionales PDFDocumento7 pagineProblemas Diseño Combinacionales PDFXiomaraNessuna valutazione finora

- LAB 2 y 3 FinalDocumento15 pagineLAB 2 y 3 FinalJuan Jose Ravichagua Quintana100% (2)

- Circuitos de Radio ComunicacionDocumento21 pagineCircuitos de Radio ComunicacionDaniel Nunuraj0% (1)

- Proyecto - Transmisor - Receptor FMDocumento60 pagineProyecto - Transmisor - Receptor FMBleymar Quinteroz LauraNessuna valutazione finora

- Transistor Como OsciladorDocumento4 pagineTransistor Como OsciladorFermin FerminNessuna valutazione finora

- Formulario Formularios Examen BJT 3Documento1 paginaFormulario Formularios Examen BJT 3Christopher QuirósNessuna valutazione finora

- Solucionario Parcial 2005 2Documento7 pagineSolucionario Parcial 2005 2andlu666Nessuna valutazione finora

- Informe de Circuitos Electricos 1Documento5 pagineInforme de Circuitos Electricos 1Paul Angelo RomeroNessuna valutazione finora

- Dispositivos Electronicos - Laboratorio Nº2Documento16 pagineDispositivos Electronicos - Laboratorio Nº2James Rojas RomeroNessuna valutazione finora

- Lab 6 - Respuesta en Frecuencia de AmplificadoreDocumento12 pagineLab 6 - Respuesta en Frecuencia de Amplificadorev_kathyNessuna valutazione finora

- Lab2 Informe Previo Alta TensionDocumento7 pagineLab2 Informe Previo Alta TensionLuis SulcaNessuna valutazione finora

- Propagación en El Espacio LibreDocumento5 paginePropagación en El Espacio LibreAlexNzNessuna valutazione finora

- 212 EE498M Previo2 GuerreroGruberDocumento6 pagine212 EE498M Previo2 GuerreroGruberjuan ramos ruizNessuna valutazione finora

- Labo Cel 200Documento4 pagineLabo Cel 200Danna MarcaNessuna valutazione finora

- PC MicroelectronicaDocumento2 paginePC MicroelectronicaERNESTO ALBERTO LOPEZ QUISPENessuna valutazione finora

- Pasos para Conversion Con InterrupcionDocumento6 paginePasos para Conversion Con Interrupcionfede_sobNessuna valutazione finora

- Pdi 17-18 2Documento92 paginePdi 17-18 2Alejandro MarínNessuna valutazione finora

- T11-OpAmp Diferencial y en Modo ComunDocumento57 pagineT11-OpAmp Diferencial y en Modo ComunEnrique Villegas MedinaNessuna valutazione finora

- Electricidad Industrial p1Documento14 pagineElectricidad Industrial p1FMNessuna valutazione finora

- Humanidades V Politecnico Primer Bloque Agosto 2019Documento17 pagineHumanidades V Politecnico Primer Bloque Agosto 2019Diana Bruja GorgonaNessuna valutazione finora

- Examen Parcial de Circuitos Digitales 11190219Documento6 pagineExamen Parcial de Circuitos Digitales 11190219Simón Criastobal Elvis FrankNessuna valutazione finora

- Examenes Eleindo Primera Unidad KokytronicDocumento22 pagineExamenes Eleindo Primera Unidad KokytronicJoao Jesus Alberto Haro TantajulcaNessuna valutazione finora

- Laboratorio MicroelectronicaDocumento2 pagineLaboratorio Microelectronicaageha28Nessuna valutazione finora

- Tarea de Electromagnetismo I (Ee 522 P)Documento2 pagineTarea de Electromagnetismo I (Ee 522 P)Junior Espinoza EspirituNessuna valutazione finora

- Diseño Curricular de Técnico en ElectronicaDocumento91 pagineDiseño Curricular de Técnico en ElectronicaAlejandroMaxRomeroNessuna valutazione finora

- FinalDocumento9 pagineFinaldennisNessuna valutazione finora

- 2012-II Dispositivos Electronicos SDocumento2 pagine2012-II Dispositivos Electronicos SJose JaureguiNessuna valutazione finora

- Cuestionario 2Documento9 pagineCuestionario 2AntonioLinkEzeroNessuna valutazione finora

- C2 Senales Espectros PDFDocumento60 pagineC2 Senales Espectros PDFzulainyNessuna valutazione finora

- Formato Informe FinalDocumento3 pagineFormato Informe FinalMarco Manuel Marca CastilloNessuna valutazione finora

- ValladaresSantiagoOM MFI TES2Documento6 pagineValladaresSantiagoOM MFI TES2ValladaresSantiagoOmarNessuna valutazione finora

- Circuitos DigitalesDocumento58 pagineCircuitos DigitalesRubén PerézNessuna valutazione finora

- Practica 2 PDFDocumento4 paginePractica 2 PDFmigue alejandroNessuna valutazione finora

- Practica Teoria de Telecomunicaciones IiDocumento5 paginePractica Teoria de Telecomunicaciones Iiroger macias marcaNessuna valutazione finora

- Ejercicios Memorias Diseño DigitalDocumento11 pagineEjercicios Memorias Diseño DigitalAlba ChaparroNessuna valutazione finora

- Lab4 Ee604 - Fiee UniDocumento2 pagineLab4 Ee604 - Fiee UniDavidNessuna valutazione finora

- Analizador de Espectro Informe 01 VallejosDocumento13 pagineAnalizador de Espectro Informe 01 VallejosAngelGuerreroNessuna valutazione finora

- P1 - Ee637n - 2020-1 PDFDocumento2 pagineP1 - Ee637n - 2020-1 PDFEDUARDO DOMINGO MARAÑON AGUILARNessuna valutazione finora

- EXTEMAIIrlc 4Documento70 pagineEXTEMAIIrlc 4Jefry CordovaNessuna valutazione finora

- Práctica #5. Figuras de LissajousDocumento9 paginePráctica #5. Figuras de LissajousMiguelangel ReymyNessuna valutazione finora

- Lab 2Documento18 pagineLab 2Ale RQNessuna valutazione finora

- Amplificador Emisor Comun Aquino Mamani Jose AlvaroDocumento27 pagineAmplificador Emisor Comun Aquino Mamani Jose AlvaroJose Alvaro Aquino MamaniNessuna valutazione finora

- Práctica3 VLSIDocumento8 paginePráctica3 VLSIMaximiliano Quiñones ReyesNessuna valutazione finora

- Practica1 DesarrolloDocumento16 paginePractica1 DesarrolloDanielEscalonaNessuna valutazione finora

- MATPEL 1 ReconocimientoDocumento1 paginaMATPEL 1 ReconocimientoElmer525Nessuna valutazione finora

- Laboratorio Calificado N°2 - Viernes 24/05/19 - AdanaqueDocumento2 pagineLaboratorio Calificado N°2 - Viernes 24/05/19 - AdanaqueElmer525Nessuna valutazione finora

- MATPEL 2 IdentificaciónDocumento1 paginaMATPEL 2 IdentificaciónElmer525Nessuna valutazione finora

- Tarea Academica - Simulacion de Sistemas - Upc PDFDocumento4 pagineTarea Academica - Simulacion de Sistemas - Upc PDFElmer525Nessuna valutazione finora

- Estudio de La Tecnología de Comunicación Por Radiofrecuencia RFID y Su ImplementaciónDocumento110 pagineEstudio de La Tecnología de Comunicación Por Radiofrecuencia RFID y Su ImplementaciónElmer525Nessuna valutazione finora

- Control de Velocidad de Un Motor DC Con DacDocumento9 pagineControl de Velocidad de Un Motor DC Con DacElmer525100% (1)

- Informe #1 - Lab. Introducción A Las TelecomunicacionesDocumento22 pagineInforme #1 - Lab. Introducción A Las TelecomunicacionesElmer525Nessuna valutazione finora

- Modelos de Organización Del Sector ElectricoDocumento5 pagineModelos de Organización Del Sector ElectricoElmer525Nessuna valutazione finora

- Tema1 Circuitos Temporizadores 74121 74122 74123Documento21 pagineTema1 Circuitos Temporizadores 74121 74122 74123Julio David Vilca PizarroNessuna valutazione finora

- Sistemas Digitales Problemas 2 PDFDocumento27 pagineSistemas Digitales Problemas 2 PDFElmer525Nessuna valutazione finora

- LAB 8 - Circuitos de Conversión ADC y DAC PDFDocumento2 pagineLAB 8 - Circuitos de Conversión ADC y DAC PDFElmer525Nessuna valutazione finora

- Los Microcontroladores en La IndustriaDocumento5 pagineLos Microcontroladores en La IndustriaElmer525Nessuna valutazione finora

- LAB 5 - Análisis y Diseño de Circuitos Secuenciales Modelos Tipo Moore y Tipo Mealy (Prof. Casimiro)Documento2 pagineLAB 5 - Análisis y Diseño de Circuitos Secuenciales Modelos Tipo Moore y Tipo Mealy (Prof. Casimiro)Elmer525100% (1)

- LAB 7 - Análisis Circuitos Lógicos Secuenciales (Prof. Casimiro)Documento2 pagineLAB 7 - Análisis Circuitos Lógicos Secuenciales (Prof. Casimiro)Elmer525Nessuna valutazione finora

- Tema1 Circuitos Temporizadores 74121 74122 74123Documento21 pagineTema1 Circuitos Temporizadores 74121 74122 74123Julio David Vilca PizarroNessuna valutazione finora

- LAB 8 - Circuitos de Conversión ADC y DAC PDFDocumento2 pagineLAB 8 - Circuitos de Conversión ADC y DAC PDFElmer525Nessuna valutazione finora

- LAB 7 - Análisis Circuitos Lógicos Secuenciales (Prof. Casimiro)Documento2 pagineLAB 7 - Análisis Circuitos Lógicos Secuenciales (Prof. Casimiro)Elmer525Nessuna valutazione finora

- LAB 6 - Análisis y Síntesis de Circuitos Lógicos Secuenciales (Prof. Casimiro)Documento3 pagineLAB 6 - Análisis y Síntesis de Circuitos Lógicos Secuenciales (Prof. Casimiro)Elmer525Nessuna valutazione finora

- LAB 4 - Contadores 2011-0 (Prof. Casimiro)Documento4 pagineLAB 4 - Contadores 2011-0 (Prof. Casimiro)Elmer525Nessuna valutazione finora

- Actividad Inicial Software para IngenieriaDocumento2 pagineActividad Inicial Software para IngenieriaPeterNessuna valutazione finora

- PSPB-300-X-PR-001 - 0 Informe Ejecutivo SemanalDocumento7 paginePSPB-300-X-PR-001 - 0 Informe Ejecutivo SemanalPercy MejiaNessuna valutazione finora

- Grandes Paneles PDFDocumento15 pagineGrandes Paneles PDFluis0107Nessuna valutazione finora

- Investigación No1 Analisis Estructural 1Documento20 pagineInvestigación No1 Analisis Estructural 1Jeriel MercedesNessuna valutazione finora

- Ejemplo Informe CCTV CarlosibarraDocumento37 pagineEjemplo Informe CCTV CarlosibarraObek EscotoNessuna valutazione finora

- CYPE - Instalaciones Del Edificio - Ejemplo de GasDocumento16 pagineCYPE - Instalaciones Del Edificio - Ejemplo de GaspoepeidoNessuna valutazione finora

- Ciclo 9 Ici Practicas Preprofesionales 2016 1 (Continuidad)Documento2 pagineCiclo 9 Ici Practicas Preprofesionales 2016 1 (Continuidad)Tulio Guillén SheenNessuna valutazione finora

- 2024 23 03 06 Universidades Requisito m2 p2024Documento20 pagine2024 23 03 06 Universidades Requisito m2 p2024javiera alvarezNessuna valutazione finora

- Ejercicio de Nacimiento y Muerte 2Documento3 pagineEjercicio de Nacimiento y Muerte 2José Verdejo Rodriguez100% (1)

- Civil 2016 IDocumento9 pagineCivil 2016 ICapuñay Diaz ChristianNessuna valutazione finora

- Intercambiador de CalorDocumento11 pagineIntercambiador de CalorDaniel Alejandro Quispe CaballeroNessuna valutazione finora

- Acta 11 SODocumento15 pagineActa 11 SORONALD_TVNessuna valutazione finora

- ACTIVIDAD No 5 BCOS CONDDocumento5 pagineACTIVIDAD No 5 BCOS CONDWilmer SuarezNessuna valutazione finora

- Brochure 2022 NavisworksDocumento2 pagineBrochure 2022 NavisworksAngelo Paolo Valenzuela ContrerasNessuna valutazione finora

- Caso 2 - Metodologías - Híbridas PDFDocumento17 pagineCaso 2 - Metodologías - Híbridas PDFSamuel MiramontesNessuna valutazione finora

- Generadores CompletoDocumento34 pagineGeneradores CompletoOzwaldoHernandezNessuna valutazione finora

- Memoria Descriptiva de Parque Villa TajoDocumento7 pagineMemoria Descriptiva de Parque Villa Tajofelipe azurin chalcoNessuna valutazione finora

- Examen Parcial de Construccion 2Documento7 pagineExamen Parcial de Construccion 2Gino Huallanca CoronadoNessuna valutazione finora

- Calculo TecnariaDocumento8 pagineCalculo TecnarianelsonhugoNessuna valutazione finora

- Ejemplo 1 Zapata Corrida para Muro de Carga PDFDocumento24 pagineEjemplo 1 Zapata Corrida para Muro de Carga PDFDiego Vargas HerreraNessuna valutazione finora

- Mc-Casa Tiburon Rev0Documento80 pagineMc-Casa Tiburon Rev0Luis Arturo ReséndizNessuna valutazione finora

- Probabilidad y Estadística para Ingeniería y Ciencias - Jay L. Devore - 7edDocumento33 pagineProbabilidad y Estadística para Ingeniería y Ciencias - Jay L. Devore - 7edIgnacio Morgado GabrielNessuna valutazione finora

- Fundamentos Básicos de Ingeniería EconómicaDocumento7 pagineFundamentos Básicos de Ingeniería EconómicaYarizel Serralta0% (1)

- Mamposteria Tradicional Vs Sistema LivianoDocumento10 pagineMamposteria Tradicional Vs Sistema LivianoMiguel AlferezNessuna valutazione finora

- 05 Procedimiento Trabajos Topográficos en Área Mina Rev 0Documento13 pagine05 Procedimiento Trabajos Topográficos en Área Mina Rev 0rmroa2007Nessuna valutazione finora

- ACS580MV Catalog 3BHT490775R0001 ES RevC 09082018 Lowres CorrectedDocumento32 pagineACS580MV Catalog 3BHT490775R0001 ES RevC 09082018 Lowres Correcteddaniel gallardoNessuna valutazione finora

- Ensayo Tipos de SistemasDocumento3 pagineEnsayo Tipos de SistemasDeron Alfredo Ruiz Pineda50% (2)

- Estudio de Torre Grua PDFDocumento115 pagineEstudio de Torre Grua PDFnelhioNessuna valutazione finora

- Silabo Resistencia de Materiales I 2022-IDocumento5 pagineSilabo Resistencia de Materiales I 2022-IFranklin Gutierrez CamposNessuna valutazione finora

- Cálculo 1er-InformeDocumento16 pagineCálculo 1er-InformeGary VargasNessuna valutazione finora

- Inteligencia artificial: Lo que usted necesita saber sobre el aprendizaje automático, robótica, aprendizaje profundo, Internet de las cosas, redes neuronales, y nuestro futuroDa EverandInteligencia artificial: Lo que usted necesita saber sobre el aprendizaje automático, robótica, aprendizaje profundo, Internet de las cosas, redes neuronales, y nuestro futuroValutazione: 4 su 5 stelle4/5 (1)

- Influencia. La psicología de la persuasiónDa EverandInfluencia. La psicología de la persuasiónValutazione: 4.5 su 5 stelle4.5/5 (14)

- 7 tendencias digitales que cambiarán el mundoDa Everand7 tendencias digitales que cambiarán el mundoValutazione: 4.5 su 5 stelle4.5/5 (87)

- Ciencia de datos: La serie de conocimientos esenciales de MIT PressDa EverandCiencia de datos: La serie de conocimientos esenciales de MIT PressValutazione: 5 su 5 stelle5/5 (1)

- El trading de opciones de una forma sencilla: La guía introductoria al trading de opciones y a las principales estrategias de beneficios.Da EverandEl trading de opciones de una forma sencilla: La guía introductoria al trading de opciones y a las principales estrategias de beneficios.Valutazione: 5 su 5 stelle5/5 (1)

- EL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.Da EverandEL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.Valutazione: 4 su 5 stelle4/5 (51)

- El Mom Test: Cómo Mantener Conversaciones con tus Clientes y Validar tu Idea de Negocio Cuando Todos te MientenDa EverandEl Mom Test: Cómo Mantener Conversaciones con tus Clientes y Validar tu Idea de Negocio Cuando Todos te MientenValutazione: 5 su 5 stelle5/5 (8)

- Sistema de gestión lean para principiantes: Fundamentos del sistema de gestión lean para pequeñas y medianas empresas - con muchos ejemplos prácticosDa EverandSistema de gestión lean para principiantes: Fundamentos del sistema de gestión lean para pequeñas y medianas empresas - con muchos ejemplos prácticosValutazione: 4 su 5 stelle4/5 (16)

- Guía para la aplicación de ISO 9001 2015Da EverandGuía para la aplicación de ISO 9001 2015Valutazione: 4 su 5 stelle4/5 (1)

- Toma de decisiones en las empresas: Entre el arte y la técnica: Metodologías, modelos y herramientasDa EverandToma de decisiones en las empresas: Entre el arte y la técnica: Metodologías, modelos y herramientasNessuna valutazione finora

- Electrónica básica: INGENIERÍA ELECTRÓNICA Y DE LAS COMUNICACIONESDa EverandElectrónica básica: INGENIERÍA ELECTRÓNICA Y DE LAS COMUNICACIONESValutazione: 5 su 5 stelle5/5 (16)

- Python Paso a paso: PROGRAMACIÓN INFORMÁTICA/DESARROLLO DE SOFTWAREDa EverandPython Paso a paso: PROGRAMACIÓN INFORMÁTICA/DESARROLLO DE SOFTWAREValutazione: 4 su 5 stelle4/5 (13)

- Excel y SQL de la mano: Trabajo con bases de datos en Excel de forma eficienteDa EverandExcel y SQL de la mano: Trabajo con bases de datos en Excel de forma eficienteValutazione: 1 su 5 stelle1/5 (1)

- Conquista de las Redes Sociales: 201 Consejos para Marketeros y Emprendedores DigitalesDa EverandConquista de las Redes Sociales: 201 Consejos para Marketeros y Emprendedores DigitalesValutazione: 4.5 su 5 stelle4.5/5 (2)

- Clics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaDa EverandClics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaValutazione: 4.5 su 5 stelle4.5/5 (117)

- Cultura y clima: fundamentos para el cambio en la organizaciónDa EverandCultura y clima: fundamentos para el cambio en la organizaciónNessuna valutazione finora

- Excel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másDa EverandExcel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másValutazione: 2.5 su 5 stelle2.5/5 (3)

- Radiocomunicaciones: Teoría y principiosDa EverandRadiocomunicaciones: Teoría y principiosValutazione: 5 su 5 stelle5/5 (3)

- Python Deep Learning: Introducción práctica con Keras y TensorFlow 2Da EverandPython Deep Learning: Introducción práctica con Keras y TensorFlow 2Valutazione: 3.5 su 5 stelle3.5/5 (5)

- Agile: Una guía para la Gestión de Proyectos Agile con Scrum, Kanban y LeanDa EverandAgile: Una guía para la Gestión de Proyectos Agile con Scrum, Kanban y LeanValutazione: 5 su 5 stelle5/5 (1)

- Ingeniería química. Soluciones a los problemas del tomo IDa EverandIngeniería química. Soluciones a los problemas del tomo INessuna valutazione finora

- Guía para la crianza en un mundo digital: Cómo educar para un uso sano y seguro de la tecnologíaDa EverandGuía para la crianza en un mundo digital: Cómo educar para un uso sano y seguro de la tecnologíaValutazione: 3.5 su 5 stelle3.5/5 (2)

- 44 Apps Inteligentes para Ejercitar su Cerebro: Apps Gratuitas, Juegos, y Herramientas para iPhone, iPad, Google Play, Kindle Fire, Navegadores de Internet, Windows Phone, & Apple WatchDa Everand44 Apps Inteligentes para Ejercitar su Cerebro: Apps Gratuitas, Juegos, y Herramientas para iPhone, iPad, Google Play, Kindle Fire, Navegadores de Internet, Windows Phone, & Apple WatchValutazione: 3.5 su 5 stelle3.5/5 (2)

- Manual técnico para la interpretación de análisis de suelos y fertilización de cultivosDa EverandManual técnico para la interpretación de análisis de suelos y fertilización de cultivosValutazione: 4 su 5 stelle4/5 (1)