Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

h4 f07 PDF

Caricato da

Devaraj Subrmanayam0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

182 visualizzazioni2 pagineThis document contains 7 homework problems for a course on VLSI design. The problems involve timing analysis of flip-flops and latches under different clocking conditions, determining maximum propagation delays and minimum contamination delays, calculating time borrowing, and deriving timing parameters for a positive edge-triggered register circuit. The homework is worth a total of 110 points.

Descrizione originale:

Titolo originale

h4.f07.pdf

Copyright

© © All Rights Reserved

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoThis document contains 7 homework problems for a course on VLSI design. The problems involve timing analysis of flip-flops and latches under different clocking conditions, determining maximum propagation delays and minimum contamination delays, calculating time borrowing, and deriving timing parameters for a positive edge-triggered register circuit. The homework is worth a total of 110 points.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

182 visualizzazioni2 pagineh4 f07 PDF

Caricato da

Devaraj SubrmanayamThis document contains 7 homework problems for a course on VLSI design. The problems involve timing analysis of flip-flops and latches under different clocking conditions, determining maximum propagation delays and minimum contamination delays, calculating time borrowing, and deriving timing parameters for a positive edge-triggered register circuit. The homework is worth a total of 110 points.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 2

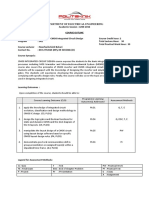

CPE/EE 427, CPE 527 VLSI Design I: Homework 4

1 2 3 4 5 6 7 Sum

15 15 15 15 15 20 15 110

For the following exercises use the timing parameters below.

Setup Time Clk-to-Q D-to-Q Contamination Hold delay

delay delay delay

Flip-flops 65 ps 50 ps n/a 35 ps 30 ps

Latches 25 ps 50 ps 40 ps 35 ps 30 ps

1. (15 points) Propagation delay

For each of the following sequencing styles, determine the maximum logic propagation

delay available within a 500 ps clock cycle. Assume there is zero clock skew and no time

borrowing takes place.

(a) Flip-flops

(b) Two-phase transparent latches

(c) Pulsed latches with 80 ps pulse width.

2. (15 points) Repeat the exercise 1 if the clock skew between any two elements can be

up to 50 ps.

3. (15 points) Contamination delay

For each of the following sequencing styles, determine the minimum logic contamination

delay in each clock cycle (or half-cycle for two-phase latches). Assume a zero clock

skew.

(a) Flip-flops

(b) Two-phase transparent latches with 50% duty cycle clocks

(c) Two-phase transparent latches with 60 ps of nonoverlap between phases

(d) Pulsed latches with 80 ps pulse width.

4. (15 points) Repeat the exercise 3 if the clock skew between any two elements can be

up to 50 ps.

5. (15 points) Time borrowing

Suppose one cycle of logic is particularly critical and the next cycle is nearly empty.

Determine the maximum amount of time the first cycle can borrow into the second for

each of the following sequencing styles. Assume there is zero clock skew.

(a) Flip-flops

(b) Two-phase transparent latches with 50% duty cycle clocks

(c) Two-phase transparent latches with 60 ps of nonoverlap between phases

(d) Pulsed latches with 80 ps pulse width.

EE/CPE 427, CPE 527 Page 1 of 2

6. (20 points)

Determine the minimum clock period at which the circuit below will operate correctly for

each of the following logic delays. Assume there is zero clock skew and that the latch

delays are accounted for in the propagation delay ∆’s.

(a) ∆1 = 300 ps, ∆2 = 400 ps, ∆3 = 200 ps, ∆4 = 350 ps.

(b) ∆1 = 300 ps, ∆2 = 400 ps, ∆3 = 400 ps, ∆4 = 550 ps.

(c) ∆1 = 300 ps, ∆2 = 900 ps, ∆3 = 200 ps, ∆4 = 350 ps.

7. (15 points) FF design

Consider the following edge-triggered register. Assume that the clock inputs CLK and

CLK have a 0V to VDD swing. Also assume that there is no skew between CLK and CLK

(i.e., the inverter delay to derive CLK from CLK is zero). Assume that the rise/fall times

on all signals are zero.

(a) (5 points) What type of register is this? Explain. (Positive Edge-Triggered Register or

Negative Edge-Triggered Register).

(b) (10 points) Assume that the propagation delay of each clocked inverter (e.g., M1-M4)

is TCK-INV and the delay of inverters I1 and I2 is TINV. Derive the expression for the set-up

time (tSU), the propagation delay (tc-q) and the hold time (th) in terms of the above

parameters, TCK-INV and TINV.

EE/CPE 427, CPE 527 Page 2 of 2

Potrebbero piacerti anche

- PNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGDa EverandPNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGNessuna valutazione finora

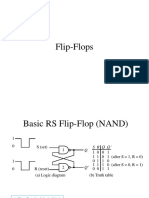

- Sequential LogicDocumento94 pagineSequential LogicPranav DarganNessuna valutazione finora

- Dic Quiz 03 Seq v01Documento6 pagineDic Quiz 03 Seq v01OPTICALMIMOOFDMNessuna valutazione finora

- EE 5311 Digital IC Design Tutorial 3 - Sep 25, 2015: N Ox 2 P Ox 2 Min Min T T Dsat Dsat DDDocumento2 pagineEE 5311 Digital IC Design Tutorial 3 - Sep 25, 2015: N Ox 2 P Ox 2 Min Min T T Dsat Dsat DDHarshithNessuna valutazione finora

- Timing Issues in Digital ASIC DesignDocumento101 pagineTiming Issues in Digital ASIC Designnsai_vs1513Nessuna valutazione finora

- Solution ST1 Set ADocumento12 pagineSolution ST1 Set Agaurika.sawhney2003Nessuna valutazione finora

- ECE586 Homework No. 3 SolutionDocumento5 pagineECE586 Homework No. 3 SolutionMaster Chandra babuNessuna valutazione finora

- Digital Ic Design TutorialDocumento4 pagineDigital Ic Design Tutorialkrishna kanthNessuna valutazione finora

- Ramkumar PDFDocumento5 pagineRamkumar PDFKiruthika MNessuna valutazione finora

- Logic Design For Single On-Chip Test Clock Generation For N Clock Domain - Impact On SOC Area and Test QualityDocumento5 pagineLogic Design For Single On-Chip Test Clock Generation For N Clock Domain - Impact On SOC Area and Test QualitymohanNessuna valutazione finora

- VLSI RamDocumento18 pagineVLSI RamrAM100% (4)

- Question 1 (50 Points) PipeliningDocumento3 pagineQuestion 1 (50 Points) PipeliningMuhammad Zahid iqbalNessuna valutazione finora

- Frequency Dividers: Device Modelling Mini-ProjectDocumento24 pagineFrequency Dividers: Device Modelling Mini-Projectjoshuacool4Nessuna valutazione finora

- QA - Copy - Copy2Documento12 pagineQA - Copy - Copy2Physical DesignNessuna valutazione finora

- Clocking and Latches: Notes For EEC180B Spring 1999 University of California DavisDocumento18 pagineClocking and Latches: Notes For EEC180B Spring 1999 University of California Davisrvs_093Nessuna valutazione finora

- Power Electronics LAB 1Documento21 paginePower Electronics LAB 1Mustafa MhmoodNessuna valutazione finora

- 11 Clock SkewDocumento35 pagine11 Clock SkewMaheshNessuna valutazione finora

- EC Lab ManualsDocumento53 pagineEC Lab ManualsArish AliNessuna valutazione finora

- Lab 1Documento8 pagineLab 1Mulugeta AbebawNessuna valutazione finora

- Clock PowerDocumento8 pagineClock PowerSathish BalaNessuna valutazione finora

- Clocked Systems (Cont.) : Clock SkewDocumento4 pagineClocked Systems (Cont.) : Clock SkewDuy DungNessuna valutazione finora

- Lect17 SeqDocumento18 pagineLect17 SeqorengeneralNessuna valutazione finora

- 3 SequentialDocumento25 pagine3 SequentialZaziNessuna valutazione finora

- Analog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and EngineeringDocumento61 pagineAnalog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and Engineeringvadla77Nessuna valutazione finora

- Homework Assignment 12: SolutionDocumento7 pagineHomework Assignment 12: SolutionTarik ZiadNessuna valutazione finora

- ENS/ELT466: Telecommunication Systems Lab Fall 2013 Week 4 - Sept. 24Documento8 pagineENS/ELT466: Telecommunication Systems Lab Fall 2013 Week 4 - Sept. 24kaethamNessuna valutazione finora

- DE PaperDocumento4 pagineDE Paperbhaveshgupta098Nessuna valutazione finora

- Chapter2 Clocks Resets-04Documento8 pagineChapter2 Clocks Resets-04hardeepNessuna valutazione finora

- VLSI Interview QuestionsDocumento112 pagineVLSI Interview QuestionsrAM100% (10)

- CTSDocumento2 pagineCTSRamakrishnaRao SoogooriNessuna valutazione finora

- Cmos Nor and Nand GateDocumento3 pagineCmos Nor and Nand GateClarisse GambotaNessuna valutazione finora

- F10 E1 SolutionDocumento5 pagineF10 E1 Solutionkashi13Nessuna valutazione finora

- QUALCOMM Interview Questions 1. Basic View of Compression?Documento9 pagineQUALCOMM Interview Questions 1. Basic View of Compression?deepa100% (2)

- Design A Pulse Mode Circuit Having Two InputDocumento4 pagineDesign A Pulse Mode Circuit Having Two InputSiva GuruNessuna valutazione finora

- 18csl37-Ade Lab ManualDocumento41 pagine18csl37-Ade Lab ManualEragon ShadeSlayerNessuna valutazione finora

- April 2005 WithsloutionDocumento21 pagineApril 2005 Withsloutionapi-3755462Nessuna valutazione finora

- General Instructions To The CandidateDocumento4 pagineGeneral Instructions To The Candidateapurv shuklaNessuna valutazione finora

- Digital Electronics Tutorial Sheet-1Documento13 pagineDigital Electronics Tutorial Sheet-1shraddhabansalNessuna valutazione finora

- AVD2Documento2 pagineAVD2ankushwreNessuna valutazione finora

- MHZ 1-Micron Cmos Pipelined 8-Bit Adder Using True Single-Phase Logic-Flip-FlopsDocumento4 pagineMHZ 1-Micron Cmos Pipelined 8-Bit Adder Using True Single-Phase Logic-Flip-FlopsMamta JatoliaNessuna valutazione finora

- ELE 4613 - ProjectDocumento6 pagineELE 4613 - ProjectmukulNessuna valutazione finora

- DLC LAB - 07 - Student - ManualDocumento6 pagineDLC LAB - 07 - Student - Manualrk refatNessuna valutazione finora

- Lovely Professional University "Term Paper" ON " " (CSE-211)Documento11 pagineLovely Professional University "Term Paper" ON " " (CSE-211)Sandeep KaurNessuna valutazione finora

- Chp1 - Latches and Flip-FlopsDocumento44 pagineChp1 - Latches and Flip-FlopsAbnen OngNessuna valutazione finora

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsDa EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsValutazione: 1 su 5 stelle1/5 (1)

- Numerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityDa EverandNumerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityNessuna valutazione finora

- Advanced Opensees Algorithms, Volume 1: Probability Analysis Of High Pier Cable-Stayed Bridge Under Multiple-Support Excitations, And LiquefactionDa EverandAdvanced Opensees Algorithms, Volume 1: Probability Analysis Of High Pier Cable-Stayed Bridge Under Multiple-Support Excitations, And LiquefactionNessuna valutazione finora

- Modern Borehole Analytics: Annular Flow, Hole Cleaning, and Pressure ControlDa EverandModern Borehole Analytics: Annular Flow, Hole Cleaning, and Pressure ControlNessuna valutazione finora

- GARCH Models: Structure, Statistical Inference and Financial ApplicationsDa EverandGARCH Models: Structure, Statistical Inference and Financial ApplicationsValutazione: 5 su 5 stelle5/5 (1)

- Measurement While Drilling: Signal Analysis, Optimization and DesignDa EverandMeasurement While Drilling: Signal Analysis, Optimization and DesignNessuna valutazione finora

- Food Safety and Quality Policy: M/s Dwaraka Sea Foods Sanitary Standard Operating ProcedureDocumento2 pagineFood Safety and Quality Policy: M/s Dwaraka Sea Foods Sanitary Standard Operating ProcedureDevaraj SubrmanayamNessuna valutazione finora

- 5.management Commitment - 07Documento1 pagina5.management Commitment - 07Devaraj SubrmanayamNessuna valutazione finora

- Akshay Food Impex Pvt. LTD.,: Register of Maintenance of Lab EquipmentsDocumento2 pagineAkshay Food Impex Pvt. LTD.,: Register of Maintenance of Lab EquipmentsDevaraj SubrmanayamNessuna valutazione finora

- Sanitary Standard Operating Procedure ScopeDocumento2 pagineSanitary Standard Operating Procedure ScopeDevaraj SubrmanayamNessuna valutazione finora

- PCB AknowledgmentDocumento6 paginePCB AknowledgmentDevaraj SubrmanayamNessuna valutazione finora

- Application For Approval of EstablishmentDocumento20 pagineApplication For Approval of EstablishmentDevaraj SubrmanayamNessuna valutazione finora

- AD CVD NON REIMBURSEMENT STATEMENT (fINAL)Documento1 paginaAD CVD NON REIMBURSEMENT STATEMENT (fINAL)Devaraj SubrmanayamNessuna valutazione finora

- Nova Led SlideDocumento25 pagineNova Led SlideDevaraj SubrmanayamNessuna valutazione finora

- Ece 467 HW Assignment 2Documento1 paginaEce 467 HW Assignment 2Devaraj SubrmanayamNessuna valutazione finora

- HW2 SolutionDocumento7 pagineHW2 SolutionDevaraj SubrmanayamNessuna valutazione finora

- EIA INTERDEPARTMENTAL PANEL NON CONFORMITY (Final)Documento4 pagineEIA INTERDEPARTMENTAL PANEL NON CONFORMITY (Final)Devaraj SubrmanayamNessuna valutazione finora

- Munnangi Sea Foods Private LimitedDocumento77 pagineMunnangi Sea Foods Private LimitedDevaraj SubrmanayamNessuna valutazione finora

- Contents:: Unit Iii Cmos Logic Gates Design and LayoutDocumento35 pagineContents:: Unit Iii Cmos Logic Gates Design and LayoutDevaraj SubrmanayamNessuna valutazione finora

- h3 f06 PDFDocumento5 pagineh3 f06 PDFDevaraj SubrmanayamNessuna valutazione finora

- EE/CPE 428, CPE 528 Homework 1 Solutions: Exercise 1.Documento7 pagineEE/CPE 428, CPE 528 Homework 1 Solutions: Exercise 1.Devaraj SubrmanayamNessuna valutazione finora

- Homework2 Soln DevDocumento18 pagineHomework2 Soln DevDevaraj SubrmanayamNessuna valutazione finora

- hw1 PDFDocumento3 paginehw1 PDFDevaraj SubrmanayamNessuna valutazione finora

- Low-Power All-Analog Circuit For Rectangular-Type Analog Joint Source Channel CodingDocumento4 pagineLow-Power All-Analog Circuit For Rectangular-Type Analog Joint Source Channel CodingDevaraj SubrmanayamNessuna valutazione finora

- Declaration Compliance ANIA CLIFE 2011 enDocumento4 pagineDeclaration Compliance ANIA CLIFE 2011 enDevaraj SubrmanayamNessuna valutazione finora

- Blue Park Account DetailsDocumento23 pagineBlue Park Account DetailsDevaraj SubrmanayamNessuna valutazione finora

- HIGH Frequency and Low Out (Ut Impedance BufferDocumento4 pagineHIGH Frequency and Low Out (Ut Impedance BufferDeepak BishtNessuna valutazione finora

- DEE6113 Course Outline Jun2016Documento4 pagineDEE6113 Course Outline Jun2016FonzBahariNessuna valutazione finora

- Tutorial C4 SEEU2012Documento4 pagineTutorial C4 SEEU2012dukeNessuna valutazione finora

- Fm/Am Tuner Frequency & Clock Display Driver: DescriptionDocumento13 pagineFm/Am Tuner Frequency & Clock Display Driver: DescriptionВячеслав ГлушакNessuna valutazione finora

- Design of A New 3 Bit Flash Analog To DiDocumento11 pagineDesign of A New 3 Bit Flash Analog To DisayemeeceNessuna valutazione finora

- Kuijk Bandgap Voltage Reference With High Immunity To EMIDocumento5 pagineKuijk Bandgap Voltage Reference With High Immunity To EMIjulio perezNessuna valutazione finora

- Lab 4: Design and Analysis of BJT Biasing and Amplifier CircuitDocumento7 pagineLab 4: Design and Analysis of BJT Biasing and Amplifier CircuitSatyam SatyaprakashNessuna valutazione finora

- Nte85 PDFDocumento2 pagineNte85 PDFWilson DuranNessuna valutazione finora

- Difference Between BJT and MOSFET - Advantages & DisadvantagesDocumento1 paginaDifference Between BJT and MOSFET - Advantages & DisadvantagesShiva H. AdhikariNessuna valutazione finora

- Logic FamiliesDocumento18 pagineLogic FamiliesHiiiNessuna valutazione finora

- Mos Integrated Circuit: Data SheetDocumento62 pagineMos Integrated Circuit: Data SheetdgdNessuna valutazione finora

- PLDTUTORDocumento13 paginePLDTUTORAjay Nath S ANessuna valutazione finora

- FM600BLFDocumento3 pagineFM600BLFRemy MendozaNessuna valutazione finora

- 10B17EC271Documento2 pagine10B17EC271Shivam MauryaNessuna valutazione finora

- Presentation Microwave Transmitter and Receiver-1Documento22 paginePresentation Microwave Transmitter and Receiver-1Subrata Maiti100% (1)

- 50 TOP SOLID STATE SWITCHING CIRCUITS Questions and Answers PDFDocumento7 pagine50 TOP SOLID STATE SWITCHING CIRCUITS Questions and Answers PDFijazNessuna valutazione finora

- Solution Manual For Microelectronic CircDocumento28 pagineSolution Manual For Microelectronic CircMiguel Angel Henao PradaNessuna valutazione finora

- Digital Electronics: Course Description and ObjectivesDocumento3 pagineDigital Electronics: Course Description and ObjectivesMaxNessuna valutazione finora

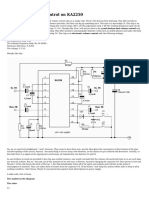

- AplicationKA2250 PDFDocumento3 pagineAplicationKA2250 PDFnotlianNessuna valutazione finora

- Sginverter 230515Documento1 paginaSginverter 230515Ibrahim Dalafika AbdullahiNessuna valutazione finora

- Bee Unit 2 Complete NotesDocumento32 pagineBee Unit 2 Complete NotesRamesh DongaraNessuna valutazione finora

- Course On MicrocontrollersDocumento115 pagineCourse On MicrocontrollersKorom ChandNessuna valutazione finora

- Telcom 1-1Documento36 pagineTelcom 1-1Abdurrahman Aliyu JafarNessuna valutazione finora

- FAN7602 DataDocumento18 pagineFAN7602 DataSergio Daniel BarretoNessuna valutazione finora

- Verified Analog Parts - LNKDocumento3 pagineVerified Analog Parts - LNKAnonymous BW9mIv22NNessuna valutazione finora

- GAL Databook 1991 PDFDocumento251 pagineGAL Databook 1991 PDFbkaplan452Nessuna valutazione finora

- Datasheet D2061 NPN 3ADocumento3 pagineDatasheet D2061 NPN 3AFaça voce mesmoNessuna valutazione finora

- Systematic Design of Three Stage Opamps Using Split-Length CompensationDocumento4 pagineSystematic Design of Three Stage Opamps Using Split-Length CompensationSumeet SauravNessuna valutazione finora

- ETI-CA-1980-01 Struss FuzzDocumento4 pagineETI-CA-1980-01 Struss FuzzBrunoNessuna valutazione finora