Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

MG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCC

Caricato da

chaitanyaCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

MG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCC

Caricato da

chaitanyaCopyright:

Formati disponibili

AppNote MG580225

A Practical Clock Control Circuit Design & Example

Tessent® ATPG Test Case

October 2013

©Copyright Mentor Graphics Corporation 1995-2013. All rights reserved.

This document contains information that is proprietary to Mentor Graphics ® Corporation. The original recipient

of this document may duplicate this document in w hole or in part for internal business purposes only, provided

that this entire notice appears in all copies in duplicating any part of this document, the recipient agrees to make

every reasonable effort to prevent the unauthorized use and distribution of the proprietary information.

Trademarks that appear in Mentor Graphics product publications that are not ow ned by Mentor Graphics are

trademarks of their respective ow ners.

Mentor Graphics Confidential 1 September 2013

Table of Contents

1. Introduction .............................................................................................................. 5

2. Clock Control Circuit Description ................................................................................. 5

2.1. Design Placement .............................................................................................. 5

2.2. Schematic ......................................................................................................... 6

2.3. Scan Enable Synchronization ............................................................................... 7

2.4. Clock Gater Cells ............................................................................................... 7

2.5. Clock Definition for ATPG .................................................................................... 7

2.6. Shift Register Block ............................................................................................ 8

2.7. Clock Control Operation Modes ............................................................................ 9

2.7.1. Functional Mode ......................................................................................................... 9

2.7.2. Shift Mode ................................................................................................................. 9

2.7.3. Slow Capture Mode....................................................................................................10

2.7.4. Fast Capture Mode ....................................................................................................10

2.8. Timing Diagrams ................................................................................................ 10

2.9. RTL Description ................................................................................................. 12

3. Test Case Description................................................................................................ 14

3.1. Test Case Design Statistics ................................................................................. 14

3.2. Directory Structure.............................................................................................. 14

3.3. Test Case Steps................................................................................................. 15

3.4. RTL Simulation .................................................................................................. 15

3.5. RTL Synthesis ................................................................................................... 16

3.6. Baseline ATPG .................................................................................................. 16

3.7. Clock Control Logic Insertion................................................................................ 16

3.8. Slow Capture ATPG ............................................................................................ 18

3.8.1. ATPG Commands ........................................................................................... 18

3.8.2. Test Procedure File ......................................................................................... 20

3.9. Fast Capture ATPG ............................................................................................ 23

3.10. Pattern Verification.......................................................................................... 24

Mentor Graphics Confidential 2 September 2013

3.11. Compression Logic Insertion and ATPG ............................................................. 25

Appendix A – Using OCC in an LPCT flow ............................................................................ 27

1. Introduction .............................................................................................................. 27

2. Clock Control Circuit Description ................................................................................. 27

2.1. Design Placement .............................................................................................. 27

2.2. Schematic ......................................................................................................... 27

2.3. Capture Enable Synchronization ........................................................................... 29

2.4. Clock Gater Cells ............................................................................................... 29

2.5. Clock Definition for ATPG .................................................................................... 29

2.6. Shift Register Block ............................................................................................ 30

2.7. Clock Control Operation Modes ............................................................................ 31

2.7.1. Functional Mode ........................................................................................................31

2.7.2. Shift Mode ................................................................................................................31

2.7.3. Slow Capture Mode....................................................................................................32

2.7.4. Fast Capture Mode ....................................................................................................32

2.8. Timing Diagrams ................................................................................................ 32

2.9. RTL Description ................................................................................................. 34

3. Test Case Description................................................................................................ 36

3.1. Test Case Design Statistics ................................................................................. 36

3.2. Directory Structure.............................................................................................. 36

3.3. Test Case Steps................................................................................................. 37

3.4. RTL Synthesis ................................................................................................... 37

3.5. Test logic and clock control insertion ..................................................................... 38

3.6. Generating, inserting and synthesizing LPCT and TestKompress logic ....................... 40

3.7. Generating patterns ............................................................................................ 41

3.7.1. Dofile for pattern generation .............................................................................. 42

3.7.2. Test Procedure File ......................................................................................... 42

3.7.3. Slow Capture ATPG ........................................................................................ 42

3.7.4. Fast Capture ATPG ......................................................................................... 43

Mentor Graphics Confidential 3 September 2013

3.8. Pattern Verification ............................................................................................. 43

Mentor Graphics Confidential 4 September 2013

1. Introduction

In modern designs, clock control circuits are commonly used to manage clocks during test to ensure the

following requirements are met:

Independent control by ATPG of each clock domain to improve coverage, reduce pattern count, and

achieve safe clocking with minimal user intervention

During capture, deliver correct number of clock pulses on a per-pattern basis

Cleanly switch between shift and capture clocks

Enable slow or fast clocks during capture for application of slow and at-speed patterns

Scan-programmable clock waveforms generated within a wrapped core are ideal for generating

patterns at the core level that can be retargeted to the top level while simultaneously testing

multiple cores without conflicts in how clocks are controlled within each core

This application note describes a practical PLL clock control circuit design and demonstrates its use in a

test case using Tessent® ATPG tools.

A complete test case that demonstrates the use of this clock control design in a circuit is described in the

last section. The test case is available from Mentor Graphics by downloading it from the following

SupportNet page: http://supportnet.mentor.com/reference/tutorials/index.cfm?id=MG576857

2. Clock Control Circuit Description

2.1. Design Placement

In order to avoid delay on the clock path due to test logic, a multiplexer should already exist on the clock

source to the core flops and timed for functional behavior. It is important to only balance the functional

clock path of the mux in order to avoid over-constraining the clock tree synthesis flow and causing

excessive clock latency. For example, if using a layout tool like ICCompiler, this can be accomplished by

using a set_clock_tree_exceptions -exclude_pins command and listing slow and fast clock inputs of

the clock control block. In tools such as Talus from Magma, a skew group definition for each clock control

block can be used.

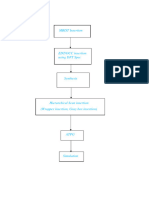

The mux should be controlled by the test mode signal as shown in Figure 1.

Figure 1 – Clock Control Logic Design Placement

The clock control design described in this application note should supply the clock when in test mode

while using the clock output of the PLL as the fast clock for at-speed capture. A top-level slow clock will

be used for shift and slow capture. The reference clock supplied to the PLL is a free-running clock.

It is also recommended not to flatten the clock control blocks during layout in order to keep the test

procedure file definition easier post layout.

Mentor Graphics Confidential 5 September 2013

2.2. Schematic

The schematic for the clock control circuit is shown in Figure 2 and the corresponding RTL can be found

in section 2.9 of this document.

Figure 2 – Clock Control Logic Schematic

The following table describes the functionality of pins at the top of the clock control block as well as some

of the internal signals:

Name Direction Description

SCAN_EN Input Scan enable driven by top-level pin

Configures number of clock pulses during capture cycle

CAP_CYCLE_CONFIG [1:0] Input (maximum clock pulses = CAP_CYCLE_CONFIG + 1)

as well as length of scan chain during shift

SCAN_IN Input Scan chain input for loading shift register

FAST_CAP_MODE Input Selects fast or slow capture clock (0 = slow, 1 = fast)

Selects test or functional mode (0 = functional, 1 = test).

TEST_MODE Input During functional mode, the clock control block is

disabled to minimize power and cross talk.

FAST_CLK Input Clock for fast capture (typically output of PLL)

SLOW_CLK Input Clock for shift and slow capture

SCAN_OUT Output Scan chain output for unloading shift register

CLK_OUT Output Controlled clock output

SCAN_EN_sync Internal Synchronized scan enable

SHIFT_REG_CLK_en Internal Clock enable signal for shift register

SHIFT_REG_CLK Internal Clock source for shift register

CLK_OUT_source Internal Clock source for controlled clock output

CLK_OUT_en Internal Clock enable signal for controlled clock output

Static signals that do not change during the test session can be controlled through on-chip controllers

(such as JTAG) or other means in order to reduce the need for top-level pins.

Mentor Graphics Confidential 6 September 2013

2.3. Scan Enable Synchronization

In order to synchronize the top-level scan enable signal with the fast clock (PLL output), a two-flop

synchronization cell is used and clocked by FAST_CLK. This is important because scan enable is used

as the trigger signal to gate the clock to the shift register. The output of the synchronization cell produces

a scan enable signal which is synchronized with the fast clock (SCAN_EN_sync) and can be used during

fast capture test.

In version 1.1 of the clock controller RTL, a flop was added on the input side of the synchronization cell

and clocked by the trailing edge of SLOW_CLK. Since SCAN_EN normally fans out to the entire circuit

and may arrive after FAST_CLK, the flop on SLOW_CLK ensures that SCAN_EN is not synchronized by

the fast clock until SLOW_CLK is pulsed thus reducing the risk of a race condition.

Note that the scan enable synchronization logic is not used for slow capture mode which uses

SLOW_CLK for shift and capture.

In the RTL description, the synchronization cell is described as module “tessent_sync_cell” so that it can

be replaced with a technology specific synchronization cell from the appropriate library.

module tessent_sync_cell (d, clk, q);

input d, clk;

output q;

reg [1:0] R;

always @ (posedge clk) begin

R <= {R[0],d};

end

assign q = R[1];

endmodule

In order to ensure proper DRC analysis and simulation, the output of the clock gater cell driven by the

synchronization logic should be defined as a free-running internal clock. This is indicated by an arrow in

Figure 2 and ensures correct simulation of the logic during load_unload and avoids DRC violations.

2.4. Clock Gater Cells

The clock control circuit uses two clock gater cells to gate the clock for sequential elements inside and

outside the circuit. Similar to the synchronization cell, the clock gater cells are described as module

“tessent_cgc” so that they can be replaced with technology specific clock gater cells.

module tessent_cgc (clk, te, fe, clkg);

input clk, te, fe;

output clkg;

wire te_fe;

reg latch;

assign te_fe = te | fe;

always @ (clk or te_fe) begin

if (~clk) latch <= te_fe;

end

assign clkg = clk & latch;

endmodule

2.5. Clock Definition for ATPG

In the ATPG dofile, the output of the clock control logic block should be defined as an internal clock

source as shown in Figure 2. For example:

add_clocks 0 /clock_control_i/CLK_OUT –internal

Mentor Graphics Confidential 7 September 2013

With this specification, both shift and capture clocks are supplied to the design at this location which

means the internal clock should be specified in capture as well as shift procedures.

2.6. Shift Register Block

Figure 3 – Shift Register Block Schematic

The shift register block contains the programmable scan cells which will be loaded during shift in order to

pulse the internal clock during the cycle required by ATPG.

The AND gate on the input of the shift register loads zeros into the register during capture to clear it. The

EN output signal of the shift register block is used in the clock control block (Figure 2) to turn off the fast

clock to the shift register once the shift register has been unloaded. This ensures switching from the fast

capture clock to slow shift clock without risk of glitches and disturbing the values present in the shift

register. It also ensures that the shift register flip-flops have stable values when the ATPG tool simulates

the load_unload procedure and eliminates unnecessary DRC violations.

A lockup cell on the SCAN_OUT output of the shift register block ensures proper shift operation when

several clock control blocks are concatenated into a scan chain or when scan cells from chains with

different clocks are combined with the shift register flops. This is important because as described in

section 2.1, each clock control block forms a locally balanced clock tree which is not balanced with any

other chain segment.

A key feature of the shift register block is the ability to bypass up to 3 shift registers in order to reduce the

number of bits that must be specified in the patterns. This is done by setting the CAP_CYCLE_CONFIG

signals per the following table:

Maximum Clock Pulses

CAP_CYCLE_CONFIG[0] CAP_CYCLE_CONFIG[1]

During Capture Cycle

0 0 1

0 1 2

1 0 3

1 1 4

Limiting the number of condition bits to only those needed for the longest capture sequence reduces the

overall shift cycles as well as the number of scan bits that must be specified for each pattern. Minimizing

Mentor Graphics Confidential 8 September 2013

the number of specified scan cells per pattern will ensure the ATPG tool can provide the most efficient

pattern set as well as the highest compression ratio when using embedded compression.

In addition to limiting the overall number of specified scan cells, it is also important to limit the number of

scan cells that must be specified in each shift cycle. When using compression, the output of the

decompressor loads all chains simultaneously one shift cycle at a time. When stitching the shift register

sub-chains into the design scan chains, care should be taken to avoid the alignment of multiple condition

bits into the same shift cycle. One approach is to stitch the condition registers into an uncompressed scan

chain which is directly loaded. For designs in which all scan chains are compressed, placing condition bits

at the beginning, end or similar cell number of all scan chains should be avoided so that it is not

necessary to load many specified bits in the same shift cycle.

2.7. Clock Control Operation Modes

2.7.1. Functional Mode

When operating in functional mode (TEST_MODE = 0), all clock gaters are disabled to reduce

power.

Figure 4 – Test Mode Disabled

2.7.2. Shift Mode

In shift mode (SCAN_EN = 1), SLOW_CLOCK is used to load/unload scan chains which

include the condition bits in ShiftReg.

Figure 5 – Shift Mode Operation

Mentor Graphics Confidential 9 September 2013

2.7.3. Slow Capture Mode

In slow capture mode (FAST_CAP_MODE = 0), SLOW_CLOCK is used to capture data into

scan cells and to shift the condition bits in ShiftReg.

Figure 6 – Slow Capture Mode Operation

2.7.4. Fast Capture Mode

In fast capture mode (FAST_CAP_MODE = 1), FAST_CLOCK is used to capture data into scan

cells and to shift the condition bits in ShiftReg.

Figure 7 – Fast Capture Mode Operation

2.8. Timing Diagrams

The timing diagram for slow speed capture (FAST_CAP_MODE = 0) is shown in Figure 8. For this

example, CAP_CYCLE_CONFIG is set to “10” resulting in sequential depth of 3 (per table in section 2.6).

In this mode, SLOW_CLK is used for shift as well as capture. Based on condition bits loaded into the shift

register, the CLK_OUT port will generate the appropriate number of slow clock pulses.

Figure 8 – Slow Speed Capture Timing Diagram

Mentor Graphics Confidential 10 September 2013

In fast capture mode (FAST_CAP_MODE = 1) the waveforms in Figure 9 are generated. Similar to the

previous example, CAP_CYCLE_CONFIG is set to “10” here resulting in sequential depth of 3. In this

mode, the slow clock is still used for shift but the fast capture pulses on CLK_OUT are based FAST_CLK.

As shown, the scan enable signal which has been synchronized to the fast clock (SCAN_EN_sync) is

used to trigger the fast clock pulses on SHIFT_REG_CLK. The SHIFT_REG_CLK signal is the clock

source for the shift register containing the condition bits. Based on the condition bits loaded during shift,

the correct number of fast clock pulses will appear on CLK_OUT.

Figure 9 – Fast Capture Timing Diagram

Mentor Graphics Confidential 11 September 2013

2.9. RTL Description

The RTL description of the circuit described in this application note and used in the test case is shown in

the following section:

(* version=1.2 *)

module tessent_atpg_clock_controller (FAST_CLK, SLOW_CLK, TEST_MODE, SCAN_IN, SCAN_EN,

FAST_CAP_MODE, CAP_CYCLE_CONFIG, SCAN_OUT, CLK_OUT);

input FAST_CLK, SLOW_CLK, TEST_MODE, SCAN_IN, SCAN_EN, FAST_CAP_MODE;

input [1:0] CAP_CYCLE_CONFIG;

output SCAN_OUT, CLK_OUT;

wire SCAN_EN_sync;

wire ShiftReg_EN;

wire ShiftReg_SCAN_OUT;

wire SHIFT_REG_CLK_en;

wire SHIFT_REG_CLK_G;

wire SHIFT_REG_CLK;

wire CLK_OUT_source;

wire CLK_OUT_en;

wire CLK_OUT_G;

reg ShiftReg_SCAN_OUT_lockup;

reg SE_SLOW_CLK;

always @ (negedge SLOW_CLK) begin

SE_SLOW_CLK <= {SE_SLOW_CLK,SCAN_EN};

end

tessent_sync_cell sync_cell (.d(SE_SLOW_CLK), .clk(FAST_CLK), .q(SCAN_EN_sync));

assign SHIFT_REG_CLK_en = TEST_MODE & ShiftReg_EN & ~SCAN_EN_sync;

tessent_cgc cgc_SHIFT_REG_CLK

(.clk(FAST_CLK), .fe(SHIFT_REG_CLK_en), .te(1'b0), .clkg(SHIFT_REG_CLK_G));

tessent_clk_mux clock_mux_SHIFT_REG_CLK

(.a(SHIFT_REG_CLK_G), .b(SLOW_CLK), .s(SCAN_EN | ~FAST_CAP_MODE), .y(SHIFT_REG_CLK));

always @ (negedge SHIFT_REG_CLK) begin

ShiftReg_SCAN_OUT_lockup <= ShiftReg_SCAN_OUT;

end

assign SCAN_OUT = ShiftReg_SCAN_OUT_lockup & SCAN_EN;

assign CLK_OUT_en = ShiftReg_SCAN_OUT & (~FAST_CAP_MODE | SHIFT_REG_CLK_en) & TEST_MODE;

tessent_clk_mux clock_mux_CLK_OUT_source

(.a(FAST_CLK), .b(SLOW_CLK), .s(TEST_MODE & ~FAST_CAP_MODE), .y(CLK_OUT_source));

tessent_cgc cgc_CLK_OUT

(.clk(CLK_OUT_source), .fe(CLK_OUT_en), .te(1'b0), .clkg(CLK_OUT_G));

tessent_clk_mux clock_mux_CLKP (.a(CLK_OUT_G), .b(SLOW_CLK), .s(SCAN_EN), .y(CLK_OUT));

tessent_atpg_cc_shift_reg ShiftReg

(.CLK(SHIFT_REG_CLK), .SCAN_EN(SCAN_EN), .CAP_CYCLE_CONFIG(CAP_CYCLE_CONFIG),

.EN(ShiftReg_EN), .SCAN_IN(SCAN_IN), .SCAN_OUT(ShiftReg_SCAN_OUT));

endmodule

module tessent_cgc (clk, te, fe, clkg);

input clk, te, fe;

output clkg;

wire te_fe;

reg latch;

assign te_fe = te | fe;

always @ (clk or te_fe) begin

if (~clk) latch <= te_fe;

end

assign clkg = clk & latch;

endmodule

Mentor Graphics Confidential 12 September 2013

module tessent_sync_cell (d, clk, q);

input d, clk;

output q;

reg [1:0] R;

always @ (posedge clk) begin

R <= {R[0],d};

end

assign q = R[1];

endmodule

module tessent_clk_mux (a, b, s, y);

input a, b, s;

output y;

assign y = (s) ? b : a;

endmodule

module tessent_atpg_cc_shift_reg (CLK, SCAN_EN, CAP_CYCLE_CONFIG, EN, SCAN_IN, SCAN_OUT);

input CLK, SCAN_EN, SCAN_IN;

input [1:0] CAP_CYCLE_CONFIG;

output EN, SCAN_OUT;

reg [3:0] FF;

wire [3:0] FFD;

wire CAP_CONFIG_3, CAP_CONFIG_2, CAP_CONFIG_1;

always @ (posedge CLK) begin

FF <= FFD;

end

assign FFD[3] = SCAN_EN & SCAN_IN;

assign FFD[2] = (CAP_CONFIG_3 | CAP_CONFIG_2 | CAP_CONFIG_1) ? FFD[3] : FF[3];

assign FFD[1] = ( CAP_CONFIG_2 | CAP_CONFIG_1) ? FFD[3] : FF[2];

assign FFD[0] = ( CAP_CONFIG_1) ? FFD[3] : FF[1];

assign CAP_CONFIG_3 = (CAP_CYCLE_CONFIG == 2'b10);

assign CAP_CONFIG_2 = (CAP_CYCLE_CONFIG == 2'b01);

assign CAP_CONFIG_1 = (CAP_CYCLE_CONFIG == 2'b00);

assign EN = |FF;

assign SCAN_OUT = FF[0];

endmodule

RTL Change History

Version 1.0 – Initial release

Version 1.1 – Retiming flop on trailing edge of SLOW_CLK added in front of SCAN_EN

synchronization cell

Version 1.2 – Added AND gate on SCAN_OUT to keep scan path quiet when SCAN_EN=0

Mentor Graphics Confidential 13 September 2013

3. Test Case Description

In the test case that accompanies this application note, Tessent Shell is used for pattern generation, EDT

IP creation and hardware insertion. A test case which implements the clock controller design in this

application note has been verified with tool version v2013.3 and is available from Mentor Graphics (see

section 1 for download link). The following section describes the test case in more detail.

3.1. Test Case Design Statistics

The example design used in this test case has the following characteristics:

Gates: 10k

Clocks: 3 internal clocks

Scan chains: 12

o 11 design chains

o 1 clock control condition bits

Scan flops: 446

Total faults: 48k

Test Coverage:

o Stuck-at: ~99%

o Transition: ~93%

3.2. Directory Structure

The test case directory contains the following directories

design

o edt_created

Verilog, dofiles, and procedure files generated during EDT IP creation

o gates

Gate-level netlist

Synthesized clock controller

o rtl

clock_controller

Clock controller RTL

Simulation test benches and scripts

Synthesis script

pll

Simple RTL simulation model

dofiles

o Command dofile

o Test procedure file

o Clock control definitions for slow and fast capture (tool-generated)

library

o liberty

Liberty file

o synopsys

Compiled synthesis library file t18.db is not shipped with this test case due to

licensing agreements but should be placed in this directory for use by various

synthesis steps. The t18.db file can be created from the supplied liberty file

(t18.lib) using Synopsys’ lc_shell library compiler.

o tessent

Tessent cell library

o verilog

Simulation library

logfiles

Mentor Graphics Confidential 14 September 2013

o Generated log files

patterns

o Generated pattern files

3.3. Test Case Steps

Step 1

o Generate baseline stuck-at and transition patterns on original test case with top-level

clocks

Step 2

o Insert clock control logic and PLL

Steps 3 – 5

o Create and simulate patterns with internal clocks (slow and fast capture)

Steps 6 – 7

o Create, insert, and synthesize EDT hardware

Steps 8 – 10

o Create and simulate compressed patterns with internal clocks (slow and fast capture)

3.4. RTL Simulation

Before synthesizing the clock controller RTL, it can be simulated to ensure clock pulses are generated as

expected. To run the simulation, execute the following scripts in the design/rtl/clock_controller

directory.

run_vsim_slow_capture

run_vsim_fast_capture

For slow capture test, the test bench in the referenced directory sets the CAP_CYCLE_CONFIG signals

to 01 and loads the condition bits to generate a single clock pulse during capture. The waveform for slow

capture test is shown in Figure 10.

Figure 10 – RTL Simulation Results for Slow Capture Test

Mentor Graphics Confidential 15 September 2013

For the fast capture test example, the CAP_CYCLE_CONFIG value is set to 11 and condition bits are

setup to create 2 fast clock pulses during capture on CLK_OUT in the second and third cycles. The

waveform for fast capture test is shown in Figure 11.

Figure 11 – RTL Simulation Results for Fast Capture Test

3.5. RTL Synthesis

After verification, the RTL is synthesized using a Design Compiler synthesis script in the

design/rtl/clock_controller directory:

run_synthesis

This will run a simple synthesis based on the ADK library and create the following gate-level netlist:

design/gates/clock_controller_gate.v

NOTE: The compiled synthesis library file t18.db is not shipped with this test case due to licensing

agreements but should be placed in the library/synopsys directory for use by various synthesis

steps. The t18.db file can be created from the supplied liberty file (t18.lib) using Synopsys’ lc_shell

library compiler.

3.6. Baseline ATPG

Before inserting the clock controller into the design, you can run ATPG in Tessent Shell to get the

baseline test coverage nubmers for stuck-at and transition test. To run the baseline ATPG, execute the

following script:

01.atpg_pre_clock_control

The baseline stuck-at test coverage is ~99% while transition fault test coverage is ~99%.

3.7. Clock Control Logic Insertion

The next step is to run Tessent Shell and insert an instance of the clock control logic for each top-level

clock. At the same time, we’ll insert a PLL to provide an internal fast clock for at-speed test. Execute the

following script to insert the clock control logic:

02.insert_clock_control

See the insertion dofile for details of various commands in Tessent Shell for insertion and design editing.

Mentor Graphics Confidential 16 September 2013

#! /bin/sh -f

#\

exec tessent -shell -log logfiles/$0.log -replace -dofile "$0"

###################################################################

## SCRIPT TO INSERT PLL AND CLOCK CONTROLLER INTO A DESIGN

## TESSENT VERSION 2013.3

###################################################################

###################################################################

## UPDATE FOLLOWING VARIABLE VALUES TO MATCH THE DESIGN

## ADD/REMOVE CLOCKS AS NEEDED

###################################################################

set var_pre_cc_netlist design/gates/cpu_scan_pre_clock_control.v

set var_cell_library library/tessent/adk.tessent_cell

set var_cc_netlist design/gates/clock_controller_gate.v

set var_cc_module tessent_atpg_clock_controller

User-defined

set var_pll_module pll

set var_clock(1) clk1 design

set var_clock(2) clk2 parameters

set var_clock(3) clk3

set var_scan_enable test_se

set var_scan_group_name grp1

###################################################################

## UPDATE FOLLOWING VARIABLE VALUES TO SPECIFY DESIRED NAMES

###################################################################

set var_post_cc_netlist design/gates/cpu_scan_cc.v

set var_slow_clock slow_clock

set var_ref_clock reference_clock

User-defined

set var_cap_config cap_cycle_config naming

set var_fast_cap_mode fast_capture_mode

preferences

set var_test_mode test_mode

set var_scan_in SI_control

set var_scan_out SO_control

###################################################################

set num_clocks [array size var_clock]

set_context dft -no_rtl

read_verilog $var_pre_cc_netlist

read_verilog $var_cc_netlist

# Read cell library to allow creation of some instances such as muxes

read_cell_library $var_cell_library

set_system_mode insertion

set_current_design $var_top_module

# Create top-level ports for new signals

create_port $var_slow_clock -direction input

create_port $var_ref_clock -direction input

create_port $var_cap_config[1:0] -direction input

create_port $var_fast_cap_mode -direction input

create_port $var_test_mode -direction input

create_port $var_scan_in -direction input

create_port $var_scan_out -direction output

# Create instance of PLL and define I/O (module will be excluded from output netlist)

# If PLL already exists in design, remove or modify this section as necessary

create_module $var_pll_module

create_instance pll_i -of_module $var_pll_module

create_pin pll_i/reference_clock -direction input

create_pin pll_i/pll_clock_270 -direction output

Mentor Graphics Confidential 17 September 2013

create_pin pll_i/pll_clock_180 -direction output

create_pin pll_i/pll_clock_90 -direction output

create_pin pll_i/pll_clock_0 -direction output

create_pin pll_i/LOCKED -direction output

create_connection $var_ref_clock pll_i/reference_clock

# Create instances of clock controller and connect

for {set i 1} {$i <= $num_clocks} {incr i} {

create_instance clock_control_i$i -of_module $var_cc_module

}

create_connection pll_i/pll_clock_180 [get_pins clock_control_i*/FAST_CLK]

create_connection $var_fast_cap_mode [get_pins clock_control_i*/FAST_CAP_MODE]

create_connection $var_slow_clock [get_pins clock_control_i*/SLOW_CLK]

create_connection $var_test_mode [get_pins clock_control_i*/TEST_MODE]

create_connection $var_scan_enable [get_pins clock_control_i*/SCAN_EN]

for {set i 1} {$i <= $num_clocks} {incr i} {

create_connection $var_cap_config clock_control_i$i/CAP_CYCLE_CONFIG

}

# Concatenate condition bit shift registers into new scan chain

create_connection $var_scan_in clock_control_i1/SCAN_IN

for {set i 1} {$i < $num_clocks} {incr i} {

create_connection clock_control_i$i/SCAN_OUT clock_control_i[expr $i + 1]/SCAN_IN

}

create_connection clock_control_i$num_clocks/SCAN_OUT $var_scan_out

# Create instances of muxes to switch between PLL and clock controller clocks

for {set i 1} {$i <= $num_clocks} {incr i} {

create_instance MX$i -of_module mux21

move_connection -from $var_clock($i) -to MX$i/Y

create_connection clock_control_i$i/CLK_OUT MX$i/A1

}

create_connection $var_test_mode [get_pins MX*/S0]

create_connection pll_i/pll_clock_180 [get_pins MX*/A0]

# Remove the original top-level clock pins

for {set i 1} {$i <= $num_clocks} {incr i} {

delete_ports $var_clock($i)

}

write_design -output_file $var_post_cc_netlist -exclude_modules "$var_cc_module \

$var_pll_module" -replace

# Create dofile to define internal clocks & test procedure file for clock control defs

source dofiles/procedures.tcl

create_pre_drc_dofile $var_cc_module $var_pll_module $var_fast_cap_mode $var_slow_clock \

$var_ref_clock var_clock $var_test_mode $var_scan_enable $var_cap_config \

$var_scan_group_name $var_scan_in $var_scan_out

create_ccds $var_cc_module $var_slow_clock

exit -force

3.8. Slow Capture ATPG

To run pattern generation for slow capture, execute the following script at the top directory:

03.atpg_slow_capture

3.8.1. ATPG Commands

The script sets an environment variable for slow capture test and launches Tessent Shell with the

necessary commands. Contents of this and other included dofiles are shown here:

#! /bin/sh -f

#\

Mentor Graphics Confidential 18 September 2013

exec tessent -shell -log logfiles/$0.log -replace -dofile "$0"

setenv atpg_mode slow_capture

set_context patterns -scan

read_verilog design/gates/cpu.v

read_cell_library library/tessent/adk.tessent_cell

set_current_design 1

# Define scan chains

add_scan_group grp1 dofiles/atpg.testproc

dofile dofiles/scan_setup.dofile

dofile dofiles/pre_drc.dofile 2

# Run Design Rule Checks

set_system_mode analysis 3

# Read Clock Control Definitions

read_procfile dofiles/$env(atpg_mode).ccd

# Run ATPG

create_patterns 4

# Save pattern

report_patterns > patterns/patterns_report_$env(atpg_mode).txt

write_patterns patterns/pat1_$env(atpg_mode)_parallel.v -verilog -parallel -replace

set_pattern_filtering –sample 2

write_patterns patterns/pat1_$env(atpg_mode)_serial.v -verilog -serial -replace

exit

scan_setup.dofile

# Define external clocks

add_clocks 1 rst_in

2.1

# Define input constraints

add_input_constraints -c1 rst_in

# Define scan chains

add_scan_chains c1 grp1 test_si1 test_so1

add_scan_chains c2 grp1 test_si2 test_so2

add_scan_chains c3 grp1 test_si3 test_so3 2.2

add_scan_chains c4 grp1 test_si4 test_so4

add_scan_chains c5 grp1 test_si5 test_so5

add_scan_chains c6 grp1 test_si6 test_so6

add_scan_chains c7 grp1 test_si7 test_so7

add_scan_chains c8 grp1 test_si8 test_so8

add_scan_chains c9 grp1 test_si9 test_so9

add_scan_chains c10 grp1 test_si10 test_so10

add_scan_chains c11 grp1 test_si11 test_so11

pre_drc.dofile

add_black_box -module pll

if {$env(atpg_mode) == "slow_capture"} {

# Slow-Speed Capture Test Mode

add_input_constraints -c0 fast_capture_mode

} elseif {$env(atpg_mode) == "fast_capture"} { 3.1

# At-Speed Capture Test Mode

add_input_constraints -c1 fast_capture_mode

set_fault_type transition -no_shift_launch

set_output_masks on 3.2

add_input_constraints -all -hold

set_external_capture_options -capture_procedure ext_fast_cap_proc

add_clocks 0 clock_control_i1/cgc_SHIFT_REG_CLK/clkg -internal -free_running \

-pin_name int_clkg_1

add_clocks 0 clock_control_i2/cgc_SHIFT_REG_CLK/clkg -internal -free_running \

-pin_name int_clkg_2

add_clocks 0 clock_control_i3/cgc_SHIFT_REG_CLK/clkg -internal -free_running \

-pin_name int_clkg_3

}

add_clocks 0 clock_control_i1/CLK_OUT -internal -pin_name int_clk1

Mentor Graphics Confidential 19 September 2013

add_clocks 0 clock_control_i2/CLK_OUT -internal -pin_name int_clk2

add_clocks

add_clocks

0

0

clock_control_i3/CLK_OUT -internal -pin_name int_clk3

slow_clock

3.3

add_clocks 0 reference_clock -free_running

add_input_constraints -c1 test_mode

add_input_constraints -c0 test_se

# Define number of shift registers per clock controller 3.4

# cap_cycle_config value Maximum clock pulses

# 00 1

# 01 2

# 10 3

# 11 4 3.5

add_input_constraints -c1 cap_cycle_config[0]

add_input_constraints -c1 cap_cycle_config[1]

3.6

add_scan_chains clock_control_chain grp1 SI_control SO_control

The dofile first reads the netlist and cell library files [1] and sets the current design to the top module in

the design. The next step [2] is to define the original scan structure of the design (prior to clock control

logic insertion). In section [2.1], the external reset is defined and constrained and section [2.2] defines the

original scan chains in the design.

Command [3] calls the dofile that was generated during clock control logic insertion to setup the new scan

chain as well as ATPG commands for slow and fast capture.

The conditional section at the top of the generated dofile [3.1] defines settings specific to each test mode.

For slow capture test, only the proper constraint for at_speed_capture_mode is needed. For fast capture

[3.2], transition test ATPG commands (fault type, mask PO, hold PI) are defined. Additionally, an external

capture procedure (ext_fast_cap_proc) is defined to ensure proper pulses on external clocks are written

to the pattern file. This step also defines the output of the internal clock gates used for fast capture as

free-running internal clocks. Note that internal clocks are defined with the –pin_name switch in order to

create short aliases for use in the test procedure file.

Section [3.3] defines the internal clocks on the output pin of the clock control logic (CLK_OUT) as shown

in Figure 2.

Section [3.4] adds constraints on primary input pins such as test mode and scan enable signals. The scan

enable signal must be constrained to its off state to ensure the two clock muxes that select

SHIFT_REG_CLK and CLK_OUT are controlled properly except during the load_unload procedure which

overrides this constraint.

The next section [3.5] adds constraints to the pins that select how many condition bits will be used and

how many will be bypassed. See section 2.6 for more details. For the purpose of this test case, the select

pins are constrained to 11 to allow use of all 4 condition bits.

The last command in pre_drc.dofile [3.6] defines the new scan chain added during clock control insertion

that contains all condition bits from the 3 clock control blocks.

After issuing the set_system_mode analysis command to run design rules checks, section [4] reads the

clock control definitions for the appropriate test mode. The clock control definitions will be discussed in

more detail when the test procedure file is described.

The tool then generates patterns, writes them to a file, and exits the tool.

3.8.2. Test Procedure File

The first part of the test procedure file is common for all test modes and is stored in the file

dofiles/atpg.testproc . The content of this file is shown below:

//

Mentor Graphics Confidential 20 September 2013

// Test Procedure File

//

set time scale 1.000000 ns ;

timeplate tmp1 =

force_pi 0 ;

measure_po 2 ;

///external clocks//////

pulse rst_in 16 32;

pulse slow_clock 16 32;

pulse reference_clock 16 32;

///internal clocks//////

pulse int_clk1 16 32;

pulse int_clk2 16 32;

pulse int_clk3 16 32;

if {$env(atpg_mode) == "fast_capture"} {

pulse int_clkg_1 16 32;

pulse int_clkg_2 16 32;

pulse int_clkg_3 16 32;

}

period 64 ;

end;

procedure test_setup =

timeplate tmp1 ;

cycle =

force test_mode 1;

pulse rst_in;

pulse slow_clock;

end;

end;

procedure shift =

timeplate tmp1 ;

cycle =

force_sci ;

measure_sco ;

pulse slow_clock;

pulse int_clk1;

pulse int_clk2;

pulse int_clk3;

end;

end;

procedure load_unload =

scan_group grp1 ;

timeplate tmp1 ;

cycle =

force test_se 1;

end;

apply shift 44;

end;

procedure external_capture ext_fast_cap_proc =

timeplate tmp1 ;

cycle =

force_pi ;

pulse slow_clock;

end;

end;

Most of the test procedure file is typical to most design. An “if” statement in the timplate checks the ATPG

mode variable and selectively defines the timing for the internal clocks which are only used for fast

capture. Additionally, the test procedure file contains the external capture procedure ext_fast_cap_proc to

ensure proper pulses on external clocks are saved to the pattern file.

Since this designs uses clock control blocks with specific condition bits to control each clock, a clock

control definition must be defined for each internal clock. This is the portion of the test procedure file

which is loaded in section [4] of the dofile using the read_procfile command. The clock control

definitions for slow capture test are shown here:

Mentor Graphics Confidential 21 September 2013

//

// Clock Control Definitions for Slow Speed Capture Test

//

clock_control "int_clk1" =

source_clock "slow_clock";

atpg_cycle 0 =

condition /clock_control_i1/ShiftReg/FF_reg[0] 1;

end; 2 1

atpg_cycle 1 =

condition /clock_control_i1/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i1/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i1/ShiftReg/FF_reg[3] 1; 3

end;

end;

clock_control "int_clk2" =

source_clock "slow_clock";

atpg_cycle 0 =

condition /clock_control_i2/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i2/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i2/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i2/ShiftReg/FF_reg[3] 1;

end;

end;

clock_control "int_clk3" =

source_clock "slow_clock";

atpg_cycle 0 =

condition /clock_control_i3/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i3/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i3/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i3/ShiftReg/FF_reg[3] 1;

end;

end;

A clock control definition is needed for each internal clock. The first line of the clock control definition [1]

refers to the internal clock port defined using the add_clocks command. Note the short aliases defined

with the –pin_name switch are used here.

The second line [2] refers to the top-level source clock which must be pulsed during each capture cycle

when the internal clock is being pulsed.

The third section of the clock control definition [3] defines the scan cell (condition bit) which must be

loaded with the specified value in order to pulse the internal clock during that cycle. Once the ATPG tool

has determined the required clock pulse sequence to detect faults, it will load the appropriate condition

bits during scan chain loading.

Mentor Graphics Confidential 22 September 2013

3.9. Fast Capture ATPG

Fast capture ATPG is very similar to the slow capture flow described in the previous section. To run

pattern generation for fast capture, execute the following script at the top directory:

04.atpg_fast_capture

The conditional statement at the beginning of the file will execute the following commands

# At-Speed Capture Test Mode

add_input_constraints -c1 fast_capture_mode

set_fault_type transition -no_shift_launch 1

set_output_masks on

add_input_constraints -all -hold

set_external_capture_options -capture_procedure ext_fast_cap_proc

add_clocks 0 clock_control_i1/cgc_SHIFT_REG_CLK/clkg \

-internal -free_running -pin_name int_clkg_1

add_clocks 0 clock_control_i2/cgc_SHIFT_REG_CLK/clkg \

-internal -free_running -pin_name int_clkg_2

add_clocks 0 clock_control_i3/cgc_SHIFT_REG_CLK/clkg \ 2

-internal -free_running -pin_name int_clkg_3

After constraining the fast capture mode pin and setting the fault type, the dofile masks primary output

pins and holds the primary input pins. This is typical since most testers cannot change or observe I/O

value fast enough for fast capture test.

The set_external_capture_cycles command is issued [1] to ensure all patterns will pulse SLOW_CLK.

This ensures the scan enable synchronization circuitry described in section 2.3 is properly initialized thus

correctly controlling the clock for the condition bits. Note that this command only impacts how patterns are

saved and does not change the simulation during DRC or ATPG. This approach reduces simulation run

time while ensuring the patterns work correctly during Verilog simulation.

The last section [2] adds internal free-running clocks on the output of the clock gater cell that generates

SHIFT_REG_CLK for the shift regiser (see Figure 2). This elimniates stability issues during DRC which

result from the scan enable synchronization circuit described in section 2.3.

As noted in the previous section, the same test procedure file is used for slow and fast capture test with

the exception of the clock control definitions. The clock control definitions for fast clock capture are shown

below:

//

// Clock Control Definitions for Fast Speed Capture Test

//

clock_control "int_clk1" =

atpg_cycle 0 =

condition /clock_control_i1/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i1/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i1/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i1/ShiftReg/FF_reg[3] 1;

end;

end;

clock_control "int_clk2" =

atpg_cycle 0 =

condition /clock_control_i2/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i2/ShiftReg/FF_reg[1] 1;

Mentor Graphics Confidential 23 September 2013

end;

atpg_cycle 2 =

condition /clock_control_i2/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i2/ShiftReg/FF_reg[3] 1;

end;

end;

clock_control "int_clk3" =

atpg_cycle 0 =

condition /clock_control_i3/ShiftReg/FF_reg[0] 1;

end;

atpg_cycle 1 =

condition /clock_control_i3/ShiftReg/FF_reg[1] 1;

end;

atpg_cycle 2 =

condition /clock_control_i3/ShiftReg/FF_reg[2] 1;

end;

atpg_cycle 3 =

condition /clock_control_i3/ShiftReg/FF_reg[3] 1;

end;

end;

Note that the only difference is the lack of the source_clock statements at the beginning of each clock

control defintion. A source clock is not necessary because the source clock for fast capture mode

(reference_clock) is already defined as a free-running clock and will be pulsed in every capture cycle.

For more information on definition and use of clock control definitions in Tessent ATPG tools, see the

Tessent Shell User’s Manual.

3.10. Pattern Verification

The next step is to simulate the generated patterns to ensure no mismatches exist. The following script

simulates serial and paralel Verilog test benches in various test modes:

05.simulate_patterns

The script compiles the design, library, and patterns using ModelSim and verifes that all patterns (serial

and parallel) simulate with no mismatches. The simulation waveform for slow capture pattern number 1 is

shown in Figure 12:

Figure 12 – Pattern Simulation Results for Slow Capture Test

The last 3 signals are the output of the clock control blocks which show a single pulse on the output of

clock_control_i2/CLK_OUT. This can also be seen in the output of the report_patterns command

which is stored in the file patterns/patterns_report_sa.txt . The content of this file for the first few

pattersn is shown here:

//

// pattern # type cycles loads ... capture_clock_sequence

// --------- ------- ------ ----- ---------------------------------------------

// 0 basic 1 1 [slow_clock,reference_clock,int_clk2]

// 1 basic 1 1 [slow_clock,reference_clock,int_clk2]

// 2 basic 1 1 [slow_clock,reference_clock,int_clk3]

Mentor Graphics Confidential 24 September 2013

// 3 basic 1 1 [slow_clock,reference_clock,int_clk1]

// 4 basic 1 1 [slow_clock,reference_clock,int_clk2]

// 5 basic 1 1 [slow_clock,reference_clock,int_clk2]

As shown in the waveform, pattern number 0 pulses the top level slow_clock, reference_clock, and

internal clock 2.

Similar observations can be made for fast capture pattern number 0 which pulses in_clk2 followed by

int_clk2 . The waveform for this pattern is shown in Figure 13:

Figure 13 – Pattern Simulation Results for Fast Capture Test

The corresponding report_patterns output is shown below:

//

// pattern # type cycles loads ... capture_clock_sequence

// --------- ------- ------ ----- --------------------------------------

// 0 clock_sequential 2 1

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 1 clock_sequential 2 1

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 2 clock_sequential 2 1

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 3 clock_sequential 2 1

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 4 clock_sequential 2 1

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

// 5 clock_sequential 2 1

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

[reference_clock,int_clk2,int_clkg_3,int_clkg_2,int_clkg_1]

3.11. Compression Logic Insertion and ATPG

The next steps in the test case use Tessent Shell to create and insert EDT compression logic [step 6] and

to synthesize the created RTL with Design Compiler [step 7]:

06.create_edt_ip

07.synthesize_edt_ip

The IP creation step runs Tessent Shell with slow clock and fast clock setup files in order to automatically

create the ATPG files for both clock speeds. Since only one compression hardware design file is needed,

only the IP creation step with slow clock writes the compression hardware to a file. This file is synthesized

in step 7.

NOTE: The compiled synthesis library file t18.db is not shipped with this test case due to licensing

agreements but should be placed in the library/synopsys directory for use by various synthesis

steps. The t18.db file can be created from the supplied liberty file (t18.lib) using Synopsys’ lc_shell

library compiler.

Mentor Graphics Confidential 25 September 2013

The next step is to create compressed patterns using the slow and fast capture clocks [steps 8 & 9]:

08.atpg_edt_slow_capture

09.atpg_edt_fast_capture

The final step is to simulate the compressed patterns to ensure no mismatches exist. Script 10 simulates

all compressed patterns:

10.simulate_edt_patterns

To obtain the complete test case for the flow described in this application note, use the download link in

section 1 of this document.

Mentor Graphics Confidential 26 September 2013

Appendix A – Using OCC in an LPCT flow

1. Introduction

The clock controller described in the appnote above cannot be used as -is when using the LPCT

controllers. This is because the LPCT controllers make use of post-shift and pre-shift cycles to separate

synchronously generated cycles. All three LPCT controllers are also capable of generating a capture

enable signal that can be used as a trigger for the capture cycles independent of scan enable.

A complete test case that demonstrates the use of this clock control design in a circuit is described in the

last section. The test case is available from Mentor Graphics by downloading it from the following

SupportNet page:

2. Clock Control Circuit Description

2.1. Design Placement

In order to avoid delay on the clock path due to test logic, a multiplexer should already exist on the clock

source to the core flops and timed for functional behavior. It is important to only balance the functional

clock path of the mux in order to avoid over-constraining the clock tree synthesis flow and causing

excessive clock latency. For example, if using a layout tool like ICCompiler, this can be accomplished by

using a set_clock_tree_exceptions -exclude_pins command and listing slow and fast clock inputs of

the clock control block. In tools such as Talus from Magma, a skew group definition for each clock control

block can be used.

The mux should be controlled by the test mode signal as shown in Figure 1.

Figure 14 – Clock Control Logic Design Placement

The clock control design described in this application note should supply the clock when in test mode

while using the clock output of the PLL as the fast clock for at-speed capture. A top-level slow clock will

be used for shift and slow capture. The reference clock supplied to the PLL is a free-running clock. The

slow clock to the OCC logic is the same frequency as the LPCT clock and must also be aligned with the

shift clock in the design.

It is also recommended not to flatten the clock control blocks during layout in order to keep the test

procedure file definition easier post layout.

2.2. Schematic

The schematic for the clock control circuit is shown in Figure 2 and the corresponding RTL can be found

in section 2.9 of this document.

Mentor Graphics Confidential 27 September 2013

Figure 15 – Clock Control Logic Schematic

The following table describes the functionality of pins at the top of the clock control block as well as some

of the internal signals:

Name Direction Description

Scan enable driven by LPCT_SHIFT_EN signal

SCAN_EN Input

generated by LPCT controller

Capture enable signal driven by LPCT_CAPTURE_EN

CAPTURE_EN Input

signal generated by LPCT controller

Configures number of clock pulses during capture cycle

CAP_CYCLE_CONFIG [1:0] Input (maximum clock pulses = CAP_CYCLE_CONFIG + 1)

as well as length of scan chain during shift

SCAN_IN Input Scan chain input for loading shift register

FAST_CAP_MODE Input Selects fast or slow capture clock (0 = slow, 1 = fast)

Selects test or functional mode (0 = functional, 1 = test).

TEST_MODE Input During functional mode, the clock control block is

disabled to minimize power and cross talk.

FAST_CLK Input Clock for fast capture (typically output of PLL)

SLOW_CLK Input Clock to be used for shift and slow capture

SCAN_OUT Output Scan chain output for unloading shift register

CLK_OUT Output Controlled clock output

CAPTURE_EN_sync Internal Synchronized capture enable

SHIFT_REG_CLK_en Internal Clock enable signal for shift register

SHIFT_REG_CLK Internal Clock source for shift register

CLK_OUT_source Internal Clock source for controlled clock output

CLK_OUT_en Internal Clock enable signal for controlled clock output

Static signals that do not change during the test session can be controlled through on-chip controllers

(such as JTAG) or other means in order to reduce the need for top-level pins.

Mentor Graphics Confidential 28 September 2013

2.3. Capture Enable Synchronization

In order to synchronize the capture enable signal that is generated by the LPCT controller with the fast

clock (PLL output), a two-flop synchronization cell is used and clocked by FAST_CLK. This is important

because capture enable is used as the trigger signal to gate the clock to the shift register. The output of

the synchronization cell produces an enable signal which is synchronized with the fast clock

(CAPTURE_EN_sync) and can be used during fast capture test.

Note that this synchronization logic is not used for slow capture mode which uses SLOW_CLK for shift

and capture.

In the RTL description, the synchronization cell is described as module “tessent_sync_cell” so that it can

be replaced with a technology specific synchronization cell from the appropriate library.

module tessent_sync_cell (d, clk, q);

input d, clk;

output q;

reg [1:0] R;

always @ (posedge clk) begin

R <= {R[0],d};

end

assign q = R[1];

endmodule

In order to ensure proper DRC analysis and simulation, the output of the clock gater cell driven by the

synchronization logic should be defined as a free-running internal clock. This is indicated by an arrow in

Figure 2 and ensures correct simulation of the logic during load_unload and avoids DRC violations.

2.4. Clock Gater Cells

The clock control circuit uses two clock gater cells to gate the clock for sequential elements inside and

outside the circuit. Similar to the synchronization cell, the clock gater cells are described as module

“tessent_cgc” so that they can be replaced with technology specific clock gater cells.

module tessent_cgc (clk, te, fe, clkg);

input clk, te, fe;

output clkg;

wire te_fe;

reg latch;

assign te_fe = te | fe;

always @ (clk or te_fe) begin

if (~clk) latch <= te_fe;

end

assign clkg = clk & latch;

endmodule

2.5. Clock Definition for ATPG

In the ATPG dofile, the output of the clock control logic block should be defined as an internal clock

source as shown in Figure 2. For example:

add_clocks 0 /clock_control_i/CLK_OUT –internal

With this specification, both shift and capture clocks are supplied to the design at this location which

means the internal clock should be specified in capture as well as shift procedures.

Mentor Graphics Confidential 29 September 2013

2.6. Shift Register Block

Figure 16 – Shift Register Block Schematic

The shift register block contains the programmable scan cells which will be loaded during shift in order to

pulse the internal clock during the cycle required by ATPG.

The AND gate on the input of the shift register loads zeros into the register during capture to clear it. The

EN output signal of the shift register block is used in the clock control block (Figure 2) to turn off the fast

clock to the shift register once the shift register has been unloaded. This ensures switching from the fast

capture clock to slow shift clock without risk of glitches and disturbing the values present in the shift

register. It also ensures that the shift register flip-flops have stable values when the ATPG tool simulates

the load_unload procedure and eliminates unnecessary DRC violations.

A lockup cell on the SCAN_OUT output of the shift register block ensures proper shift operation when

several clock control blocks are concatenated into a scan chain or when scan cells from chains with

different clocks are combined with the shift register flops. This is important because as described in

section 2.1, each clock control block forms a locally balanced clock tree which is not balanced with any

other chain segment.

A key feature of the shift register block is the ability to bypass up to 3 shift registers in order to reduce the

number of bits that must be specified in the patterns. This is done by setting the CAP_CYCLE_CONFIG

signals per the following table:

Maximum Clock Pulses

CAP_CYCLE_CONFIG[0] CAP_CYCLE_CONFIG[1]

During Capture Cycle

0 0 1

0 1 2

1 0 3

1 1 4

Limiting the number of condition bits to only those needed for the longest capture sequence reduces the

overall shift cycles as well as the number of scan bits that must be specified for each pattern. Minimizing

the number of specified scan cells per pattern will ensure the ATPG tool can provide the most efficient

pattern set as well as the highest compression ratio when using embedded compression.

Mentor Graphics Confidential 30 September 2013

In addition to limiting the overall number of specified scan cells, it is also important to limit the number of

scan cells that must be specified in each shift cycle. When using compression, the output of the

decompressor loads all chains simultaneously one shift cycle at a time. When stitching the shift register

sub-chains into the design scan chains, care should be taken to avoid the alignment of multiple condition

bits into the same shift cycle. One approach is to stitch the condition registers into an uncompressed scan

chain which is directly loaded. For designs in which all scan chains are compressed, placing condition bits

at the beginning, end or similar cell number of all scan chains should be avoided so that it is not

necessary to load many specified bits in the same shift cycle.

2.7. Clock Control Operation Modes

2.7.1. Functional Mode

When operating in functional mode (TEST_MODE = 0), all clock gaters are disabled to reduce

power.

Figure 17 – Test Mode Disabled

2.7.2. Shift Mode

During the shift cycles, (LPCT_SHIFT_EN = 1), SLOW_CLOCK is used to load/unload scan

chains which include the condition bits in ShiftReg. Note that LPCT_SHIFT_EN drives the OCC

SCAN_EN pin.

Figure 18 – Shift Mode Operation

Mentor Graphics Confidential 31 September 2013

2.7.3. Slow Capture Mode

In slow capture mode (FAST_CAP_MODE = 0), SLOW_CLOCK is used to capture data into

scan cells and to shift the condition bits in ShiftReg.

Figure 19 – Slow Capture Mode Operation

2.7.4. Fast Capture Mode

In fast capture mode (FAST_CAP_MODE = 1), FAST_CLOCK is used to capture data into scan

cells and to shift the condition bits in ShiftReg.

Figure 20 – Fast Capture Mode Operation

2.8. Timing Diagrams

The timing diagram for slow speed capture (FAST_CAP_MODE = 0) is shown in Figure 8. For this

example, CAP_CYCLE_CONFIG is set to “10” resulting in sequential depth of 3 (per table in section 2.6).

In this mode, SLOW_CLK is used for shift as well as capture. Based on condition bits loaded into the shift

register, the CLK_OUT port will generate the appropriate number of slow clock pulses.

Mentor Graphics Confidential 32 September 2013

Figure 21 – Slow Speed Capture Timing Diagram

In fast capture mode (FAST_CAP_MODE = 1) the waveforms in Figure 9 are generated. Similar to the

previous example, CAP_CYCLE_CONFIG is set to “10” here resulting in sequential depth of 3. In this

mode, the slow clock is still used for shift but the fast capture pulses on CLK_OUT are based FAST_CLK.

As shown, the scan enable signal which has been synchronized to the fast clock (CAPTURE_EN_sync) is

used to trigger the fast clock pulses on SHIFT_REG_CLK. The SHIFT_REG_CLK signal is the clock

source for the shift register containing the condition bits. Based on the condition bits loaded during shift,

the correct number of fast clock pulses will appear on CLK_OUT.

Figure 22 – Fast Capture Timing Diagram

Mentor Graphics Confidential 33 September 2013

2.9. RTL Description

The RTL description of the circuit described in this application note and used in the test case is shown in

the following section:

(* version=1.0LPCT *)

module tessent_lpct_clock_controller (FAST_CLK, SLOW_CLK, TEST_MODE, SCAN_IN, SCAN_EN,

FAST_CAP_MODE, CAP_CYCLE_CONFIG, SCAN_OUT, CLK_OUT, CAPTURE_EN);

input FAST_CLK, SLOW_CLK, TEST_MODE, SCAN_IN, FAST_CAP_MODE;

input SCAN_EN; // This pin should connect to LPCT_SHIFT_EN from LPCT hardware (or

scan enable for normal ATPG)

input CAPTURE_EN; // This pin should connect to LPCT_CAPTURE_EN from LPCT hardware (or

inverted SCAN_EN for normal ATPG)

input [1:0] CAP_CYCLE_CONFIG;

output SCAN_OUT, CLK_OUT;

wire ShiftReg_EN;

wire ShiftReg_SCAN_OUT;

wire SHIFT_REG_CLK_en;

wire SHIFT_REG_CLK_G;

wire SHIFT_REG_CLK;

wire CLK_OUT_source;

wire CLK_OUT_en;

wire CLK_OUT_G;

reg SCAN_OUT;

reg CAPTURE_EN_SLOW_CLK;

wire CAPTURE_EN_sync ;

wire SLOW_CLK_EN;

wire SLOW_CLK_G;

assign SLOW_CLK_EN = TEST_MODE & (SCAN_EN | CAPTURE_EN) ;

always @ (negedge SLOW_CLK) begin

CAPTURE_EN_SLOW_CLK <= CAPTURE_EN;

end

tessent_sync_cell sync_cell

(.d(CAPTURE_EN_SLOW_CLK), .clk(FAST_CLK), .q(CAPTURE_EN_sync));

assign SHIFT_REG_CLK_en = TEST_MODE & ShiftReg_EN & CAPTURE_EN_sync ; //FAST_CLK

should not pulse until the capture cycles

tessent_cgc cgc_SHIFT_REG_CLK

(.clk(FAST_CLK), .fe(SHIFT_REG_CLK_en), .te(1'b0), .clkg(SHIFT_REG_CLK_G));

//SLOW CLK clock gater - gates the SLOW_CLK during the dead cycles

tessent_cgc cgc_SLOW_CLK

(.clk(SLOW_CLK), .fe(SLOW_CLK_EN), .te(1'b0), .clkg(SLOW_CLK_G));

// Want the select to change before the FAST_CLK gater is enabled

tessent_clk_mux clock_mux_SHIFT_REG_CLK

(.a(SHIFT_REG_CLK_G), .b(SLOW_CLK_G), .s(~CAPTURE_EN | ~FAST_CAP_MODE), .y(SHIFT_REG_CLK));

always @ (negedge SHIFT_REG_CLK) begin

SCAN_OUT <= ShiftReg_SCAN_OUT;

end

assign CLK_OUT_en = ShiftReg_SCAN_OUT & (~FAST_CAP_MODE | SHIFT_REG_CLK_en) &

TEST_MODE ;

tessent_clk_mux clock_mux_CLK_OUT_source (.a(FAST_CLK), .b(SLOW_CLK_G), .s(TEST_MODE &

~FAST_CAP_MODE ), .y(CLK_OUT_source));

tessent_cgc cgc_CLK_OUT

(.clk(CLK_OUT_source), .fe(CLK_OUT_en), .te(1'b0), .clkg(CLK_OUT_G));

tessent_clk_mux test_clock_select_mux

(.a(CLK_OUT_G), .b(SLOW_CLK_G), .s(SCAN_EN), .y(CLK_OUT));

Mentor Graphics Confidential 34 September 2013

tessent_atpg_cc_shift_reg ShiftReg

(.CLK(SHIFT_REG_CLK), .SCAN_EN(SCAN_EN), .CAP_CYCLE_CONFIG(CAP_CYCLE_CONFIG),

.EN(ShiftReg_EN), .SCAN_IN(SCAN_IN), .SCAN_OUT(Shift

Reg_SCAN_OUT));

endmodule

module tessent_cgc (clk, te, fe, clkg);

input clk, te, fe;

output clkg;

wire te_fe;

reg latch;

assign te_fe = te | fe;

always @ (clk or te_fe) begin

if (~clk) latch <= te_fe;

end

assign clkg = clk & latch;

endmodule

module tessent_sync_cell (d, clk, q);

input d, clk;

output q;

reg [1:0] R;

always @ (posedge clk) begin

R <= {R[0],d};

end

assign q = R[1];

endmodule

module tessent_clk_mux (a, b, s, y);

input a, b, s;

output y;

assign y = (s) ? b : a;

endmodule

module tessent_atpg_cc_shift_reg (CLK, SCAN_EN, CAP_CYCLE_CONFIG, EN, SCAN_IN, SCAN_OUT);

input CLK, SCAN_EN, SCAN_IN;

input [1:0] CAP_CYCLE_CONFIG;

output EN, SCAN_OUT;

reg [3:0] FF;

wire [3:0] FFD;

wire CAP_CONFIG_3, CAP_CONFIG_2, CAP_CONFIG_1;

always @ (posedge CLK) begin

FF <= FFD;

end

assign FFD[3] = SCAN_EN & SCAN_IN;

assign FFD[2] = (CAP_CONFIG_3 | CAP_CONFIG_2 | CAP_CONFIG_1) ? FFD[3] : FF[3];

assign FFD[1] = ( CAP_CONFIG_2 | CAP_CONFIG_1) ? FFD[3] : FF[2];

assign FFD[0] = ( CAP_CONFIG_1) ? FFD[3] : FF[1];

assign CAP_CONFIG_3 = (CAP_CYCLE_CONFIG == 2'b10);

assign CAP_CONFIG_2 = (CAP_CYCLE_CONFIG == 2'b01);

assign CAP_CONFIG_1 = (CAP_CYCLE_CONFIG == 2'b00);

assign EN = |FF;

assign SCAN_OUT = FF[0];

endmodule

RTL Change History

Version 1.0LPCT – Initial release of LPCT compatible OCC

Mentor Graphics Confidential 35 September 2013

3. Test Case Description

There are two test cases that accompany this application note appendix. Tessent Shell is used to insert

the OCC logic, perform scan insertion and TestKompress and LPCT logic generation and insertion and

finally to generate patterns for the design.

3.1. Test Case Design Statistics

The example design used in this test case has the following characteristics:

Gates: 23k

Clocks: 1 internal clocks

Scan chains: 35

o 34 design chains

o 1 clock control condition bits chain

Scan flops: 4004

Total faults: 93k

Test Coverage:

o Stuck-at: ~94%

o Transition: ~88%

3.2. Directory Structure

The test case directory contains the following directories

NETLISTS

o Gate-level netlist of clock controller (clock_controller_gates.v)

o Synthesized non-scan netlist (core_noscan.v)

o Synthesized netlist with PLL and OCC inserted (core_scan_occ.v)

o Backup of synthesized EDT and LPCT logic inserted netlist (create_edt_top_gate.v)

PLL_lib

o Verilog simulation model of PLL

ADK3

o liberty

Liberty file

o synopsys

Compiled synthesis library file t18.db is not shipped with this test case due to

licensing agreements but should be placed in this directory for use by various

synthesis steps. The t18.db file can be created from the supplied liberty file

(t18.lib) using Synopsys’ lc_shell library compiler.

o Verilog Simulation library (adk.v)

o Library files for DFT (adk.atpg)

RTL

o RTL of clock controller (clock_controller_rtl.v)

0_insertion

o Run script to insert OCC, PLL and scan chains in the design (run_test_logic_insertion)

o Run script to synthesize LPCT and TK logic after logic creation (synthesize)

o dofiles

Command file /dofile to perform PLL and OCC insertion and scan insertion

(test_logic_insertion.dofile)

Test procedure file to trace subchains in OCC (occ.testproc)

o generated

Mentor Graphics Confidential 36 September 2013

ATPG dofile generated by Tessent Scan (core_scan.dofile)

ATPG test procedure file generated by Tessent Scan (core_scan.testproc)

1_tk_logic_generation

o Run script to insert TK and LPCT logic in the design (run_tk_lpct_logic_generation)

o dofiles

Command file /dofile to perform TK and LPCT logic insertion (tk_lpct_gen.dofile)

o generated

LPCT and TK logic RTL files and synthesis scripts generated by Tessent

TestKompress

Synthesized netlist with LPCT and TK logic post-synthesis (core_edt_top_gate.v)

2_tk_pattern_generation

o Run script to generate patterns in the design (run_tk_patgen)

o Run script to simulate generated patterns in ModelSim (sim_patterns)

o dofiles

Command file /dofile to perform pattern generation

(pattern_generation_edt.dofile)

Pattern parameter file (paramfile)

Command file/dofile generated by Tessent TestKompress (core_edt.dofile)

Test procedure file generated by Tessent TestKompress (core_edt.testproc)

Clock control definitions for FAST_CAP_MODE=0 (slow_clk.ccd)

Clock control definitions for FAST_CAP_MODE=1 (fast_clk.ccd)

o generated

Verilog testbench and patterns generated by Tessent TestKompress

3.3. Test Case Steps

Step 1

o Insert clock control logic and PLL into design and perform scan insertion

Step 2

o Generate and insert LPCT and TK logic into design

Step 3

o Synthesize the generated LPCT and TK RTL from Step 2

Steps 4 - 7

o Create and simulate patterns for the design with internal clocks (slow and fast capture)

(change the environment variable FAST_OR_SLOW_CAPTURE to “fast” or “slow” as

needed).

3.4. RTL Synthesis

The OCC RTL can be synthesized using the Design Compiler synthesis script in the RTL directory:

synthesize_occ

This will run a simple synthesis based on the ADK library and create the following gate-level netlist:

clock_controller_gates.v

Mentor Graphics Confidential 37 September 2013

NOTE: The compiled synthesis library file t18.db is not shipped with this test case due to licensing

agreements but should be placed in the library/synopsys directory for use by various synthesis

steps. The t18.db file can be created from the supplied liberty file (t18.lib) using Synopsys’ lc_shell

library compiler.

3.5. Test logic and clock control insertion

The next step is to run Tessent Shell and insert an instance of the clock control logic for each top-level

clock. At the same time, we’ll insert a PLL to provide an internal fast clock for at -speed test. Execute the

following script in the 0_insertion subdirectory to insert the clock control logic, PLL and insert scan chains

in the design:

run_test_logic_insertion

See the insertion dofile for details of various commands in Tessent Shell for insertion and design editing.

//*****************************************************************************************

// Read in design files and libraries.

//*****************************************************************************************

// Read in the library and design.

set_context dft -no_rtl

read_cell_library ../ADK3/adk.atpg

read_verilog ../PLL_lib/PLL_stub.v

read_verilog ../NETLISTS/core_noscan.v

read_verilog ../NETLISTS/clock_controller_gates.v

set_current_design top

// Add a black box for the PLL.

add_black_box -modules { PLL }

add_clock 0 port_clock

add_clocks 1 por

add_pin_constraints por C1

set clock_names {port_clock}

//*****************************************************************************************

// Insert an OCC into the design.

//*****************************************************************************************

source ../TCL/insertion_procs.tcl

//

// Setting variable values

//

set var_scan_enable SCAN_EN

set var_slow_clock port_clock

set var_fast_clock i_PLL/VCO_4

set var_cap_cycle_config "11"

set var_fast_cap_mode "1"

set var_capture_en "0"

set pll_module PLL

set reference_clock port_clock

set slow_clock_pin port_clock

set pll_clock_port i_PLL/VCO_4

set fast_cap_mode_pin FAST_CAP_MODE

set test_mode_pin TEST_MODE

set_system_mode insertion

puts "## TCL NOTE: Inserting PLL in design"

insert_pll $pll_module $reference_clock

puts "## TCL NOTE: PLL inserted in design"

set num_clock_controllers [llength clock_names]

puts "## TCL NOTE: Inserting $num_clock_controllers clock controller(s) in the design"

insert_occ $clock_names $pll_clock_port $fast_cap_mode_pin $test_mode_pin $slow_clock_pin

$var_scan_enable