Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

1control Unit Hard and Micro

Caricato da

Karthik RajanDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

1control Unit Hard and Micro

Caricato da

Karthik RajanCopyright:

Formati disponibili

Datorarkitektur I Fö 11- 1 Datorarkitektur I Fö 11- 2

Let’s Have a Look into the CPU

THE CONTROL UNIT I/O I/O I/O

1 2 n

System Bus

1. Why is a Control Unit Needed inside the CPU?

Main

CPU

Memory

2. Microoperations and Control Signals

3. The Control Unit - Basic Tasks

System Bus

CPU

4. Hardwired Control

Registers

5. Microprogrammed Control

ALU

Address Bus

Control Bus

Data Bus

IR

PC

Control

Unit

Internal

CPU Bus

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 3 Datorarkitektur I Fö 11- 4

Instruction Execution

Let’s Have a Look into the CPU (cont’d)

• The CPU executes a sequence of instructions.

• The execution of an instruction is organized as an

instruction cycle: it is performed as a succession of

several steps;

The question that has to be answered:

• How are the elements inside the CPU and the

Fetch

interface to the external datapath controlled in order instruction

to work properly?

Execute

To perform this control, that’s instruction

the task of the Control Unit

• Each step is executed as a set of several

microoperations.

• The task performed by any microoperation falls in

one of the following categories:

- Transfer data from one register to another;

- Transfer data from a register to an external

interface (system bus);

- Transfer data from an external interface to a

register;

- Perform an arithmetic or logic operation, using

registers for input and output.

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 5 Datorarkitektur I Fö 11- 6

Instruction Execution (cont’d) Microoperations and Control Signals

PCin Control signals

In order to allow the execution of a microoperation, one

PC

Status&Cond.

or several control signals have to be issued; they allow

the corresponding data transfer and/or computation to

Flags

PCout

Control be performed.

unit

MARin

Examples:

MAR IRin

System bus

Clock

MBRin a) signals for transferring content of register R0 to R1:

IR R0out, R1in

MBR

IRout b) signals for adding content of Y to that of R0 (result in Z):

R0out, Add, Zin

MBRout R0in

Yin c) signals for reading a memory location; address in R3:

R0

R3out, MARin, Read

Clear Y

Y

R0out

• The CPU executes an instruction as a sequence of

Yout control steps. In each control step one or several

microoperations are executed.

Add

• One clock pulse triggers the activities

Rn-1in corresponding to one control step ⇒ for each

XOR ALU Carry-in clock pulse the control unit generates the control

Zin signals corresponding to the microoperations to be

Rn-1

executed in the respective control step.

Z

Zout Rn-1out

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 7 Datorarkitektur I Fö 11- 8

Microoperations and Control Signals (cont’d)

Microoperations and Control Signals (cont’d)

instruction:

ADD R1,R3 R1 ← R1 + R3 instruction:

BR target unconditional branch (with

control steps and control signals: relative addressing - see lect. 5)

PC←PC+1

fetch ins.

1 PCout, MARin, Read, Clear Y, Carry-in, Add, Zin control steps and control signals:

2 Zout, PCin

PC←PC+1

fetch ins.

3 MBRout, IRin 1 PCout, MARin, Read, Clear Y, Carry-in, Add, Zin

4 R1out, Yin 2 Zout, PCin

5 R3out, Add, Zin 3 MBRout, IRin

6 Zout, R1in, End 4 PCout, Yin

5 (displacement-field)IRout, Add, Zin

6 Zout, PCin, End

instruction:

ADD R1,(R3) R1 ← R1 + [R3]

Comments:

control steps and control signals: • The first (three) control steps are identical for each

instruction; they perform instruction fetch and

PC←PC+1

increment the PC. The following steps depend on

fetch ins.

1 PCout, MARin, Read, Clear Y, Carry-in, Add, Zin

the actual instruction (stored in the IR).

2 Zout, PCin

• If a control step issues a read, the value will be

3 MBRout, IRin

available in the MBR after one additional step.

4 R3out, MARin, Read indirect addressing

• Several microoperations can be performed in the

5 R1out, Yin same control step if they don’t conflict (for example,

6 MBRout, Add, Zin only one of them is allowed to output on the bus)

7 Zout, R1in, End

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 9 Datorarkitektur I Fö 11- 10

Control Unit Control Unit (cont’d)

The basic task of the control unit: IR

- for each instruction the control unit causes the

CPU to go through a sequence of control steps;

- in each control step the control unit issues a set Control signals in-

of signals which cause the corresponding ternal to the CPU

Status&Cond.

microoperations to be executed.

Flags

Control Control signals

unit on system bus

• The control unit is driven by the processor clock.

Signals from

The signals to be generated at a certain moment system bus

depend on:

- the actual step to be executed;

- the condition and status flags of the processor; Clock

- the actual instruction executed;

- external signals received on the system bus

(e.g. interrupt signals).

• Techniques for implementation of the control unit:

1. Hardwired control

2. Microprogrammed control

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 11 Datorarkitektur I Fö 11- 12

Hardwired Control

Hardwired Control (cont’d)

• In this case, the control unit is a combinatorial

circuit; it gets a set of inputs (from IR, flags, clock,

system bus) and transforms them into a set of

control signals. Generation of signal Zin:

- first step of all instructions (fetch instruction)

IR - step 5 of ADD with register addressing

- step 5 of BR

Instruction - step 6 of ADD with register-indirect addressing

decoder - -------------------

I1 I2 I3 In

Zin = T1 + T5 ⋅ (ADDreg + BR) + T6 ⋅ ADDreg_ind + . . .

Status&Cond.

Flags

T1

Generation of signal End:

and decoder

Reset Step counter

T2 Encoder block - step 6 of ADD with register addressing

(combinatorial signal

Clock - step 7 of ADD with register-indirect addressing

generator)

tem bus

From sys-

- step 6 of BR

Tn - -------------------

End = T6 ⋅ (ADDreg + BR) + T7 ⋅ ADDreg_ind + . . .

End

Control signals

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 13 Datorarkitektur I Fö 11- 14

Control signals

Hardwired Control (cont’d)

Status&Cond.

Flags

Control

unit

• Hardwired control provides highest speed.

Clock

• RISCs are implemented with hardwired control.

IR

• If the instruction set becomes very complex

(CISCs) implementing hardwired control is very PC

difficult. In this case microprogrammed control units

are used. R0

• In order to allow execution of register-to-register

operations in a single clock cycle, RISCs (and other

Rn-1

modern processors) use three-bus CPU structures

(see following slide).

ALU

MBR

MAR

System bus

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 15 Datorarkitektur I Fö 11- 16

Microprogrammed Control Microprogrammed Control Unit

• Control word (CW): a sequence of Nsig bits, where Status&Cond.

Nsig is the total number of control signals; each bit Flags

in a CW corresponds to one control signal.

• Each control step during execution of an instruction

defines a certain CW; it represents a combination

of 1s and 0s corresponding to the active and non-

active control signals.

• Microroutine: a sequence of CWs corresponding to Address Control

the control sequence of a machine instruction. An IR generator µPC store

individual CW in a microroutine is called a (AG) (CS)

microinstruction.

INCR

gen. addr

Microprogrammed control - basic idea: IAB

• All microroutines corresponding to the machine

Control buffer/

instructions are stored in the control store.

decoder

• The control unit generates the sequence of control (CB/D)

signals for a certain machine instruction by reading end, end-fetch

from the control store the CWs of the microroutine Clock Sequencer

branch

corresponding to the respective instruction.

Control signals

The control unit is implemented just like another Signals from

very simple CPU, inside the CPU, executing system bus

microroutines stored in the control store.

IAB: Internal Address Bus

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 17 Datorarkitektur I Fö 11- 18

Control Store Organization

Microroutine Executed for Conditional Branch

Control store

Addr-fetch

---------------------

--------------------- Fetch A_fetch PCout, MARin, Read, Clear Y, Carry-in, Add, Zin

end-fetch instruction

+1 Zout, PCin

Addr-interr. +2 MBRout, IRin

---------------------

--------------------- Interrupt

+3 end-fetch this produces the jump to A_CB

branch addr-fetch routine

--------------

Addr-instr0

--------------------- A_CB branch to A_CB+2 if N set

--------------------- Execute

instr. code 0 +1 end

end

Addr-instr1 +2 PCout, Yin

---------------------

Execute +3 (displacement-field)IRout, Add, Zin

---------------------

end instr. code 1 +4 Zout, PCin

+5 end

Addr-instrn

---------------------

Execute

---------------------

instr. code n

end • The microroutines contain, beside CWs, also

branches which have to be interpreted by the

microprogrammed controller.

• The sequencer is controlling the right execution

• The control store contains the microprogram sequence of microinstructions. The sequencer is a

(sometimes called firmware). small control unit of the control unit.

Petru Eles, IDA, LiTH Petru Eles, IDA, LiTH

Datorarkitektur I Fö 11- 19

Summary

• The control unit is in charge of coordinating the

activities inside the CPU and the interaction with

the outside. It is doing this by issuing in each clock

cycle the appropriate control signals.

• A set of control signals activates the

microoperations which have to be executed in a

given control step.

• Control units can be implemented hardwired or

microprogrammed.

• A hardwired control unit is a combinatorial circuit

which gets a set of inputs and transforms them into

a set of control signals.

• A microprogrammed control unit is implemented

like another CPU inside the CPU. It executes

microprogrammes stored in the control store.

• Each instruction of the microprogram practically

represents the set of signals which the control unit

has to issue in the respective control step.

• Hardwired controllers are faster then

microprogrammed ones. They are used in all

RISCs.

• If the instruction set is complex, hardwired

controllers become too complicated. Therefore

CISCs are implemented with microprogrammed

controllers.

Petru Eles, IDA, LiTH

Potrebbero piacerti anche

- ELEC3300 06 InterruptDocumento38 pagineELEC3300 06 InterruptKeith wongNessuna valutazione finora

- COMPORGA - Module 4Documento12 pagineCOMPORGA - Module 4Happy Feet100% (1)

- Unit 3 PLC (Programmable Logic Controller)Documento66 pagineUnit 3 PLC (Programmable Logic Controller)hicinobNessuna valutazione finora

- Computer ArchitectureDocumento3 pagineComputer ArchitectureabdallaNessuna valutazione finora

- Chapter 1 Computer ArchitectureDocumento19 pagineChapter 1 Computer ArchitectureKHAWAJA MANNANNessuna valutazione finora

- Week 3 - The Processing Unit and Input Output OrganizationsDocumento18 pagineWeek 3 - The Processing Unit and Input Output OrganizationsGame AccountNessuna valutazione finora

- Lecture Slides Chapter 1 Computer ArchitectureDocumento65 pagineLecture Slides Chapter 1 Computer ArchitectureMuhammad Sohail Younas 1Nessuna valutazione finora

- Introduction To Computer Architecture and OrganizationDocumento40 pagineIntroduction To Computer Architecture and OrganizationTawki BakiNessuna valutazione finora

- Chapter 7 - Processor Structure and FunctionDocumento23 pagineChapter 7 - Processor Structure and FunctionNUR SYAFIQAH BINTI BAIDROL AZMEE / UPMNessuna valutazione finora

- Coa Unit 1 To 04Documento118 pagineCoa Unit 1 To 04manjushkumar719Nessuna valutazione finora

- 04-CO BasicsDocumento29 pagine04-CO Basicsfakhar_fastNessuna valutazione finora

- Lecture 1 COADocumento35 pagineLecture 1 COATashinga Ryan ManunureNessuna valutazione finora

- CO1 Chapter 1 IntroductionDocumento15 pagineCO1 Chapter 1 IntroductionhudhaifaNessuna valutazione finora

- System Architecture: Ref. Computer Organization and Architecture, Stalling W.Documento40 pagineSystem Architecture: Ref. Computer Organization and Architecture, Stalling W.Priscilla Muthoni WakahiaNessuna valutazione finora

- Computer Programming Laboratory-14cpl16Documento126 pagineComputer Programming Laboratory-14cpl16Mahalakshmi ShanmugamNessuna valutazione finora

- Computer System Architecture (NCP 423) : Engr. Joan P. LazaroDocumento24 pagineComputer System Architecture (NCP 423) : Engr. Joan P. LazaroLester GimenaNessuna valutazione finora

- Computer Organization and Architecture: William StallingsDocumento78 pagineComputer Organization and Architecture: William StallingsNITHIYA PAUL 1847244Nessuna valutazione finora

- Computer Architecture and OrganisationDocumento15 pagineComputer Architecture and OrganisationArshad MohmandNessuna valutazione finora

- Microprocessors and Programming: Fall: 2021Documento50 pagineMicroprocessors and Programming: Fall: 2021Emirhan AlmaNessuna valutazione finora

- Ciclo de Búsqueda y Ejecución StallingDocumento7 pagineCiclo de Búsqueda y Ejecución StallingMatias BeneitezNessuna valutazione finora

- Computer Organization and ArchitectureDocumento13 pagineComputer Organization and ArchitectureassadNessuna valutazione finora

- Von Nuemann ArchitectureDocumento3 pagineVon Nuemann ArchitectureMuhammad UsamaNessuna valutazione finora

- Processing DeviceDocumento4 pagineProcessing DeviceKundai ChiwesheNessuna valutazione finora

- (Advanced) Computer Architechture Prof. Dr. Hasan Hüseyin BALIK (3 Week)Documento47 pagine(Advanced) Computer Architechture Prof. Dr. Hasan Hüseyin BALIK (3 Week)فقد الاحبه غربةNessuna valutazione finora

- Dpco Unit 5 Part 4Documento9 pagineDpco Unit 5 Part 4AparnaNessuna valutazione finora

- 01 IntroductionDocumento18 pagine01 Introductiondommy omosaNessuna valutazione finora

- Computer Organization and Architecture 8 EditionDocumento15 pagineComputer Organization and Architecture 8 EditionDaWheng VargasNessuna valutazione finora

- Computer Organization & Architecture: Instructor Engr. Zeeshan RazaDocumento35 pagineComputer Organization & Architecture: Instructor Engr. Zeeshan RazaMeena ShahNessuna valutazione finora

- Computer Organization and StructureDocumento49 pagineComputer Organization and Structurebong_blue2k6Nessuna valutazione finora

- BBA - HM - III CA Unit 1Documento13 pagineBBA - HM - III CA Unit 1Sanika AgrawalNessuna valutazione finora

- CH 01 - OS8eDocumento59 pagineCH 01 - OS8emyzalNessuna valutazione finora

- Version 2 EE IIT, Kharagpur 1Documento15 pagineVersion 2 EE IIT, Kharagpur 1ahamed100% (1)

- Computer Organization and Architecture: Julius BancudDocumento36 pagineComputer Organization and Architecture: Julius BancudRed StreakNessuna valutazione finora

- Computer-System StructuresDocumento37 pagineComputer-System StructuresHamoodi AlmayahiNessuna valutazione finora

- Lect 02 PDFDocumento26 pagineLect 02 PDFVijendra PandeyNessuna valutazione finora

- Mba (1 Semester) Computer Fundamental Mba Unit - I: Secondary StorageDocumento12 pagineMba (1 Semester) Computer Fundamental Mba Unit - I: Secondary Storageshashi shekhar dixitNessuna valutazione finora

- William Stallings Computer Organization and ArchitectureDocumento15 pagineWilliam Stallings Computer Organization and Architecturemuzammil kibriyaNessuna valutazione finora

- 12 Simple Computer Design 2Documento17 pagine12 Simple Computer Design 2WikiNessuna valutazione finora

- CH 1 3.ppt Type IDocumento71 pagineCH 1 3.ppt Type Ilaraibnawaz86Nessuna valutazione finora

- Computer Organization and Architecture: 06 Jumada II, 1440 Tuesday, 12 February 2019Documento15 pagineComputer Organization and Architecture: 06 Jumada II, 1440 Tuesday, 12 February 2019muhammad farooqNessuna valutazione finora

- Computer Structure and ComponentsDocumento18 pagineComputer Structure and Componentsapi-3801329100% (1)

- Chapter 01 IntroductionDocumento14 pagineChapter 01 IntroductionALEMU DEMIRACHEWNessuna valutazione finora

- Computer System ArchitectureDocumento27 pagineComputer System ArchitectureAvigyan BasuNessuna valutazione finora

- The Control Unit Unit 4Documento18 pagineThe Control Unit Unit 4SongYak YamNessuna valutazione finora

- ESY LEC01 ComputerArchitectureDocumento54 pagineESY LEC01 ComputerArchitectureThomNessuna valutazione finora

- D02 HardwareDocumento27 pagineD02 Hardwarechuong NguyenNessuna valutazione finora

- Infoplc Net Chap2 SDocumento28 pagineInfoplc Net Chap2 SVishwendra SahuNessuna valutazione finora

- COMPUTER ARCHITECTURE ch-1Documento38 pagineCOMPUTER ARCHITECTURE ch-1Tolera TamiruNessuna valutazione finora

- The Central Processing UnitDocumento17 pagineThe Central Processing UnitGetaye AysheshimNessuna valutazione finora

- Session1-CPU OrganizationDocumento11 pagineSession1-CPU OrganizationHillary MurungaNessuna valutazione finora

- ch01 ComputerBasic PDFDocumento131 paginech01 ComputerBasic PDFAbdreyll GerardNessuna valutazione finora

- Vision de Alto Nivel Del Computador V5 PDFDocumento52 pagineVision de Alto Nivel Del Computador V5 PDFGARY DAVID TRUJILLO MOTATO100% (1)

- Module 1 - IntroductionDocumento20 pagineModule 1 - IntroductionLikhithapNessuna valutazione finora

- Computer Organization and Architecture: Chapter 1 - Introduction Sameer AkramDocumento21 pagineComputer Organization and Architecture: Chapter 1 - Introduction Sameer AkramMuhammad Tariq RanaNessuna valutazione finora

- Introduction Lec 1Documento14 pagineIntroduction Lec 1Mehmood KhanNessuna valutazione finora

- CompArch 01 IntroductionDocumento80 pagineCompArch 01 Introductionmilkii kasayeNessuna valutazione finora

- Intro - Comp ArchDocumento17 pagineIntro - Comp ArchEphraimNessuna valutazione finora

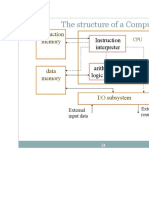

- The Structure of A ComputerDocumento4 pagineThe Structure of A ComputerNgeiNessuna valutazione finora

- Theory Universalism - Andrew FaridaniDocumento2 pagineTheory Universalism - Andrew FaridaniUmar YaqoobNessuna valutazione finora

- What Are The Similarities Between The Management Thoughts of Taylor and FayolDocumento1 paginaWhat Are The Similarities Between The Management Thoughts of Taylor and FayolUmar YaqoobNessuna valutazione finora

- Collegeresult - Islamia College of Science and CommerceDocumento3 pagineCollegeresult - Islamia College of Science and CommerceUmar YaqoobNessuna valutazione finora

- Form No Roll No Name UG Points Entrance Points Total Points General Merit ListDocumento2 pagineForm No Roll No Name UG Points Entrance Points Total Points General Merit ListUmar YaqoobNessuna valutazione finora