Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Mipsology Aws f1

Caricato da

hiperboreoatlantecCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Mipsology Aws f1

Caricato da

hiperboreoatlantecCopyright:

Formati disponibili

Mipsology:

The Future of FPGA-Based

Machine Learning

Abstract

A.I. is an exploding market, projected to grow at a compound annual rate of 62.9 percent from

2016 to 2022. Neural networks are in greater demand than ever, appearing in an ever-growing

range of consumer electronics. Even so, the processing demands of Deep Learning and inference

exceed the capacity of traditional CPUs and GPUs – and the shortfall becomes even more

pronounced at scale, in data centers. FPGAs, by contrast, are already used in many data centers,

and measure up to the processing demands of Deep Learning and inference – but until now,

Mipsology SAS © 2017 zebra@mipsology.com Page | 1

Mipsology: The Future of

FPGA-Based Machine Learning

they’ve been very difficult to use without expertise.

Mipsology’s team of expert founders, leveraging more than 20 years of

experience designing high-performance electronic systems, have brought the

cutting-edge technology of FPGA-based acceleration to bear on neural network

processing, delivering a fully integrated FPGA replacement for GPUs, which

works seamlessly and easily with all neural networks, and is ready-made for use in

data centers.

Why use an FPGA for Your Neural Network Inference?

Machine learning is moving from GPU to FPGA… and momentum is growing.

Field Programmable Gate Array components (FPGAs) have already proven to be the

fastest, most flexible, power-efficient chips on the market.

That means they’re ideally suited to be used in data centers, especially in the fast-moving

world of machine learning.

FPGA is crucial for Deep Learning

Demand for Deep Learning continues to skyrocket, spurring the development of a variety of new

technologies. Some of these applications are very visible – for example, the self-driving car. Others, such

as speech recognition and face recognition, are less obvious, but nonetheless essential to our daily lives.

Many more exist to serve specialized but important verticals, such as identifying cancers on medical

images, identifying breaches into computer networks, adapting efficiently power consumption in data

centers, attempting to predict election results, or improving the internet ad profiling.

Deep Learning is a method of computerized learning performed by neural networks, which are simplified

mathematical simulations of how brains function. By looking at many examples or associations, the neural

network is able to “learn” connections and relationships much more quickly than a traditional recognition

program could.

For example, a neural network might listen to many vocal samples, and use Deep Learning to learn to

“recognize” the sounds of specific words. This neural network could then sift through a list of brand-new

vocal samples, and correctly identify the samples containing the words it has learned, using a technique

called inference.

Even the simplest neural network requires a tremendous amount of mathematical “heavy lifting.” Deep

Learning requires an even greater number of calculations, and the computing demands of inference are

greater still. This is because, whereas Deep Learning typically only needs to be performed one single time,

a neural network must perform inference again and again, for each new sample it receives.

Mipsology SAS © 2017 zebra@mipsology.com Page | 2

Mipsology: The Future of

FPGA-Based Machine Learning

The fact that many popular applications use inference to

perform common tasks like speech recognition and image tagging – millions

upon millions of times every day – highlights an obvious need for a categorical

upgrade in computing power.

The future of Deep Learning is on FPGA

We founded Mipsology in 2015 to deliver fully integrated solutions that accelerate the

computing of Deep Learning and inference. Our focus has always been to deliver full solutions for

data centers, with the goal of supporting very large loads and high throughput. Rather than

attempting to accelerate one neural network for a single application, our technology, called Zebra,

can accelerate all neural networks for all applications – effectively replacing the GPUs currently used

by most scientists.

Mipsology’s founders bring together more than 20 years of experience designing high performance

systems based on many FPGAs. In the past, several of our team members led the design of multiple

emulators for high-speed ASIC verification, based on

thousands of Xilinx FPGAs.

In January 2017, our team demonstrated Zebra

executed on a KU115 – showcasing the fastest 100

percent FPGA-based solution computing any neural

network inference (as far as we’ve been able to

determine).

We ported Zebra to AWS in just two months, and will

soon offer access to our Zebra f1 implementation on

AWS Marketplace. In Q2, we will support all

convolutional neural networks (CNN) similar to

AlexNet and GoogLeNet, delivering inference

performance reaching 4000 images per second and

more than 100 images per second per watt. We will

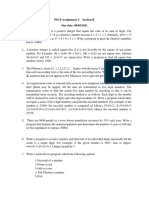

also add support for Caffe and MXNET infrastructures, Figure 1: Mipsology Zebra general flow. The GPU is replaced by

so our users will never have to worry about their an FPGA when performing inference in the same infrastructure.

FPGAs running “undercover.”

In the near future, we’ll continue to add new features that deliver stronger performance, while supporting

more Deep Learning infrastructures and innovations.

FPGA solves your toughest Deep Learning processing challenges

Traditional central processing units (CPUs), while very flexible, fail to measure up in high-demand

computing tasks of Deep Learning and inference. Many neural network developers quickly recognized

this, and switched to graphics processing units (GPUs), which allow more computation bandwidth, at the

cost of decreased flexibility.

Mipsology SAS © 2017 zebra@mipsology.com Page | 3

Mipsology: The Future of

FPGA-Based Machine Learning

This trade-off worked reasonably well at first – but it, too, didn’t

last for long. As neural networks continued to increase in complexity,

demanding ever more calculation bandwidth, even GPUs reached the limits of their

abilities. GPUs also turned out to present other problems as well: they consume quite

a bit of power and demand a lot of cooling, making them less-than-ideal for

deployment in the data centers used in big-data cloud applications.

In fact, while custom ASICs may seem to present an ideal solution, they also create significant

challenges for data centers. For one thing, ASICs are not yet available in any data center. If

available, they must comply with data centers’ strict requirements in order to be deployed, which will

be another challenge before large adoption. But mainly, they are highly dedicated to a specific task,

which makes them even less flexible than CPU, GPU and FPGA.

Developing a specific ASIC takes several years – but the Deep Learning and neural network fields are

evolving rapidly, with ongoing breakthroughs making last year’s technology irrelevant. Plus, in order

to compete with a CPU or a GPU, an ASIC would need to use a large silicon area using with the thinner

manufacturing technology. This makes the upfront investment expensive, without any guarantee of long-

term relevancy. The neural network field evolves rapidly, and the acceleration provided by a given ASIC

may not always be as powerful as that of an equivalent GPU, CPU or FPGA.

Many of these challenges have already been solved by FPGAs.

An FPGA is programmable at the hardware level, making it highly parallel, to a greater degree than a CPU

or a GPU. FPGAs use less power than a GPU or CPU, and are proven to comply with data center

requirements. Unlike a specialized ASIC, an FPGA is hardware programmable, permitting acceleration of

many different loads, and enabling quick updates to accelerate new neural network architectures without

having to wait for the next ASIC to be released. It’s true that, until very recently, FPGAs lacked high

computation bandwidth – but that has changed. In 2017, the two major FPGA design companies are

releasing the most powerful FPGAs so far, which offer computation bandwidth equivalent to that of a

GPU, with the additional potential to use the millions of logic cells and flip-flops necessary to match the

requirements of a neural network.

Design and Methodology

How we chose our FPGA

Our choice of FPGA has been driven by our design goal: to create a neural network computation system

that can run any neural network and reach the highest potential performance on a single FPGA.

Several research teams have concluded that high GPU precision is not required for high accuracy in neural

network computation. In other words, it’s possible to obtain accurate results using fixed-point 16 bits, 8

bits, or even fewer. Thus, although we do support 32-bit floating-point calculation as a reference when

comparing results to GPU, our focus has been to design a system that values performance over precision.

Mipsology SAS © 2017 zebra@mipsology.com Page | 4

Mipsology: The Future of

FPGA-Based Machine Learning

By the same token, we value fixed-point throughput over

floating-point. While Intel’s Stratix-10 GX2800, for example, natively supports

floating-point calculations in the silicon, the fixed-point Xilinx Ultra-Scale Plus

VU13P actually offers more fixed-point calculations per cycle, thanks to a higher

number of DSPs.

Of course, maximum frequency must also be considered, because higher frequency

correlates with high performance. While some FPGAs may run faster than others, the constraint

of fitting into a data center requires to tightly control the power then to limit the frequency.

Since even a higher-frequency FPGA would also be subject to the same power constraints, frequency

was not a differentiator in our choice of FPGA.

FPGA Intel Stratix-10 GX2800 Xilinx VU9P Xilinx VU13P

DSP 5,760 (11,520 mult) 6,840 12,288

Boolean Logic 2,753k LE 2,586k LC 3,780k LC

Flip-Flops 3,732k 2,592k 3,456k

Table 1 : Logic available in newest FPGA

Over time, the performance and functionality of Intel’s and Xilinx’s FPGAs will continue to improve, which

may lead to a different choice. In all cases, we are convinced that next generations, with more DSP and

logic, will offer even better solution for neural network in data centers. However, with our current

considerations in mind, and current components available, we chose the Xilinx KU115 as the basis for

developing a prototype of the system, and the Xilinx VU9P and VU13P as targets for our production FPGA.

HLS vs. RTL, and OpenCL vs. PCIe

For a while, Xilinx and Intel are pushing the use of high-level synthesis (HLS) to design FPGA content. One

goal is to allow a wider audience to develop FPGA content, particularly software developers who can write

C/C++ code. When the goal is to create a design utilizing a lot of arithmetic, HLS allows design at a higher

level of abstraction than register-level transfer (RTL). This can reduce the coding effort. However, if the

goal is to push global performance as high as possible, HLS may fall short. Using RTL to design, on the

other hand, allows for finer control of the implementation result, at the potential cost of a longer design

time. Since our goal is to reach the highest possible performance, we decided to use RTL coding.

OpenCL is a framework for writing programs that execute across heterogeneous platforms. On a typical

PC, this allows programs to transfer data over a PCIe bus without going into low-level details – which

means OpenCL enables heterogeneous platforms to get up and running more quickly, with less coding

effort from the developer.

However, like any generic solution, OpenCL may lack the highest throughput desirable for certain specific

solutions. Because we sought the highest possible performance, we decided to invest in writing our own

SW/HW interface.

In short, no perfect solution exists – it’s all a matter of choosing the right trade-offs.

Mipsology SAS © 2017 zebra@mipsology.com Page | 5

Mipsology: The Future of

FPGA-Based Machine Learning

We can imagine that a larger developer community will drive

HLS and OpenCL to close the performance gap eventually. For those who are

new to FPGA and acceleration, or those who want to design quickly with fewer

performance requirements, both these options are probably equally good choices.

We’ve already solved the architecture and performance challenges

A growing number of companies are adding FPGAs to their data centers, for the primary reason

of increasing calculation throughput. This means computation performance is the most important

driver in FPGA choice (typically followed by the drive to reduce power consumption). In certain

applications, the latency offered by FPGA could also be a primary driver, like in fast-trading and

more generally financial markets. But in most application, the computation acceleration justifies by

itself the use of FPGA.

Thus, while it’s mandatory to utilize the highest possible number of digital signal processors (DSPs)

at high frequency, it’s equally important to feed each DSP with data. In particular, the ways in which look

up tables (LUT), flip-flops and memories are used around DSPs create significant impacts on eventual

performance. These facts drove many of our architecture decisions. Google, in its recent article, provides

some interesting related information. If some may see specific ASIC as superior for performance, the

architectural choice also impacts them greatly. Google’s TPU, for example, has a low actual MAC utilization

rate with an average of 23% (and as low as 6.3% on one of the neural network used to measure

performance). This does not differ for FPGA: the architecture can drastically impact the real eventual

performance.

Our first focus was to choose between internal and external memory. While internal memory offers a

large amount of bandwidth, it has limited capacity. External memory, on the other hand, offers high

capacity at the costs of lower limited bandwidth and high latency, while also consuming more power.

Thus, we decided to avoid external memory as much as possible in our architecture.

Another challenge was to reduce the logic per DSP. There are thousands of DSPs in the FPGA, driven by

data busses. If those busses are 32-bits wide, for example, every extra LUT (flip-flop) on them costs not

one LUT (flip-flop) but thousands multiplied by 32. This significantly increases the size of the logic used.

For example, on a VU9P, the addition of a mux on each bit in front of each of the 6840 DSP costs roughly

18 percent of LUTs on the FPGA.

Thus, we defined a budget-per-bloc and per-DSP before we began coding. We also took advantage of the

large set of arithmetic operations offered by the Xilinx DSP to improve the per-cycle performance, which

a CPU or a GPU cannot offer. Aggregating the DSPs to construct larger operations, without involving extra

logic, allowed us to also reduce the logic involved for larger operations.

When coding using RTL or C, it is important to understand the results at the gate level. One may think that

the synthesizer will do one thing, but the tools will sometimes produce a different result. This may be due

to incorrect syntax, a missing option, an area optimization reducing frequency, or the opposite. However,

when one can check the synthesis result, it’s possible to compare to the budgeted size and make sure the

design will fit the targeted FPGA with the highest filling rate for each DSP, in order to obtain maximum

performance.

Mipsology SAS © 2017 zebra@mipsology.com Page | 6

Mipsology: The Future of

FPGA-Based Machine Learning

Our final focus was frequency. Utilizing all the DSP and most of

the other resources of the FPGA leads to challenging placement and routing

problems for Vivado. We believe that RTL coding is quite helpful to reach higher

frequencies – which is why we didn’t neglect this crucial step toward reaching our

performance goal.

Running your FPGA in the Cloud provides many advantages

Amazon Web Services (AWS) offers FPGA-based instances, named AWS Elastic Compute Cloud

(EC2) F1 instances, enabling users to accelerate algorithms in several advantageous ways. Each EC2

F1 instance is like a virtual PC in the cloud equipped with 1 or 8 VU9P FPGAs.

From the end user’s point of view

For end users, who are not familiar with FPGAs, but want to take advantage of their benefits, AWS

provides an easy solution of an FPGA instance in the Cloud, similar to using a GPU-based or a CPU-based

instance. This offers many benefits:

• Zero up-front cost. AWS provides access to one of the largest FPGAs, without requiring the user

to buy it before using it. The board was designed to accelerate computations, so the end-user

does not have to mind about which board is adequate.

• Hardware comes pre-installed and pre-tested. AWS has already taken care of compatibility with

the computer and OS, which can consume a lot of time and money when a PCIe board (FPGA or

otherwise) is not compatible with a certain machine.

• High hardware quality. AWS monitors the hardware on an ongoing basis, eliminating the impact

of a failing board remaining undetected for a long time. If a board fails, you can simply switch to

another instance and restart your application without delay.

• Adaptable bandwidth. After starting with one FPGA, it’s easy to scale up the bandwidth without

any up-front cost – or to scale down if required. For applications with only a few hours of high

peak activity, or applications that only require a few hours on a regular basis, the average cost

will be reduced by only using the instances when required. This means there’s no need to buy

many boards to use them only sparsely.

• Simplified usage. Since many users are not FPGA specialists, and prefer to focus on their

applications more than on the FPGA, AWS provides applications that make using an FPGA as

simple as using a CPU.

From the startup’s point of view

For companies in the business of providing FPGA-based acceleration, using a FPGA in the cloud also

provides some significant advantages:

• No up-front hardware investment. If the acceleration can be performed on a generic board,

there’s no need to invest in physical hardware.

Mipsology SAS © 2017 zebra@mipsology.com Page | 7

Mipsology: The Future of

FPGA-Based Machine Learning

• Consistent, uniform hardware. Since the hardware

installed on AWS is uniform, you’ll be using the same hardware for

development, evaluation and execution. This limits compatibility issues

and risks of operating in an unknown environment, while focusing your

development on one specific platform.

• Immediate testing and evaluation. You won’t have to spend weeks, or even

months, installing software for a potential customer to evaluate. An evaluation can

start immediately on the Cloud, yet the customer can still control the pace of testing.

• No lead time for additional bandwidth. Whenever a customer needs more bandwidth, new

FPGAs are immediately available in volume – with no lead time for hardware manufacture,

and no need to call in a team to install boards (or maintain existing ones).

• No need to deal with borders, customs and shipping companies. In fact, no need to ship

hardware at all.

• Unlimited number of customers. All can share the same hardware, without a dedicated

support team to look after them.

• Automatic upgrades and deployments. AWS’s own infrastructure manages every application

upgrade, deployment and distribution.

• Much broader customer reach. Every customer can simply use the application on AWS, rather

than having to order custom hardware and/or install custom software.

However, while those benefits are significant, it does take some work to integrate AWS requirements into

the development process.

We’ve already ported Zebra to EC2 F1

Using OpenCL can significantly reduce the effort of porting to a cloud platform, because OpenCL is

designed to be portable between platforms, as long as the API is used correctly.

Whether you choose to use OpenCL or not, the principle is the same for the FPGA integration: AWS’s

Hardware Design Kit provides a shell for the FPGA. This shell is the layer around your IP, providing access

to PCIe and DDR memories. While the shell runs permanently on the EC2 F1 instance, the application the

user runs is loaded using partial reconfiguration of the FPGA. Since we’ve already tested essential blocks

and made them ready for use, running a neural network on Zebra essentially functions like running a

program on a CPU, using only about 20 percent of the FPGA’s resources.

Mipsology SAS © 2017 zebra@mipsology.com Page | 8

Mipsology: The Future of

FPGA-Based Machine Learning

Porting our application to the EC2 F1 board turned out not to

be too complex. We started from a design running on a KU115 coupled to a SW

stack under Linux, and ported them to the VU9P available on EC2 F1 instances with

our software stack, within four weeks. Adapting the design to a different FPGA was

made easy as the architecture is scalable (see Figure 2). Most of the work was focused

on bridging our control bus to the shell, and making sure that routing and timing would be

achievable.

Then, we spent another four weeks optimizing the FPGA

compiles to reach higher performances. We performed

the software porting in parallel without major issue.

Although we began with no knowledge of how to use

AWS, we found it to be very easy to use, and found the

AWS team to be very reactive and knowledgeable. They

automated the process of building the Amazon FPGA

Image (AFI) which is required to run on the EC2 F1. This

AFI cannot be accessed directly by the F1 instance user,

allowing us to protect our IP, which – along with the fact

that no one else offers cloud access to FPGA as AWS

does – was one of our most important criteria in

choosing AWS. Figure 2: Zebra architecture in the AWS Shell

Next, we actually ran our design and debug it. For newbies – who most likely use HLS design – this can be

a shock. The High-Level Synthesis tool significantly transforms the source code, resulting in a low-level

gate netlist. Nothing looks like software debug anymore. Instead, it is millions of gates executed in parallel,

which are typically debugged with waveforms.

Benefits of running Mipsology Zebra on FPGAs in your data center

Every Cloud-based FPGA designed by Mipsology processes over 24,000 operations at a time. It works

with all neural networks, boasting compatibility with any typical CNN or RNN. It requires, from the user,

no FPGA knowledge, no FPGA tool knowledge, no hardware knowledge; in fact, the user can just forget

there is an FPGA. It runs on “standard” PCIe board ready to be used in data centers. It’s also low power,

consuming 6 times less power than an equivalent GPU.

Plus, since Mipsology provides FPGAs as Software as a Service (SaaS) for data centers, you’ll save

significant overhead on servers, software licenses and staff. All you’ll have to do is to connect to the

Cloud and start running your neural networks.

Mipsology SAS © 2017 zebra@mipsology.com Page | 9

Mipsology: The Future of

FPGA-Based Machine Learning

Data Center Benefits

Mipsology Zebra runs in high density in data centers, without

consuming excess power. The hardware works seamlessly with the

data center’s loads, and complies with all the usual HVAC requirements.

Neural Network Technology Benefits

Mipsology Zebra doesn’t require any FPGA-related knowledge from the end user. It is

already integrated with deep learning infrastructures, which means it can simply

replace your existing GPU without any changes. Mipsology Zebra will also support

new neural network technologies more quickly than a GPU as the same silicon can be

reprogrammed at the hardware level to accommodate new needs, no re-spin, no new

silicon, no tape-in tape-out delays, acceleration can be made available in few weeks.

Performance and Power Benefits

Mipsology Zebra boast higher performance than equivalent CPUs or GPUs. It will pass 100

images/s/W in 2017 in comparison to only 14.2 images/s/W from the newest GPU. As the

power used is lower than GPU, having 8 boards per host is simple, allowing to increase the

density of computation in data center with hundreds thousand images per host within a

slim power budget below 700W. They support various precisions, and can even handle

other processing demands on the same FPGA.

Cost Benefits Using AWS and Zebra

Mipsology Zebra runs on AWS EC2 F1 which is available with no upfront cost to the user. As

switching to Zebra can be done in minutes, there is no engineering cost related to changing

the neural networks or the code in place for GPU or CPU. The billing being done per hour,

the hardware and software costs can be adapted to the real loads and needs, so no

hardware is sitting in a computer doing nothing. No need to mind about availability,

hardware compatibility, hardware support and failures, depreciation, deployment, IT costs,

all that is made transparent and managed by AWS. You’ll be able to use the same hardware

for inference and learning, all for a smaller R&D budget than ever before.

Mipsology stands at the forefront of FPGA-based machine learning. In

terms of cost, power, flexibility and adaptability, the answer to your

Deep Learning challenges is clear: Mipsology Zebra.

Ludovic Larzul, Founder and CEO of Mipsology

www.mipsology.com

zebra@mipsology.com

Mipsology SAS © 2017 zebra@mipsology.com Page | 10

Potrebbero piacerti anche

- Applsci 12 10771 v2Documento44 pagineApplsci 12 10771 v2Amit JainNessuna valutazione finora

- High Performance FPGA Based CNN AcceleratorDocumento4 pagineHigh Performance FPGA Based CNN AcceleratorInternational Journal of Innovative Science and Research TechnologyNessuna valutazione finora

- Deep Learning On Modern CpusDocumento11 pagineDeep Learning On Modern CpusGary Ryan DonovanNessuna valutazione finora

- FPGA Frontiers - Digital Book PDFDocumento87 pagineFPGA Frontiers - Digital Book PDFkocekoNessuna valutazione finora

- Introduction To Hardware Accelerator Systems For Artificial Intelligence and Machine LearningDocumento21 pagineIntroduction To Hardware Accelerator Systems For Artificial Intelligence and Machine LearningRAMISHNessuna valutazione finora

- Chameleon Chips Full ReportDocumento40 pagineChameleon Chips Full Reporttejaswi_manthena05Nessuna valutazione finora

- Literature Review On FpgaDocumento4 pagineLiterature Review On Fpgaafdtfhtut100% (1)

- Automates Neural Architecture ConstructionDocumento23 pagineAutomates Neural Architecture ConstructionAlex AstraNessuna valutazione finora

- New DlauDocumento52 pagineNew DlaudeepaNessuna valutazione finora

- Does Nvidia Use FPGA in Machine LearningDocumento3 pagineDoes Nvidia Use FPGA in Machine LearningjackNessuna valutazione finora

- FPGA Genreal PaperDocumento7 pagineFPGA Genreal PaperParth SomkuwarNessuna valutazione finora

- Image Hardware PDFDocumento19 pagineImage Hardware PDFJanardhan ChNessuna valutazione finora

- Inference Hardware Review by MicrosoftDocumento17 pagineInference Hardware Review by MicrosoftRonald dNessuna valutazione finora

- Design of Fpga Based General Purpose Neural Network: MR Prashant D.Deotaleproflalit DoleDocumento5 pagineDesign of Fpga Based General Purpose Neural Network: MR Prashant D.Deotaleproflalit DolePurohit Manish RNessuna valutazione finora

- Individual Paper - Nina Luksha - ITEC 625 9080 - UpdatedDocumento11 pagineIndividual Paper - Nina Luksha - ITEC 625 9080 - UpdatedzubairNessuna valutazione finora

- Chameleon Chips Full ReportDocumento38 pagineChameleon Chips Full ReportAtul VijayNessuna valutazione finora

- Term Paper On FpgaDocumento8 pagineTerm Paper On Fpgaaflsjizaf100% (1)

- Seminar ReportDocumento25 pagineSeminar Reportpratt2012Nessuna valutazione finora

- FPGA Lessons Learned: Understanding When and How to Use Field Programmable Gate ArraysDocumento5 pagineFPGA Lessons Learned: Understanding When and How to Use Field Programmable Gate ArraysCarlos Andrés Moreno PetroNessuna valutazione finora

- Chapter 1. General IntroductionDocumento5 pagineChapter 1. General IntroductionrajendraNessuna valutazione finora

- Introduction To FPGA Technology: Top 5 Benefits: 1. What Is An FPGA?Documento1 paginaIntroduction To FPGA Technology: Top 5 Benefits: 1. What Is An FPGA?ferdiNessuna valutazione finora

- We Are Intechopen, The World'S Leading Publisher of Open Access Books Built by Scientists, For ScientistsDocumento15 pagineWe Are Intechopen, The World'S Leading Publisher of Open Access Books Built by Scientists, For ScientistsPramod Reddy RNessuna valutazione finora

- Chameleon Chips Full ReportDocumento24 pagineChameleon Chips Full ReportSai Sree CharanNessuna valutazione finora

- C R A M: Ompression For EAL Time Pplications EdiaDocumento4 pagineC R A M: Ompression For EAL Time Pplications EdiaJair Vasquez RiosNessuna valutazione finora

- FPGA-Based Haar Classifier Accelerates Face DetectionDocumento11 pagineFPGA-Based Haar Classifier Accelerates Face DetectionRaymondNessuna valutazione finora

- Research Paper Based On FpgaDocumento7 pagineResearch Paper Based On Fpgakgtsnhrhf100% (1)

- Part Number List of QuickLogic PASIC 3 FPGA FamilyDocumento12 paginePart Number List of QuickLogic PASIC 3 FPGA FamilyjackNessuna valutazione finora

- ICACCI 2016: Low Cost IoT Based Image Processing Using FPGA-SoC InterfaceDocumento6 pagineICACCI 2016: Low Cost IoT Based Image Processing Using FPGA-SoC InterfaceMouna elamariNessuna valutazione finora

- Programming and Synthesis For Software-Defined FPGA Acceleration - Status and Future ProspectsDocumento39 pagineProgramming and Synthesis For Software-Defined FPGA Acceleration - Status and Future ProspectsSourabhNessuna valutazione finora

- Cpu Gpu SystemDocumento26 pagineCpu Gpu SystemsadikNessuna valutazione finora

- FPGAs in Data CentersDocumento6 pagineFPGAs in Data CentersAnthony FelderNessuna valutazione finora

- Project Proposal - Ver 1.3Documento10 pagineProject Proposal - Ver 1.3Eshaan AgarwalNessuna valutazione finora

- Hamamu ASAP 2020 Jun9Documento8 pagineHamamu ASAP 2020 Jun9amanNessuna valutazione finora

- Chameleon Chips Full ReportDocumento39 pagineChameleon Chips Full ReportVivek AnanthNessuna valutazione finora

- Digital Logic & Design DA-1: Datacenters Integrates An FPGA Into A Unique Distributed ArchitectureDocumento2 pagineDigital Logic & Design DA-1: Datacenters Integrates An FPGA Into A Unique Distributed ArchitectureyashNessuna valutazione finora

- FPGA Vs Micro ControlDocumento11 pagineFPGA Vs Micro ControlsenthilvlNessuna valutazione finora

- AI AcceleratorDocumento5 pagineAI AcceleratorRama DeviNessuna valutazione finora

- Chameleon Chips Seminar Report 09Documento39 pagineChameleon Chips Seminar Report 09mhdbasheerNessuna valutazione finora

- Start:Fpgas vs. DSPS: A Look at The Unanswered QuestionsDocumento4 pagineStart:Fpgas vs. DSPS: A Look at The Unanswered QuestionsŽele ZekaNessuna valutazione finora

- Thesis Gpu ProgrammingDocumento6 pagineThesis Gpu Programmingcynthiasmithmanchester100% (2)

- An Implementation of Convolutional Neural NetworksDocumento23 pagineAn Implementation of Convolutional Neural NetworksRishima SardaNessuna valutazione finora

- FPGA Technology and Its Role in Electronics Engineering in Nepal July 3, 2013Documento4 pagineFPGA Technology and Its Role in Electronics Engineering in Nepal July 3, 2013Gaihre KrishnaNessuna valutazione finora

- Latest Research Paper On FpgaDocumento5 pagineLatest Research Paper On Fpgapykig1nupyf3100% (1)

- Security of Cloud FPGA SurveyDocumento32 pagineSecurity of Cloud FPGA SurveyZia JoeNessuna valutazione finora

- What Is An FPGA?Documento4 pagineWhat Is An FPGA?SUNILPATRONessuna valutazione finora

- What Is FPGA and Why Should You CareDocumento6 pagineWhat Is FPGA and Why Should You CarejackNessuna valutazione finora

- Image Processing Using FPGADocumento12 pagineImage Processing Using FPGAMehanathan Maggie MikeyNessuna valutazione finora

- Autoencoders: Parallel Programming Parallel ProcessingDocumento5 pagineAutoencoders: Parallel Programming Parallel ProcessingbaskarchennaiNessuna valutazione finora

- Final Report EE 498 Fall 2015Documento5 pagineFinal Report EE 498 Fall 2015AF91Nessuna valutazione finora

- Embedded Systems Design with Platform FPGAs: Principles and PracticesDa EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesValutazione: 5 su 5 stelle5/5 (1)

- Performance Evaluation of Offline Speech RecognitiDocumento16 paginePerformance Evaluation of Offline Speech RecognitiVoleti VnkumarNessuna valutazione finora

- An FPGA-Based Solution For A Graph Neural Network AcceleratorDocumento9 pagineAn FPGA-Based Solution For A Graph Neural Network Acceleratorjohn BronsonNessuna valutazione finora

- Fpga Thesis IdeasDocumento5 pagineFpga Thesis Ideasafcmausme100% (1)

- Edge DetectionDocumento9 pagineEdge Detectionabinabin2Nessuna valutazione finora

- 10 1109@vlsi-Dat49148 2020 9196288Documento1 pagina10 1109@vlsi-Dat49148 2020 9196288Gauswami HirvaNessuna valutazione finora

- Thesis FpgaDocumento7 pagineThesis FpgaWriteMyPaperCanada100% (2)

- TigerGraph Buyers Guide Part 1Documento8 pagineTigerGraph Buyers Guide Part 11977amNessuna valutazione finora

- A Deep Learning Prediction Process Accelerator Based FPGA PDFDocumento4 pagineA Deep Learning Prediction Process Accelerator Based FPGA PDFBoppidiSrikanthNessuna valutazione finora

- Gpu Computing ThesisDocumento6 pagineGpu Computing Thesiswyppfyhef100% (2)

- m18qwg Global Lte Kit HW Ug v1 4Documento52 paginem18qwg Global Lte Kit HW Ug v1 4hiperboreoatlantecNessuna valutazione finora

- Eame 2015 Xilinx Paper v1 8Documento6 pagineEame 2015 Xilinx Paper v1 8hiperboreoatlantecNessuna valutazione finora

- pg202 Mipi DphyDocumento87 paginepg202 Mipi DphyhiperboreoatlantecNessuna valutazione finora

- Xapp894 D Phy SolutionsDocumento24 pagineXapp894 D Phy SolutionshiperboreoatlantecNessuna valutazione finora

- Imagenet ClassificationDocumento9 pagineImagenet Classificationice117Nessuna valutazione finora

- Wp502 PythonDocumento12 pagineWp502 PythonhiperboreoatlantecNessuna valutazione finora

- Deep Learning XilinxDocumento11 pagineDeep Learning XilinxhiperboreoatlantecNessuna valutazione finora

- Global Lte Iot Starter KitDocumento2 pagineGlobal Lte Iot Starter KithiperboreoatlantecNessuna valutazione finora

- ARM-CEVA LTE-Advanced White Paper Final PDFDocumento13 pagineARM-CEVA LTE-Advanced White Paper Final PDFhiperboreoatlantecNessuna valutazione finora

- Sdaccel Development Environment: Release Notes, Installat On, and Licensing GuideDocumento28 pagineSdaccel Development Environment: Release Notes, Installat On, and Licensing GuidehiperboreoatlantecNessuna valutazione finora

- Sdaccel Development Environment: Release Notes, Installat On, and Licensing GuideDocumento28 pagineSdaccel Development Environment: Release Notes, Installat On, and Licensing GuidehiperboreoatlantecNessuna valutazione finora

- Machine Learning Application LandscapeDocumento9 pagineMachine Learning Application LandscapeblablablouNessuna valutazione finora

- Machine Vision XILINXDocumento4 pagineMachine Vision XILINXhiperboreoatlantecNessuna valutazione finora

- Wp493 Iiot Edge PlatformsDocumento10 pagineWp493 Iiot Edge PlatformshiperboreoatlantecNessuna valutazione finora

- Installation Guideline: Guideline For Planning, Assembling and Commissioning of Ethercat NetworksDocumento70 pagineInstallation Guideline: Guideline For Planning, Assembling and Commissioning of Ethercat NetworkshiperboreoatlantecNessuna valutazione finora

- Ethercat Ipcore Xilinx v2 04e Datasheet V1i0Documento126 pagineEthercat Ipcore Xilinx v2 04e Datasheet V1i0hiperboreoatlantecNessuna valutazione finora

- ZYBo PinesDocumento123 pagineZYBo PineshiperboreoatlantecNessuna valutazione finora

- Sdsoc Environment Tutorial: Ug1028 (V2017.1) June 20, 2017Documento64 pagineSdsoc Environment Tutorial: Ug1028 (V2017.1) June 20, 2017hiperboreoatlantecNessuna valutazione finora

- OV5640 DatasheetDocumento179 pagineOV5640 DatasheetseansinhNessuna valutazione finora

- Esquematico de ZyboDocumento14 pagineEsquematico de Zybohiperboreoatlantec100% (1)

- FPGA GigEDocumento64 pagineFPGA GigEhiperboreoatlantecNessuna valutazione finora

- Zybo-Z7 RMDocumento31 pagineZybo-Z7 RMPablo Mechon Araneda CisternaNessuna valutazione finora

- Xilinx TimingClosureDocumento31 pagineXilinx TimingClosurehiperboreoatlantecNessuna valutazione finora

- Which ARM Cortex Core Is Right For Your ApplicationDocumento5 pagineWhich ARM Cortex Core Is Right For Your ApplicationS_gabrielNessuna valutazione finora

- CM2B25 PDFDocumento169 pagineCM2B25 PDFhiperboreoatlantecNessuna valutazione finora

- Design of Arithmetic UnitsDocumento25 pagineDesign of Arithmetic UnitshiperboreoatlantecNessuna valutazione finora

- 05 Timing Clocking p6Documento11 pagine05 Timing Clocking p6Rahul BhattacharyaNessuna valutazione finora

- 05 Timing Clocking p6Documento11 pagine05 Timing Clocking p6Rahul BhattacharyaNessuna valutazione finora

- PSCP Loops ProblemsDocumento2 paginePSCP Loops ProblemsDevarapalli HarithaNessuna valutazione finora

- GCC and Make: Compiling, Linking and Building C/C++ ApplicationsDocumento11 pagineGCC and Make: Compiling, Linking and Building C/C++ ApplicationssemabayNessuna valutazione finora

- Airfiber AF-11FX UG PDFDocumento58 pagineAirfiber AF-11FX UG PDFKevin RiveraNessuna valutazione finora

- Lab 1 - Introduction To MininetDocumento26 pagineLab 1 - Introduction To MininetFerat AzizNessuna valutazione finora

- Arduino Oscilloscope Poor Mans OscilloscopeDocumento3 pagineArduino Oscilloscope Poor Mans OscilloscopeGilson BaldoNessuna valutazione finora

- NEX2U Plus Manual (Full) - DealerDocumento41 pagineNEX2U Plus Manual (Full) - DealerArbey GonzalezNessuna valutazione finora

- LSMR Engineer Alpesh Diwate Seeks New OpportunityDocumento4 pagineLSMR Engineer Alpesh Diwate Seeks New OpportunityAlpesh DiwateNessuna valutazione finora

- SMU05A V200R002C00 Site Monitoring Unit User ManualDocumento107 pagineSMU05A V200R002C00 Site Monitoring Unit User ManualAhmad ImadNessuna valutazione finora

- AR Setup ChecklistDocumento9 pagineAR Setup ChecklistDavid SparksNessuna valutazione finora

- 16-Bit Language Tools Libraries 51456FDocumento248 pagine16-Bit Language Tools Libraries 51456Fthienthuy232Nessuna valutazione finora

- 01 (17.3") Intel Shark Bay Platform Block Diagram: HaswellDocumento45 pagine01 (17.3") Intel Shark Bay Platform Block Diagram: HaswellAditya Forest ResanantaNessuna valutazione finora

- PACS Server Components: Merge Healthcare - ConfidentialDocumento26 paginePACS Server Components: Merge Healthcare - ConfidentialPrashantNessuna valutazione finora

- M3 Service BlueprintingDocumento12 pagineM3 Service BlueprintingGhiffariNessuna valutazione finora

- Astronomical Controller 5.0Documento20 pagineAstronomical Controller 5.0Everest100% (1)

- 20533D ENU TrainerHandbook PDFDocumento460 pagine20533D ENU TrainerHandbook PDFmadhan1510Nessuna valutazione finora

- Edit PDF - Free PDF Editor Working Directly in Your BrowserDocumento5 pagineEdit PDF - Free PDF Editor Working Directly in Your BrowserAbhay ThakurNessuna valutazione finora

- Data Science Terminology Flashcards - QuizletDocumento15 pagineData Science Terminology Flashcards - QuizletKonstantinos Michailidis100% (1)

- Module 5: Technology Enabled Learning & Life Long Self LearningDocumento50 pagineModule 5: Technology Enabled Learning & Life Long Self LearningChandrakant Thakare100% (2)

- El GenioDocumento242 pagineEl GenioAs PaNessuna valutazione finora

- 3gpp - SIM Application ToolkitDocumento157 pagine3gpp - SIM Application ToolkitGuru BalaguruNessuna valutazione finora

- Erp NDocumento11 pagineErp NPrateek MallNessuna valutazione finora

- SmartBus G4 IR Emitter (Data Sheet)Documento2 pagineSmartBus G4 IR Emitter (Data Sheet)Smart-G4Nessuna valutazione finora

- Owner's Manual: Wireless Music StreamerDocumento4 pagineOwner's Manual: Wireless Music StreamerJD MedinaNessuna valutazione finora

- Intro Computing Assignment 2 TipsDocumento2 pagineIntro Computing Assignment 2 TipsSiddique RanaNessuna valutazione finora

- Deployment of 200 - 400GbE Ethernet - RGBDocumento20 pagineDeployment of 200 - 400GbE Ethernet - RGBJuan Marcelo ArteagaNessuna valutazione finora

- User's Guide: Oregon Trail 5th Edition, Adventures Along The Oregon Trail - 1Documento41 pagineUser's Guide: Oregon Trail 5th Edition, Adventures Along The Oregon Trail - 1Melissa Missy SalasNessuna valutazione finora

- C Ternary OperatorDocumento4 pagineC Ternary OperatorNepal OoNessuna valutazione finora

- PIC16 (L) F1938/9 Data SheetDocumento452 paginePIC16 (L) F1938/9 Data SheetCynthia AlvarezNessuna valutazione finora

- Workflowsim: A Toolkit For Simulating Scientific Workflows in Distributed EnvironmentsDocumento8 pagineWorkflowsim: A Toolkit For Simulating Scientific Workflows in Distributed EnvironmentsSanthosh B AcharyaNessuna valutazione finora

- User's Manual: Downloaded From Manuals Search EngineDocumento69 pagineUser's Manual: Downloaded From Manuals Search Enginejnraidoo6724Nessuna valutazione finora