Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Sn74als259 PDF

Caricato da

michael luqueTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Sn74als259 PDF

Caricato da

michael luqueCopyright:

Formati disponibili

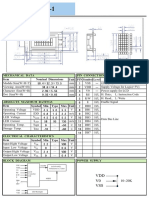

SN54ALS259, SN74ALS259

8-BIT ADDRESSABLE LATCHES

SDAS217A DECEMBER 1982 REVISED DECEMBER 1994

8-Bit Parallel-Out Storage Register SN54ALS259 . . . J PACKAGE

Performs Serial-to-Parallel Conversion With SN74ALS259 . . . D OR N PACKAGE

(TOP VIEW)

Storage

Asynchronous Parallel Clear

S0 1 16 VCC

Active-High Decoder S1 2 15 CLR

Enable/Disable Input Simplifies Expansion S2 3 14 G

Expandable for n-Bit Applications Q0 4 13 D

Four Distinct Functional Modes Q1 5 12 Q7

Q2 6 11 Q6

Package Options Include Plastic Q3 Q5

7 10

Small-Outline (D) Packages, Ceramic Chip GND Q4

8 9

Carriers (FK), and Standard Plastic (N) and

Ceramic (J) 300-mil DIPs

SN54ALS259 . . . FK PACKAGE

description (TOP VIEW)

CLR

VCC

These 8-bit addressable latches are designed for

NC

S1

S0

general-purpose storage applications in digital

systems. Specific uses include working registers, 3 2 1 20 19

serial-holding registers, and active-high decoders S2 4 18 G

or demultiplexers. They are multifunctional Q0 5 17 D

devices capable of storing single-line data in eight NC 6 16 NC

addressable latches and being a 1-of-8 decoder or Q1 7 15 Q7

demultiplexer with active-high outputs. Q2 8 14 Q6

9 10 11 12 13

Four distinct modes of operation are selectable by

Q3

Q4

Q5

NC

GND

controlling the clear (CLR) and enable (G) inputs

as shown in the function table. In the

addressable-latch mode, data at the data-in NC No internal connection

terminal is written into the addressed latch. The

addressed latch follows the data input with all unaddressed latches remaining in their previous states. In the

memory mode, all latches remain in their previous states and are unaffected by the data or address inputs. To

eliminate the possibility of entering erroneous data in the latches, G should be held high (inactive) while the

address lines are changing. In the 1-of-8 decoding or demultiplexing mode, the addressed output follows the

level of the D input with all other outputs low. In the clear mode, all outputs are low and unaffected by the address

and data inputs.

The SN54ALS259 is characterized for operation over the full military temperature range of 55C to 125C. The

SN74ALS259 is characterized for operation from 0C to 70C.

Function Tables

FUNCTION

INPUTS OUTPUT OF EACH

ADDRESSED OTHER FUNCTION

CLR G LATCH OUTPUT

H L D QiO Addressable latch

H H QiO QiO Memory

L L D L 8-line demultiplexer

L H L L Clear

D = the level at the data input.

QiO = the level of Qi (i = Q, 1, . . . 7 as appropriate) before the indicated

steady-state input conditions were established.

PRODUCTION DATA information is current as of publication date. Copyright 1994, Texas Instruments Incorporated

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 1

SN54ALS259, SN74ALS259

8-BIT ADDRESSABLE LATCHES

SDAS217A DECEMBER 1982 REVISED DECEMBER 1994

Function Tables (Continued)

LATCH SELECTION

SELECT INPUTS LATCH

S2 S1 S0 ADDRESSED

L L L 0

L L H 1

L H L 2

L H H 3

H L L 4

H L H 5

H H L 6

H H H 7

logic symbol

1

S0 0

2 0

S1 8M

3 7

S2 2

14

G G8

13

D Z9

15

CLR Z10

9, 0D 4

Q0

10, 0R

9, 1D 5

Q1

10, 1R

9, 2D 6

Q2

10, 2R

9, 3D 7

Q3

10, 3R

9, 4D 9

Q4

10, 4R

9, 5D 10

Q5

10, 5R

9, 6D 11

Q6

10, 6R

9, 7D 12

Q7

10, 7R

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the D, J, and N packages.

2 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

SN54ALS259, SN74ALS259

8-BIT ADDRESSABLE LATCHES

SDAS217A DECEMBER 1982 REVISED DECEMBER 1994

logic diagram (positive logic)

14 4

G Q0

13

D

5

Q1

1

S0

6

Q2

7

Q3

2

S1

9

Q4

10

Q5

3

S2

11

Q6

12

Q7

15

CLR

Pin numbers shown are for the D, J, and N packages.

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 3

SN54ALS259, SN74ALS259

8-BIT ADDRESSABLE LATCHES

SDAS217A DECEMBER 1982 REVISED DECEMBER 1994

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Input voltage, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Operating free-air temperature range, TA: SN54ALS259 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55C to 125C

SN74ALS259 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0C to 70C

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65C to 150C

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

recommended operating conditions

SN54ALS259 SN74ALS259

UNIT

MIN NOM MAX MIN NOM MAX

VCC Supply voltage 4.5 5 5.5 4.5 5 5.5 V

VIH High-level input voltage 2 2 V

VIL Low-level input voltage 0.7 0.8 V

IOH High-level output current 0.4 0.4 mA

IOL Low-level output current 4 8 mA

G low 20 15

tw Pulse duration ns

CLR low 10 10

Data before G 20 15

tsu Setup time ns

Address before G 20 15

Data after G 0 0

th Hold time ns

Address after G 0 0

TA Operating free-air temperature 55 125 0 70 C

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

SN54ALS259 SN74ALS259

PARAMETER TEST CONDITIONS UNIT

MIN TYP MAX MIN TYP MAX

VIK VCC = 4.5 V, II = 18 mA 1.5 1.5 V

VOH VCC = 4.5 V to 5.5 V, IOH = 0.4 mA VCC 2 VCC 2 V

IOL = 4 mA 0.25 0.4 0.25 0.4

VOL VCC = 4

4.5

5V V

IOL = 8 mA 0.35 0.5

II VCC = 5.5 V, VI = 7 V 0.1 0.1 mA

IIH VCC = 5.5 V, VI = 2.7 V 20 20 A

IIL VCC = 5.5 V, VI = 0.4 V 0.1 0.1 mA

IO VCC = 5.5 V, VO = 2.25 V 20 112 30 112 mA

ICC VCC = 5.5 V 14 22 14 22 mA

All typical values are at VCC = 5 V, TA = 25C.

The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

4 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

SN54ALS259, SN74ALS259

8-BIT ADDRESSABLE LATCHES

SDAS217A DECEMBER 1982 REVISED DECEMBER 1994

switching characteristics (see Figure 1)

VCC = 4.5 V to 5.5 V,

CL = 50 pF,

FROM TO RL = 500 ,

PARAMETER

(INPUT) (OUTPUT) TA = MIN to MAX UNIT

SN54ALS259 SN74ALS259

MIN MAX MIN MAX

tPHL CLR Any Q 2 15 2 12 ns

tPLH 4 22 4 19

Data Any Q ns

tPHL 2 15 2 12

tPLH 4 26 4 22

Address Any Q ns

tPHL 2 15 2 12

tPLH 4 22 4 20

Execute Any Q ns

tPHL 2 16 2 13

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 5

SN54ALS259, SN74ALS259

8-BIT ADDRESSABLE LATCHES

SDAS217A DECEMBER 1982 REVISED DECEMBER 1994

PARAMETER MEASUREMENT INFORMATION

SERIES 54ALS/74ALS AND 54AS/74AS DEVICES

7V

VCC RL = R1 = R2

S1

RL

R1

From Output Test From Output Test From Output Test

Under Test Point Under Test Point Under Test Point

CL RL CL

CL R2

(see Note A) (see Note A)

(see Note A)

LOAD CIRCUIT FOR

BI-STATE LOAD CIRCUIT LOAD CIRCUIT

TOTEM-POLE OUTPUTS FOR OPEN-COLLECTOR OUTPUTS FOR 3-STATE OUTPUTS

Timing 3.5 V High-Level 3.5 V

Input 1.3 V Pulse 1.3 V 1.3 V

0.3 V 0.3 V

th tw

tsu

3.5 V 3.5 V

Data Low-Level

Input 1.3 V 1.3 V 1.3 V 1.3 V

Pulse

0.3 V 0.3 V

VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES PULSE DURATIONS

3.5 V

Output

Control 1.3 V 1.3 V

(low-level

enabling) 0.3 V 3.5 V

tPZL Input 1.3 V 1.3 V

tPLZ

[3.5 V 0.3 V

tPHL

Waveform 1 tPLH

S1 Closed 1.3 V

In-Phase VOH

(see Note B) 1.3 V 1.3 V

VOL Output

tPHZ 0.3 V VOL

tPZH tPLH

VOH tPHL

Waveform 2 VOH

Out-of-Phase

S1 Open 1.3 V 0.3 V 1.3 V 1.3 V

Output

(see Note B)

[0 V (see Note C) VOL

VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS PROPAGATION DELAY TIMES

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. When measuring propagation delay items of 3-state outputs, switch S1 is open.

D. All input pulses have the following characteristics: PRR 1 MHz, tr = tf = 2 ns, duty cycle = 50%.

E. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuits and Voltage Waveforms

6 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TIs standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (CRITICAL

APPLICATIONS). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO

BE FULLY AT THE CUSTOMERS RISK.

In order to minimize risks associated with the customers applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TIs publication of information regarding any third

partys products or services does not constitute TIs approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Potrebbero piacerti anche

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- BONENT Candidate Handbook PDFDocumento28 pagineBONENT Candidate Handbook PDFParshanwa Johnson100% (1)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- UFO and PentagonDocumento69 pagineUFO and PentagonNur Agustinus100% (3)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- C TADM70 73 Sample QuestionsDocumento2 pagineC TADM70 73 Sample QuestionsPriya ChNessuna valutazione finora

- TRANSLATIONDocumento4 pagineTRANSLATIONGarren Jude Aquino100% (1)

- The Big Table of Quantum AIDocumento7 pagineThe Big Table of Quantum AIAbu Mohammad Omar Shehab Uddin AyubNessuna valutazione finora

- Chapter 2 Solutions - Power-Generation-OperationDocumento11 pagineChapter 2 Solutions - Power-Generation-OperationKleilson Chagas50% (4)

- T.D.A 1010a PDFDocumento22 pagineT.D.A 1010a PDFmichael luqueNessuna valutazione finora

- TL - 080 PDFDocumento12 pagineTL - 080 PDFmichael luqueNessuna valutazione finora

- TL081Documento10 pagineTL081miguelhm13Nessuna valutazione finora

- T.D.A 04H0SK1RDocumento1 paginaT.D.A 04H0SK1Rmichael luqueNessuna valutazione finora

- Dumisani Maths Prac AssignmentDocumento6 pagineDumisani Maths Prac AssignmentDumisani Tawanda DubeNessuna valutazione finora

- Pure Theory of Law Hans Kelson-Ltp..Documento45 paginePure Theory of Law Hans Kelson-Ltp..ShabnamNessuna valutazione finora

- Lecture Notes 10: Fading Channels ModelsDocumento19 pagineLecture Notes 10: Fading Channels ModelsayushNessuna valutazione finora

- The Standard Model Theory - Kreon Papathanasiou - ph4884Documento30 pagineThe Standard Model Theory - Kreon Papathanasiou - ph4884Haigh RudeNessuna valutazione finora

- Materi 2 - Obligation, Prohibition, and Suggestion - AdviceDocumento12 pagineMateri 2 - Obligation, Prohibition, and Suggestion - AdviceShadrina ChaerunissaNessuna valutazione finora

- Arguments and FallaciesDocumento18 pagineArguments and FallaciesSarah Mae Peñaflor Baldon-IlaganNessuna valutazione finora

- Section A - Listening (15 PTS) I. Listen To The Dialogue and Fill in Each Blank With ONE Suitable Word or Number. The House For RentDocumento22 pagineSection A - Listening (15 PTS) I. Listen To The Dialogue and Fill in Each Blank With ONE Suitable Word or Number. The House For RentThanh PhongNessuna valutazione finora

- Thermal Stress AnalysisDocumento11 pagineThermal Stress AnalysisFahad KhanNessuna valutazione finora

- Prudence and FrugalityDocumento17 paginePrudence and FrugalitySolaiman III SaripNessuna valutazione finora

- High Low MethodDocumento4 pagineHigh Low MethodSamreen LodhiNessuna valutazione finora

- S1 Mock 2Documento13 pagineS1 Mock 2Abdulrahman HatemNessuna valutazione finora

- Lac CultureDocumento7 pagineLac CultureDhruboNessuna valutazione finora

- Accenture United Nations Global Compact IndexDocumento4 pagineAccenture United Nations Global Compact IndexBlasNessuna valutazione finora

- What's New: Contemporary Quiz#5Documento2 pagineWhat's New: Contemporary Quiz#5Christian Castañeda100% (1)

- Intermolecular Force Worksheet KeyDocumento3 pagineIntermolecular Force Worksheet KeyBill alfonsoNessuna valutazione finora

- English Project Basic Listo (Realizado)Documento3 pagineEnglish Project Basic Listo (Realizado)Javier ToapantaNessuna valutazione finora

- Final Model Paper Computer Science HSSC-IIDocumento9 pagineFinal Model Paper Computer Science HSSC-IIMUhammad Milad AwanNessuna valutazione finora

- V0 VSS VDD: Unit PIN Symbol Level Nominal Dimensions Pin Connections Function Mechanical Data ItemDocumento1 paginaV0 VSS VDD: Unit PIN Symbol Level Nominal Dimensions Pin Connections Function Mechanical Data ItemBasir Ahmad NooriNessuna valutazione finora

- Daily ReportDocumento39 pagineDaily ReportLe TuanNessuna valutazione finora

- MLA 7th Edition Formatting and Style GuideDocumento14 pagineMLA 7th Edition Formatting and Style Guideapi-301781586Nessuna valutazione finora

- AI Coming For LawyersDocumento4 pagineAI Coming For LawyersbashiNessuna valutazione finora

- TOC - Question AnswerDocumento41 pagineTOC - Question AnsweretgegrgrgesNessuna valutazione finora

- 01 Agile Challenge-Does Anyone Have A PencilDocumento13 pagine01 Agile Challenge-Does Anyone Have A PencilAbhisek MukherjeeNessuna valutazione finora

- Group 2 PBA - ScriptDocumento6 pagineGroup 2 PBA - ScriptruciNessuna valutazione finora