Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

8255

Caricato da

nnngoc13Descrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

8255

Caricato da

nnngoc13Copyright:

Formati disponibili

Page 1 of 4

IA8255 Advanced Information Sheet

Programmable Peripheral Interface Adapter

FEATURES

• Form, Fit, and Function Compatible with the Intel 8255A and Harris

82C55A

• Packaging options available: 40 Pin Plastic DIP or 44 Pin Plastic Leaded

Chip Carrier

• 24 Programmable Input/Outputs

• Static Read/Write or Handshaking Modes

• Direct Bit Set/Reset Capability

• High Speed, No “Wait State” Operation

The IA8255 uses innovASIC’s innovative new f 3 Program to provide industry with parts that

other vendors have declared obsolete. By specifying parts through this program a customer is

assured of never having a component become obsolete again. This advanced information sheet

assumes the original part has been designed in, and so provides a summary of capabilities only. For

new designs contact innovASIC for more detailed information.

Intel is a registered trademark of Intel Corporation

Harris is a copyright trademark of Harris Corporation

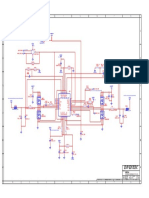

Package Pinout

WR_n

PA3 (1) (40) PA4

RD_n

IA8255

N. C.

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PA2 (2) (39) PA5

40 Pin DIP

PA1 (3) (38) PA6

PA0 (4) (37) PA7

(6)

(5)

(4)

(3)

(2)

(1)

(44)

(43)

(42)

(41)

(40)

RD_n (5) (36) WR_n CS_n (7) RESET

(39)

CS_n (6) (35) RESET GND (8) D0

(38)

GND (7) (34) D0 A1 (9) D1

IA8255 (37)

A1 (8) (33) D1 A0 (10) (36) D2

A0 (9) D2 PC7 (11)

44 Pin LCC D3

(32) (35)

PC7 (10) (31) D3 N. C. (12) (34) N. C.

PC6 (11) (30) D4 PC6 (13) (33) D4

PC5 (12) (29) D5 PC5 (14) (32) D5

PC4 (13) (28) D6 PC4 (15) (31) D6

PC0 (14) (27) D7 PC0 (16) (30) D7

PC1 (15) (26) VCC PC1 (17) (29) VCC

(18)

(19)

(20)

(21)

(22)

(23)

(24)

(25)

(26)

(27)

(28)

PC2 (16) (25) PB7

PC3 (17) (24) PB6

PB0 (18) (23) PB5

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

PC2

PC3

N. C.

PB1 (19) (22) PB4

PB2 (20) (21) PB3

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 2 of 4

IA8255 Advanced Information Sheet

Programmable Peripheral Interface Adapter

The IA8255 is a programmable peripheral interface adapter mega-function designed to be

functionally equivalent to the Intel 8255A and Harris 82C55A devices. This function has 24 I/O

signals programmable in two groups of 12. Three modes of operation allow the following:

• Basic Input/Output (Mode 0) - Port A, Port B, Port C (upper), and Port C (lower) can be

independently configured as inputs or outputs to read or hold static data. Outputs are

latched, but inputs are not latched.

• Strobed Input/Output (Mode 1) - Port A and Port B can be independently configured as

strobed input or output buses. Signals from Port C are dedicated as control signals for data

handshaking.

• Bidirectional Bus (Mode 2) - Port A can also be configured as a bidirectional bus, with the

majority of Port C providing the control signals. In this case, Port B is still capable of

implementing one of the previous described modes.

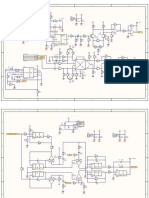

A block diagram is shown in Figure 1.

Functional Block Diagram

Figure 1

8 BIT INTERNAL

DATA BUS

D7:D0

I/O

DATA BUS

PA7:PA0

BUFFER GROUP A

PORT A

(8)

GROUP A

CONTROL

I/O

GROUP A PC7:PC4

PORT C

UPPER (4)

RESET

I/O

CS_n GROUP B PC3:PC0

PORT C

RD_n LOWER

CONTROL GROUP B

(4)

CONTROL

WR_n REGISTER AND

LOGIC

A0

A1

I/O

GROUP B PB7:PB0

PORT B

(8)

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 3 of 4

IA8255 Advanced Information Sheet

Programmable Peripheral Interface Adapter

Qualification Levels

Table 1

Part Number Environmental/ Qual Level

IA8255-PDW40C Commercial

IA8255-PLC44C Commercial

IA8255-PDW40I Industrial

IA8255-PLC44I Industrial

The following diagram depicts the innovASIC Product Identification Number.

IAXXXXX-PPPPNNNT/SP

Special Processing:

S = Space

Q = MIL-STD-883

Temperature:

C = Commercial

I = Industrial

M = Military

Number of Leads

Package Type:

Per Package Designator Table

IC Base Number

innovASIC Designator

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 4 of 4

IA8255 Advanced Information Sheet

Programmable Peripheral Interface Adapter

Package Designator Table

Package Type innovASIC

Designator

Ceramic side brazed Dual In-line CDB

Cerdip with window CDW

Ceramic leaded chip carrier CLC

Cerdip without window CD

Ceramic leadless chip carrier CLL

PLCC PLC

Plastic DIP standard (300 mil) PD

Plastic DIP standard (600 mil) PDW

Plastic metric quad flat pack PQF

Plastic thin quad flat pack PTQ

Skinny Cerdip CDS

Small outline plastic gull-wing(150 mil body) PSO

Small outline medium plastic gull-wing (207 mil body) PSM

Small outline narrow plastic gull wing (150 mil body) PSN

Small outline wide plastic gull wing (300 mil body) PSW

Skinny Plastic Dip PDS

Shrink small outline plastic (5.3mm .208 body) PS

Thin shrink small outline plastic PTS

Small outline large plastic gull wing (330 mil body) PSL

Thin small outline plastic gull-wing (8 x 20mm) [TSOP] PST

PGA CPGA

BGA CBGA

Contact innovASIC for other package and processing options.

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Potrebbero piacerti anche

- 025 Boogie Oogie Oogie DMSDocumento2 pagine025 Boogie Oogie Oogie DMSDima100% (1)

- Left foot coordination exercisesDocumento5 pagineLeft foot coordination exercisesPaul JudgeNessuna valutazione finora

- AIX For The System AdministratorDocumento10 pagineAIX For The System AdministratorDima ShcherbakovNessuna valutazione finora

- User ManualDocumento86 pagineUser ManualAlvaro CotaquispeNessuna valutazione finora

- ABB REM Relay Unit Software Manual CAP 505Documento102 pagineABB REM Relay Unit Software Manual CAP 505mitch1973100% (1)

- 2019 Led LCD T-4Documento136 pagine2019 Led LCD T-4Diego Correa67% (3)

- Smart Ups Su1000 1400 Chassis 733Documento5 pagineSmart Ups Su1000 1400 Chassis 733miklexNessuna valutazione finora

- Orawa (8) Violin II 2Documento7 pagineOrawa (8) Violin II 2Zdeněk ŽertNessuna valutazione finora

- Orawa (8) Violin I 1Documento5 pagineOrawa (8) Violin I 1Zdeněk Žert100% (1)

- Step by Step Guide To Become Big Data DeveloperDocumento15 pagineStep by Step Guide To Become Big Data DeveloperSaggam Bharath75% (4)

- CANOA - DO RIO BateriaDocumento2 pagineCANOA - DO RIO BateriaAle MennutiNessuna valutazione finora

- Smoking Snakes CymbalsDocumento1 paginaSmoking Snakes CymbalsJonathan SilvaNessuna valutazione finora

- Forr Das Antigas N 1 Drum SetDocumento3 pagineForr Das Antigas N 1 Drum SetJhonatas LimaNessuna valutazione finora

- ATMEGA128 Development Board SchematicDocumento2 pagineATMEGA128 Development Board SchematichwtekNessuna valutazione finora

- Smoking Snakes Snare DrumDocumento1 paginaSmoking Snakes Snare DrumDaniel NetoNessuna valutazione finora

- Raça Negra - Grandes Sucessos Drum SetDocumento2 pagineRaça Negra - Grandes Sucessos Drum SetFábio MoraisNessuna valutazione finora

- Raça Negra - Grandes Sucessos Drum SetDocumento2 pagineRaça Negra - Grandes Sucessos Drum SetFábio MoraisNessuna valutazione finora

- Zone1-Layout1Documento1 paginaZone1-Layout1haymsa977Nessuna valutazione finora

- Hyde Park DrumsDocumento1 paginaHyde Park DrumsOdeon ChoroNessuna valutazione finora

- 8-Bit Microcontroller With 12K Bytes Flash AT89S53: FeaturesDocumento32 pagine8-Bit Microcontroller With 12K Bytes Flash AT89S53: FeaturesJOSEPH GOMEZ SAENZNessuna valutazione finora

- 8-Bit Microcontroller With 12K Bytes Flash AT89S53: FeaturesDocumento32 pagine8-Bit Microcontroller With 12K Bytes Flash AT89S53: Featuresapi-3808344Nessuna valutazione finora

- Beethoven in Samba Drum Set PDFDocumento2 pagineBeethoven in Samba Drum Set PDFApoena BorgesNessuna valutazione finora

- AbrilescoDocumento1 paginaAbrilescoJavier SanchoNessuna valutazione finora

- RTD2120LDocumento37 pagineRTD2120LNeha WadyalkarNessuna valutazione finora

- 8-Bit Microcontroller With 8K Bytes Flash AT89S8252: FeaturesDocumento31 pagine8-Bit Microcontroller With 8K Bytes Flash AT89S8252: Featuresapi-3808344Nessuna valutazione finora

- At8-9s51 DatasheetDocumento31 pagineAt8-9s51 Datasheet3112210007 fariz alghofiqiNessuna valutazione finora

- Aduc812: Microconverter Quick Reference GuideDocumento2 pagineAduc812: Microconverter Quick Reference GuideFelipe VasconcelosNessuna valutazione finora

- Parapet Wall With Crash BarrierDocumento1 paginaParapet Wall With Crash BarrierSharun ShajiNessuna valutazione finora

- Pre-Amplifier Circuit DiagramDocumento2 paginePre-Amplifier Circuit DiagramrigaboNessuna valutazione finora

- Festival Junino Drum Set Arrangement SheetDocumento2 pagineFestival Junino Drum Set Arrangement SheetFábio MesquitaNessuna valutazione finora

- HL-MT 1Documento1 paginaHL-MT 1romeo_mecNessuna valutazione finora

- ATmega 16Documento1 paginaATmega 16Mohammad Amirul MukmininNessuna valutazione finora

- EduShield SchematicDocumento1 paginaEduShield SchematicPlaymr 365Nessuna valutazione finora

- Billie Jean PercussionDocumento2 pagineBillie Jean PercussionAkimychNessuna valutazione finora

- M4 N4 C6 P3 P5 chip layout and pin connectionsDocumento1 paginaM4 N4 C6 P3 P5 chip layout and pin connectionsdevesh.ehrenNessuna valutazione finora

- Hidraulic SchematicDocumento2 pagineHidraulic SchematicHamilton Miranda100% (1)

- Schema Shield Invatare ArduinoDocumento1 paginaSchema Shield Invatare ArduinoTokra2007Nessuna valutazione finora

- MFS Arduino PDFDocumento1 paginaMFS Arduino PDFDusmantha AnandaratneNessuna valutazione finora

- 100R R3 K12 100R R2 K11 K5 K2: QuantumopticsDocumento1 pagina100R R3 K12 100R R2 K11 K5 K2: QuantumopticsbaymanNessuna valutazione finora

- The Shadows-Fly Me To The MoonDocumento4 pagineThe Shadows-Fly Me To The Moonmouhsine arfaouiNessuna valutazione finora

- 8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT89S51Documento30 pagine8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT89S51Girish GnNessuna valutazione finora

- 6 - EthernetDocumento1 pagina6 - EthernetHungNessuna valutazione finora

- One-Way Cycle Track at Signalised T-Intersection: Give Way Line R10Documento1 paginaOne-Way Cycle Track at Signalised T-Intersection: Give Way Line R10winniwNessuna valutazione finora

- Iriihnfo: ÉkfǒzdztaDocumento1 paginaIriihnfo: Ékfǒzdzta王鈺靜Nessuna valutazione finora

- MRI Flyer 10 2010Documento4 pagineMRI Flyer 10 2010Osama EvaNessuna valutazione finora

- ATF2500C CPLD Family Datasheet ATF2500C: FeaturesDocumento9 pagineATF2500C CPLD Family Datasheet ATF2500C: FeaturesSolikin AjNessuna valutazione finora

- Dona Maria DrumsDocumento1 paginaDona Maria DrumsFábio MesquitaNessuna valutazione finora

- Schematic - Hexapod Schematics - 2024 03 28Documento1 paginaSchematic - Hexapod Schematics - 2024 03 28yashgotherwalNessuna valutazione finora

- FRC NI RoboRIO User Manual PDFDocumento31 pagineFRC NI RoboRIO User Manual PDFJuan de Dios Alardín HernándezNessuna valutazione finora

- RoboRIO ManualDocumento31 pagineRoboRIO ManualHectorNessuna valutazione finora

- Fingerprint Module: Micro Usb ConnDocumento2 pagineFingerprint Module: Micro Usb ConnNetking SystemNessuna valutazione finora

- SBBR - Rnav Opnok 1a Rwy 29r - Sid - 20190912Documento1 paginaSBBR - Rnav Opnok 1a Rwy 29r - Sid - 20190912Rodrigo HalzenthNessuna valutazione finora

- System PowerDocumento1 paginaSystem Powerradu2000vNessuna valutazione finora

- 10面板Documento1 pagina10面板MARIA FERNANDA MORA AREVALONessuna valutazione finora

- DD Expander - MB - Diy - Schematics - Rev1Documento3 pagineDD Expander - MB - Diy - Schematics - Rev1JosephNessuna valutazione finora

- VCC R57 10K Idle AccLed R56 Tx WarmLed InjLed CANRx CANRx 4 4Documento10 pagineVCC R57 10K Idle AccLed R56 Tx WarmLed InjLed CANRx CANRx 4 4MartinKampffNessuna valutazione finora

- SchematicDocumento71 pagineSchematichemantasahoo1009Nessuna valutazione finora

- Schemetic Smart MeterDocumento3 pagineSchemetic Smart Meteranmol24soeNessuna valutazione finora

- Swing de ChocoboDocumento9 pagineSwing de ChocobosportadenoNessuna valutazione finora

- Algebra PuzzleDocumento1 paginaAlgebra PuzzleAnonymous ydkBiMVlNessuna valutazione finora

- So Do Nguyen Ly Mach Do DuongDocumento2 pagineSo Do Nguyen Ly Mach Do DuongLhthang KtvNessuna valutazione finora

- 32x8 SRAM DatasheetDocumento12 pagine32x8 SRAM DatasheetAhmet AyanNessuna valutazione finora

- DL1100Documento2 pagineDL1100Wong Wong WLNessuna valutazione finora

- Primary Guide To UMTS Voice Quality Problems: Security LevelDocumento16 paginePrimary Guide To UMTS Voice Quality Problems: Security Levelyusia yokiNessuna valutazione finora

- Red Hat Enterprise Linux-7-High Availability Add-On Overview-en-USDocumento18 pagineRed Hat Enterprise Linux-7-High Availability Add-On Overview-en-USaeldeeb7Nessuna valutazione finora

- 9100 BTS Product Description Ed32relDocumento67 pagine9100 BTS Product Description Ed32relAniq AhmedNessuna valutazione finora

- "DENON DJ Music Manager" Has The Functions Described BelowDocumento13 pagine"DENON DJ Music Manager" Has The Functions Described Belowhirenshah74Nessuna valutazione finora

- Cloud Data Lakes For Dummies Snowflake Special Edition V1 3Documento10 pagineCloud Data Lakes For Dummies Snowflake Special Edition V1 3CarlosVillamilNessuna valutazione finora

- Rman Hands OnDocumento161 pagineRman Hands OnCharles G GalaxyaanNessuna valutazione finora

- noLink detected: yesDocumento7 paginenoLink detected: yesAditya PaulNessuna valutazione finora

- AC1200 MU-MIMO Wi-Fi Router with Gigabit Ethernet PortsDocumento7 pagineAC1200 MU-MIMO Wi-Fi Router with Gigabit Ethernet PortsMarcio MendesNessuna valutazione finora

- Blood Bank Management System SYNOPSISDocumento10 pagineBlood Bank Management System SYNOPSISRishabh ShuklaNessuna valutazione finora

- Java Magazine JanuaryFebruary 2013Documento93 pagineJava Magazine JanuaryFebruary 2013rubensaNessuna valutazione finora

- Service Manual Aspire 4253Documento226 pagineService Manual Aspire 4253valyexNessuna valutazione finora

- Kedareswara Vratham Telugu Book PDF Free 46Documento2 pagineKedareswara Vratham Telugu Book PDF Free 46Akhil AnumandlaNessuna valutazione finora

- GeoMax Zenith 25proDocumento2 pagineGeoMax Zenith 25probbutros_317684077Nessuna valutazione finora

- ATM With An EyeDocumento25 pagineATM With An EyeMadhuri Ch67% (6)

- The Mysteries of Microsoft Print To PDFDocumento12 pagineThe Mysteries of Microsoft Print To PDFbibiana8593Nessuna valutazione finora

- Pre Emphasis de EmphasisDocumento2 paginePre Emphasis de EmphasisgodierobertNessuna valutazione finora

- C Data Types For StudentsDocumento20 pagineC Data Types For StudentsJayeshNessuna valutazione finora

- Access ControlDocumento15 pagineAccess Controlrubrino87100% (1)

- FactoryTalk View SE - Backup Your Application Using The Distributed Application ManagerDocumento4 pagineFactoryTalk View SE - Backup Your Application Using The Distributed Application ManagerPelife GoNessuna valutazione finora

- Howd To Set First Page of PDF Opens (Adobe Community)Documento2 pagineHowd To Set First Page of PDF Opens (Adobe Community)Anonymous BeH7Okq8rNessuna valutazione finora

- Atoll 3.3.1 User Manual RadioDocumento1.428 pagineAtoll 3.3.1 User Manual RadioSemihOzer100% (1)

- III Year Syllabus UITDocumento14 pagineIII Year Syllabus UITAnith AshokNessuna valutazione finora

- 10-14 Batch Vi Sem Grade AnalysisDocumento4 pagine10-14 Batch Vi Sem Grade AnalysisPrabha Karan MurugadossNessuna valutazione finora