Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Final Exam Formula Sheet

Caricato da

Mohab SamehCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Final Exam Formula Sheet

Caricato da

Mohab SamehCopyright:

Formati disponibili

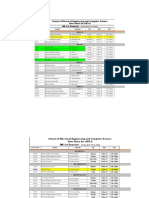

Final Exam Semiconductor Devices (ELCT503) Time allowed : Three hours

Faculty of Information

Engineering & Technology (IET)

Electronics Engineering Dept.

Semiconductor Devices: ELCT 503

Final Exam (Fall 2014)

Course Instructor: Dr. Hassan Mostafa

Bar Code

Instructions:

1. Answer all questions.

2. The exam consists of x questions in x pages including this page.

3. A cheat sheet is attached at end of this booklet.

4. The exam allowed time is Three hours.

5. Electronic calculators are allowed.

6. Clearly show all steps used in your solutions.

7. This is a closed book exam.

Please, do not write anything on this page

Final Exam Semiconductor Devices (ELCT503) Time allowed : Three hours

Cheat Sheet

Intrinsic Si: Carriers Transport:

Vbi

e

2

N D xn N A x p

2 2

1 1 3

F (E) mn vth2 kT

e ( E EF )/kT 1 2 2 kT N D N A

Vbi ln

vn n E e ni 2

n f(E)N(E)dE

EC v p pE 2 N A N D

xd Vbi

N(E)

4

( 2me )3 / 2(E Ec )1/ 2 J J n J p e nn p p E e ND N A

h3

e nn p p xd xn x p

4 dn pn with forward bias V=Va:

N(E) ( 2mh )3 / 2(Ev E)1/ 2 J n eDn

h3 dx 2 N A N D

xd Vbi V

dp e ND N A

J p eDp

n p ni f(E)N(E)dE dx

Cj

e N A N D

2N A N D Vbi V

EC

dn xd w

(EC EF )/kT J n en nE eDn

n NC e dx

D p ni2 Dn ni2 qVa

3/ 2

dp J t e exp 1

2 mn kT J p e p pE eDp L p N d Ln N a kT

N C 12

h

2

dx

Ln Dn n L p D p p

p NV e (EF EV )/kT Dn D p kT

VT

n p e qV

2 mh kT

3/ 2 I d J t A I sd exp a 1

NV 2 Quasi Fermi Level: kT

h

2

Reverse bias pn junction:

Ei EFp

Extrinsic Si: p p0 p ni exp

kT D p ni2 Dn ni2

n ni exp (E F Ei )/kT I (Va ) qA I sd

L p N d Ln N a

E Ei

p ni exp (Ei EF )/kT n n0 n ni exp Fn

kT Diffusion capacitance:

Mass Action Law:

Continuity equation: Ae 2 L p pn 0 eV

pn n 2 Cd exp a

n 1 Jn kT kT

Gn Rn

i

Charge neutrality: t e x

n N A p N D p 1 Jp

G p R p

dt e x

pn junction:

N A x p N D xn

Final Exam Semiconductor Devices (ELCT503) Time allowed : Three hours

Diode DC model: Transistor in Saturation region Constants:

Exponential model: (VBE >= 0.7V) and (VBC >= 0.4V) KT = 0.026 eV

at T=300OK

I D2 VCE =0.2V

VD 2 VD1 nVT * ln( )

I D1 ICsat = forced IB

q = 1.6 *10-19 C

IE = IC + IB = (forced+1) IB

0 = 8.85*10-12 F m-1

Diode small signal model: BJT small signal:

For Si:

nV I

rd T gm C Eg = 1.12 eV

ID VT

NC = 2.84*1019 cm-3

V V

BJT Physics: r T T NV = 3.08*1019 cm-3

IB IC gm

I pE I pE 1 Si = 11.7

|V |

IE I pE I nE D N W ro A Sio2 = 3.9

1 n B B IC

D p N EW E s = 4.05 V

V V

I pC I BB W

2 re T T

T 1 1 B 2 IE IC gm

I pE I pE 2Lp

MOSFET Physics:

I pC 2kT N A

0

IE S inv 2 B ln

e ni

0 S kT ln N A /ni

2

W

Base _ Transit _ Time : D B wm 2

2Dp e2 N A

Diffusion_ length : L p D p p

2e0 S N A 2 B

2 Vth VFB 2 B

Lp Cox

Diffusion_ life _ time : p

Dp

Qox

VFB ms

BJT DC Models: Cox

Transistor OFF

MOSFET DC models:

(VBE < 0.7V) and (VBC < 0.4V)

VGS < Vtn OFF ID=0

IB = 0 IC = 0 IE = 0

VGS >= Vtn ON

Transistor in Active region

VDS < (VGS Vtn) (Triode)

(VBE >= 0.7V) and (VBC < 0.4V)

ID = n Cox (W/L) [(VGS - Vtn) VDS VDS2/2]

VCE >=0.3V

VDS << (VGS Vtn) (Linear)

IC = IS exp (VBE/VT)

IC = IB = IE ID = n Cox (W/L) [(VGS - Vtn) VDS]

IE = IC + IB = (+1) IB RON = VDS/ID = 1/[n Cox (W/L) (VGS - Vtn) ]

= / (1- ) and >> 1 VDS >= (VGS Vtn) (Saturation)

= / (+1) and <= 1 ID =0.5* n Cox (W/L) (VGS - Vtn)2

Potrebbero piacerti anche

- Transformer 1 2Documento94 pagineTransformer 1 2Tobi AQWNessuna valutazione finora

- Sonosite Echo Machine Model MicromaxxDocumento100 pagineSonosite Echo Machine Model MicromaxxAakshiRajputNessuna valutazione finora

- How To Configure Tvheadend For DVB Tuner PDFDocumento8 pagineHow To Configure Tvheadend For DVB Tuner PDFRafa AguileraNessuna valutazione finora

- R5888C Quadramho A4RBDocumento336 pagineR5888C Quadramho A4RBdbeard811100% (1)

- حلول سعادات p43-54Documento12 pagineحلول سعادات p43-54يمامه انورNessuna valutazione finora

- Assignment-2question and SolutionDocumento12 pagineAssignment-2question and SolutionDharmender KumarNessuna valutazione finora

- Chapter 3 Energy of A System ThermoDocumento25 pagineChapter 3 Energy of A System ThermoEmadudin AbdulkaderNessuna valutazione finora

- O20 Btech 1183Documento251 pagineO20 Btech 1183Aditya GuptaNessuna valutazione finora

- Auto TransformerDocumento5 pagineAuto TransformerAugy HaerudyNessuna valutazione finora

- Exercises For Lecture 5-6-7 - SOLUTIONDocumento8 pagineExercises For Lecture 5-6-7 - SOLUTIONLam Pham Phuoc Loc100% (1)

- Scott Connection ProblemsDocumento1 paginaScott Connection ProblemsToper GarciaNessuna valutazione finora

- EXP2 Half Wave RectifierDocumento3 pagineEXP2 Half Wave RectifierMohammed Dyhia Ali50% (2)

- PTDU Lab No. 10 Study of Real Time Operation of Bus Bars Abdul Wahab Nasir (02) Bsee 16-20Documento2 paginePTDU Lab No. 10 Study of Real Time Operation of Bus Bars Abdul Wahab Nasir (02) Bsee 16-20Ali ArshadNessuna valutazione finora

- Single Tuned Voltage Amplifier: Siddhartha Engineering CollegeDocumento11 pagineSingle Tuned Voltage Amplifier: Siddhartha Engineering CollegeChakri KamaniNessuna valutazione finora

- ECS332 2015 Postmidterm HWDocumento69 pagineECS332 2015 Postmidterm HWDeadpool 001Nessuna valutazione finora

- Civil-V-Transportation Engineering-1 (10CV56) - SolutionDocumento92 pagineCivil-V-Transportation Engineering-1 (10CV56) - SolutionLokesh KNessuna valutazione finora

- Mariah Lydia Supremo Ee 404 Laboratory Experiment 5Documento5 pagineMariah Lydia Supremo Ee 404 Laboratory Experiment 5andrei saad100% (1)

- EEL2026-LabsheetDocumento23 pagineEEL2026-LabsheetchandraNessuna valutazione finora

- Assignment 1Documento6 pagineAssignment 1Dr.Hesham El-BadawyNessuna valutazione finora

- Chapter 10 Sym Comp and Unbalanced FaultDocumento45 pagineChapter 10 Sym Comp and Unbalanced FaultjaysonlkhNessuna valutazione finora

- Solved Problems To Chapter 14Documento2 pagineSolved Problems To Chapter 14methoxy67% (3)

- SKEE 2742 Basic Electronics Lab: Experiment 2 BJT Small-Signal AmplifierDocumento8 pagineSKEE 2742 Basic Electronics Lab: Experiment 2 BJT Small-Signal Amplifierمحمد ابو جرادNessuna valutazione finora

- Experiment 4Documento10 pagineExperiment 4djelbouNessuna valutazione finora

- Eca Lab Manual Final Print PDFDocumento41 pagineEca Lab Manual Final Print PDFvineethaNessuna valutazione finora

- DC-DC ConvertersDocumento30 pagineDC-DC ConvertersTema HassanNessuna valutazione finora

- CH-2-DC MachineDocumento83 pagineCH-2-DC MachineÙm ØrthøbøyNessuna valutazione finora

- Bifpcl Question Solve - 2015: R 5+3+2 10 V 20+20 40 Sor 10 P 40 / (4 X 10)Documento7 pagineBifpcl Question Solve - 2015: R 5+3+2 10 V 20+20 40 Sor 10 P 40 / (4 X 10)Mazharul HaqueNessuna valutazione finora

- Test Based On Electric DipoleDocumento5 pagineTest Based On Electric DipoleKunal MukherjeeNessuna valutazione finora

- Electromagnetic Fields II-SummerDocumento39 pagineElectromagnetic Fields II-SummerMINESY60% (5)

- Solution of Tutorial Sheet-3 (Three Phase Networks) : Ans. Given, - Vab - 45kV, ZL (0.5 + j3), Z (4.5 + j9)Documento10 pagineSolution of Tutorial Sheet-3 (Three Phase Networks) : Ans. Given, - Vab - 45kV, ZL (0.5 + j3), Z (4.5 + j9)Shroyon100% (2)

- ADE Lab Manual - Analog Part PDFDocumento21 pagineADE Lab Manual - Analog Part PDFJk RinkuNessuna valutazione finora

- FM Balanced Slope DetectorDocumento5 pagineFM Balanced Slope DetectorPujjalPandeyNessuna valutazione finora

- Electrical 4Documento2 pagineElectrical 4Puran Singh LabanaNessuna valutazione finora

- Magnetically Coupled Circuits PDFDocumento21 pagineMagnetically Coupled Circuits PDFOrlando100% (1)

- M Systems: ScilloscopesDocumento6 pagineM Systems: ScilloscopesAnkit KumarNessuna valutazione finora

- UNIT1Documento37 pagineUNIT1Azliana Mohd Taib0% (1)

- OC and SC Test On Single Phase TransformerDocumento5 pagineOC and SC Test On Single Phase TransformerhavejsnjNessuna valutazione finora

- 213 EMF JustificationDocumento3 pagine213 EMF JustificationEEE CRRNessuna valutazione finora

- Circuit Lab Div. B Tryout Test PDFDocumento6 pagineCircuit Lab Div. B Tryout Test PDFMadhavi VangipurapuNessuna valutazione finora

- Chapter 25 D.C. MachinesDocumento20 pagineChapter 25 D.C. MachinesJosh'z LlamesNessuna valutazione finora

- North South University: Lab 3: Loading Effect of Voltage Divider CircuitDocumento3 pagineNorth South University: Lab 3: Loading Effect of Voltage Divider CircuitNazmul Hasan 1911742042Nessuna valutazione finora

- Lecs 2 After MidtermDocumento41 pagineLecs 2 After MidtermAbdalkader Alibrahim100% (1)

- Eeeb113 Circuit Analysis 1: Chapter 6: Capacitors and Inductors Sharifah Azma Syed MustaffaDocumento25 pagineEeeb113 Circuit Analysis 1: Chapter 6: Capacitors and Inductors Sharifah Azma Syed MustaffaSharifah Azma100% (1)

- AC Circuits: Fundamentals of Electric CircuitsDocumento16 pagineAC Circuits: Fundamentals of Electric CircuitsHiếu Dương100% (1)

- Performance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDocumento7 paginePerformance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDr-Sanjeev KashyapNessuna valutazione finora

- D 01Documento209 pagineD 01Raj Boda0% (1)

- C 3Documento47 pagineC 3Saurabh SharmaNessuna valutazione finora

- 1 (1) 4Documento10 pagine1 (1) 4Angga SeptianNessuna valutazione finora

- EENG428 Midterm Exam SOLUTIONS PDFDocumento9 pagineEENG428 Midterm Exam SOLUTIONS PDFhastitoNessuna valutazione finora

- Reference: OPAMP and Linear Integrated Circuits by Ramakant A. Gayakwad, PHIDocumento27 pagineReference: OPAMP and Linear Integrated Circuits by Ramakant A. Gayakwad, PHIchandra prakash purbiaNessuna valutazione finora

- Cap 5Documento29 pagineCap 5deberes ucacueNessuna valutazione finora

- Captitulo 6 Potencial ElectricDocumento16 pagineCaptitulo 6 Potencial ElectricDavidCaloNessuna valutazione finora

- Chapter 6 DM PDFDocumento84 pagineChapter 6 DM PDFjewish vanNessuna valutazione finora

- Experiment 1Documento12 pagineExperiment 1Jomar RosalesNessuna valutazione finora

- Chapter 3: Ac Power AnalysisDocumento40 pagineChapter 3: Ac Power AnalysisAtyia Javed100% (1)

- Syllabus in Electrical Equipment DevicesDocumento15 pagineSyllabus in Electrical Equipment Devicesrare machineNessuna valutazione finora

- Proposed 15 Numerical Problems For PresentationDocumento8 pagineProposed 15 Numerical Problems For PresentationalexNessuna valutazione finora

- Unit Iv: Frequency Domain AnalysisDocumento35 pagineUnit Iv: Frequency Domain AnalysisVinod Jagdale100% (1)

- Experiment: Title: DC Power Supply Unit: Transformer ObjectiveDocumento14 pagineExperiment: Title: DC Power Supply Unit: Transformer ObjectiveLian Ai Chen100% (1)

- Solution:: KVA IpDocumento3 pagineSolution:: KVA IpNoor Mohammed100% (1)

- Experiment 1Documento6 pagineExperiment 1Jomel JomelNessuna valutazione finora

- VFFDT ManualDocumento41 pagineVFFDT ManualVera SimilarNessuna valutazione finora

- Derivation of Optical Absorption Coefficient in Direct SemiconductorsDocumento48 pagineDerivation of Optical Absorption Coefficient in Direct SemiconductorsquintoNessuna valutazione finora

- Lecture 7 PDFDocumento40 pagineLecture 7 PDFMohab Sameh100% (1)

- Lecture 5 PDFDocumento57 pagineLecture 5 PDFMohab SamehNessuna valutazione finora

- Lecture 6 PDFDocumento61 pagineLecture 6 PDFMohab SamehNessuna valutazione finora

- Lecture 2Documento57 pagineLecture 2Mohab SamehNessuna valutazione finora

- Lecture 8 PDFDocumento49 pagineLecture 8 PDFMohab SamehNessuna valutazione finora

- Lecture 9 PDFDocumento17 pagineLecture 9 PDFMohab SamehNessuna valutazione finora

- Somary For FedbockDocumento4 pagineSomary For FedbockMohab SamehNessuna valutazione finora

- Lecture 1Documento55 pagineLecture 1Mohab SamehNessuna valutazione finora

- Lecture 4Documento23 pagineLecture 4Mohab SamehNessuna valutazione finora

- Lect - 3 - Sensor Technology PDFDocumento26 pagineLect - 3 - Sensor Technology PDFAhmedSeragNessuna valutazione finora

- Elct 903 T8 PDFDocumento30 pagineElct 903 T8 PDFMohab SamehNessuna valutazione finora

- Introduction To Electromagnetism and Its Application To Materials ScienceDocumento26 pagineIntroduction To Electromagnetism and Its Application To Materials ScienceMohab SamehNessuna valutazione finora

- Lecture 3Documento41 pagineLecture 3Mohab SamehNessuna valutazione finora

- Dynamic Response of Measurement Systems: ME231 Measurements Laboratory Spring 1999Documento19 pagineDynamic Response of Measurement Systems: ME231 Measurements Laboratory Spring 1999Giriraj HedaNessuna valutazione finora

- Computer Arithmetic: Introduction: Programmable Logic CircuitsDocumento75 pagineComputer Arithmetic: Introduction: Programmable Logic CircuitsMohab SamehNessuna valutazione finora

- Optoelectronics Homework Sheet 6Documento1 paginaOptoelectronics Homework Sheet 6Mohab SamehNessuna valutazione finora

- Concert MailDocumento1 paginaConcert MailMohab SamehNessuna valutazione finora

- Running Head: Title of Paper in Caps 1: Hadoop, Mapreduce and HDFS: A Developers PerspectiveDocumento5 pagineRunning Head: Title of Paper in Caps 1: Hadoop, Mapreduce and HDFS: A Developers PerspectiveMohab SamehNessuna valutazione finora

- CT FinalDocumento5 pagineCT FinalMohab SamehNessuna valutazione finora

- FP ReportDocumento3 pagineFP ReportMohab SamehNessuna valutazione finora

- NnoalsndolasDocumento13 pagineNnoalsndolasMohab SamehNessuna valutazione finora

- DeadlinesDocumento2 pagineDeadlinesMohab SamehNessuna valutazione finora

- Step by StepDocumento18 pagineStep by StepAncil CleetusNessuna valutazione finora

- Review: Dye Lasers: Presented By: Mohab Sameh Supervisor: Dr. Haitham OmranDocumento19 pagineReview: Dye Lasers: Presented By: Mohab Sameh Supervisor: Dr. Haitham OmranMohab SamehNessuna valutazione finora

- Design ProblemDocumento8 pagineDesign ProblemMohab SamehNessuna valutazione finora

- Jazz Concert Preliminary Preparations: 1. Dr. Yehia Al Razazz MeetingDocumento2 pagineJazz Concert Preliminary Preparations: 1. Dr. Yehia Al Razazz MeetingMohab SamehNessuna valutazione finora

- StudentRecital Classical TemplateDocumento2 pagineStudentRecital Classical TemplateMohab SamehNessuna valutazione finora

- M.sc. Research Proposal GuideDocumento1 paginaM.sc. Research Proposal GuideMohab SamehNessuna valutazione finora

- Interview QuestionsDocumento1 paginaInterview QuestionsMohab SamehNessuna valutazione finora

- ChapterDocumento37 pagineChapterMohab SamehNessuna valutazione finora

- Excel Document Tutorial For BeginnersDocumento2 pagineExcel Document Tutorial For BeginnersSehar KhanNessuna valutazione finora

- 3WA11 DatashDocumento9 pagine3WA11 DatashsuadNessuna valutazione finora

- Minerva Control PanelDocumento4 pagineMinerva Control Panellucas barriosNessuna valutazione finora

- Series RLC Circuit: ObjectivesDocumento10 pagineSeries RLC Circuit: ObjectivesAhmed JamalNessuna valutazione finora

- JuiceMeter Installation Manual enDocumento22 pagineJuiceMeter Installation Manual env2vorovendrellNessuna valutazione finora

- TDJ709008A65FT0Documento1 paginaTDJ709008A65FT0Asim SaleemNessuna valutazione finora

- Philips hts3020Documento45 paginePhilips hts3020Robert VojakNessuna valutazione finora

- Toshiba Manual Tecra R950-R940Documento199 pagineToshiba Manual Tecra R950-R940Ricardo5199Nessuna valutazione finora

- Wireless RF Project Report For Web PDFDocumento70 pagineWireless RF Project Report For Web PDFpedro100% (1)

- ET7102-Microcontroller Based System DesignDocumento19 pagineET7102-Microcontroller Based System DesignbalaNessuna valutazione finora

- Lab 08Documento17 pagineLab 08salloum18Nessuna valutazione finora

- Netis WF2216 Quick Installation Guide V1.0Documento1 paginaNetis WF2216 Quick Installation Guide V1.0Daniel Teodor PoruțiuNessuna valutazione finora

- Analog Circuits in 28 NM and 14 NM Finfet: Lukas Dörrer, Franz Kuttner, Francesco Conzatti, and Patrick TortaDocumento15 pagineAnalog Circuits in 28 NM and 14 NM Finfet: Lukas Dörrer, Franz Kuttner, Francesco Conzatti, and Patrick TortaRodrigo SantosNessuna valutazione finora

- Electronic SymbolDocumento28 pagineElectronic Symbolsponge bobNessuna valutazione finora

- Instruction Manual Universal Fieldbus-Gateway Unigate CM - ProfibusDocumento62 pagineInstruction Manual Universal Fieldbus-Gateway Unigate CM - ProfibusFakhri GhrairiNessuna valutazione finora

- Assignment 1: Implementation of A Processor (10marks) : Constant RDST OpcodeDocumento6 pagineAssignment 1: Implementation of A Processor (10marks) : Constant RDST OpcodeTharakram KorripatiNessuna valutazione finora

- Antenna SpecificationsDocumento2 pagineAntenna SpecificationsRobertNessuna valutazione finora

- Information Theory: Dr. Muhammad Imran FaridDocumento32 pagineInformation Theory: Dr. Muhammad Imran FaridMalik Adil FarooqNessuna valutazione finora

- Battery-Powered Night Lamp CircuitDocumento1 paginaBattery-Powered Night Lamp Circuitrik206Nessuna valutazione finora

- M29F400T M29F400B: 4 Mbit (512Kb x8 or 256Kb x16, Boot Block) Single Supply Flash MemoryDocumento34 pagineM29F400T M29F400B: 4 Mbit (512Kb x8 or 256Kb x16, Boot Block) Single Supply Flash MemorykokotnoNessuna valutazione finora

- GLZ201600026 Attach2Documento10 pagineGLZ201600026 Attach2Lucas ZelioliNessuna valutazione finora

- EENG 271 Signals and Systems: Linear FunctionDocumento13 pagineEENG 271 Signals and Systems: Linear Functionmohammed alansariNessuna valutazione finora

- 8810 UserguideDocumento64 pagine8810 UserguideUTC2011Nessuna valutazione finora

- .Design and Synthesis of BPSK QPSK Using SimulinkDocumento3 pagine.Design and Synthesis of BPSK QPSK Using SimulinkSudeepa HerathNessuna valutazione finora

- 1131expt 03 MCC Be A SH21Documento7 pagine1131expt 03 MCC Be A SH21AlkaNessuna valutazione finora

- BD135 BD137/BD139: NPN Silicon TransistorDocumento4 pagineBD135 BD137/BD139: NPN Silicon TransistorCristianNessuna valutazione finora

- Matrix 2000 Standalone Inverter C A4size PDFDocumento2 pagineMatrix 2000 Standalone Inverter C A4size PDFYoYoRamezNessuna valutazione finora