Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Preinforme p3 Circuitos

Caricato da

John HerreraTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Preinforme p3 Circuitos

Caricato da

John HerreraCopyright:

Formati disponibili

ELECTRONICA DIGITAL 1- 17 DE ABRIL DE 2017 1

Preinforme P3: Circuitos Sncronos y Contadores

Herrera P. John S.1 , Ramirez B. Nestor D. 2 , Guzman R. Jaime A.3 ,

jsherrerap@unal.edu.co 1 ndramirezb@unal.edu.co 2 jaaguzmanro@unal.edu.co 3

Departamento de Ingeniera Electrica y Electronica

Universidad Nacional de Colombia

AbstractEl presente documento muestra los conceptos pre- estado del sistema y sus salidas. Por tanto, una de sus

vios y los procedimientos para la preparacion de una correcta caractersticas es que las mismas entradas en estados

ejecucion de la practica 3. diferentes dan lugar a salidas distintas, ya que estas

dependen tambien del estado [2].

I. O BJETIVO

Entender mas afondo la logica secuencial, sus

caractersticas principales, ventajas con su respectiva

implementacion.

II. M ARCO TE ORICO

Logica secuencial

La Logica Secuencial es el metodo de ordenamiento

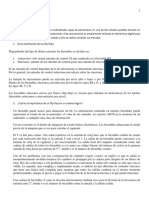

Figure 1: Composicion de un circuito sncrono

de acciones, razonamiento, y expresion de la

automatizacion de maquinaria, equipos y procesos.

La logica secuencial es un tipo de circuito de logica

que salida dependa no solo de la actual entrada pero El bloque Estado esta formado por biestables, todos

tambien de la historia de la entrada. Esto esta en ellos sincronizados con la misma senal de reloj.

contraste con logica combinacional, del que salida es Flip flop

una funcion, y solamente de, la actual entrada. Es

decir la logica secuencial tiene almacenaje (memoria) Un biestable (flip-flop en ingles), es un multivibrador

mientras que la logica combinacional no. En los capaz de permanecer en uno de dos estados posibles

Circuitos Secuenciales las salidas dependen de la durante un tiempo indefinido en ausencia de

conducta anterior del circuito, as como de los valores perturbaciones. Esta caracterstica es ampliamente

presentes en las entradas[1]. utilizada en electronica digital para memorizar

informacion. El paso de un estado a otro se realiza

Circuito sncrono variando sus entradas. Dependiendo del tipo de dichas

entradas los biestables se dividen en:

En los circuitos combinacionales la salida en un de-

terminado momento depende u nicamente de los val- -Asncronos: solamente tienen entradas de control. El

ores de las senales de entrada en el mismo instante. mas empleado es el biestable RS.

Sin embargo, en el mundo real la mayor parte de -Sncronos: ademas de las entradas de control posee una

los sistemas con los que nos enfrentamos tienen una entrada de sincronismo o de reloj.

dimension adicional: el funcionamiento de los mismos Si las entradas de control dependen de la de sincronismo

depende no u nicamente de sus entradas actuales, sino se denominan sncronas y en caso contrario asncronas.

tambien de la historia por la que han pasado. As, Por lo general, las entradas de control asncronas

los circuitos secuenciales surgen para solucionar las prevalecen sobre las sncronas.

limitaciones intrnsecas de los combinacionales. Los La entrada de sincronismo puede ser activada por nivel

circuitos secuenciales son sistemas que, ademas de (alto o bajo) o por flanco (de subida o de bajada). Dentro

entradas y salidas, tambien tienen estados que recuerdan de los biestables sncronos activados por nivel estan los

la historia pasada por el circuito. Utilizan la informacion tipos RS y D, y dentro de los activos por flancos los

del estado conjuntamente con una combinacion logica tipos JK, T y D.

de sus entradas de datos para determinar el futuro Los biestables sncronos activos por flanco (flip-flop)

Universidad Nacional de Colombia -Sede Bogota- Facultad de Ingeniera, se crearon para eliminar las deficiencias de los latches

Departamento de Ingeniera Electrica y Electronica- Electronica digital 1 (biestables asncronos o sincronizados por nivel)[3].

ELECTRONICA DIGITAL 1- 17 DE ABRIL DE 2017 2

III. P REGUNTAS Se muestra un numero a la vez y se va cambiando a una

1. Que es un divisor de frecuencia y como se construye? alta frecuencia ara que parezca que se muestran todos a

Se dice divisor de frecuencia un circuito que recibe la vista humana.

en entrada una senal de una frecuencia determinada f 4. Que frecuencias de actualizacion se utilizan para que el

y da una senal de salida de frecuencia f /n donde n ojo humano no perciba la multiplexacion? Las frecuencias

es un numero entero. La necesidad de un divisor de minimas requeridas para la la actualizacion es de 60Hz.

frecuencia, ya que tiene tanto con una y la misma senal

de clock debe conducir circuitos en diferentes frecuencias, R EFERENCES

y porque es mas facil para estabilizar por medio de un

[1] L OGICA SECUENCIAL Available on:

circuito en el cuarzo un circuito dado a una tasa superior https://sites.google.com/site/electronicadigitaluvfime/4-logica-

secuencial -Abril 2017.

y luego obtener una frecuencia mas baja, que tambien [2] C IRCUITOS SECUENCIALES SI NCRONOS Y ASI NCRONOS Available

se estabilizado, aunque no es un cristal de cuarzo a la on: https://es.slideshare.net/alexaramirez7549/circuitos-secuenciales-

frecuencia deseada. sincronos-y-asincronos -Abril 2017.

[3] B IESTABLE Available on: https://es.wikipedia.org/wiki/Biestable -Abril

Conectando en cascada multiples flip flops de tipo T se 2017.

puede obtener divisores de frecuencia multiplos de 2 de [4] D IVISORES DE FRECUENCIA Available on:

acuerdo con la siguiente formula: https://scuolaelettrica.it/escuelaelectrica/elettronica/differe6.php

-Abril 2017.

[5] D IVISOR DE FRECUENCIA Available on:http://es.edaboard.com/topic-

f n = f /2n 1696772.0.html -Abril 2017.

donde n es un numero entero[4].

2. Como se describe un divisor de frecuencia en Verilog?

A continuacion se describe un divisor de frecuencia de

50MHz a 1Hz. Las funciones usadas son always, if y

else [5].

module divisor_de_frecuecia(clk,clk_out);

input clk;

output reg clk_out;

reg rst;

reg [25:0] counter;

initial

rst=0;

always @(posedge clk or negedge rst)

begin

if(!rst)

begin

rst<=1;

counter<=26d0;

clk_out <= 1b0;

end

else

if(counter==26d49_999_999) //va convertir un clk de 100mhz a 1hz

begin

counter<=26d0;

clk_out <= clk_out;

end

else

begin

counter<=counter+1;

end

end

endmodule

3. Como se realiza la multiplexacion para la visualizacion

en multiples displays de 7 segmentos?

Potrebbero piacerti anche

- FLIP FLOP Marco Teorico + 2pregDocumento17 pagineFLIP FLOP Marco Teorico + 2pregrobertitoNessuna valutazione finora

- Digital TelmexDocumento14 pagineDigital TelmexRaul Andrade100% (1)

- Practica 2 - Ejercicios en VHDLDocumento17 paginePractica 2 - Ejercicios en VHDLAlejandro StaveleyNessuna valutazione finora

- Laboratorio de Adicionadores BinariosDocumento5 pagineLaboratorio de Adicionadores Binariospc hoyNessuna valutazione finora

- Actividad 1 Manuel RinconDocumento7 pagineActividad 1 Manuel RinconMANUEL RINCON GONZALEZNessuna valutazione finora

- Diseño de FSM Con SSI y MSI 2010 PDFDocumento38 pagineDiseño de FSM Con SSI y MSI 2010 PDFErnesto RosalesNessuna valutazione finora

- Latch, Flip Flops, Maquinas de Estados FinitosDocumento28 pagineLatch, Flip Flops, Maquinas de Estados FinitosItaloCardenasNessuna valutazione finora

- Contadores AscendentesDocumento8 pagineContadores AscendentesMauricio lópez hernándezNessuna valutazione finora

- Unidad 1 Maquinas de Estado Sistemas Secuenciales.Documento10 pagineUnidad 1 Maquinas de Estado Sistemas Secuenciales.Jovana Salas CentenoNessuna valutazione finora

- Circuitos Secuenciales BasicosDocumento22 pagineCircuitos Secuenciales BasicosEdgar Iván Marcelo LópezNessuna valutazione finora

- SecuencialesDocumento15 pagineSecuencialesjose gonzalezNessuna valutazione finora

- Digitales Practica 6Documento10 pagineDigitales Practica 6Joan RuizNessuna valutazione finora

- Reloj Digital ReporteDocumento15 pagineReloj Digital ReporteHertz77Nessuna valutazione finora

- Electrónica DigitalDocumento13 pagineElectrónica DigitalgeorgeNessuna valutazione finora

- Practica 5Documento9 paginePractica 5vagprogrammerNessuna valutazione finora

- 4.1 Flip-Flops TrejoDocumento18 pagine4.1 Flip-Flops TrejoAndres RodriguezNessuna valutazione finora

- Informe 5 PrevioDocumento5 pagineInforme 5 PrevioEmmanuel AlvizNessuna valutazione finora

- Circuitos SecuencialesDocumento74 pagineCircuitos SecuencialesRodolfo Garcia GalazNessuna valutazione finora

- Informe de Practicas de Circuitos Digitales Practica #5Documento8 pagineInforme de Practicas de Circuitos Digitales Practica #5carlos sanchezNessuna valutazione finora

- Analisis Transitorio Circuitos PDFDocumento7 pagineAnalisis Transitorio Circuitos PDFChristian HernandezNessuna valutazione finora

- Lógica Secuencial SincrónicaDocumento18 pagineLógica Secuencial SincrónicaAlexanderJ.RojasHerreraNessuna valutazione finora

- Actividad 3.1-ADocumento5 pagineActividad 3.1-ADimas Ramirez PortasNessuna valutazione finora

- LuisDocumento22 pagineLuisLuis Blas TorresNessuna valutazione finora

- Compedio de Sistema Unidad 3 y 4Documento132 pagineCompedio de Sistema Unidad 3 y 4DMA ESTUDIOSNessuna valutazione finora

- Recopilacion Sistema Compendio y DiaspositivasDocumento312 pagineRecopilacion Sistema Compendio y DiaspositivasDaniel ErazoNessuna valutazione finora

- Simulacion de Descripciones en VHDLDocumento6 pagineSimulacion de Descripciones en VHDLNico BernalNessuna valutazione finora

- T Lab #03. Laboratorio Diseño Digital - 030218Documento34 pagineT Lab #03. Laboratorio Diseño Digital - 030218luis carrasquelNessuna valutazione finora

- Control Automatico de LlenadoDocumento8 pagineControl Automatico de LlenadoVictor Hugo Castañeda Lavin0% (1)

- Digitales 4Documento37 pagineDigitales 4Alissa DimasNessuna valutazione finora

- Chapa EléctricaDocumento20 pagineChapa EléctricaCarlos ArriazaNessuna valutazione finora

- Primera Leccion 1Documento20 paginePrimera Leccion 1Eduardo Adair martinezNessuna valutazione finora

- Informe 4 - Felipe Rojas ArredondoDocumento6 pagineInforme 4 - Felipe Rojas ArredondoRicardoJimenezNessuna valutazione finora

- Guia Practica 6aDocumento7 pagineGuia Practica 6aanthony RomeroNessuna valutazione finora

- Trabajo Investigación Tema 4 (N°c.18500311)Documento32 pagineTrabajo Investigación Tema 4 (N°c.18500311)Jason ClementeNessuna valutazione finora

- Lab 5Documento8 pagineLab 5juan pablo rojas ruizNessuna valutazione finora

- Qdoc - Tips Espectro Mediante SimulinkDocumento39 pagineQdoc - Tips Espectro Mediante SimulinkKrisha Mae ChaNessuna valutazione finora

- Laboratorio 3 Sistemas Digitales PrevioDocumento14 pagineLaboratorio 3 Sistemas Digitales PrevioJhulian VillafuerteNessuna valutazione finora

- Memoria LCELDocumento51 pagineMemoria LCELAlberto Lorente LealNessuna valutazione finora

- 07 electronicaII ContenidosDocumento21 pagine07 electronicaII ContenidosJavi Pinto0% (3)

- Protocolo Individual Unidad 4 de Sistemas DigitalesDocumento3 pagineProtocolo Individual Unidad 4 de Sistemas DigitalesTati RamirezNessuna valutazione finora

- Guias Ceii p6 2014Documento8 pagineGuias Ceii p6 2014Emmanuel AlvizNessuna valutazione finora

- PULSOSDocumento7 paginePULSOSedwinNessuna valutazione finora

- Reporte Práctica Circuitos Combinatorios y Secuenciales CHyNDocumento8 pagineReporte Práctica Circuitos Combinatorios y Secuenciales CHyN19610658Nessuna valutazione finora

- Proyecto de RPM de Un MotorDocumento4 pagineProyecto de RPM de Un Motorbigmaster_777Nessuna valutazione finora

- Informe 6 DigitalDocumento2 pagineInforme 6 Digitalcristhian jaya0% (1)

- Lab N°5 Microelectrónica (1161481 - 1161167)Documento9 pagineLab N°5 Microelectrónica (1161481 - 1161167)Julian MolinaNessuna valutazione finora

- Informe #6 EncoderDocumento5 pagineInforme #6 EncoderCatalina GonzálezNessuna valutazione finora

- Digital TLMXDocumento39 pagineDigital TLMXPaul Granados R.Nessuna valutazione finora

- Fundamentos de Sistemas de Control Laboratorio 2Documento5 pagineFundamentos de Sistemas de Control Laboratorio 2andres felipe martinezNessuna valutazione finora

- Laboratorio Primera Parte SistemasDocumento5 pagineLaboratorio Primera Parte SistemasMDLR YTNessuna valutazione finora

- Sistemas Eléctricos y Electrónicos TAREA 1Documento8 pagineSistemas Eléctricos y Electrónicos TAREA 1Cristian LopezNessuna valutazione finora

- Trabajo Unidad 4Documento12 pagineTrabajo Unidad 4Carlos Martinez VazquezNessuna valutazione finora

- Informe de SemaforoDocumento3 pagineInforme de SemaforoKenny VarelaNessuna valutazione finora

- MINIMIZACIONDocumento11 pagineMINIMIZACIONMxm Monzter GervacioNessuna valutazione finora

- Aplicaciones de Los Circuitos SecuencialesDocumento6 pagineAplicaciones de Los Circuitos SecuencialesAndy Barraza0% (1)

- Informe Digital I - Practica 1Documento6 pagineInforme Digital I - Practica 1Raúl A.Nessuna valutazione finora

- Articulo Feria DigitalesDocumento4 pagineArticulo Feria Digitalesjaider torresNessuna valutazione finora

- RPerezBatista Reporte#1Documento14 pagineRPerezBatista Reporte#1Victor LópezNessuna valutazione finora

- Circuitos Secuenciales SincronosDocumento5 pagineCircuitos Secuenciales SincronosDaniela SevillaNessuna valutazione finora

- Calidad Del Aire - Art.304Documento2 pagineCalidad Del Aire - Art.304Luce Dávila FernandezNessuna valutazione finora

- Guia de Actividades y Rúbrica de Evaluación - Unidad 3 - Tarea 3 - Vídeo Donde Informe Sobre La Complejidad en Nuestro ContextoDocumento6 pagineGuia de Actividades y Rúbrica de Evaluación - Unidad 3 - Tarea 3 - Vídeo Donde Informe Sobre La Complejidad en Nuestro ContextopimientabravoNessuna valutazione finora

- MASSEY Teorias Migracion InternacionalDocumento27 pagineMASSEY Teorias Migracion Internacionalchinopat100% (1)

- LINFEDEMADocumento72 pagineLINFEDEMARichard A. MejíasNessuna valutazione finora

- Creados - para - Ser - Como Cristo.v2Documento10 pagineCreados - para - Ser - Como Cristo.v2Luis CorderoNessuna valutazione finora

- Microbiologia de Alimentos TermoprocesadosDocumento26 pagineMicrobiologia de Alimentos TermoprocesadosCecilia De la cruzNessuna valutazione finora

- Cuadro Filosofía Esa Búsqueda ReflexivaDocumento7 pagineCuadro Filosofía Esa Búsqueda ReflexivaJoaquin RiverosNessuna valutazione finora

- Calculo Hidraulico de Reservorio 13.5 m3Documento4 pagineCalculo Hidraulico de Reservorio 13.5 m3José Eduardo Cruz GómezNessuna valutazione finora

- Importancia Del Mantenimiento de MotoresDocumento6 pagineImportancia Del Mantenimiento de MotoresAnonymous rsIdXBVJe5Nessuna valutazione finora

- Regeneración Ósea Guiada Simultánea A La Colocación de Implantes: Presentación de Un Caso ClínicoDocumento8 pagineRegeneración Ósea Guiada Simultánea A La Colocación de Implantes: Presentación de Un Caso ClínicoSABUESO FINANCIERONessuna valutazione finora

- Metrado Tuberia Desague PVCDocumento4 pagineMetrado Tuberia Desague PVCJHonHuberthCalderonAguilarNessuna valutazione finora

- Corte Administrativo Estadistica 2022Documento2 pagineCorte Administrativo Estadistica 2022eloy rubio matosNessuna valutazione finora

- Comercio Electrónico - Tarea 2 MairelyDocumento2 pagineComercio Electrónico - Tarea 2 MairelyMAIRELY CRUZNessuna valutazione finora

- Tabel BajaDocumento49 pagineTabel BajaGamaHkiJatengdiyNessuna valutazione finora

- Planeacion AgregadaDocumento1 paginaPlaneacion AgregadaEdgar Noriega GarciaNessuna valutazione finora

- Inecuaciones XDocumento3 pagineInecuaciones XRamiro DominguezNessuna valutazione finora

- Informe Especies MayoresDocumento24 pagineInforme Especies MayoresAlvaro ATNessuna valutazione finora

- Acido Acetico en VinagreDocumento3 pagineAcido Acetico en VinagreJuanse VasquezNessuna valutazione finora

- Proyecto Edu en NutDocumento18 pagineProyecto Edu en NutMadai SotoNessuna valutazione finora

- Guia 1 - Grado 6Documento2 pagineGuia 1 - Grado 6edwin yepesNessuna valutazione finora

- Esquema MPSDocumento20 pagineEsquema MPSCarlos MendezNessuna valutazione finora

- Semana 15 - PDF - Formato de Sílabo para El Plan de CapacitaciónDocumento3 pagineSemana 15 - PDF - Formato de Sílabo para El Plan de CapacitaciónFrank SubileteNessuna valutazione finora

- Viuda NegraDocumento4 pagineViuda Negrajimena feitoNessuna valutazione finora

- Boaventura de Sousa Santos - Epistemología Del SurDocumento23 pagineBoaventura de Sousa Santos - Epistemología Del SurGabrielito ParavanoNessuna valutazione finora

- Libro 2 U1 Clasificación de Funciones RealesDocumento18 pagineLibro 2 U1 Clasificación de Funciones RealesG&K FreshiesNessuna valutazione finora

- Curricula CCNA Exploration 4 Instalable, PDF, PPT - IdentiDocumento4 pagineCurricula CCNA Exploration 4 Instalable, PDF, PPT - Identimacabeo12Nessuna valutazione finora

- 04 - Capitulo IVBDocumento2 pagine04 - Capitulo IVBCristhian De La PavaNessuna valutazione finora

- La Arquitectura en La Era de La Austeridad PDFDocumento98 pagineLa Arquitectura en La Era de La Austeridad PDFComité Nacional Boliviano IcomosNessuna valutazione finora

- Geodesia y Su Impacto en La Vida CotidianaDocumento2 pagineGeodesia y Su Impacto en La Vida CotidianaGianella RamonNessuna valutazione finora

- Términos de Mecánica de Suelos.Documento6 pagineTérminos de Mecánica de Suelos.luisNessuna valutazione finora