Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Cb3lv-3i 100M0000

Caricato da

amiteshtripathiDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Cb3lv-3i 100M0000

Caricato da

amiteshtripathiCopyright:

Formati disponibili

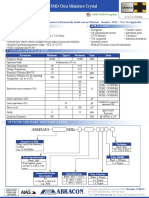

Model CB3 & CB3LV

HCMOS/TTL Clock Oscillator

FEATURES

Standard 7.0mm x 5.0mm 4-Pad Surface Mount Package

HCMOS/TTL Compatible Output

Fundamental and 3rd Overtone Crystal Designs

Frequency Range 1 200 MHz

Frequency Stability 50 ppm Standard, 25 ppm and 20 ppm Available

Operating Voltages +5.0Vdc or +3.3Vdc

Operating Temperature to -40C to +85C

Output Enable Standard

Tape & Reel Packaging

RoHS/Green Compliant (6/6)

APPLICATIONS

Applications for Model CB3 and CB3LV include digital video, networking equipment, wireless communications,

broadband access, Ethernet/Gigabit Ethernet, microprocessors/DSP/FPGA, storage area networks, fiber channel,

computers and peripherals, test and measurement, SONET/SDH/DWDM, base stations and Pico cells.

ORDERING INFORMATION

CB3 - - M

SUPPLY VOLTAGE FREQUENCY IN MHz

LV = +3.3Vdc 3

M - indicates MHz and decimal point.

Blank = +5.0Vdc

FREQUENCY STABILITY OPERATING TEMPERATURE RANGE

1 C = -20C to +70C [standard]

6 = 20 ppm 7 = 32 ppm

2

5 = 25 ppm 2

I = -40C to +85C 1

2 = 100 ppm

3 = 50 ppm [std]

1] 6I Stability/Temperature combination is not available.

2] These stabilities are not recommended for new designs.

3] Frequency is recorded with only leading significant digits before the M and 4 - 6 significant digits after the M (including zeros).

[Ex. 3.579545 MHz, code as 3M579545; 14.31818 MHz, code as 14M31818; 125 MHz, code as 125M0000]

4] CTS Distributors may add a -T or -1 at the end of the part number to indicate Tape and Reel packaging.

Not all performance combinations and frequencies may be available.

Contact your local CTS Representative or CTS Customer Service for availability.

PACKAGING INFORMATION [reference]

Device quantity is 1,000 pieces maximum per reel.

Document No. 008-0256-0 Page 1- 3 Rev. G

www.ctscorp.com

Model CB3 & CB3LV

7.0mm x 5.0mm Low Cost

HCMOS/TTL Clock Oscillator

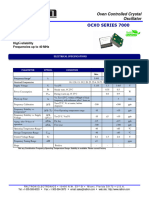

ELECTRICAL CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNIT

Maximum Supply Voltage VCC - -0.5 - +7.0 V

Storage Temperature TSTG - -40 - +100 C

Frequency Range

CB3 fO - 1.5 - 107 MHz

CB3LV - 1.5 - 200

Frequency Stability f/fO See Note 1 and Ordering Information - - 20,25,50 or 100 ppm

Aging f First year - 3 5 ppm

Operating Temperature

Commercial TA - -20 +70 C

25

Industrial -40 +85

Supply Voltage

CB3 VCC 10% 4.5 5.0 5.5 V

CB3LV 3.0 3.3 3.6

Supply Current Frequency Range

Tested load condition noted for typical values.

CB3 1.5MHz to 20MHz CL=50pF - 10 25

20.001MHz to 80MHz CL=50pF - 30 50

ICC CL=15pF mA

80.001MHz to 107MHz - 40 80

CB3LV 1.5MHz to 20MHz CL=15pF - 7 12

20.001MHz to 80MHz CL=15pF - 20 40

80.001MHz to 200MHz CL=15pF - 30 60

ELECTRICAL PARAMETERS

1.5MHz to 50MHz - - 50

Output Load CL 50.001MHz to 80MHz - - 30 pF

80.001MHz to 200MHz - - 15

Output Voltage Levels

Logic '1' Level CMOS Load 90%VCC

VOH - -

10 TTL LOAD VCC-0.6V V

Logic '0' Level CMOS 10%VCC

VOL - -

TTL Load 0.4

Output Current

Logic '1' Level IOH VOH = 3.9V/2.2V VCC = 4.5V/3.0V - - -16/-8 mA

Logic '0' Level IOL VOL = 0.4V VCC = 4.5V/3.0V - - +16/+8

Output Duty Cycle SYM @ 50% Level 45 - 55 %

Rise and Fall Time @ 10% - 90% Levels

Tested load condition noted for typical values.

CB3 1.5MHz to 20MHz CL=50pF - 8 10

20.001MHz to 80MHz CL=50pF - 5 8

TR, TF CL=15pF ns

80.001MHz to 200MHz - 2.5 5

CB3LV 1.5MHz to 20MHz CL=15pF - 6 8

20.001MHz to 80MHz CL=15pF - 3 5

80.001MHz to 200MHz CL=15pF - 1.5 3

Start Up Time TS Application of VCC - - 10 ms

Enable Function

Enable Input Voltage VIH Pin 1 Logic '1', Output Enabled 2.0 - - V

Disable Input Voltage VIL Pin 1 Logic '0', Output Disabled - - 0.8

Enable Time TPLZ Pin 1 Logic '1' - - 200 ns

Standby Current IST Pin 1 Logic '0', Output Disabled - - 10 A

Period Jitter, Pk-Pk - - - - 50

Period Jitter, RMS - - - - 5 ps

Phase Jitter, RMS - Bandwidth 12kHz - 20MHz - - 1

Notes:

1. Inclusive of initial tolerance at time of shipment, changes in supply voltage, load, temperature and 1st year aging.

Document No. 008-0256-0 Page 2 - 3 Rev. G

Model CB3 & CB3LV

7.0mm x 5.0mm Low Cost

HCMOS/TTL Clock Oscillator

ELECTRICAL CHARACTERISTICS

LVCMOS OUTPUT WAVEFORM TEST CIRCUIT, CMOS LOAD

ENABLE TRUTH TABLE D.U.T. PIN ASSIGNMENTS

PIN SYMBOL DESCRIPTION

PIN 1 PIN 3

Logic 1 Output 1 EOH Enable

Open Output 2 GND Circuit & Package Ground

Logic 0 High Imp.

3 Output RF Output

4 VCC Supply Voltage

MECHANICAL SPECIFICATIONS

PACKAGE DRAWING MARKING INFORMATION

1. ** Manufacturing Site Code.

[Note a dash may follow the site code and is acceptable.]

2. XXXMXXXXXX Frequency is marked with only

leading significant digits before the M and

4 6 digits after the M (including zeros).

CTS**CB3 Ex. XMXXXXXX [3M579545]

XXMXXXXX [14M31818]

XXXMXXXXXX XXXMXXXX [125M0000]

YYWWSTV 3. YYWW Date code, YY year, WW week.

4. ST Frequency stability/temperature code.

[Refer to Ordering Information.]

5. V Voltage code. 3 = 3.3V, 5 = 5.0V.

NOTES

1. Termination pads [e4]. Barrier-plating is nickel

[Ni] with gold [Au] flash plate.

2. Reflow conditions per JEDEC J-STD-020, 260C

maximum.

3. Moisture Sensitivity Level 1 per JEDEC J-STD-020.

SUGGESTED SOLDER PAD GEOMETRY

CBYPASS should be 0.01 uF.

Document No. 008-0256-0 Page 3 - 3 Rev. G

Potrebbero piacerti anche

- Immigrant Italian Stone CarversDocumento56 pagineImmigrant Italian Stone Carversglis7100% (2)

- Midterm Exam Gor Grade 11Documento2 pagineMidterm Exam Gor Grade 11Algelle AbrantesNessuna valutazione finora

- Datasheet 636Documento4 pagineDatasheet 636agus satyaNessuna valutazione finora

- Ecs 3225S-1064150Documento3 pagineEcs 3225S-1064150miri10861Nessuna valutazione finora

- Tcxo - 0749c Older Datasheet - Presently Using in LewDocumento3 pagineTcxo - 0749c Older Datasheet - Presently Using in LewMohendra PatiNessuna valutazione finora

- Ecs Txo 2520Documento2 pagineEcs Txo 2520miri10861Nessuna valutazione finora

- Standard Specifications:: Applications: FeaturesDocumento3 pagineStandard Specifications:: Applications: FeaturesNguyen HuanNessuna valutazione finora

- ABL Series: Standard SpecificationsDocumento3 pagineABL Series: Standard SpecificationsVinny SinghNessuna valutazione finora

- STC53K SeriesDocumento4 pagineSTC53K SeriesonallpelinNessuna valutazione finora

- Parameters Minimum Typical Maximum Units NotesDocumento4 pagineParameters Minimum Typical Maximum Units NotesKiran PatelNessuna valutazione finora

- Vectron: InternationalDocumento5 pagineVectron: Internationalm3y54mNessuna valutazione finora

- SiT1552 DatasheetDocumento12 pagineSiT1552 DatasheetMustafa TuncNessuna valutazione finora

- QCL Series: General Specifi Cations Equivalent Series Resistance (ESR)Documento2 pagineQCL Series: General Specifi Cations Equivalent Series Resistance (ESR)Alberto Fernández VázquezNessuna valutazione finora

- ABM8GDocumento2 pagineABM8GJorge LealNessuna valutazione finora

- Abracom ABM3Documento2 pagineAbracom ABM3Joseph Abou El OulaNessuna valutazione finora

- Abm8Aig Abm8AigDocumento4 pagineAbm8Aig Abm8AigpepeNessuna valutazione finora

- ABMMDocumento2 pagineABMMenrique.ci.martinezNessuna valutazione finora

- OX7000 Series DatasheetDocumento4 pagineOX7000 Series Datasheetsanjubonik2017Nessuna valutazione finora

- NIC Components NAWE SeriesDocumento4 pagineNIC Components NAWE SeriesNICCompNessuna valutazione finora

- MF-2500DS-T12-18x/19x/20x/21x MF-2500DS-R13-18x MF-2500DS-R14-19x/20x/21xDocumento9 pagineMF-2500DS-T12-18x/19x/20x/21x MF-2500DS-R13-18x MF-2500DS-R14-19x/20x/21xGabriel RacovskyNessuna valutazione finora

- NTH089 C3Documento3 pagineNTH089 C3Javier LopezNessuna valutazione finora

- OLT-C-Optical-Module PotenciasDocumento8 pagineOLT-C-Optical-Module PotenciasWilmer MonteroNessuna valutazione finora

- BR93H86RF-2LB: 125 Operation Microwire BUS EEPROM (3-Wire)Documento29 pagineBR93H86RF-2LB: 125 Operation Microwire BUS EEPROM (3-Wire)Tomi OzzyNessuna valutazione finora

- ABNTC-0201: MSL Level: 2A (This Product Is Packed With Dry Packaging)Documento3 pagineABNTC-0201: MSL Level: 2A (This Product Is Packed With Dry Packaging)ricky syandiNessuna valutazione finora

- Standard Specifications:: Applications: FeaturesDocumento2 pagineStandard Specifications:: Applications: FeaturespepeNessuna valutazione finora

- SP GB LX CDFM ZTDocumento9 pagineSP GB LX CDFM ZTJoyner Daniel Garcia DuarteNessuna valutazione finora

- 50-000MHZX09 DatasheetDocumento2 pagine50-000MHZX09 DatasheetsongdashengNessuna valutazione finora

- 40-000MHZX09 DatasheetDocumento2 pagine40-000MHZX09 DatasheetsongdashengNessuna valutazione finora

- 6C WDM 0220BDDocumento7 pagine6C WDM 0220BDNugi Anugrah M1221562Nessuna valutazione finora

- TS0021ADocumento8 pagineTS0021AitflyiljulwhzthzxfNessuna valutazione finora

- Abl 16.000MHZ B2 PDFDocumento3 pagineAbl 16.000MHZ B2 PDFkarthik4096Nessuna valutazione finora

- TS0016ADocumento8 pagineTS0016AitflyiljulwhzthzxfNessuna valutazione finora

- Typical Applications Features: 10 MHZ - 200 MHZ 10, 19.44, 20.48, 38.88, 77.76MhzDocumento6 pagineTypical Applications Features: 10 MHZ - 200 MHZ 10, 19.44, 20.48, 38.88, 77.76MhzdexkezzNessuna valutazione finora

- SMD Crystal: Operating Conditions / Electrical CharacteristicsDocumento2 pagineSMD Crystal: Operating Conditions / Electrical CharacteristicsManu MathewNessuna valutazione finora

- 6C WDM 0240adDocumento7 pagine6C WDM 0240adIdris KusumaNessuna valutazione finora

- ABMM2Documento3 pagineABMM2QAISER IJAZNessuna valutazione finora

- 6C WDM 0240BDDocumento7 pagine6C WDM 0240BDIdris KusumaNessuna valutazione finora

- 40GBASE-ZR4 QSFP+ 1310nm 80km DDM SMF Transceiver P/N: QT-QSFP+-ZR4Documento12 pagine40GBASE-ZR4 QSFP+ 1310nm 80km DDM SMF Transceiver P/N: QT-QSFP+-ZR4Utel TVNessuna valutazione finora

- Ecs 2520SMV EcsDocumento2 pagineEcs 2520SMV EcsVictor GomesNessuna valutazione finora

- F230TSDocumento2 pagineF230TScuentadosngrokNessuna valutazione finora

- Anexa 3 Qxp85b4 02d ViDocumento14 pagineAnexa 3 Qxp85b4 02d Vistelea7577Nessuna valutazione finora

- 1.25Gb 20klm 1490T-1310R SM (Standard Code)Documento6 pagine1.25Gb 20klm 1490T-1310R SM (Standard Code)Sean SerinNessuna valutazione finora

- SiT1534 Rev1p31Documento12 pagineSiT1534 Rev1p31Oleh SehedaNessuna valutazione finora

- SiT1533 Rev1.4 03202018Documento13 pagineSiT1533 Rev1.4 03202018Oleh SehedaNessuna valutazione finora

- Dsk321std Car enDocumento1 paginaDsk321std Car en천일계전Nessuna valutazione finora

- 7W-25.000MBA - CMOS OscillatorsDocumento2 pagine7W-25.000MBA - CMOS OscillatorsLau LauNessuna valutazione finora

- NIC Components NMC High CV SeriesDocumento4 pagineNIC Components NMC High CV SeriesNICCompNessuna valutazione finora

- 1.25Gb 20klm SM 1550nm LC (Cisco Coded)Documento7 pagine1.25Gb 20klm SM 1550nm LC (Cisco Coded)Sean SerinNessuna valutazione finora

- Abls7M2: Standard SpecificationsDocumento5 pagineAbls7M2: Standard Specificationssteven MelgarejoNessuna valutazione finora

- Description Features: 1 To 26 Mhz, Ultra-Small Μpower OscillatorDocumento10 pagineDescription Features: 1 To 26 Mhz, Ultra-Small Μpower OscillatorSantiago OspinaNessuna valutazione finora

- Shenzhen Hifibercom Technology Co.,Ltd 10G Bidi 20km Optical ModuleDocumento8 pagineShenzhen Hifibercom Technology Co.,Ltd 10G Bidi 20km Optical Modulehifibercom comNessuna valutazione finora

- D O S O: Ifferential Utput Ilicon ScillatorDocumento8 pagineD O S O: Ifferential Utput Ilicon ScillatorkynixNessuna valutazione finora

- AXIOM75 50 25 1B - Rev.6 10.000MHzDocumento4 pagineAXIOM75 50 25 1B - Rev.6 10.000MHzTürkay PektürkNessuna valutazione finora

- ASDMBDocumento5 pagineASDMBTcppunkNessuna valutazione finora

- Cfps 72 73Documento2 pagineCfps 72 73Istvan KovasznaiNessuna valutazione finora

- HYG050N10NS1MFDocumento10 pagineHYG050N10NS1MFequimarNessuna valutazione finora

- KI 118F Specifiaction1Documento3 pagineKI 118F Specifiaction1tierranuevaNessuna valutazione finora

- Features Applications: 220 To 725 MHZ Ultra-Low Jitter Differential OscillatorDocumento12 pagineFeatures Applications: 220 To 725 MHZ Ultra-Low Jitter Differential OscillatorÇağrı GürleyükNessuna valutazione finora

- Datasheet TP TemperatureDocumento12 pagineDatasheet TP Temperaturebtheo91190Nessuna valutazione finora

- 1.25Gb/s SFP (Small Form Pluggable) Long Wavelength (1310nm) TransceiverDocumento8 pagine1.25Gb/s SFP (Small Form Pluggable) Long Wavelength (1310nm) TransceiverHuy DoanNessuna valutazione finora

- Product Features: Applications:: 3.2 MM X 5 MM Ceramic Package SMD TCXODocumento2 pagineProduct Features: Applications:: 3.2 MM X 5 MM Ceramic Package SMD TCXOandcamiloq3199Nessuna valutazione finora

- Samtec ASP 134488 01 DatasheetDocumento4 pagineSamtec ASP 134488 01 DatasheetamiteshtripathiNessuna valutazione finora

- Advanced MEMS Packaging 2017 (Class 1)Documento24 pagineAdvanced MEMS Packaging 2017 (Class 1)amiteshtripathiNessuna valutazione finora

- Paper 22Documento21 paginePaper 22amiteshtripathiNessuna valutazione finora

- Prohibited Properties in HyderbadDocumento33 pagineProhibited Properties in HyderbadamiteshtripathiNessuna valutazione finora

- (Ebook - Electronics) - Analog and Mixed Signal Vlsi CircuitDocumento418 pagine(Ebook - Electronics) - Analog and Mixed Signal Vlsi CircuitPuja GuptaNessuna valutazione finora

- Pipelined Multistep AdcDocumento40 paginePipelined Multistep AdcamiteshtripathiNessuna valutazione finora

- VLSI Interview QuestionDocumento17 pagineVLSI Interview QuestionamiteshtripathiNessuna valutazione finora

- Defence Research and Development Organisation PDFDocumento296 pagineDefence Research and Development Organisation PDFSourav MondalNessuna valutazione finora

- Crouse Hinds XPL Led BrochureDocumento12 pagineCrouse Hinds XPL Led BrochureBrayan Galaz BelmarNessuna valutazione finora

- Kinematics in One DimensionDocumento4 pagineKinematics in One DimensionAldrin VillanuevaNessuna valutazione finora

- Training Report On Self Contained Breathing ApparatusDocumento4 pagineTraining Report On Self Contained Breathing ApparatusHiren MahetaNessuna valutazione finora

- Extract From The Painted Door' by Sinclair RossDocumento2 pagineExtract From The Painted Door' by Sinclair RosssajifisaNessuna valutazione finora

- C.Abdul Hakeem College of Engineering and Technology, Melvisharam Department of Aeronautical Engineering Academic Year 2020-2021 (ODD)Documento1 paginaC.Abdul Hakeem College of Engineering and Technology, Melvisharam Department of Aeronautical Engineering Academic Year 2020-2021 (ODD)shabeerNessuna valutazione finora

- Esteem 1999 2000 1.3L 1.6LDocumento45 pagineEsteem 1999 2000 1.3L 1.6LArnold Hernández CarvajalNessuna valutazione finora

- Hydrodynamic Calculation Butterfly Valve (Double Disc)Documento31 pagineHydrodynamic Calculation Butterfly Valve (Double Disc)met-calcNessuna valutazione finora

- JRC JFE-680 Instruct ManualDocumento86 pagineJRC JFE-680 Instruct ManualMark Dominic FedericoNessuna valutazione finora

- JC Series Jaw Crusher PDFDocumento8 pagineJC Series Jaw Crusher PDFgarrybieber100% (1)

- TreesDocumento69 pagineTreesADITYA GEHLAWATNessuna valutazione finora

- TNM History Updated June2017Documento2 pagineTNM History Updated June2017Lucas AndreoNessuna valutazione finora

- Emw 2007 FP 02093Documento390 pagineEmw 2007 FP 02093boj87Nessuna valutazione finora

- Elements of Romanticism in The Poetry of W. B. Yeats: Romantic InfluencesDocumento8 pagineElements of Romanticism in The Poetry of W. B. Yeats: Romantic InfluencesSadman Shaid SaadNessuna valutazione finora

- Table Equivalent Schedule 40 Steel PipeDocumento1 paginaTable Equivalent Schedule 40 Steel PipeorisNessuna valutazione finora

- Shandong Baoshida Cable Co, LTD.: Technical ParameterDocumento3 pagineShandong Baoshida Cable Co, LTD.: Technical ParameterkmiqdNessuna valutazione finora

- 1762 Ob8 PDFDocumento16 pagine1762 Ob8 PDFRodríguez EdwardNessuna valutazione finora

- Design and Development of Automatic Pneumatic Jack in Four Wheeler Ijariie5374Documento5 pagineDesign and Development of Automatic Pneumatic Jack in Four Wheeler Ijariie5374Saravanan ViswakarmaNessuna valutazione finora

- Manual Wire Rope Winches Wall-Mounted Wire Rope Winch SW-W: Equipment and ProcessingDocumento1 paginaManual Wire Rope Winches Wall-Mounted Wire Rope Winch SW-W: Equipment and Processingdrg gocNessuna valutazione finora

- De Vault 1996Documento22 pagineDe Vault 1996Harumi OONessuna valutazione finora

- Cost Analysis - Giberson Art GlassDocumento3 pagineCost Analysis - Giberson Art GlassSessy Saly50% (2)

- Mahindra & MahindraDocumento13 pagineMahindra & MahindraAbhishek DharmadhikariNessuna valutazione finora

- EPCC Hydrocarbon Downstream L&T 09.01.2014Documento49 pagineEPCC Hydrocarbon Downstream L&T 09.01.2014shyaminannnaNessuna valutazione finora

- Rekomendasi AnimeDocumento11 pagineRekomendasi Animeosvaldo manurungNessuna valutazione finora

- Material Specification - 077154C-000-JSS-1700-009 - DDocumento13 pagineMaterial Specification - 077154C-000-JSS-1700-009 - DStructures ProductionNessuna valutazione finora

- Fyp-Hydraulic Brakes CompleteDocumento32 pagineFyp-Hydraulic Brakes CompleteRishabh JainNessuna valutazione finora

- The Passion For Cacti and Other Succulents: June 2017Documento140 pagineThe Passion For Cacti and Other Succulents: June 2017golf2010Nessuna valutazione finora

- 300 PSI CTS (MP-1115) Operation Manual Rev1.3Documento18 pagine300 PSI CTS (MP-1115) Operation Manual Rev1.3Juan Manuel VizosoNessuna valutazione finora

- Industrial Artificial Intelligence For Industry 4.0-Based Manufacturing SystemsDocumento5 pagineIndustrial Artificial Intelligence For Industry 4.0-Based Manufacturing SystemsMuhammad HaziqNessuna valutazione finora