Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Skema Advan s5m

Caricato da

Anto SeblinkTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Skema Advan s5m

Caricato da

Anto SeblinkCopyright:

Formati disponibili

5

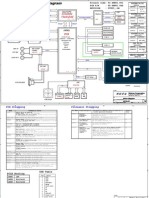

2G RF

O

SA100

2

W102

R135

0R

R136

1K

GND10

GND11

ANT

GND12

TRX_6

TRX_5

29

NC

R107

28

27

26

25

24

23

R108

NC

0R

R104

R109

0R

C102

NC

51R

C101

NC

15

16

17

18

19

20

21

22

VBATT

C117

C118

1.5nF

NC

W_PA_B5_EN

W_PA_B1_EN

GND9

VEN_HB

CPL_OUT

W_PA_OUT_B1/W_PA_OUT_B2

10

C126

NC

R120

51R

VRF18-1

P1

P1,3

P1,3

P1,3

P1,3

P1,3

VBAT

VBAT

W_PA_VCC

P1,3,4

P1,3

P9

P1,4

R133

SRCLKENA

CLK1_BB

CLK2_WCN

CLK4_Audio

CLK4_Audio

C140

K2

470nF

L2

E4

F4

G4

H4

VBAT_RF

VTCXO28-1

P1,3,4

SRCLKENA

P1,3,4

SRCLKENA

MT6166

DCXO_32K_EN

P1,3

P1,9

XMODE

P1,4

P1

VTCXO28-1

P1,4

P1,9

P1,3

P1,4

CLK4_Audio

CLK2_WCN

CLK1_BB

DCXO_32K

L117

P1

P1

3GH1_B1_TX L115

RFVCO_MON

3GTX_QN

TXVCO_MON

XTAL1

VTXLF

XTAL2

TXBPI

XO

VTCXO28

RCAL

Test pin

32K_EN

TST2

EN_BB

TST1

BSI

CLK_SEL

BSI_DATA2

26M output

XO3

GND7

GND8

GND9

GND10

BSI_DATA1

RX(I/Q)

0R

XMODE

VIO18

L118

P1

C7

J7

C8

J8

C9

GND38

GND37

GND36

GND35

GND34

GND40

GND39

A11

B10

C10

B11

D11

DET

VTXHF

2GLB_TX

B6

A8

B8

2GHB_TX

3GB8_RXP

3GB8_RXN

3GB5_RXN

A6

B5

3GB2_RXN

3GB5_RXP

B4

A3

A5

3GB2_RXP

3GB5_RXN

3GB1_RXP

3GB1_RXN

A2

B3

3GB5_RXP

3GB1_RXP

GGE_PA_LB_IN

GGE_PA_HB_IN

L1

VTCXO28-1

VBATT

TXBPI

P1,3

SRCLKENA

P1,3,4

SRCLKENA

P1,3,4

CLK1_BB

SYSCLK_WCN

P1

G1

DCXO_32K_EN

MT6166 QVL 26M

2.2uF

0R_0603_NC

P1

TXBPI

K1

MT6166

VRXHF

J4

C5

D5

E5

F5

D7

P1,3

R131

VPA_PMU

VBAT

BSI-A_EN

BSI-A_CK

BSI-A_DAT0

BSI-A_DAT1

BSI-A_DAT2

HOT1

J1

H2

NC

BSI-A_EN

BSI-A_CK

BSI-A_DAT0

BSI-A_DAT1

BSI-A_DAT2

GND1

P1

GND27

GND26

GND25

GND24

D10

C11

E10

V28

G10

G11

F10

F11

TX_BBIP

P3

TX_BBIN

P3

TX_BBQP

P3

TX_BBQN

P3

L11

VTCXO28-1

470nF

VRF18-1

J11

C138

H10

P1

470nF

TXBPI

J10

P1

C135

P1,3

RCAL

K11

R132

L10

G8

H8

BSI-A_DAT2

P1,3

BSI-A_DAT1

P1,3

2K

B7

J6

D8

E8

GND19

GND20

GND22

GND23

0R

C139

P1,3

P1,3

P1,3

P1,3

P1,3

F2

470nF

G2

HOT2

GND17

GND18

R128

P1

VIO18

VIO18_PMU

C136

GND2

P1,4

VTCXO28-1

P1

C6

D6

E6

F6

0R

GND_AUXADC

RX_IP

R130

P4

100K 1% NC

3GTX_IN

3GTX_QP

VRXLF

0R

0R

HB_RXN

VXODIG

VRF18-1

X100

R127

TX(I/Q)

L8

R126 P1

F1

3GTX_IP

HB_RXP

L7

VRF18_PMU

DCXO_32K

R129

P1

C128

NC

D9

E9

F9

G9

H9

J9

VIO18_VGPIO

VTCXO_PMU

AUXADC_TSX

HB_RX_N

LB_RXN

AVDD_VIO18

R125

C137

1uF

P4

P1

E1

V28

K7

AUXADC_REF

P1,3

HB_RX_P

TMEAS

TDD RX

K6

WG_GGE_PA_VRAMP

DCXO_32K

LB_RX_N

P1

TXO

XMODE

WG_GGE_PA_VRAMP

P1,4

TRXB5

C125 33pF

GND33

GND32

GND31

GND30

GND29

GND28

DETGND

LB_RXP

OUT32K

P4

P1,3

P1

PDET

B40_RXN

L5

connect to main GND

D1

K5

P1,3

C1

LB_RX_P

XO1

P1

FDD RX

XO2

B1

P1,3

P1,3

WG_GGE_PA_ENABLE

VRF18-1

B40_RXP

XO4

A1

L4

1(VIO18) 1(VIO18)

1(VTXCO28) 1(VTXCO28) 1(VTXCO28)

GND1

GND2

GND3

GND4

GND5

GND6

3GB1_RXN

E3

D3

C3

J2

C2

F3

G3

H3

J3

C4

D4

K3

0(GND)

DCXO + 32K-Less

U105

XMODE VXODIG

K4

DCXO + 32K XO

DCXO_

32K_EN

GND45

GND44

GND43

GND42

GND41

Logic

WG_GGE_PA_ENABLE

ANT

C134 470nF

BSI_DATA0

P1

L114

7.5nH

BSI_CLK

HB_RX_N

R124

35R

NC

BSI_EN

P1

F8

6.2nH

P1

HB_RX_P

E7

J5

L116

LB_RX_N

P1

H6

PDET

G6

26R

W_PA_B1_IN

6.2nH

TX

W_PA_OUT_B5

R122

W_PA_B5_IN

L113

RXA

C129 1.5nH

26R

2nH

NC

3GL5_TX

NC

RX_QN

NC

A9

C131

A10

C145

3GH2_TX

C130

MODE

P1,3

RXB

P1

7

6

1

3

HBout

12nH

P1

C127

0.5pF

5.6nH

CPL_IN

VMODE

1nH

11

RFOUT_HB

NC

U103

SAYFH836MCA0F00

L107

VM0

RFIN_HB

1.5nH

L106

C123

L104

VM1

WCDMA_Band5_Rx

GND1

C122

NC

GND2

C121

NC

12

GND4

VCC

RX_QP

LBout

HBout

L111

P1

SKY77758

13

GND13

U102

GND3

VBATT

GND5

0R

RFIN_LB

K9

LBout

GND2

4.3pF/3.9pF

R119

NC P3

R123

GND1

HBin

RFOUT_LB

K10

LBin

LB_RX_P

VEN_LB

R121

1.5pF

ASM_VCTRL_A

ASM_VCTRL_B

P1

C112

NC

P1

0R

C124 18pF

W_PA_B1_IN

C115

W_PA_OUT_B5

3GH1_TX

C133

ASM_VCTRL_A

ASM_VCTRL_B

TRXB1/TRXB2

0R/6.8pF

3.6nH

14

33nH

R117

NC

R118

L109

39nH

10

3

3nH

GND3

2

NC

GND4

2.2nH

C132

P1,3

P1,3

C109

C120 56pF

W_PA_B5_IN

P3

12nH

RX_IN

P1

L112

ANT

W_PA_OUT_B1/W_PA_OUT_B2

L103

P3

R116

P1

C114

NC

NC

C116

1uF

U104

Balun / RFBLN2012090BM5T25

2G_HB

TX

L105

C119

220pF

L108

L110

RXA

L101

L100

C113

120pF

R115

24K

P3

2G_LB

U101

SAYRF1G95HN0F0A

VBAT_RF

10K

SKY77590 control logic table

Enable VctC VctB VctA

LB_GMSK_TX

H

L

L

H

HB_GMSK_TX

H

L

H

H

LB_EDGE_TX

H

H

L

H

HB_EDGE_TX

H

H

H

H

TRX1

L

H

L

L

TRX2

L

H

H

L

TRX3

L

H

L

H

TRX4

L

H

H

H

TRX5

L

L

H

L

TRX6

L

L

L

H

K8

R114

WG_GGE_PA_VRAMP

RXB

W_PA_VCC

GND11

GND12

GND13

GND14

GND15

GND16

P1,3

L102

2nH/12nH

C111

22pF

NC

EDGE TXM

WG_GGE_PA_ENABLE

C110

22pF

4.3.nH/2.7nH

1K

EXP

R113

P1,3

C108 4.3pF/3.9pF

ASM_VCTRL_C

15

P3

WCDMA_Band1_Rx/WCDMA_Band2_Rx

P1

1K

GND1

TRXB1/TRXB2

2G_LB

2G_HB

R112

GND2

C107

22pF

GND3

C106

100nF

10uF/6.3V

P1

GND4

C105

TRXB5

GND5

C104

22pF

C103

22pF

8

7

6

5

4

3

2

1

GND8

GND7

GND6

GND5

GND4

GND3

GND2

GND1

1K

TX_HB_IN

TX_LB_IN

BS2

BS1

VBATT

VCC

0R_NC

RF

C100

GND13

MODE

TxEN

VRAMP

TRX_1

TRX_2

TRX_3

TRX_4

ASM_VCTRL_B

U100

PA / SKY77590

GND9

9

10

11

12

13

14

SKY77590

P1,3

0R

NC

R106 0R

NC

R111

ANTENNA3*5

SA101

2

I

S100

R105

ASM_VCTRL_A

ANTENNA3*5 ANTENNA3*5

SWDMM8430

GGE_PA_LB_IN

P1,3

ANTENNA3*5

R110

W105

ANTENNA3*5 ANTENNA3*5

R101

SD100

R103 0R

NC

1

R102

GGE_PA_HB_IN

W104

W101

W103

R134

0R_NC

W100

RF CARKIT III

BSI-A_DAT0

P1,3

BSI-A_CK

P1,3

BSI-A_EN

P1,3

RX_BBQN

P3

RX_BBQP

P3

RX_BBIN

P3

RX_BBIP

P3

0R

C141

VXODIG

P1

1uF

VTCXO28-1

VRF18-1

C142

P1

470nF

Title

VXODIG

<Title>

Reserved LC filter

Size

D

Document Number

<Doc>

Date:

5

Tuesday, April 22, 2014

1

Rev

<RevCode>

Sheet

of

10

T13

T16

T17

T18

T21

M11

U11

U12

V11

V12

V13

DVDD12_EMI

1.2V IO for DDR2

AE5

V7

U7

W7

Y7

AB6

AB8

AC3

AC5

AC7

AD4

AE3

W20

U20

V20

V21

U21

W21

Y20

Y21

AA21

AB21

U17

U18

A2

R24

AE21

VIO18_PMU

AE19

AE22

AE18

A3

VTCXO_PMU

VIO18_PMU

AC21

AD22

AG26

V17

V18

AA18

AB19

VIO18_PMU

C232

100nF

100nF

C233

AF3

AG1

DVDD12_EMI1

DVDD12_EMI2

DVDD12_EMI3

DVDD12_EMI4

DVDD12_EMI5

DVDD12_EMI6

DVDD12_EMI7

DVDD12_EMI8

DVDD12_EMI9

DVDD12_EMI10

DVDD12_EMI11

DVDD12_EMI12

DVDD12_EMI13

DVDD12_EMI14

DVDD12_EMI15

DVDD12_EMI16

DVDD28_MSDC1

DVDD28_MSDC2

DVDD28_BPI

DVDD18_IO1_1

DVDD18_MSDC0

DVDD18_IO0

DVDD18_IO1

DVDD18_IO2

DVDD18_IO3

DVDD18_IO4

VCCK1

VCCK2

VCCK3

VCCK4

VCCK5

VCCK6

VCCK7

VCCK8

VCCK9

VCCK10

VCCK11

VCCK12

VCCK13

VCCK14

VCCK15

VCCK16

VCCK17

VCCK18

VCCK19

AVSS18_WBG1

AVSS18_WBG2

AVSS18_WBG3

AVSS18_WBG4

AVSS18_WBG5

AVSS18_WBG6

AVSS18_WBG7

AVSS18_WBG8

AVSS18_WBG9

AVSS18_WBG10

AVSS18_WBG11

AVSS18_WBG12

AVSS18_MD1

AVSS18_MD2

AVSS18_MD3

AVSS18_MD4

AVSS18_MD5

AVSS18_MD6

AVSS18_MD7

AVSS18_MD8

AVSS18_MD9

AVSS18_MD10

AVSS18_AP1

AVSS18_AP2

VCCK_VPROC1

VCCK_VPROC2

VCCK_VPROC3

VCCK_VPROC4

VCCK_VPROC5

VCCK_VPROC6

VCCK_VPROC7

VCCK_VPROC8

VCCK_VPROC9

VCCK_VPROC10

VCCK_VPROC11

VCCK_VPROC12

VCCK_VPROC13

VCCK_VPROC14

VCCK_VPROC15

VCCK_VPROC16

VCCK_VPROC17

VCCK_VPROC18

VCCK_VPROC19

VCCK_VPROC20

DVSS73

DVSS74

DVSS75

DVSS76

DVSS77

DVSS78

DVSS79

DVSS80

DVSS81

DVSS82

DVSS83

DVSS84

AVSS18_MEMPLL

AVSS33_USB

AVDD18_MD

DVDD18_MIPITX

AVDD18_AP

DVDD18_MIPIIO

AVDD28_DAC

DVDD18_PLLGP

AVDD18_MEMPLL

AVSS18_MD11

AVSS18_MD12

AVSS18_MD13

AVSS18_AP3

AVSS18_AP4

AVSS18_AP5

AVSS18_AP6

AVSS18_WBG13

AVSS18_WBG14

AVDD33_USB

AVDD18_USB

DVSS18_MIPIIO1

DVSS18_MIPIIO2

DVSS18_MIPIIO3

DVSS18_MIPIIO4

DVSS18_MIPITX1

DVSS18_MIPITX2

DVSS18_MIPITX3

DVSS18_MIPITX4

H18

H16

H15

G9

G11

G13

G15

G16

G18

H8

E7

F7

F8

G8

H11

H13

VM_PMU

C200

C201

C202

C203

C204

100nF

100nF

100nF

100nF

4.7uF

Bottom cap/1st cap group

check MSDC1/2

IO power

check MSDC1/2

C115 close to pin E1 (150mil)

IO power

C125 close to pin G26 (150mil)

E1

V1

AD26

U25

G26

L26

Y26

D1

W1

AG13

R10

P9

L11

L12

L13

L14

L15

L16

L17

M10

M18

N10

N18

P18

R9

R18

T10

U10

V10

N12

N13

N14

N15

N16

N17

P14

R15

P15

R14

R13

R12

R16

R17

T14

T15

U15

U16

V15

V16

VMC_PMU

VIO18_PMU

VIO18_PMU

VIO18_PMU

C205

C206

C207

C208

C209

C210

C211

C212

100nF

1uF

100nF

100nF

100nF

100nF

100nF

100nF

C213

C214

C215

C216

C217

C218

C219

100nF

100nF

100nF

1uF

1uF

10uF

10uF

VCCK

Bottom cap

1st cap group

VCCK_VPROC

VPROC_PMU

C220

C221

C222

C223

C224

C225

C226

C227

100nF

100nF

100nF

1uF

1uF

10uF

10uF

10uF

Bottom cap

1st cap group

ST200 SHOT

GND_VPROC_FB

ST201 SHOT

VPROC_FB

P4

P4

To MT6323 GND_VPROC_FB pin

To MT6323 VPROC_FB pin

(1)VPROC_BB, GND pin of 1st cap group should be laid differential

pair with ground shielding remote sense to PMIC

M15

N21

P10

P11

P12

P13

P16

P17

L18

M14

M13

M12

(2)R107 & R103 must be close to 1st cap group.

If you want to remove them,

please make sure the VPROC_FB/GND_VPROC_FB must connect from 1st cap. group of VPROC

B

L2

VIO18_PMU

G1

T24

P26

VUSB_PMU

VIO18_PMU

H4

H5

J5

J7

L4

M7

M8

N3

C234

C235

100nF

1uF

C228

C229

100nF

100nF

DVSS63

DVSS64

DVSS65

DVSS66

DVSS67

DVSS68

DVSS69

DVSS70

DVSS71

DVSS72

100nF

DVSS1

DVSS2

DVSS3

DVSS4

DVSS5

DVSS6

DVSS7

DVSS8

DVSS9

DVSS10

DVSS11

DVSS12

DVSS13

DVSS14

DVSS15

DVSS16

DVSS17

DVSS18

DVSS19

DVSS20

DVSS21

DVSS22

DVSS23

DVSS24

DVSS25

DVSS26

DVSS27

DVSS28

DVSS29

DVSS30

DVSS31

DVSS32

DVSS33

DVSS34

DVSS35

DVSS36

DVSS37

DVSS38

DVSS39

DVSS40

DVSS41

DVSS42

DVSS43

DVSS44

DVSS45

DVSS46

DVSS47

DVSS48

DVSS49

DVSS50

DVSS51

ST202

SHOT

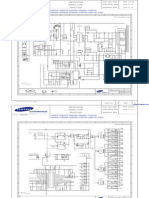

MT6582_LPDDR2

T12

M16

K21

M17

H12

J21

H20

H17

H14

V14

C231

C230

100nF

DVSS52

DVSS53

DVSS54

DVSS55

DVSS56

DVSS57

DVSS58

DVSS59

DVSS60

DVSS61

DVSS62

U300B

T11

R11

R2

G6

G7

G14

G17

G20

H10

M20

N11

A19

A26

B4

B10

E21

F6

B12

B14

B17

B22

B24

C4

C8

C11

C12

C16

C17

C18

C20

C21

C22

C23

C25

D4

D5

D7

D9

D11

D13

D15

D17

D21

D24

E5

E8

E10

E18

F18

P21

L10

AVDD18_MEMPLL pin and AVSS18_MEMPLL pin should

be connected with PCB CAP first, and then connected

with PMU and PCB ground. CAP should be near MT6582

as possible as we can.

A

Title

<Title>

Size

C

Date:

5

Document Number

<Doc>

Rev

<RevCode>

Sheet

Sunday, February 09, 2014

1

of

10

U300A

P1

P1

P1

P1

AF22

AF21

AG20

AF20

TX_BBIP

TX_BBIN

TX_BBQP

TX_BBQN

AG25

AG24

AG22

AG23

RX_BBIP

RX_BBIN

RX_BBQP

RX_BBQN

UL_I_P

UL_I_N

UL_Q_P

UL_Q_N

DVDD28_BPI

P1

P1

P1

P1

DL_I_P

DL_I_N

DL_Q_P

DL_Q_N

P1

AF25

AE24

WG_GGE_PA_VRAMP

P1

AE14

TXBPI

DVDD18_IO4

VBIAS

APC

TXBPI

BPI_BUS0

BPI_BUS1

BPI_BUS2

BPI_BUS3

BPI_BUS4

BPI_BUS5

BPI_BUS6

BPI_BUS7

BPI_BUS8

BPI_BUS9

BPI_BUS10

BPI_BUS11

BPI_BUS12

BPI_BUS13

BPI_BUS14

BPI_BUS15

VM0

VM1

BSI_EN

BSI_CLK

BSI_DATA0

BSI_DATA1

BSI_DATA2

AB24

AB23

AD25

AC24

AC23

AE25

AD24

AF16

AA17

AD16

AC16

AF15

AC17

AB17

AC15

Y15

ASM_VCTRL_A

P1

ASM_VCTRL_B

P1

ASM_VCTRL_C

P1

WG_GGE_PA_ENABLE

P1

U300D

AG14

AF14

VM0

VM1

W_PA_B1_EN

P1

W_PA_B5_EN

P1

P5

ED[0..31]

ED31

ED30

ED29

ED28

ED27

ED26

ED25

ED24

ED23

ED22

ED21

ED20

ED19

ED18

ED17

ED16

ED15

ED14

ED13

ED12

ED11

ED10

ED9

ED8

ED7

ED6

ED5

ED4

ED3

ED2

ED1

ED0

P1

P1

AD14

Y14

AB14

AA14

AC14

BSI-A_EN

BSI-A_CK

BSI-A_DAT0

BSI-A_DAT1

BSI-A_DAT2

P1

P1

P1

P1

P1

DVDD12_EMI

R300

C300

100nF

8K

P3,5

MT6582_LPDDR2

Pin

DVDD18_EFUSE

Voltage

FSOURCE_P

SCL0

SDA0

SCL1

SDA1

SCL2

SDA2

EVREF

EVREF

R301

P3,7

P3,7

P3,7

P3,7

P3,7

P3,7

C301

C302

100nF

1uF

8K

C26

C24

A25

B25

B26

B23

A23

D25

A11

A14

A13

D12

A10

B13

C10

B11

D22

B20

D20

A22

C19

B19

A20

B21

B16

A17

B18

A16

B15

C15

D14

C14

LPDDR2 ballmap

Description

VGP2 (2V0)

w/i EFUSE program

GND

w/o EFUSE program

P3,5

EINT11_G

EVREF

F16

EINT14_CTP_RST

EINT16_SUB_CMRST

P7

P4

RTC32K_CK

R306

R304

0R

NC

P4

L25

RTC32K_CK

TESTMODE AF11

R5

FSOURCE_P

R4

N26

WATCHDOG_B

AF12

AE12

AG11

AF13

R307

5.1K

Close to MT6582

P3,8

P3,8

USB_VRT

P25

USB_DP

USB_DM

R26

R25

90 Ohm

differential

P4

P4

N23

N24

CHD_DP

CHD_DM

V5

U5

W5

TESTMODE

FSOURCE_P

DVDD18_EFUSE

WATCHDOG

JTDI

AUD_CLK_MOSI

AUD_DAT_MISO

AUD_DAT_MOSI

JTMS

USB_VRT

GPIO12

GPIO13

USB_DP

USB_DM

SIM1_SCLK

SIM1_SIO

SIM1_SRST

SIM2_SCLK

SIM2_SIO

SIM2_SRST

CHD_DP

CHD_DM

EINT0

EINT1

EINT2

EINT3

EINT4

EINT5

DVDD18_IO1 EINT6

EINT7

EINT8

EINT9

EINT10

DVDD18_IO3

I2S_BCK

I2S_LRCK

I2S_DATA_IN

PCM_CLK

PCM_RX

PCM_SYNC

PCM_TX

AUX_IN0

AUX_IN1

DVDD28_MSDC2 DVDD28_MSDC1

4.7K

P5

P5

P5

P5

E15

E17

E12

F20

EDQS0_B

EDQS1_B

EDQS2_B

EDQS3_B

F9

E9

EDCLK_B

EDCLK

P5

P5

P5

P5

P5

P5

EA[0..9]

RA0

RA1

RA2

RA3

RA4

RA5

RA6

RA7

RA8

RA9

VREF

B8

B9

D8

A8

A7

C7

A5

D6

C6

A4

P5

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

1K

R316

R317

1K

1K

TP_MEMPLL

REXTDN

B3

REXTDN

KCOL1

KCOL2

NC

P8

P8

MT6605 OSC_EN (SRCLKENAI) need to default low

for MT6605 TESTMODE boot-strap

M25

SYSRST_B

P4

M24

N25

SRCLKENA

J23

H23

J24

H22

H24

K26

K25

J25

AUD_CLK

AUD_MISO

AUD_MOSI

AG10

AF9

P4

P4

P4

P4

U300E

P4

P4

P4

GPIO12_FLASH_EN

GPIO13_FLASH_SEL

L21

K23

L23

L20

L24

K24

SIM1_SCLK

SIM1_SIO

SIM1_SRST

SIM2_SCLK

SIM2_SIO

SIM2_SRST

W22

V22

AA24

V24

W25

Y25

AA23

AA26

AA25

Y23

Y22

EINT1_A

EINT2_CTP

NC

P1,4

PMIC_SPI_CS

PMIC_SPI_SCK

PMIC_SPI_MISO

PMIC_SPI_MOSI

EINT_PMIC

P4

P7

P7

P4

P4

P4

P4

P4

P4

For earpohne & MSDC hotplug EINT,

plase choose EINT0~15

with HW de-bounce function.

P7

P7

EINT4_HP

EINT6_M

P6

P7

P7

P7

P7

P7

P7

MIPI_TCP

MIPI_TCN

MIPI_TDP0

MIPI_TDN0

MIPI_TDP1

MIPI_TDN1

P7

P7

P7

P7

P7

P7

MIPI_RCP

MIPI_RCN

MIPI_RDP0

MIPI_RDN0

MIPI_RDP1

MIPI_RDN1

P7

P7

P7

P7

P7

P7

MIPI_RCP_A

MIPI_RCN_A

MIPI_RDP0_A

MIPI_RDN0_A

MIPI_RDP1_A

MIPI_RDN1_A

M3

M4

M1

M2

P2

N2

P1

R1

N5

M5

K6

K5

L3

K3

K1

K2

J1

J2

G2

H2

P7

EINT9_MAINCAM_RST

EINT10_CMPDN

P7

P7

V23

V26

V25

U24

F5

G5

G4

G3

J3

H3

N1

TCP

TCN

TDP0

TDN0

TDP1

TDN1

TDP2

TDN2

TDP3

TDN3

LCM_RST

DSI_TE

DISP_PWM

RCP

RCN

RDP0

RDN0

RDP1

RDN1

RDP2

RDN2

RDP3

RDN3

CMMCLK

CMPCLK

CMDAT0

CMDAT1

U3

Y3

AD9

B2

B1

LRSTB

LPTE

PWM

P7

P7

P7

CMMCLK

P7

E2

F2

RCP_A

RCN_A

RDP0_A

RDN0_A

RDP1_A

RDN1_A

VRT

MSDC0_DAT7

MSDC0_DAT6

MSDC0_DAT5

MSDC0_DAT4

MSDC0_DAT3

MSDC0_DAT2

MSDC0_DAT1

MSDC0_DAT0

MSDC0_CLK

MSDC0_CMD

MSDC0_RSTB

MT6582_LPDDR2

1.5K

Close to MT6582

eMMC_RST

eMMC_CMD

eMMC_CLK

eMMC_DAT0

eMMC_DAT1

eMMC_DAT2

eMMC_DAT3

eMMC_DAT4

eMMC_DAT5

eMMC_DAT6

eMMC_DAT7

ST300

4.7K

C213 Close to MT6582

AF19 should connect to C213.2 first,

than connect to GND by via

SCL1

SDA1

EDQS0

EDQS1

EDQS2

EDQS3

DVDD18_MSDC0

SHOT

P3,7

P3,7

F15

F17

F12

E20

P6

F22

E23

F24

G24

E26

E25

G23

G22

D26

E24

G25

MT6582_LPDDR2

1uF

R311 R312

P5

P5

P5

P5

R310

REFP

AVSS_REFN

C306

VIO18_PMU

RCLK0_B

RCLK0

P5

P5

P5

R302

EINT20_AUPA_EN

KCOL0

P8

MIPI_VRT

AUX_XP

AUX_XM

AUX_YP

AUX_YM

MSDC1_DAT3

MSDC1_DAT2

MSDC1_DAT1

MSDC1_DAT0

MSDC1_CLK

MSDC1_CMD

AG19

AF19

REFP

RDQS0_B

RDQS1_B

RDQS2_B

RDQS3_B

ECKE

EDQM0

EDQM1

EDQM2

EDQM3

Y13

AA13

SRCLKENAI

SRCLKENA

PWRAP_SPI0_CSN

PWRAP_SPI0_CK

PWRAP_SPI0_MI

PWRAP_SPI0_MO

PWRAP_INT

JTCK

JTDO

D3

C2

D2

E4

C3

E3

AF18

AG17

AF17

AG16

4.7K

SCL2

SDA2

RDQS0

RDQS1

RDQS2

RDQS3

ECS0_B

ECS1_B

D16

D18

D10

D23

C303

T2

T1

T5

T6

R7

T3

4.7K

P3,7

P3,7

RDQM0

RDQM1

RDQM2

RDQM3

B7

B6

B5

P7

RTC32K_CK

MSDC2_DAT3

MSDC2_DAT2

MSDC2_DAT1

MSDC2_DAT0

MSDC2_CLK

MSDC2_CMD

R308 R309

AD13

AE13

SYSRSTB

VIO18_PMU

AC19

AD19

R315

KPCOL2

KPROW2

AB13

AC13

KPCOL0

KPROW0

DVDD18_IO1

KPCOL1

KPROW1

AF8

AG8

AE10

AC11

AD10

AE9

AC10

AC8

AC9

AB9

AD7

AF10

EINT14

EINT15

EINT16

EINT17

EINT18

EINT19

EINT20

EINT11

SCL0

SDA0

SCL1

SDA1

SCL2

SDA2

T23

R23

AA3

AB3

AD8

AE7

AA1

AA2

P23

P22

CLK26M

DVDD18_IO3

VGP2

UTXD3

URXD3

UTXD2

URXD2

AF26

CLK1_BB

SPI_CS

SPI_MO

SPI_MI

SPI_CK

P1

UTXD0

URXD0

U300C

U2

V2

Y2

W2

TP300URXD1

TP301UTXD1

TP302URXD0

TP303UTXD0

UTXD1

URXD1

URXD1

UTXD1

URXD0

UTXD0

RCKE

P7

EINT18_SUB_CMPDN

Please reserve UART0/1 test point

UART0 for AP log

UART1 for MD log

RCS0_B

RCS1_B

P7

A1

EFUSE Notice

RDQ31

RDQ30

RDQ29

RDQ28

RDQ27

RDQ26

RDQ25

RDQ24

RDQ23

RDQ22

RDQ21

RDQ20

RDQ19

RDQ18

RDQ17

RDQ16

RDQ15

RDQ14

RDQ13

RDQ12

RDQ11

RDQ10

RDQ9

RDQ8

RDQ7

RDQ6

RDQ5

RDQ4

RDQ3

RDQ2

RDQ1

RDQ0

P5

P5

P5

P5

P5

P5

P5

P5

P5

P5

P5

VIO18_PMU

MC1CMD

MC1CK

MC1DAT0

MC1DAT1

MC1DAT2

MC1DAT3

R313 R314

4.7K

P3,7

P3,7

P8

P8

P8

P8

P8

P8

4.7K

SCL0

SDA0

TP304

P4,8

PWRKEY

P3,8

USB_DM

P3,8

USB_DP

PWRKEY GND

DM

VCHG

DP

VBAT

TP305

KCOL0

6

5

4

VCHG

VBAT

KCOL0

P8

test6pin

MK300

MK301

MK302

MK303

T POINT S T POINT S T POINT S T POINT S

Title

<Title>

Size

D

Document Number

<Doc>

Date:

Tuesday, April 22, 2014

Rev

<RevCode>

Sheet

of

10

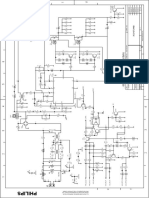

Before you select BJT , please take power dissipation into consideration.

Refer to MT6323 design notice

Charger

1. Close to Battery Connector.

VCHG

(Rsense (R328) <10mm)

2. Main path should be 40mil.

(VBUS -> U303's E, -> U303's C -> R328 -> VBAT)

3. Star connection from R328 to BAT Connector

330K(1%)

R400

330K 1%

VCDT

if you use digital MIC,

please change cap (C312)

to 1.0uF

P4

VCDT rating: 1.268V

cap rating depends on

Phone OVP spec.

C400

R401

39K 1%

U400

39K(1%)

1uF

VBAT

40mils

P1

C401

L2

3.3K

ST400 SHOT

R402

3.3K

CHR_LDO

2.2uF

12MIL

P4

F2

G2

MICBIAS1

100nF

2

Q401

PT723

VDRV

VA_PMU

C403

ST401 SHOT

ISENSE

Differential

ST403 SHOT

Rsense

BATSNS

SHOT

P6

P1

AUXADC_REF

AUXADC_REF

AU_HPL

AU_HPR

AU_MICBIAS0

AU_MICBIAS1

P6

P6

AU_VIN2_P

AU_VIN2_N

D2

D1

16.9K 1%

16.9K(1%)

80mils from battery connector to MT6323 chip

ACCDET

E2

CLK4_Audio

E1

R405

1K

30K(1%)

BAT_ON

ISINK0

ISINK1

ISINK2

ISINK3

DRIVER

AU_VIN1_P

AU_VIN1_N

P4

P4

P4

P4

P4

BATSNS

ISENSE

BAT_ON

VCDT

VDRV

P4

CHR_LDO

BATSNS P13

P12

ISENSE

K3

BAT_ON

A12

VCDT

M13

VDRV

CHR_LDON13

TVS0402_NC

TVS0402_NC

PWRKEY

WATCHDOG_B

SYSRST_B

R407

Close to PMIC

1K

P3

EINT_PMIC

P3

P3

P3

AUD_MOSI

AUD_CLK

AUD_MISO

P1,3

SRCLKENA

K

K0

01

31

==

55

33

33

RR

,,

KK

99

.

.

1

6

e

16c

==i

t

44o

33n

33

RRn

g

i

,,s

mme

hhd

oo

kkW

07H

14

3

s

i2

is

CC3

6

TTT

NNM

y

rt

ry

o

e

e

t

t

r

t

t

e

a

a

f

bbe

fR

fi

i

P3

P3

P3

P3

VBAT

Add Zenar Diode

Place on the path

from VBAT to IC

(Battery connector

or test point or IO

connector)

80mil

PMIC_SPI_SCK

PMIC_SPI_CS

PMIC_SPI_MOSI

PMIC_SPI_MISO

M2

A1

K4

A9

A7

N12

4mil (VPA no use)

A2

M1

D9

B7

D8

B8

H13

P8

P6

P5

P2

15mil

10uF

E7

E8

B6

F13

F14

G13

A13

30mil

20mil

20mil

20mil

C410

500mW

BUCK OUTPUT

VPROC1

VPROC2

VPROC3

CLK26M

VPROC_FB

GND_VPROC_FB

BATSNS

ISENSE

BATON

VCDT

VDRV

VPA1

VPA2

VPA_FB

C411

D400

10uF

J14

M14

20mil

VSYS_PMU

A8

DVDD18_DIG_PMIC

VF : 4.85V~5.36V

A5

VIO18_PMU

Between IC and IO port

P1,4

P1

C2

B1

B2

AUXADC_REF

AUXADC_REF

AUXADC_TSX

P1

Based on your system level design , if

better EOS performance is needed on your

system, please refer to EOS performance

enhance proposal

Based on your system level design , if

lower LX voltage swing is needed on

your system, please refer to Buck LX

voltage swing enhance proposal

E9

C9

E10

C10

iSINK0

iSINK1

iSINK2

iSINK3

P7

P7

P7

P8

C14

D14 VPROC_SW

E14

L400

680nH

VPROC_PMU

B12

C12

A14

B14

VPROC_FB

P2

GND_VPROC_FB

VPA_SW

L401

C404 1nF_NC

2.2uH

P2

VPA_PMU

C405

D12

2.2uF

0.68uH

PWRKEY

SYSRSTB

RESETB

FSOURCE

INT

EXT_PMIC_EN

ALDO OUTPUT

H14 VSYS_SW

L402

GND_AUXADC

C414

C415

100nF

100nF

P3

P3

VA

VCN28

VTCXO

PMU_TESTMODE

VCAMA

VCN33

AVDD33_RTC

AUD_MOSI

AUD_CLK

AUD_MISO

SRCLKEN

FCHR_ENB

M3

VA_PMU

680nH

N3

L4

VCN_2V8_PMU

VTCXO_PMU

P3

M6

C3

VCAMA_PMU

VCN_3V3_PMU

VRTC

VSYS_PMU

VA_PMU

C407 1uF

VEMC_3V3_PMU

C408

C409 1uF

100nF

DLDO OUTPUT

VM

VRF18

VIO18

VIO28

VCN18

VCAMD

VCAM_IO

SPI_CLK

SPI_CSN

SPI_MOSI

SPI_MISO

VBAT INPUT

VBAT_VPROC1

VBAT_VPROC2

VBAT_VPROC3

VBAT_VPA

VEMC_3V3

VMC

VMCH

VUSB

VSIM1

VSIM2

VGP1

VBAT_VSYS

VBAT_LDOS31

VBAT_LDOS32

VBAT_LDOS2

VBAT_LDOS1

VIBR

VGP2

VGP3

VCAM_AF

AVDD22_BUCK1

AVDD22_BUCK2

J13

H11

L12

M4

J12

K14

L13

VM_PMU

VRF18_PMU

VIO18_PMU

VIO28_PMU

VCN_1V8_PMU

VCAMD_PMU

VCAMD_IO_PMU

P7

L6

P4

N6

P9

N9

L8

VEMC_3V3_PMU

VMC_PMU

VMCH_PMU

VUSB_PMU

VSIM1_PMU

VSIM2_PMU

M7

N8

L14

N7

VGP2

VIBR_PMU

VGP2

VCAM_AF

C412

C427

1uF

1uF

VCAM_AF

DVDD18_DIG

DVDD18_IO

B

AUXADC

AUXADC_VREF18

AUXADC_AUXIN_GPS

AVSS28_AUXADC

VREF

P14

VREF

dedicate VSS ball, must return to cap then to main GND:

1. GND_VREF(N14) => C320

C413

100nF

BC 1.1

CHD_DM

CHD_DP

A10

A11

CHG_DM

CHG_DP

GND_VREF

N14

12MIL

ST404

SHOT

12MIL

10uF

10uF

C418C419C420C421 C422 C423

10uF10uF

1uF

1uF

SIM LVS

ST405

SHOT

P3

P3

P3

P3

P3

P3

60MIL

ST406

ST407

SHOT

SHOT

SIM1_SCLK

SIM1_SIO

SIM1_SRST

SIM2_SCLK

SIM2_SIO

SIM2_SRST

P8

P8

P8

SCLK

SIO

SRST

P8

P8

P8

SCLK2

SIO2

SRST2

B5

M11

E6

C5

K11

D6

M9

N11

M10

K9

L11

K10

SIM1_AP_SCLK

SIMLS1_AP_SIO

SIM1_AP_SRST

SIM2_AP_SCLK

SIMLS2_AP_SIO

SIM2_AP_SRST

SIMLS1_SCLK

SIMLS1_SIO

SIMLS1_SRST

RTC32K_CK

P3

RTC 32K : X301+C324+C319=> mount, R333=> NC

32K-less: X301+C324=> remove, C319+R333=> 0R

RTC

32K_IN

32K_OUT

GND_LDO23

GND_LDO22

GND_LDO21

GND_LDO20

GND_LDO19

GND_LDO18

GND_LDO17

GND_LDO16

GND_LDO15

B10

G11

E13

E11

F11

F10

0R

K6

K8

F5

F6

F7

F8

F9

G5

G6

Close to chip

R408

0R

DCXO_32K

P1

Vibra

MT6323

VIBR_PMU

120MIL

D5

C4

A3

A4

C424

GND_ISINK

GND_VSYS

GND_VPA

GND_VPROC1

GND_VPROC2

GND_VPROC3

SIMLS2_SCLK

SIMLS2_SIO

SIMLS2_SRST

J10

J9

J8

J7

J6

H10

H9

H8

H7

H6

H5

G9

G8

G7

refer to system analog LDO

performance improve proposal

Refer to MT6323 design notice

for Buck GND layout rule

RTC_32K1V8

RTC_32K2V8

XIN

XOUT

RTC

GND_LDO1

GND_LDO2

GND_LDO3

GND_LDO4

GND_LDO5

GND_LDO6

GND_LDO7

GND_LDO8

GND_LDO9

GND_LDO10

GND_LDO11

GND_LDO12

GND_LDO13

GND_LDO14

C417

1uF_NC

C416

10uF_NC

Refer to MT6323 design

notice for Zener selection

P6

P6

CHRLDO

MMSZ5231BT1G

AU_HPL

AU_HPR

0.68uH

ACCDET

VSYS

P3,8

P3

P3

N2

Based on your system level design , if

better ESD performance is needed on

your system, please refer to ESD

performance enhance proposal

H4

J4

P6

P6

CONTROL SIGNAL

1uF

R334,R335 must to be close to

PMIC AUXADC_REF pin

30K 1%

BAT_ID

P6

P6

AU_HSP

AU_HSN

Please use inductor recommand by MTK

Refer to MT6323 design notice

C406

R406

TVS401 TVS400

TP400

AU_SPKP

AU_SPKN

AVDD28_ABB

AVDD28_AUXADC

GND_ABB

P4

CON400

K1

L1

H1

G1

AU_VIN2_P

AU_VIN2_N

CHARGER

VBAT

AU_VIN0_P AUDIO

AU_VIN0_N

ISENSE/BSTSNS 4mil

differential to Rsense

P1,4

R404

6

7

G3

G4

J2

D3

H2

4mil

BAT_CON

AU_HSP

AU_HSN

ST402

P4

0.2R_1%

HD1 VBAT

HD2

NTC

HD3

HD4 GND

E4

F4

AU_VIN1_P

AU_VIN1_N

1uF

12MIL

P4

40mils

BATTERY

CONNECTOR

4

5

AU_VIN0_P

AU_VIN0_N

P6

P6

P4

4mil

R403

P6

P6

C1

C2

40mils

40mils

GND_SPK

C402

C3

40mils

C4

MICBIAS0

Q400

Q / STT818B

SPK_P

SPK_N

VBAT_SPK

C425

VRTC

VIB400

Vibrator

1uF

C426

R409

100nF

1K

GB400

BATTERY

Title

==> for longer RTC time sustain after battery remove,

please refer to RTC design notice

<Title>

Size

D

Document Number

<Doc>

Date:

5

Monday, April 07, 2014

1

Rev

<RevCode>

Sheet

of

10

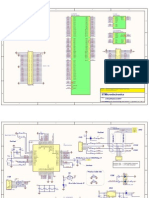

162 Ball, 0.5mm pitch

VDD1=1.8V

VDD2=1.20V

VDDCA=1.20V

VDDQ= 1.20V

eMMC MCP

VIO18_PMU

EA[0..9]

U501

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

P3

ED[0..31]

R504

R505

VIO18_PMU

P3

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

ED16

ED17

ED18

ED19

ED20

ED21

ED22

ED23

ED24

ED25

ED26

ED27

ED28

ED29

ED30

ED31

240R

240R

ZQ0

ZQ1

U3

T3

R3

R2

R1

K2

J2

J3

H3

H2

T8

R8

R7

R9

R6

P7

P8

P9

K9

K8

K7

J6

J9

J7

J8

H8

W7

U6

W8

T5

U7

W9

V8

T6

H6

F8

E9

G7

H5

E8

G6

E7

G3

F3

F6

F9

G10

H10

J5

K10

M5

P10

R5

T10

U10

V6

V9

T1

M1

H1

B9

E1

F2

F5

G1

L2

M8

U1

V2

V5

C3

A1

A2

A9

A10

B1

B10

E10

W1

W10

Y1

Y2

Y9

Y10

CA0

CA1

CA2

CA3

CA4

CA5

CA6

CA7

CA8

CA9

VDD11

VDD12

VDD13

VDD14

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

Power

VDDCA1

VDDCA2

VDDCA3

VCC1

VCC2

VCCQ

VDDI

eMMC

ZQ0

ZQ1

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSSQ11

VSSQ12

VSSQ13

CLKm

RST

CMD

DAT7

DAT6

DAT5

DAT4

DAT3

DAT2

DAT1

DAT0

CS0#

CS1#

CKE0

CKE1

CLK

CLK#

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

VSSCA1

VSSCA2

VSSCA3

VSSm1

VSSm2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSSQm

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

LP-DDR2

DM0

DM1

DM2

DM3

VREFCA

VREFDQ

NC1

NC2

NC3

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

DNU1

DNU2

DNU3

DNU4

DNU5

DNU6

DNU7

DNU8

DNU9

DNU10

DNU11

DNU12

DNU13

E6

F1

V1

W6

C509

C510

2.2uF

100nF

DVDD12_EMI

E5

G2

K1

M7

U2

W5

DVDD12_EMI

F7

F10

G5

H9

J10

L6

M6

N6

R10

T9

U5

V7

V10

C511

C512 C513

C514 C515 C516

VEMC_3V3_PMU

J1

L1

T2

A8

B2

B8

A5

VIO18_PMU

B5

C1

C5

C518

P3

P3

1uF

P3

eMMC_CLK

eMMC_RST

eMMC_CMD

B4

A4

A6

B6

A7

B7

B3

A3

eMMC_DAT7

eMMC_DAT6

eMMC_DAT5

eMMC_DAT4

eMMC_DAT3

eMMC_DAT2

eMMC_DAT1

eMMC_DAT0

P1

P2

ECKE

M3

L3

EVREF

C522

100nF

C502

C521

4.7uF

220nF

P3

EDQM0

EDQM1

EDQM2

EDQM3

K3

M9

C520

2.2uF

EDQS0

EDQS0_B

EDQS1

EDQS1_B

EDQS2

EDQS2_B

EDQS3

EDQS3_B

N5

L5

T7

H7

C519

100nF

P3

P3

EDCLK

EDCLK_B

P6

P5

K6

K5

U8

U9

G8

G9

C500

P3

P3

P3

P3

P3

P3

P3

P3

ECS0_B

ECS1_B

N1

N2

C2

C4

C6

D1

D2

D3

D4

D5

D6

E2

E3

M2

N3

P3

V3

W2

W3

C517

2.2uF 2.2uF 100nF 100nF 100nF 100nF 100nF

P3

P3

P3

P3

P3

P3

P3

P3

P3

P3

P3

P3

P3

P3

P3

C523

4.7uF 100nF

EMMC_DDR2_162BALL

B

Title

<Title>

Size

D

Document Number

<Doc>

Date:

5

Sunday, February 09, 2014

1

Rev

<RevCode>

Sheet

of

10

R600

1K

R601

1.5K

MICBIAS0

TVS0402

33pF

P4

C601

AU_VIN0_P

100nF

C602

C603

4.7uF

100pF

B600

BEAD

B601

BEAD

C600

TVS600

MIC+

P8MIC600

1

+

2

-

MIC-

P8

HEADSET MODE/DIGITAL MUSIC

R602

MIC

C604

AU_VIN0_N

100nF

P4

C606

TVS601

33pF

P4

33pF

1

R604

C605

C607

AU_HPL

10uF

R603

470R

XMP3_L

100R

TVS0402

Normally open AUDIO jack , need not pull down resistor .

C608

100pF

1.5K

P4

R606

C609

AU_HPR

10uF

R605

Normally short AUDIO jack , need pull down 10K resistor .

XMP3_R

100R

C610

R607

33pF

1K

470R

R608

R609

1.5K

MICBIAS0

1K

VIO18_PMU

TVS0402

R610

470K

J600

100nF

B603

C613

C614

4.7uF

100pF

BEAD

TVS602

XMICP

P3

MIC601

1

+

2

-

R611

EINT4_HP

XMP3_L

XMP3_R

100nF

B608

BEAD

BEAD

BEAD

B604

B606

B607

BEAD

BEAD

BEAD

2

5

6

4

3

1

TVS603

TVS604

TVS606

MIC

DET

NC

L

R

GND

C

PHONEJACK_3-5_6P

TVS605

TVS0402

TVS0402

TVS0402

1

C616

33pF

1

R612

C615

AU_VIN2_N

P4

B602

B605

MIC

C

47K

TVS0402

TVS607

C612

AU_VIN2_P

33pF

P4

C611

TVS608

TVS0402

1.5K

TVS0402

R613

P9

1K

FM_RX_N_6572

P9

FM_ANT

R614

0R

R615

0R

TVS0402

C617

B609

AU_HSP

RECEIVER

REC

TVS609

BEAD

2

1

REC601

1

2

C618

100pF

MICBIAS1

+

-

33pF

P4

R616

C619

REC600

+

-

REC602

33pF

1K

REC

B610

AU_HSN

1

2

BEAD

C622

P4

TVS610

+

-

P4

C620

AU_VIN1_N

100nF

C621

10uF

R617

C623

REC

33pF

100pF

1

1.5K

B

TVS0402

P4

C624

AU_VIN1_P

XMICP

100nF

C625

33pF

VBAT

U600

P4

VDD1

VOP

VDD2

VON

C628

P3

P4,6

AU_SPKP

P4,6

AU_SPKN

C631

22nF

R619

10K

C633

22nF

R620

10K

10uF_10V

12

17

18

7

C632

220pF

6

1

EINT20_AUPA_EN

R621

14

20

21

PVDD1

PVDD2

PVDD3

INP

CP

15

B611

BEAD

13

B612

BEAD

1

3

C629

AW8733A

4.7uF

CN

INN

NC1

NC2

NC3

NC4

NC5

FS

SHTDN

GND1

GND2

EXP

19

2

5

10

11

16

9

R618

ACCDET

1K

TVS0402

C630

33pF

P4,6

AU_SPKP

B613

C627

100nF 10uF

TVS611

0R_NC

SPK

SPK+

P8

SPK600

1

2

C634

100pF

+

SPK

P4,6

AU_SPKN

B614

0R_NC

SPKC635

10K

C626

P8

TVS612

33pF

A

TVS0402

Title

<Title>

Size

C

Date:

5

Document Number

<Doc>

Rev

<RevCode>

Sunday, February 09, 2014

Sheet

1

of

10

TP700

VIO18_PMUVIO28_PMU

VDD

TP701

LCM

R706

MIPI_TCP

0R

P3

P3

LRSTB

LPTE

VIO18_PMU

VIO28_PMU

SLED_A

SLED_K

11

12

13

14

15

16

17

18

VIO28_PMU

CLKP

GND4

GND5

RESET

TE

GND

RESET

SDA

SCL

INT

VDD

H1

H2

VIO18_PMU

P3

R705

EINT6_M

100K

C703

U703

TVS700 TVS701 TVS702 TVS703

C702

TOUCH_CON_ZIF

TVS704

1uF

IOVCC

VCI

GND6

LEDP

LEDN

TVS0402 TVS0402 TVS0402 TVS0402

TVS0402

9

10

1

2

3

4

5

6

7

8

EINT14_CTP_RST

P3

SDA0

P3

SCL0

P3

EINT2_CTP

3

ICMF062P900MFR

4

CON702

P3

D1P

GND3

CLKN

D0P

GND2

D1N

NC3

6

7

8

VDD

MIPI_TCN

3

4

5

OUT

0R

GND1

D0N

NC2

R701

0R

1

2

GND1

D0N

NC1

D0P

GND2

D1N

NC2

D1P

GND3

CLKN

NC3

CLKP

GND4

IM2/NC

BLU_PWM

GND5

RESET

TE

NC4

IOVCC

VCI

GND6

LEDP

LEDN

LCM-ID

HLD1

HLD2

GND

R704

2

U702

1

P3

MIPI_TDP0

0R

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

EXP

NC1

P3

7

1

R703

P3

MIPI_TDP1

RESET

GND

MIPI_TDN1

P3

ICMF062P900MFR

SDA

TP705

CON701

2

P3

0R

1uF

SCL

TP703

TP704

CON700

U701

1uF

0R

ICMF062P900MFR

R702

R700

U700

MIPI_TDN0

P3

INT

TP702

Capacitive Touch Panel

C701

C700

Based on your system level design , if

better LCD uniformity is needed on

your system , please refer to BL

uniformity with iSINK improve proposal

100nF

BU52011HFV

CON18PIN

ZIF25PIN

U704

4

3

MAIN CAM

1

2

ICMF062P900MFR

VCAMD_IO_PMU

VCAMD_PMU

VBAT

C

SLED_A

R709

0R

DIODE

2

D700

1

L700

U705

C723

C704

33pF

1uF_0603

SLED_K

SW

GND

FB

10uH

P3

MIPI_RDP0

P3

MIPI_RDN0

R707

0R

R708

CON703

1

2

3

4

5

6

7

8

9

10

11

12

0R

U706

VIN

OVP

SHDN

6

5

B700

R710

0R

BEAD

SLED_A

C705

P3

MIPI_RCP

P3

MIPI_RCN

4

3

1

2

ICMF062P900MFR

R711

0R

R713

0R

U707

4.7uF

R712

CP2120

PWM

P3

4.7R

R714

P3

MIPI_RDP1

P3

MIPI_RDN1

4

3

DOVDD1V8

DVDD1V5

DGND1

MIPI_RDP0

MIPI_RDN0

DGND2

MIPI_RCP0

MIPI_RCN0

DGND3

MIPI_RDP1

MIPI_RDN1

DGND4

AF_GND

AF2V8

AVDD2V8

AGND

PWDN

RESET

SIO_C

SIO_D

DGND6

PWDN_F

MCLK

DGND5

24

23

22

21

20

19

18

17

16

15

14

13

VCAM_AF

VCAMA_PMU

EINT10_CMPDN

P3

EINT9_MAINCAM_RST

SCL1

P3,7

SDA1

P3,7

EINT18_SUB_CMPDN

CMMCLK

P3,7

P3

P3,7

MAIN CAMERA

1

2

VCAM_AF

VCAMD_IO_PMU

VCAMA_PMU

VCAMD_PMU

ICMF062P900MFR

R715

0R

R716

0R

10K

VIO28_PMU

C706

EINT1_A

R717

R718

VIO28_PMU

5.1R ALS_A

4.7K

VIO18_PMU

VCAMD_IO_PMU

VCAMD_PMU

VIO28_PMU

CON704

1

2

3

4

5

6

SCL2

ALS_A

P3,7

EINT1_A

SDA2

VDD

SCL

GND

LEDA

INT

SDA

P3

P3

SUB CAM

CON705

R719

0R

R720

0R

MIPI_RDP0_A

MIPI_RDN0_A

U709

ALS

P3

MIPI_RCP_A

P3

MIPI_RCN_A

4

3

4

3

1

2

1

2

ICMF062P900MFR

R721

0R

R722

0R

U710

P3

MIPI_RDP1_A

P3

MIPI_RDN1_A

4

3

P3,7

2

P3

P3,7

P3,7

SDA1

P3,7

SCL1

EINT16_SUB_CMRST

EINT18_SUB_CMPDN

VCAMA_PMU

VCAM_AF

VIO28_PMU

U712

10uF

R727

3

R726

iSINK1

P3

P3

C719

1uF

3

4

GPIO13_FLASH_SEL

GPIO12_FLASH_EN

iSINK2

R730

P4

I2C Address: 0x1C (Write:0x38, Read:0x39)

R729

33pF_NC

10K

MMA8452Q

100nF

10K

C720

A

VIN

VOUT

C1

PGND

C2

SGND

FLASH

EN

FB

RSET

SGM3140

10

C717

10uF

1

2

8

LEDA

LED701

LEDK

FLASH_FPC

FLASH_LED

P4

C718

CON706

33pF_NC

5

10

12

13

15

16

6

R732

BYPASS

SA0

GND1

GND2

GND3

NC3

NC4

NC5

C715

C716

R731

NC2

SCL

SDA

iSINK0

P3

68K

2

7

VDD

EINT11_G

0.2R

SCL2

SDA2

8

4

6

11

9

3

EXP

P3,7

P3,7

0R

INT1

INT2

NC1

ZIF25PIN

11

14

R728

P4

VDDIO

DOVDD1V8

DVDD1V5

DGND1

MIPI_RDP0

MIPI_RDN0

DGND2

MIPI_RCP0

MIPI_RCN0

DGND3

MIPI_RDP1

MIPI_RDN1

DGND4

DGND5

MCLK

STROBE

DGND6

SIO_D

SIO_C

RESET

PWDN

AGND

AVDD2V8

AVDDAF

AFGND

AFGND1

HLD1

HLD2

VBAT

Float

U711

R725

100nF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

LED_RGB_TOP

100R

C714

100nF

180R

I2C mode

C713

2.2uF

180R

G-Sensor

CMMCLK

ICMF062P900MFR

R723

0R

R724

0R

VBAT

LED700

VIO18_PMU

C712

1uF

1uF

ICMF062P900MFR

P3,7

C722

1uF 33pF

U708

4

1uF

C708C709 C710

1uF

P3,7

C711

P3,7

C707

1uF

C721

33pF_NC

Title

<Title>

Size

D

Document Number

<Doc>

Date:

5

Wednesday, April 23, 2014

1

Rev

<RevCode>

Sheet

of

10

SD CARD

TP800 TP801 TP802 TP803 TP804 TP805 TP806 TP807

MCDAT2

MCCMD

MCDAT0

GND VMCH

VCHG

VMCH_PMU

C800

MCDAT3

MCCLK

MCDAT1

2.2uF

TVS800

TVS801 TVS802

P3

P3

1

2

3

4

5

6

7

8

MC1DAT2

MC1DAT3

MC1CMD

MC1CK

MC1DAT0

MC1DAT1

DAT2

CD/DAT3

CMD

TF12P_HING

VDD

CLK

VSS

DAT0

DAT1

HOLD1

HOLD2

HOLD3

HOLD4

P3

VCC

DM

DP

Boot

GND

6

7

8

9

RV800 RV801 RV802 RV803 RV804 RV805

HLD1

HLD2

HLD3

HLD4

NC

NC

NC

NC

NC

NC

C

TVS<3pF TVS<3pF

1

P4

CON801

1

2

3

4

5

USB_DM

USB_DP

P3

P3

P3

P3

P3

9

10

11

12

CON800

TVS0402

USB_5PIN

iSINK3

C801

33pF

SUB SIM

VIBR_PMU

CON802

P6

P6

MICMIC+

SPKSPK+

TVS803

P4

SCLK

P4

SRST

8

7

6

5

4

3

2

1

KPLIGHT_FPC

1

REV2

REV1

CLK2

CLK1

RST2

RST1

VCC2

VCC1

REV3

IO

VPP

GND

P4

P4

VSIM2_PMU

12

11

SIO

10

TVS0402

RV810 RV811

33pF

33pF

RV812

4

5

6

SCLK2

SRST2

CLK

RST

VCC

IO

VPP

GND

3

2

1

P4

SIO2

P4

VSIM2_PMU

RV806

VSIM1_PMU

RV807 RV808RV809

33pF

HD1

HD2

HD3

HD4

VSIM1_PMU

SIM_AC0100

MICRO-SIM

GND1

GND2

GND3

GND4

KCOL0

P6

P6

CON803

1

2

3

4

5

6

7

8

9

10

7

8

9

10

P3

1

2

3

4

5

6

7

8

9

10

0R

33pF33pF33pF

RV813

16

15

14

13

R800

VBAT

CON804

33pF

33pF

CON805

TVS804

TVS805

KCOL1

KCOL2

PWRKEY

2

P3

P3

P3,4,8

1

2

3

4

5

TVS806

GND1

COL1

COL2

PWRKEY

GND

VSIM1_PMU

VSIM2_PMU

C802

C803

1uF

1uF

TVS0402

TVS0402

SIDE_KEY

NC

CON806

P3,4,8

1

2

3

PWRKEY

TVS807

GND1

PWRKEY

GND2

SIDE_KEY

NC

Title

<Title>

Size

C

Date:

5

Document Number

<Doc>

Rev

<RevCode>

Sunday, February 09, 2014

Sheet

1

of

10

U300F

Based on your system level design , if

better Wifi performance is needed on

your system, please refer to WiFi

performance enhance proposal

WB_RSTB

Y10

AA10

FM_DATA

FM_CLK

X900

OUT

VCC

GND

NC

VCN_2V8_PMU

MT6627

QVL TCXO

2

1

L905

C901

MT6627 QVL TCXO

XO_IN

AF6

1uF

WB_SCLK

WB_SDATA

WB_SEN

AG7

AF7

AE6

WB_CTRL0

WB_CTRL1

WB_CTRL2

WB_CTRL3

WB_CTRL4

WB_CTRL5

Y6

AA6

AA5

AA4

AB5

AB4

ST900 SHOT

WB_RSTB

AVDD18_WBG

XIN_WBG

GPS_RXQN

GPS_RXQP

GPS_RXIN

GPS_RXIP

F2W_DATA

F2W_CLK

WB_SCLK

WB_SDATA

WB_SEN

WB_TXQN

WB_TXQP

WB_TXIN

WB_TXIP

WB_CRTL0

WB_CRTL1

WB_CRTL2

WB_CRTL3

WB_CRTL4

WB_CRTL5

WB_RXQN

WB_RXQP

WB_RXIN

WB_RXIP

ANT_SEL0

ANT_SEL1

ANT_SEL2

0R

L900

0R

SYSCLK_WCN

AE4

AD6

VCN_1V8_PMU

XO_IN

AF5

AG5

AG4

AF4

GPS_RX_QN

GPS_RX_QP

GPS_RX_IN

GPS_RX_IP

AF2

AG2

AF1

AE1

WB_TX_QN

WB_TX_QP

WB_TX_IN

WB_TX_IP

AE2

AD2

AC2

AC1

WB_RX_QN

WB_RX_QP

WB_RX_IN

WB_RX_IP

AB25

AC26

AC25

C900

100nF

ANT_SEL0

P1

MT6582_LPDDR2

WB_CTRL3

W901

WB_CTRL2

WIFI/BT/GPS Single ANT Ref.

WB_CTRL4

WB_CTRL1

W900

ANTENNA3*5

WB_CTRL5

Close to MT6572

ANTENNA3*5

WB_CTRL0

U900

TP900

WIFI_TEST

GND3

50 Ohm

WIFI

C917 15pF

WBG_ANT

WB_GPS_RF_IN

100nF

21

23

24

22

WB_RX_IP

31

WB_RX_IN

WBG_ANT 50 Ohm

WB_CTRL0

NC

C904

WB_CTRL1

W_LNA_EXT

C903

VCN_1V8_PMU

WB_RX_IN

25

U901

WB_CTRL2

C918 18pF GPS_ANT

26

GPS

WB_CTRL3

GND2

MTK QVL Diplexer

27

L902

NC

WB_CTRL4

L901

NC

30

NC

AVDD18_WBG

WB_CTRL5

C902

GND1

28

ANT

AVDD18_WBT

50 Ohm

29 AVDD18_WB

WB_RX_IP

0R 50 Ohm

R900

WB_RX_QP

20 WB_RX_QP

AVDD18_WB

32

Based on your system level design , if

better WiFi TX performance is needed on

your system, please refer to WiFi

performance enhance proposal

AVDD33_WB

33

35

AVDD28_FM

36

37

P6

FM_RX_N_6572

P6

FM_LANT_N

4mil - defferential - GND shielding

L903

FM_ANT

82nH

WB_RX_QN

AVDD33_WBT

WB_TX_IP

NC1

WB_TX_IN

NC2

WB_TX_QP

AVDD28_FM

WB_TX_QN

MT6627PN_QFN40

FM_LANT_N

GPS_RX_IP

R901

0R

R902

0R

VCN_1V8_PMU

19 WB_RX_QN

AVDD18_GPS

34

FM

GPS_DPX_RFOUT

VCN_1V8_PMU

18 WB_TX_IP

Star Conn

for WB/GPS/WBG 1V8

17 WB_TX_IN

C905

C906

C907

C908

4.7nF

100nF

100pF

1uF

16 WB_TX_QP

15 WB_TX_QN

14 GPS_RX_IP

FM_LANT_P

38

FM_LANT_P

GPS_RX_IN

13 GPS_RX_IN

MT6627 SMD QFN40

AVDD18_GPS

GPS_RX_QN

U902

OUT

4 C919 18pF

L906

G1

G2

G3

IN

2

3

5

7.5nH

GND2

RFIN

EN

VCC

11 GPS_RX_QN

R903

0R

VCN_2V8_PMU

XO_IN

CEXT

SEN

SDATA

SCLK

10nF

10

0R

R907

ANT_SEL0

F2W_CLK

0R

0R

refer to FM desense performance

enhance proposal

C910

R905

R906

F2W_DATA

6

5

GND1 RFOUT

FM_DBG

GPS_ANT

12 GPS_RX_QP

AVDD28_FM

DVSS

U903

41

GPS_RX_QP

HRST_B

AVDD18_GPS 40

GPS_RFIN

AVDD28_FSOURCE

39

NC

C909

L904

NC

Close to MT6627

VCN_2V8_PMU

C920

AR8159

SAFEB1G57KE0F00

C921

AVDD33_WB

NC

R904

0R

VCN_3V3_PMU

WB_RSTB

1uF

XO_IN

C911

C912

C913

1uF

100pF

2.2uF

C916

C914

C915

2.2uF

220nF

FM_DATA

100pF

FM_CLK

WB_SCLK

WB_SDATA

A

WB_SEN

Title

<Title>

Size

Document Number

Custom<Doc>

Date:

5

Rev

<RevCode>

Sunday, February 09, 2014

Sheet

1

of

10

1.ADD C427 C722 AND VCAM-AF POWER. 2014.04.08

2. ADD B700. 2014.04.23

3. ADD NET VM1. 2014.04.23

4. ADD R136 W103 W104 W105. 2014.04.23

D

5. ADD C723. 2014.04.24

Title

<Title>

Size

A

Date:

5

Document Number

<Doc>

Wednesday, April 23, 2014

2

Rev

<RevCod

Sheet

of

10

1

10

Potrebbero piacerti anche

- DFL-SRP For Seagate Firmware Repair ModuleDocumento4 pagineDFL-SRP For Seagate Firmware Repair ModuleStanley MorganNessuna valutazione finora

- PDF Created With Fineprint Pdffactory Trial Version: +va +VCCDocumento1 paginaPDF Created With Fineprint Pdffactory Trial Version: +va +VCCFloreaOvidiuNessuna valutazione finora

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocumento67 pagineAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaNessuna valutazione finora

- Register Transfer Level Design With Verilog: Verilog Digital System Design Z. Navabi, Mcgraw-Hill, 2005Documento77 pagineRegister Transfer Level Design With Verilog: Verilog Digital System Design Z. Navabi, Mcgraw-Hill, 2005I am number 4Nessuna valutazione finora

- Eng TELE-satellite 1211Documento292 pagineEng TELE-satellite 1211Alexander WieseNessuna valutazione finora

- CPI GTR150 Frame T74-40000-00-00Documento47 pagineCPI GTR150 Frame T74-40000-00-00Kurniawan AdeNessuna valutazione finora

- Mascaras Componentes MotorolaDocumento12 pagineMascaras Componentes MotorolaWillian da FonsecaNessuna valutazione finora

- FLEX 5000 Modules Specifications PDFDocumento112 pagineFLEX 5000 Modules Specifications PDFFederico Franchino100% (1)

- 2196cl ChinaDocumento1 pagina2196cl Chinapsequera29100% (2)

- LCD Monitor - DC - XL2720TZ - 20130805 - 144041 - 5E.23A01.011 (4H.23A01.S11)Documento12 pagineLCD Monitor - DC - XL2720TZ - 20130805 - 144041 - 5E.23A01.011 (4H.23A01.S11)pasmanteriabella100% (1)

- Transisorfm 15 Watt Schematic FM DIYDocumento1 paginaTransisorfm 15 Watt Schematic FM DIYGabrielRichardHeizerMillerNessuna valutazione finora

- FC360,361 (08) SchematicDocumento1 paginaFC360,361 (08) SchematicFloreaOvidiuNessuna valutazione finora

- Esquema PDFDocumento1 paginaEsquema PDFNaigel DiasNessuna valutazione finora

- Sonoff TH10A (16A) SchmaticDocumento2 pagineSonoff TH10A (16A) SchmaticdjbobyNessuna valutazione finora

- Frequency Central's Superfly, by ThomasDocumento3 pagineFrequency Central's Superfly, by ThomasThomas Eduardt HafemannNessuna valutazione finora

- ANI-D and TOE-8870 Control CircuitDocumento3 pagineANI-D and TOE-8870 Control Circuitserga3330% (1)

- MB1075 BBDocumento7 pagineMB1075 BBCésar TapiaNessuna valutazione finora

- 1015p Io BoardDocumento13 pagine1015p Io BoardContreras CarlosNessuna valutazione finora

- Behringer Djx700 Professional Mixer DJ Schematic AudioDocumento10 pagineBehringer Djx700 Professional Mixer DJ Schematic AudioMinciuna Catalin100% (1)

- Scott Bernardi PT2399 Echo DelayDocumento3 pagineScott Bernardi PT2399 Echo DelayMuhammad Ma'ruf AsyhariNessuna valutazione finora

- Realtek 8111F SpecDocumento2 pagineRealtek 8111F SpecPan RongNessuna valutazione finora

- TV TCL Ms82g0 Mab2xg (Ms82g) To MymDocumento6 pagineTV TCL Ms82g0 Mab2xg (Ms82g) To Mymvovan15Nessuna valutazione finora

- SDM Com128Documento1 paginaSDM Com128Kudo TruongNessuna valutazione finora

- Power SCH: Va1931Wa-Led-1 Viewsonic Corporation Va1931Wma-Led-1Documento2 paginePower SCH: Va1931Wa-Led-1 Viewsonic Corporation Va1931Wma-Led-1Deki PericNessuna valutazione finora

- Phan CungDocumento1 paginaPhan CungNguyen Anh Tuan100% (1)

- mlt666 Rev2.8l 166Documento1 paginamlt666 Rev2.8l 166victoras21Nessuna valutazione finora

- Vestel 17MB95Documento10 pagineVestel 17MB95POLAKU2002Nessuna valutazione finora

- Compact Power Supply SchematicDocumento1 paginaCompact Power Supply SchematicttnaingNessuna valutazione finora

- LG - LS-K1862HL Ex View & Parts ListDocumento8 pagineLG - LS-K1862HL Ex View & Parts ListGuillermo HernandezNessuna valutazione finora

- Samsung BN44-00351B PDFDocumento2 pagineSamsung BN44-00351B PDFmosquido100% (1)

- HDMI, GPIO and protection circuit diagramDocumento9 pagineHDMI, GPIO and protection circuit diagramnaughtybigboyNessuna valutazione finora

- CB Radio CRE8900 Schematic SMDocumento6 pagineCB Radio CRE8900 Schematic SMraymihregNessuna valutazione finora

- 196 CC EngineManualDocumento14 pagine196 CC EngineManualTony KellyNessuna valutazione finora

- ZANDER FT2101 (T2S01) (WWW - Pieseelectronice.go - Ro)Documento1 paginaZANDER FT2101 (T2S01) (WWW - Pieseelectronice.go - Ro)cosaceaion100% (1)

- Akai MPC2000XL Main Board Schematics 1 PDFDocumento1 paginaAkai MPC2000XL Main Board Schematics 1 PDFAnonymous QgauLK2jdnNessuna valutazione finora

- Amplifier Yiroshi 1500wDocumento1 paginaAmplifier Yiroshi 1500wAlvaro Jose ArgumedoNessuna valutazione finora

- AKAI VS G260 General Information and Service SettingsDocumento14 pagineAKAI VS G260 General Information and Service SettingsbartholomuszNessuna valutazione finora

- Block Diagram and Power Sequence for 1015P MotherboardDocumento42 pagineBlock Diagram and Power Sequence for 1015P MotherboardYustiani RazakNessuna valutazione finora

- Filter and control circuit diagramDocumento10 pagineFilter and control circuit diagramSledge Hammer50% (2)

- SW-5.1 3005 Service ManualDocumento17 pagineSW-5.1 3005 Service ManualBizoo76Nessuna valutazione finora

- Speedlite 580EX DespieceDocumento17 pagineSpeedlite 580EX DespieceFRANNessuna valutazione finora

- Samsung Placa Fuente-Inverter Bn44-00264a A - IpbDocumento2 pagineSamsung Placa Fuente-Inverter Bn44-00264a A - Ipbvideoson50% (2)

- JVC Th-V70-r DVD Digital Cinema System 2002 SMDocumento18 pagineJVC Th-V70-r DVD Digital Cinema System 2002 SMAriel NavarreteNessuna valutazione finora

- Bright Mid Shift: StudiotoneDocumento3 pagineBright Mid Shift: StudiotonerootedmanateeNessuna valutazione finora

- 2002 Schematic Files for 051790a3 PCBDocumento19 pagine2002 Schematic Files for 051790a3 PCBItalo BocattuNessuna valutazione finora

- C Audio SR707 SchematicsDocumento4 pagineC Audio SR707 SchematicsBNessuna valutazione finora

- Ip04 Ip08 v1.3Documento6 pagineIp04 Ip08 v1.3prasad357Nessuna valutazione finora

- 760GXK8MC Manual v1.0 TCH (91 181 760 M2 0T)Documento23 pagine760GXK8MC Manual v1.0 TCH (91 181 760 M2 0T)cesar marcanoNessuna valutazione finora

- Pt10a Ag PDFDocumento66 paginePt10a Ag PDFCharles HollandNessuna valutazione finora

- Aleph PcbsDocumento5 pagineAleph PcbsaoctaNessuna valutazione finora

- Ericsson For Sale From Powerstorm 4SI01141080Documento13 pagineEricsson For Sale From Powerstorm 4SI01141080nethouse123Nessuna valutazione finora

- STM32F4Discovery SchematicDocumento6 pagineSTM32F4Discovery SchematicAda CsabaNessuna valutazione finora

- SCH CpuDocumento1 paginaSCH CpuWilliams Giorgio Sicsu100% (2)

- Vestel 17mb62-1 SCHDocumento9 pagineVestel 17mb62-1 SCHb.nedelkov100% (2)

- DOP7Documento2 pagineDOP7Nghia Do100% (1)

- Computer-Generated Circuit DiagramDocumento1 paginaComputer-Generated Circuit Diagramatomo33Nessuna valutazione finora

- Gc150ata 01Documento5 pagineGc150ata 01ValdairVelozoSoaresNessuna valutazione finora

- STM32-E407 SCHDocumento1 paginaSTM32-E407 SCHBenjaminReckNessuna valutazione finora

- Compact title for circuit diagram documentDocumento3 pagineCompact title for circuit diagram documentAdrian PeterNessuna valutazione finora

- ANALOG IF PART SCHEMATICDocumento11 pagineANALOG IF PART SCHEMATICtavitaraNessuna valutazione finora

- Daewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBDocumento27 pagineDaewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBJavier Silva AlanisNessuna valutazione finora

- SGH-N620 Power Management Schematic: Samsung ElectronicsDocumento6 pagineSGH-N620 Power Management Schematic: Samsung ElectronicsDidik EfendiNessuna valutazione finora

- Rpi 3b v1 2 Schematic ReducedDocumento1 paginaRpi 3b v1 2 Schematic ReducedZeirus100% (1)

- Philips 42pfl5432 Lc7.1ala Psu PDFDocumento4 paginePhilips 42pfl5432 Lc7.1ala Psu PDFliviucatalinNessuna valutazione finora

- P510 Circuit DiagramDocumento6 pagineP510 Circuit DiagramtjiangNessuna valutazione finora

- CDN Incisive Simulation Acceleration DeploymentDocumento10 pagineCDN Incisive Simulation Acceleration DeploymentexfmlnNessuna valutazione finora

- MOdul Pengganti Untuk Egsv3Documento18 pagineMOdul Pengganti Untuk Egsv3yumarestuNessuna valutazione finora

- MR 198CVS Video Processor User Manual V1.0 20140505 PDFDocumento120 pagineMR 198CVS Video Processor User Manual V1.0 20140505 PDFMauricio DiazNessuna valutazione finora

- LCA Lec20-21 Thevenin-Norton 082010Documento19 pagineLCA Lec20-21 Thevenin-Norton 082010Kainat KhalidNessuna valutazione finora

- BS Au 265-2-1995 (2000) Iso 6518-2-1995 PDFDocumento16 pagineBS Au 265-2-1995 (2000) Iso 6518-2-1995 PDFamerNessuna valutazione finora

- Synchronous Step-Down11Documento57 pagineSynchronous Step-Down11ed251Nessuna valutazione finora

- An Introduction To Software Defined Radio: November 2015Documento5 pagineAn Introduction To Software Defined Radio: November 2015MarcosZelayaNessuna valutazione finora

- Analysis and Design of Wireless Power Transmission Through Inductive CouplingDocumento15 pagineAnalysis and Design of Wireless Power Transmission Through Inductive Couplingmadhan_M46Nessuna valutazione finora

- Products t1 Brochure TrioDocumento8 pagineProducts t1 Brochure TrioAhmed El-ShafeiNessuna valutazione finora

- PIX Firewall 520Documento24 paginePIX Firewall 520seshuaravapalliNessuna valutazione finora

- LG Oled65g6p T-Con Board Layout Voltages 2017Documento10 pagineLG Oled65g6p T-Con Board Layout Voltages 2017Fernando AguiarNessuna valutazione finora

- Práctica 1 TiristoresDocumento15 paginePráctica 1 TiristoresDorian JesusNessuna valutazione finora

- ASIC Design Flow TutorialDocumento130 pagineASIC Design Flow TutorialAgnathavasiNessuna valutazione finora

- Powers of 2 Table - Vaughn's SummariesDocumento2 paginePowers of 2 Table - Vaughn's SummariesAnonymous NEqv0Uy7KNessuna valutazione finora

- Paravicini 312 Control Centre Large MemoryDocumento2 pagineParavicini 312 Control Centre Large Memoryapi-3833673Nessuna valutazione finora