Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

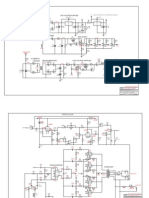

modEEGamp v1.1

Caricato da

TepeRudeboyDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

modEEGamp v1.1

Caricato da

TepeRudeboyCopyright:

Formati disponibili

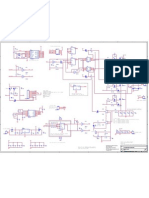

PAD202

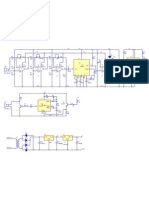

G=40

G=6..100

HP 1 pole fc=0.16 Hz

R237

R233

1F

10k

15k

R234

100k

8.2k

P203

20k

C235

VGND

R235

100k

C233

VGND

IC206PWR

C224

VGND

100nF

1nF

1nF

C227

C223

R225

1k

C230

100nF

R222

1

100nF

AGND VGND

+5V/2

TLC277P

VCC

100nF

INA114P

100nF

ADIN0

220nF 5%

C215

TLC277P

1M

R236

V-

+5V/2

VGND

Right-leg driver (DRL) notes:

simulates electrode impedance

Important usage instructions for the DRL.

If you only want to use one channel, never let the other channel float.

Always connect the unused terminals to VGND, or the DRL will not work properly.

DRL design from http://www.biosemi.com/publications/artikel7.htm, fig.3

See http://openeeg.sf.net for more information.

Authors: Moritz v. Buttlar, Joerg Hansmann, Andreas R

R238

Cal_GND

10k

AGND

R240

100

u cal

If P201 is needed, adjust potentiometer so DRL=0mV (referred to VGND)

when _all_ amplifier inputs are shorted to the DRL output (R_LEG).

PAD204

PAD203

U_cal

R239

10k

TLC277P

100nF

+

C201

47F tan 1ohm

AGND

P201 is not needed when INA114 instrumentation amplifiers are used.

You may replace it with a short wire from pin 2 and pin 1 (VGND).

C208

R227

1M

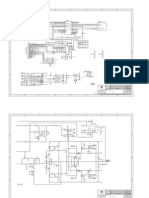

2.0V buf

Ground plane is VGND

R223

AGND

1M

voltage divider 1:20000

5Vp-p +/-10% => 250Vp-p +/-10%

250Vpp +/-10%, 0.1 .. 100Hz

Square wave Calibration Signal

+5V/2

Vcc analog

1nF

AGND

VGND ref. voltage

+2V, buffered

100nF

2.0V

+

47F

20k

P201

C219

modEEGamp_v1_1_Rev. A

Olimex LTD, Bulgaria, 2013

https://www.olimex.com

100nF

IC201B

Only insert IC201 on _one_ board

when using 2 or 3 amplifier boards

IC201A

8

10nF

C213

C211

C203 10nF

TLC277P

VGND

C202

+5V/2

VGND

TLC277P

IC204PWR

GND

10k

1nF

AGND

3

1

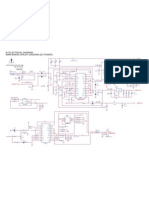

The solder-jumpers (SJ201 - SJ206)

to the right, are used for channel

mapping. This allows multiple amplifier

boards to share the same connector.

2 channels must be selected on each

board by closing two jumper gaps with

solder.

Use SJ201 and SJ204 for the first board.

J201

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

2.0V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

1

1

1

ADIN1

IC204A

R218

ADIN0

AGND

VCC

C226

C216

200k

C212

IC206B

5

1M

C218

V+

5

7

R210

C228

GND

R209

IC206A

C221

2k2

C236

2k2

G=16

33nF 5%

1F

R226

3

3

+5V/2

AGND

Q204

BC557

PAD205

COM

R213

3rd order "Besselworth" filter, fc = 59 Hz.

The 3rd pole is located on the digital board.

2k2

R217

VGND

1nF

TLC277P

R216

2k2

right leg driver

R_LEG

IC205PWR

1nF

PAD206

R_LEG

100k

C232

VGND

AGND

Right Leg

Electrode

R230

C222

VGND

2k2

R203

VGND

VGND

IC203

2

3

100pF

1 1

Q208

BC547

8.2k

C225

G=12.2

Q202

BC557

1 1

10pF

C206

CH1+

2k2

2k2

100pF

R211

2k2

Q206

BC547

R229

100k

Electrode

DC checkpoint

R212

C210

Channel 1 +

Electrode

10k

R204

C207

CH1-

R221

1k

+5V/2

TLC277P

Input Voltage Full Scale (10 Bit) = 512uVpp

Input Voltage Resolution (1 LSB) = 0.5 uVpp

Total gain = 7812.5

Input can handle up to +/-100mV DC electrode offset

Channel 1 Electrode

P202

20k

IC204B

R219

R220

1

100nF

ADIN1

15k

100nF

100nF

AGND VGND

10k

VCC

100nF

C214

INA114P

R206

1F

TLC277P

1

2

C231

V-

C217

GND

2k2

V+

33nF 5%

IC205B

R228

220nF 5%

5

7

R232

C220

C229

C234

1M

2k2

R215

Q203

BC557

R205

IC205A

2k2

2k2

1F

G=16

R231

R214

VGND

R201

G=40

G=6..100

HP 1 pole fc=0.16 Hz

1M

Q201

BC557

CH2+ 2k2

+5V/2

IC202

2

Q207

BC547

2k2

1 1

2

3

100pF

1 1

C205

10pF

C204

C209

Channel 2 +

Electrode

Q205

BC547

G=12.2

R207

2k2

3

2k2

R224

HF rejection

CH2- R202

100pF

Channel 2 Electrode

PAD201

Electrode

DC checkpoint

ESD protection

and user current limiter

R208

2 SJ201

2 SJ202

2 SJ203

1

1

1

2 SJ204

2 SJ205

2 SJ206

PWM

PINHD-2X17

PWM cal (PB1)

Output Voltage Full Scale (10 Bit) = 4.000 Vp-p (Range 0..4V)

=> 3.9mV bitstep at 10 bit resolution.

This hardware design by Olimex LTD is licensed under a Creative Commons Attribution-ShareAlike 3.0 Unported License.

Potrebbero piacerti anche

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsDa EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNessuna valutazione finora

- 11 Digit VFD Display With AC Filament Drive C021 EB 20-Bit VFD ...Documento1 pagina11 Digit VFD Display With AC Filament Drive C021 EB 20-Bit VFD ...Ioana Bulgariu100% (1)

- Watson Fa5116 Chassis Pt11Documento0 pagineWatson Fa5116 Chassis Pt11Andrei ConstantinNessuna valutazione finora

- Cigpack Main RC1aDocumento1 paginaCigpack Main RC1aMotojunkie TLNessuna valutazione finora

- SBC ShematicsDocumento16 pagineSBC ShematicsTom TommyNessuna valutazione finora

- CignalDocumento1 paginaCignalNiaz Manik100% (1)

- PCS 4000 SchematicDocumento3 paginePCS 4000 SchematicJuan Carlos Perdomo100% (3)

- VCC GND: Simple Dds - Based Signal GeneratorDocumento1 paginaVCC GND: Simple Dds - Based Signal GeneratorM'hamed Klouz100% (1)

- U3 D1 U1 LCD16x2 U2 LM7805: VCC VDDDocumento1 paginaU3 D1 U1 LCD16x2 U2 LM7805: VCC VDDNguyen Anh TuanNessuna valutazione finora

- PIC16F876A ESO Sine Wave InverterDocumento1 paginaPIC16F876A ESO Sine Wave InverterNguyen Khang100% (1)

- Vin IC2Documento1 paginaVin IC2Harish Kumar MNessuna valutazione finora

- CircuitDocumento1 paginaCircuitShahid Naseem100% (1)

- V772 Benq MonitorDocumento23 pagineV772 Benq MonitorPaulo BorgesNessuna valutazione finora

- ADV Main SchematicDocumento1 paginaADV Main Schematicgerardobrandao100% (1)

- AV42PD20ES - SchematDocumento20 pagineAV42PD20ES - SchematngoclinhdtddNessuna valutazione finora

- 42LK520 InterconnectDocumento7 pagine42LK520 InterconnectErnesto SuarezNessuna valutazione finora

- ZXSpectrum128+2 ServiceManualDocumento12 pagineZXSpectrum128+2 ServiceManualrisxcNessuna valutazione finora

- bd9303fp 165Documento1 paginabd9303fp 1659183290782Nessuna valutazione finora

- Notice DieFET V1 21Documento5 pagineNotice DieFET V1 21Lalo NuñezNessuna valutazione finora

- HPS10 Calidrare SchemaDocumento20 pagineHPS10 Calidrare SchemafercikeNessuna valutazione finora

- I29 Ver1Documento7 pagineI29 Ver1Yashwant FadnisNessuna valutazione finora

- Elite 14es11 Tda111xx La78040 Tda1035Documento1 paginaElite 14es11 Tda111xx La78040 Tda1035aureliancoNessuna valutazione finora

- Noblex 21TC678F Chasis LA7 - ADocumento1 paginaNoblex 21TC678F Chasis LA7 - AJuan Eduardo FerreyraNessuna valutazione finora

- Cce PDFDocumento1 paginaCce PDFotaviojose100% (1)

- Ce32wn4f CDocumento3 pagineCe32wn4f CthedamnedNessuna valutazione finora

- LM220WE4Documento8 pagineLM220WE4acostaricciNessuna valutazione finora

- RK-10132 113Documento1 paginaRK-10132 113Sumit SinghNessuna valutazione finora

- Tomson 32LB220B4 2Documento83 pagineTomson 32LB220B4 2lust1Nessuna valutazione finora

- 1436 AschDocumento1 pagina1436 AschchronotonNessuna valutazione finora

- Panasonic Dp1520Documento2 paginePanasonic Dp1520Dorn UnderlightNessuna valutazione finora

- Memorex MLT1532 - SM (Sharp LCD Panel)Documento16 pagineMemorex MLT1532 - SM (Sharp LCD Panel)Radu AndreiNessuna valutazione finora

- 10606-Figure 1Documento1 pagina10606-Figure 1novanecNessuna valutazione finora

- DatasheetDocumento24 pagineDatasheetRafael PavanNessuna valutazione finora

- UltrasonicDocumento1 paginaUltrasonicNaman TamrakarNessuna valutazione finora

- LG 50PJ350 Block Diagram (SCH)Documento3 pagineLG 50PJ350 Block Diagram (SCH)Lazaro80% (5)

- Schematic - Pic ModuleDocumento1 paginaSchematic - Pic ModuleDuc Le100% (1)

- L Out R Out R4 in R3 in R2 In: +5V SCL SDADocumento1 paginaL Out R Out R4 in R3 in R2 In: +5V SCL SDAFloreaOvidiuNessuna valutazione finora

- Base Amp Art Series Pst355cDocumento2 pagineBase Amp Art Series Pst355cAnastasiou Michalis100% (1)

- CT21MF2 Ac5-G1Documento1 paginaCT21MF2 Ac5-G1Riza BaduaNessuna valutazione finora

- Od3 Schematic Carrillo Values Jan 2012Documento4 pagineOd3 Schematic Carrillo Values Jan 2012Pablo Carrillo SanmartínNessuna valutazione finora

- BLF6G22-180PN 2Documento11 pagineBLF6G22-180PN 2mihai315300100% (1)

- BPL bc10fwrDocumento1 paginaBPL bc10fwrMajesticDogeNessuna valutazione finora

- TB6560AHQ 4-Axis CNC Driver PDFDocumento7 pagineTB6560AHQ 4-Axis CNC Driver PDFMai HuyNessuna valutazione finora

- Konka Chassis AXT1 EXT1 AX CX Series SchemaDocumento1 paginaKonka Chassis AXT1 EXT1 AX CX Series SchemaHenry Ecos HuayhuataNessuna valutazione finora

- DOP7Documento2 pagineDOP7Nghia Do100% (1)

- Diagrama TV Lynx 29 Xoceco Ts2980-Global Home Gh29s-Prima-ntc Nt29r Lynx Lyf-29 (Ka5q0765-La76932Documento1 paginaDiagrama TV Lynx 29 Xoceco Ts2980-Global Home Gh29s-Prima-ntc Nt29r Lynx Lyf-29 (Ka5q0765-La76932Gustavo ValdezNessuna valutazione finora

- SP200S SCH V126Documento1 paginaSP200S SCH V126thaimt97Nessuna valutazione finora

- Buck Converter Schematic PDFDocumento1 paginaBuck Converter Schematic PDFFahmy Akbar AparatNessuna valutazione finora

- RCF Art310a Base Amp Art Series Se515666 2005Documento3 pagineRCF Art310a Base Amp Art Series Se515666 2005tlw72100% (1)

- XR8600DDocumento22 pagineXR8600DHernan Ortiz Enamorado100% (1)

- SAMSUNG TFT-LCD 933HD (LS19CFE) - TroubleshootingDocumento28 pagineSAMSUNG TFT-LCD 933HD (LS19CFE) - TroubleshootingJoão Lopes100% (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDa EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsValutazione: 3 su 5 stelle3/5 (2)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Da EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Valutazione: 4.5 su 5 stelle4.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorDa Everand110 Waveform Generator Projects for the Home ConstructorValutazione: 4 su 5 stelle4/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysDa EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Rulership in 1St To 14Th Century Scandinavia: Dagfinn Skre (Ed.)Documento1 paginaRulership in 1St To 14Th Century Scandinavia: Dagfinn Skre (Ed.)TepeRudeboyNessuna valutazione finora

- H. H. Coston,: Vzžzzor ???Documento4 pagineH. H. Coston,: Vzžzzor ???TepeRudeboyNessuna valutazione finora

- (Lithuanian Annual Strategic Review) Missile Defense - What It Is Designed For and How It Is UnderstoodDocumento25 pagine(Lithuanian Annual Strategic Review) Missile Defense - What It Is Designed For and How It Is UnderstoodTepeRudeboyNessuna valutazione finora

- Ball Mill Tool For Crushing Coffee and Cocoa BeansDocumento6 pagineBall Mill Tool For Crushing Coffee and Cocoa BeansTepeRudeboyNessuna valutazione finora

- Standardization Activities On Society 5.0 in Japan Okamoto Masahide PDFDocumento19 pagineStandardization Activities On Society 5.0 in Japan Okamoto Masahide PDFTepeRudeboyNessuna valutazione finora

- ch1 PDFDocumento42 paginech1 PDFTepeRudeboyNessuna valutazione finora

- Victorian Era Architecture: Nashville Old House SeriesDocumento13 pagineVictorian Era Architecture: Nashville Old House SeriesTepeRudeboyNessuna valutazione finora

- TX Construction 9-10-2013Documento34 pagineTX Construction 9-10-2013TepeRudeboyNessuna valutazione finora

- PW Signal Pistol Ds 3Documento1 paginaPW Signal Pistol Ds 3TepeRudeboyNessuna valutazione finora

- Grcon14 Presentation GrradarDocumento11 pagineGrcon14 Presentation GrradarTepeRudeboyNessuna valutazione finora

- Katyusha Rocket LauncherDocumento7 pagineKatyusha Rocket LauncherTepeRudeboyNessuna valutazione finora

- Topic: Propellants Subtopic: Rocket Propellant: Submitted By:patel Shivam (130280105041) Submitted To: Dr. Shashi MamDocumento9 pagineTopic: Propellants Subtopic: Rocket Propellant: Submitted By:patel Shivam (130280105041) Submitted To: Dr. Shashi MamTepeRudeboyNessuna valutazione finora

- Non-Vessel Operating Common Carrier Terms and ConditionsDocumento2 pagineNon-Vessel Operating Common Carrier Terms and ConditionsTepeRudeboyNessuna valutazione finora

- The New SW 76 Submachine Gun (Small Arms Review)Documento3 pagineThe New SW 76 Submachine Gun (Small Arms Review)antermv86% (7)

- Partita1 Bach ViolinDocumento13 paginePartita1 Bach Violinjesseka.jasmine8550Nessuna valutazione finora

- Glossary of Terms in Greek Architecture HandoutDocumento9 pagineGlossary of Terms in Greek Architecture HandoutJungNessuna valutazione finora

- 537 3083 4 PBDocumento7 pagine537 3083 4 PBSupriyanto SupriyantoNessuna valutazione finora

- India Literature Silence! The Court Is in Session by Vijay TendulkarDocumento23 pagineIndia Literature Silence! The Court Is in Session by Vijay TendulkarAarti Naidu67% (3)

- Vivaldi Concerto Sol Maior Fagote PDFDocumento4 pagineVivaldi Concerto Sol Maior Fagote PDFDaniela CortezNessuna valutazione finora

- All We Need Is Love - 10 1º Trompete BBDocumento1 paginaAll We Need Is Love - 10 1º Trompete BBMarcos DoffiniNessuna valutazione finora

- F 117aDocumento192 pagineF 117aremow80% (10)

- DS27T-GDW Specification PDFDocumento3 pagineDS27T-GDW Specification PDFBromand TurkmaniNessuna valutazione finora

- Isabelle VengerovaDocumento70 pagineIsabelle VengerovaPailo76100% (1)

- Advanced Wireless CommunicationsDocumento39 pagineAdvanced Wireless CommunicationsRaees AhmadNessuna valutazione finora

- Pop Icons Take The StageDocumento2 paginePop Icons Take The StageNikki DabneyNessuna valutazione finora

- Jon BatisteDocumento4 pagineJon BatisteLuisFelipeCastañedaLópezNessuna valutazione finora

- Dhaka District ProfileDocumento19 pagineDhaka District ProfileShohel RanaNessuna valutazione finora

- BlazeVOX 14 Fall 2014 - An Online Journal of VoiceDocumento477 pagineBlazeVOX 14 Fall 2014 - An Online Journal of VoiceGeoffrey GatzaNessuna valutazione finora

- LTE Radio Protocol StackDocumento1 paginaLTE Radio Protocol StackzakiNessuna valutazione finora

- Catalogo de Antenas MoyanoDocumento198 pagineCatalogo de Antenas MoyanoDaniel SchmidtNessuna valutazione finora

- xl40h PDFDocumento60 paginexl40h PDFnenadNessuna valutazione finora

- Od Yishama (May There Be Heard) Sheet Music - 8notesDocumento1 paginaOd Yishama (May There Be Heard) Sheet Music - 8notesYohananMartinsNessuna valutazione finora

- English 1 - Week 7 C4)Documento23 pagineEnglish 1 - Week 7 C4)AlcantaraSusyNessuna valutazione finora

- Duet in C Minor Flex Score and PartsDocumento88 pagineDuet in C Minor Flex Score and PartssuperheropmgNessuna valutazione finora

- Organic Light Emitting DiodesDocumento34 pagineOrganic Light Emitting DiodesPradeepNessuna valutazione finora

- HiFi Diamond8 ManualDocumento6 pagineHiFi Diamond8 ManualRonnie AnthonyNessuna valutazione finora

- Bharat Electronics LimitedDocumento21 pagineBharat Electronics Limitedarpan shuklaNessuna valutazione finora

- Physical Education and Health Grade 12: Three Components of FitnessDocumento5 paginePhysical Education and Health Grade 12: Three Components of FitnessAndrew Arciosa Calso100% (2)

- Neibour 4GDocumento3.162 pagineNeibour 4GquyphamvanNessuna valutazione finora

- MASCHINE JAM 2.6.5 Cheat Sheet English 0517Documento3 pagineMASCHINE JAM 2.6.5 Cheat Sheet English 0517Anthony Van HamondNessuna valutazione finora

- Tesla Celebration ProgrammeDocumento8 pagineTesla Celebration Programmec1124540Nessuna valutazione finora

- Difference Between Dgps and GPS: Local Coordinate SystemDocumento2 pagineDifference Between Dgps and GPS: Local Coordinate SystemMargaveth P. BalbinNessuna valutazione finora

- Repitoire ProjectDocumento9 pagineRepitoire Projectapi-302925925Nessuna valutazione finora

- RF Power AmplifierDocumento4 pagineRF Power AmplifierYohanes ErwinNessuna valutazione finora