Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

DIC Questions

Caricato da

Ashish KrCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

DIC Questions

Caricato da

Ashish KrCopyright:

Formati disponibili

TSPCR Logic

Inductive parasitic

Barrel shifter

Ratioed Logic

Semi-custom design flow

Limits of scaling

How does power density and Vi scales for fixed voltage scaling and full

scaling.

Switching threshold voltage of a Symmetrical CMOS inverter.

Design abstraction level in the digital circuits.

Explain the source of power consumption (static and dynamic )of CMOS inverter.

Write the drain current equation for P channel MOS transistor of 3

region of operation.

Write the drain current equation for N channel MOS transistor of 3

region of operation.

If 4 pMOS transistor and cascaded source to gate find the output voltage from 4th

pass transistor is tied to 0V assume Vip=-1V.

Sources of clock skew and Jitter.

Graphically obtain the VTC of CMOS inverter where Vdd=2V consider

Vgs= 0,0.4,0.8,0,1.6,2V.

Standard cell based design

Zipper CMOS circuit

Race around condition with waveform.

Pass transistor and transmission gate and their difference

Compute the threshold voltage for Vsb =-2.5V 2(phi)f= 0.6, for PMOS

transistor having threshold of -0.4V given body effect constant of 0.4.

Discuss in detail NORA CMOS logic design style, discuss its advantages

over domino CMOS logic gate

Explain the system integrity issues in dynamic CMOS design.

Explain the standard compile cell and discuss the difference between

macro and mega cells.

Discuss the impact of positive and negative clock skew on the

performance of sequential circuits.

How negative skew avoids races and hampers of the circuit

performance.

Draw and explain the energy band gap of MOS transistor in accumulation

depletion and inversion region.

Problem of cascading of dynamic gates explain ways to solve it

Explain concept of pulse register, draw the circuit diagram and explain

the concept of glitch generation

Pipe-lining approach to optimize the sequential circuits, expression for

minimum allowable clock period for pipe-lining circuit

Design techniques to reduce the delay for large fan in circuits

Elmore delay model

Various methods of scaling of MOS

Domino Logic circuits, Draw Domino circuit for 4:1 mux, 4 bit CLA adder

Switching translation probability and its calculation for XOR Gate.

Explain PLA, PAL and FPGA

Explain meta stability in sequential circuits

Draw CMOS positive edge triggered master slave flip flop

Dual rail circuit for OR/NOR gate

Various problem in Dynamic circuits and their resolution

Draw IV characteristics of P-MOS including channel length modulation

Relationship between mask channel length and electrical length

L=Lm-2Ld where Ld is lateral diffusion length

Draw N-MOS equivalent circuit, explain variation of channel capacitance

as a function of drain source voltage for different operating modes

Potrebbero piacerti anche

- Vlsi DesignDocumento31 pagineVlsi Designajas777BNessuna valutazione finora

- 13-MOSFET - Design and Analysis-24!02!2024Documento14 pagine13-MOSFET - Design and Analysis-24!02!2024ashbinny1Nessuna valutazione finora

- Dheeraj ReportDocumento15 pagineDheeraj ReportGirdhar Gopal GautamNessuna valutazione finora

- Vlsi Design 1 Mark QuestionsDocumento7 pagineVlsi Design 1 Mark QuestionsVallabh JNessuna valutazione finora

- Explain Why & How A MOSFET WorksDocumento3 pagineExplain Why & How A MOSFET WorksRajesh PatjoshiNessuna valutazione finora

- Basic Electronics 6 2006Documento47 pagineBasic Electronics 6 2006umamaheshcoolNessuna valutazione finora

- Self Biased High Performance Folded Cascode Cmos OpampDocumento6 pagineSelf Biased High Performance Folded Cascode Cmos OpampArvind MishraNessuna valutazione finora

- A Self-Biased High Performance Folded Cascode Op-Amp: of ofDocumento6 pagineA Self-Biased High Performance Folded Cascode Op-Amp: of ofBodhayan PrasadNessuna valutazione finora

- Circuit Characterization and ModelingDocumento9 pagineCircuit Characterization and Modelingbikash routNessuna valutazione finora

- VLSI Unit 1 - MOSDocumento86 pagineVLSI Unit 1 - MOSskh_19870% (1)

- MOSFET design and operationDocumento44 pagineMOSFET design and operationAbdul KhaliqNessuna valutazione finora

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Documento10 pagineQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNessuna valutazione finora

- General Digital Design Questions: How Do You Size NMOS and PMOS Transistors To Increase The Threshold Voltage?Documento22 pagineGeneral Digital Design Questions: How Do You Size NMOS and PMOS Transistors To Increase The Threshold Voltage?Rahul VaddelliNessuna valutazione finora

- Chapter04 ExDocumento6 pagineChapter04 ExKarthikeya VemparalaNessuna valutazione finora

- Vlsi BestDocumento4 pagineVlsi Bestkunjanb11Nessuna valutazione finora

- Scaling Effects in MOS DevicesDocumento15 pagineScaling Effects in MOS DevicesVikram KumarNessuna valutazione finora

- Principles and Examples of MOSFET Technology Biasing: AbstractDocumento56 paginePrinciples and Examples of MOSFET Technology Biasing: AbstractLalit KumarNessuna valutazione finora

- EC8395Documento1 paginaEC8395Wearablemems PVTNessuna valutazione finora

- CMOS Technology Question Bank & TutorialDocumento3 pagineCMOS Technology Question Bank & TutorialRathore Yuvraj SinghNessuna valutazione finora

- Vlsi Design Question Bank EEC 703Documento10 pagineVlsi Design Question Bank EEC 703selvi0412Nessuna valutazione finora

- Wiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosDocumento10 pagineWiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosraoNessuna valutazione finora

- Devansh_210108014_LTspiceDocumento14 pagineDevansh_210108014_LTspiceDevansh SinghNessuna valutazione finora

- Ec1461 Vlsi DesignDocumento17 pagineEc1461 Vlsi DesignArunkumarNessuna valutazione finora

- Introduction to CMOS logic and gate designDocumento45 pagineIntroduction to CMOS logic and gate designNishanth Nish0% (1)

- Analog IC Design Viva Questions SummaryDocumento2 pagineAnalog IC Design Viva Questions Summarylucky jNessuna valutazione finora

- Complete Vlsi NotesDocumento160 pagineComplete Vlsi NotesTarun SinghalNessuna valutazione finora

- For Other Uses, See .: CMOS (Disambiguation)Documento11 pagineFor Other Uses, See .: CMOS (Disambiguation)Smitha KollerahithluNessuna valutazione finora

- Question BankDocumento13 pagineQuestion BankRishi JhaNessuna valutazione finora

- Design Issues in CMOS OscillatorsDocumento4 pagineDesign Issues in CMOS OscillatorsdhrubNessuna valutazione finora

- Mecve 101 SPDMDocumento2 pagineMecve 101 SPDMSalini SasidharanNessuna valutazione finora

- Lpvlsi - V Unit Q & ADocumento17 pagineLpvlsi - V Unit Q & ANarasimhulu MaddireddyNessuna valutazione finora

- From Wikipedia, The Free Encyclopedia: CMOS Inverter (NOT Logic Gate)Documento9 pagineFrom Wikipedia, The Free Encyclopedia: CMOS Inverter (NOT Logic Gate)bas_cbkNessuna valutazione finora

- Lecture NotesDocumento28 pagineLecture NotesEE22M306 Manvi ChaudharyNessuna valutazione finora

- Impact of Mosfet Parameters On Its Parasitic Capacitances: Presented byDocumento27 pagineImpact of Mosfet Parameters On Its Parasitic Capacitances: Presented bysattuhappyNessuna valutazione finora

- Linear CMOS Voltage-to-Current Converter Improves Non-LinearityDocumento4 pagineLinear CMOS Voltage-to-Current Converter Improves Non-LinearitydycsteiznNessuna valutazione finora

- VLSI Design: Dr. K. Srinivasa RaoDocumento39 pagineVLSI Design: Dr. K. Srinivasa Raoshen shahNessuna valutazione finora

- Vlsi QDocumento2 pagineVlsi QUma Maheswara Rao PNessuna valutazione finora

- For Other Uses, See .: CMOS (Disambiguation)Documento10 pagineFor Other Uses, See .: CMOS (Disambiguation)Ashutosh DabasNessuna valutazione finora

- CMOS Short-Circuit Power ModelingDocumento4 pagineCMOS Short-Circuit Power ModelingVinsen Teubun LetsoinNessuna valutazione finora

- Chapter 3Documento46 pagineChapter 3Mayank KumarNessuna valutazione finora

- Single Stage and Two Stage OP-AMP Design in 180NM CMOS TechnologyDocumento7 pagineSingle Stage and Two Stage OP-AMP Design in 180NM CMOS TechnologyIJSTE0% (1)

- Assignment - EC 443Documento1 paginaAssignment - EC 443Md saquib SalimNessuna valutazione finora

- Thesis On Operational Transconductance AmplifierDocumento7 pagineThesis On Operational Transconductance AmplifierPaperWritingServicesReviewsCanada100% (2)

- VLSILABVVVVIMPDocumento19 pagineVLSILABVVVVIMPGirija M HegdeNessuna valutazione finora

- EC6304 Electronic Circuits IDocumento12 pagineEC6304 Electronic Circuits Inalinitha100% (1)

- CMOS (Disambiguation) : For Other Uses, SeeDocumento6 pagineCMOS (Disambiguation) : For Other Uses, SeeManas NagNessuna valutazione finora

- Transistor: Vlsi Inter View QuestionsDocumento3 pagineTransistor: Vlsi Inter View QuestionsHarini ManoharanNessuna valutazione finora

- Complete Vlsi NotesDocumento159 pagineComplete Vlsi NotesSUNIL MP75% (4)

- MOS CapacitancesDocumento13 pagineMOS CapacitancesOzephSharifNessuna valutazione finora

- Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedDocumento7 pagineComplementary Metal-Oxide-Semiconductor (CMOS) (PronouncedArchana SadanandanNessuna valutazione finora

- MOSFET CapacitancesDocumento26 pagineMOSFET CapacitancesModyKing99Nessuna valutazione finora

- Question BankDocumento3 pagineQuestion BankTARUN PRASADNessuna valutazione finora

- Foundations of Electromagnetic Compatibility: with Practical ApplicationsDa EverandFoundations of Electromagnetic Compatibility: with Practical ApplicationsNessuna valutazione finora

- Solution Manual for 100 Genesys Design Examples: Second EditionDa EverandSolution Manual for 100 Genesys Design Examples: Second EditionNessuna valutazione finora

- Newnes Radio and Electronics Engineer's Pocket BookDa EverandNewnes Radio and Electronics Engineer's Pocket BookNessuna valutazione finora

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Da EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Valutazione: 4.5 su 5 stelle4.5/5 (3)

- Using Keil Compiler For ARMDocumento17 pagineUsing Keil Compiler For ARMAshish KrNessuna valutazione finora

- SapanaDocumento3 pagineSapanaAshish KrNessuna valutazione finora

- Training REPORT 2K12 (Autosaved) 1Documento29 pagineTraining REPORT 2K12 (Autosaved) 1Ashish KrNessuna valutazione finora

- Frequency Modulation: Forgot Your Password? Join UsDocumento13 pagineFrequency Modulation: Forgot Your Password? Join UsAshish KrNessuna valutazione finora

- Industrial DetailDocumento42 pagineIndustrial DetailAshish KrNessuna valutazione finora

- Amp 1Documento2 pagineAmp 1Ashish KrNessuna valutazione finora

- Need of Wireless CommunicationDocumento16 pagineNeed of Wireless CommunicationAshish KrNessuna valutazione finora

- Shiv-Parvati - (12737040)Documento1 paginaShiv-Parvati - (12737040)Ashish KrNessuna valutazione finora

- Analisis de Fourier SpiegelDocumento197 pagineAnalisis de Fourier SpiegelYenny Serrato100% (1)

- 2 GSM Cell ParametersDocumento100 pagine2 GSM Cell ParametersSalman Zaheer100% (1)

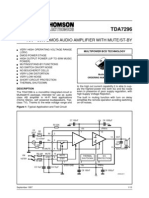

- Tda 7296Documento14 pagineTda 7296Mayra GonzálezNessuna valutazione finora

- Vips 98Pf Digital Earth Leakage Relay: FeaturesDocumento1 paginaVips 98Pf Digital Earth Leakage Relay: FeaturessanthoshNessuna valutazione finora

- Manual Usuario Harman Kardon Avr7000Documento52 pagineManual Usuario Harman Kardon Avr7000Mario Meza Garcia100% (1)

- Motorola-power-transistorsDocumento4 pagineMotorola-power-transistorsMircozzoNessuna valutazione finora

- PerumpaanatrupadaiDocumento13 paginePerumpaanatrupadaiapi-3714781Nessuna valutazione finora

- TP RAT Layer Strategy v3.0Documento28 pagineTP RAT Layer Strategy v3.0mijaz1501Nessuna valutazione finora

- Labview+pulse Shaping and Matched FilteringDocumento12 pagineLabview+pulse Shaping and Matched FilteringcarolmNessuna valutazione finora

- LM318HDocumento19 pagineLM318HAlberto MarsicoNessuna valutazione finora

- CS601 Assigment 2Documento2 pagineCS601 Assigment 2aamir shahzadNessuna valutazione finora

- 1V. Satellite Access - 2Documento49 pagine1V. Satellite Access - 2Sai TejaNessuna valutazione finora

- 010022e Dat Microrep GBDocumento6 pagine010022e Dat Microrep GBsanjittukuNessuna valutazione finora

- Datasheet 1Documento18 pagineDatasheet 1shashwatthakurNessuna valutazione finora

- Reconfigurable Antenna ReferencesDocumento7 pagineReconfigurable Antenna ReferencesFaizal IsmailNessuna valutazione finora

- Wavetek 2100 SMDocumento78 pagineWavetek 2100 SMMongolio AsuzenaNessuna valutazione finora

- DP CalibrationDocumento12 pagineDP CalibrationGeorge AsuncionNessuna valutazione finora

- 205i Innova SonicDocumento4 pagine205i Innova SonictengmorganNessuna valutazione finora

- Genius SW-HF 5.1 5000.rarDocumento26 pagineGenius SW-HF 5.1 5000.rarzzorox100% (3)

- Adptive Antenna Array ParthDocumento22 pagineAdptive Antenna Array ParthANkit JAinNessuna valutazione finora

- Vlsi Design PDFDocumento120 pagineVlsi Design PDFHareesh Harsha100% (1)

- ATPDraw Simulation of Switching TL500kV-00Documento8 pagineATPDraw Simulation of Switching TL500kV-00Ratana KemNessuna valutazione finora

- Digital Communications - Viva Voce QuestionsDocumento3 pagineDigital Communications - Viva Voce QuestionsAllanki Sanyasi Rao100% (1)

- Reidmar: Users ManualDocumento4 pagineReidmar: Users ManualerbugleNessuna valutazione finora

- Ultrasound Distance Measurement: Final Project Report E3390 Electronic Circuits Design LabDocumento8 pagineUltrasound Distance Measurement: Final Project Report E3390 Electronic Circuits Design LabCole AndersonNessuna valutazione finora

- Study On UMTSLTE in 900 MHZ Band and Coexistence With 850 MHZ BandDocumento34 pagineStudy On UMTSLTE in 900 MHZ Band and Coexistence With 850 MHZ BandMuhammad Jamil AwanNessuna valutazione finora

- ECT1J C24 GC0024 Bourns EncoderDocumento3 pagineECT1J C24 GC0024 Bourns EncoderkapokNessuna valutazione finora

- Experiment No: 01 Voltage Controlled OscillatorDocumento7 pagineExperiment No: 01 Voltage Controlled OscillatorSafia SohailNessuna valutazione finora

- The History of CommunicationDocumento3 pagineThe History of CommunicationCybernet Netweb0% (1)

- Marine VHF Radiotelephone (JHS-770S) Two-Way VHF Radiotelephone (Jhs-7) Uhf Antenna System (Nau-6) (Incl. Inst. Manual & Test Report)Documento243 pagineMarine VHF Radiotelephone (JHS-770S) Two-Way VHF Radiotelephone (Jhs-7) Uhf Antenna System (Nau-6) (Incl. Inst. Manual & Test Report)navigator1977Nessuna valutazione finora

- 2G 3G Interference Analysis Caused by RTWP PDFDocumento31 pagine2G 3G Interference Analysis Caused by RTWP PDFDemarco Dayanghirang FormalejoNessuna valutazione finora