Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

XC9536 PDF

Caricato da

Negru P. PlantatieTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

XC9536 PDF

Caricato da

Negru P. PlantatieCopyright:

Formati disponibili

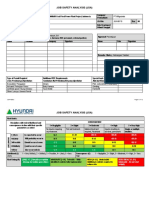

PRODUCT OBSOLETE / UNDER OBSOLESCENCE

XC9536 In-System

Programmable CPLD

DS064 (v7.0) May 17, 2013

Product Specification

Features

Description

5 ns pin-to-pin logic delays on all pins

fCNT to 100 MHz

36 macrocells with 800 usable gates

Up to 34 user I/O pins

5V in-system programmable

- Endurance of 10,000 program/erase cycles

- Program/erase over full commercial voltage and

temperature range

Enhanced pin-locking architecture

Flexible 36V18 Function Block

- 90 product terms drive any or all of 18 macrocells

within Function Block

- Global and product term clocks, output enables,

set and reset signals

Extensive IEEE Std 1149.1 boundary-scan (JTAG)

support

Programmable power reduction mode in each

macrocell

Slew rate control on individual outputs

User programmable ground pin capability

Extended pattern security features for design

protection

High-drive 24 mA outputs

3.3V or 5V I/O capability

Advanced CMOS 5V FastFLASH technology

Supports parallel programming of more than one

XC9500 concurrently

Available in 44-pin PLCC, 44-pin VQFP, 48-pin CSP

packages

The XC9536 is a high-performance CPLD providing

advanced in-system programming and test capabilities for

general purpose logic integration. It is comprised of eight

36V18 Function Blocks, providing 800 usable gates with

propagation delays of 5 ns. See Figure 2 for the architecture

overview.

Power dissipation can be reduced in the XC9536 by configuring macrocells to standard or low-power modes of operation. Unused macrocells are turned off to minimize power

dissipation.

Operating current for each design can be approximated for

specific operating conditions using the following equation:

ICC (mA) = MCHP (1.7) + MCLP (0.9) + MC (0.006 mA/MHz) f

Where:

MCHP = Macrocells in high-performance mode

MCLP = Macrocells in low-power mode

MC = Total number of macrocells used

f = Clock frequency (MHz)

Figure 1 shows a typical calculation for the XC9536 device.

(83)

manc

erfor

High P

Typical ICC (mA)

Power Management

(50)

(50)

er

w Pow

Lo

(30)

50

100

Clock Frequency (MHz)

DS064_01_110101

Figure 1: Typical ICC vs. Frequency for XC9536

1998, 2003-2006, 2013 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

DS064 (v7.0) May 17, 2013

Product Specification

www.xilinx.com

PRODUCT OBSOLETE / UNDER OBSOLESCENCE

R

XC9536 In-System Programmable CPLD

3

JTAG Port

JTAG

Controller

In-System Programming Controller

36

Function

Block 1

18

I/O

Macrocells

1 to 18

I/O

Fast CONNECT II Switch Matrix

I/O

I/O

I/O

Blocks

I/O

I/O

I/O

36

Function

Block 2

18

Macrocells

1 to 18

I/O

3

I/O/GCK

1

I/O/GSR

2

I/O/GTS

DS064_02_110101

Figure 2: XC9536 Architecture

Function block outputs (indicated by the bold line) drive the I/O blocks directly.

www.xilinx.com

DS064 (v7.0) May 17, 2013

Product Specification

PRODUCT OBSOLETE / UNDER OBSOLESCENCE

R

XC9536 In-System Programmable CPLD

Absolute Maximum Ratings

Symbol

Description

Value

Units

0.5 to 7.0

V

V

VCC

Supply voltage relative to GND

VIN

Input voltage relative to GND

0.5 to VCC + 0.5

VTS

Voltage applied to 3-state output

0.5 to VCC + 0.5

65 to +150

oC

+150

oC

TSTG

TJ

Storage temperature (ambient)

Junction temperature

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

Recommended Operation Conditions

Symbol

VCCINT

VCCIO

Parameter

Supply voltage for internal logic

and input buffers

Supply voltage for output drivers

for 5V operation

Commercial TA =

0 oC

to

70oC

Industrial TA = 40oC to +85oC

Commercial TA =

0 oC

to

70oC

Industrial TA = 40oC to +85oC

Supply voltage for output drivers for 3.3V operation

Min

Max

Units

4.75

5.25

4.5

5.5

4.75

5.25

4.5

5.5

3.0

3.6

VIL

Low-level input voltage

0.80

VIH

High-level input voltage

2.0

VCCINT + 0.5

VO

Output voltage

VCCIO

Quality and Reliability Characteristics

Symbol

Parameter

TDR

Data Retention

NPE

Program/Erase Cycles (Endurance)

Min

Max

Units

20

Years

10,000

Cycles

DC Characteristic Over Recommended Operating Conditions

Symbol

VOH

VOL

Min

Max

Units

Output high voltage for 5V outputs

Parameter

IOH = 4.0 mA, VCC = Min

Test Conditions

2.4

Output high voltage for 3.3V outputs

IOH = 3.2 mA, VCC = Min

2.4

Output low voltage for 5V outputs

IOL = 24 mA, VCC = Min

0.5

Output low voltage for 3.3V outputs

IOL = 10 mA, VCC = Min

0.4

IIL

Input leakage current

VCC = Max

VIN = GND or VCC

10

IIH

I/O high-Z leakage current

VCC = Max

VIN = GND or VCC

10

CIN

I/O capacitance

VIN = GND

f = 1.0 MHz

10

pF

ICC

Operating supply current

(low power mode, active)

VI = GND, No load

f = 1.0 MHz

30 (Typical)

DS064 (v7.0) May 17, 2013

Product Specification

www.xilinx.com

mA

PRODUCT OBSOLETE / UNDER OBSOLESCENCE

R

XC9536 In-System Programmable CPLD

AC Characteristics

Symbol

Parameter

XC9536-5

XC9536-6

XC9536-7

XC9536-10 XC9536-15

Min

Max

Min

Max

Min

Max

Min

Max

Min

5.0

6.0

7.5

10.0

15.0

ns

3.5

3.5

4.5

6.0

8.0

ns

Max Units

TPD

I/O to output valid

TSU

I/O setup time before GCK

TH

I/O hold time after GCK

ns

GCK to output valid

4.0

4.0

4.5

6.0

8.0

ns

100.0

100.0

125.0

111.1

95.2

MHz

100.0

100.0

83.3

66.7

55.6

MHz

TCO

fCNT(1)

16-bit counter frequency

fSYSTEM(2) Multiple FB internal operating

frequency

TPSU

I/O setup time before p-term

clock input

0.5

0.5

0.5

2.0

4.0

ns

TPH

I/O hold time after p-term clock

input

3.0

3.0

4.0

4.0

4.0

ns

P-term clock output valid

7.0

7.0

8.5

10.0

12.0

ns

TOE

GTS to output valid

5.0

5.0

5.5

6.0

11.0

ns

TOD

GTS to output disable

5.0

5.0

5.5

6.0

11.0

ns

TPOE

Product term OE to output

enabled

9.0

9.0

9.5

10.0

14.0

ns

TPOD

Product term OE to output

disabled

9.0

9.0

9.5

10.0

14.0

ns

TWLH

GCK pulse width (High or Low)

4.0

4.0

4.0

4.5

5.5

ns

Asynchronous preset/reset

pulse width (High or Low)

7.0

7.0

7.0

7.5

8.0

ns

TPCO

TAPRPW

Notes:

1. fCNT is the fastest 16-bit counter frequency available, using the local feedback when applicable.

fCNT is also the Export Control Maximum flip-flop toggle rate, fTOG.

2. fSYSTEM is the internal operating frequency for general purpose system designs spanning multiple FBs.

VTEST

R1

Output Type

VCCIO

VTEST

R1

5.0V

5.0V

3.3V

3.3V

Device Output

R2

R2

CL

160

120

35 pF

260

360

35 pF

CL

DS067_03_110101

Figure 3: AC Load Circuit

www.xilinx.com

DS064 (v7.0) May 17, 2013

Product Specification

PRODUCT OBSOLETE / UNDER OBSOLESCENCE

R

XC9536 In-System Programmable CPLD

Internal Timing Parameters

Symbol

Parameter

XC9536-5

XC9536-6

XC9536-7 XC9536-10 XC9536-15

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max Units

Buffer Delays

TIN

Input buffer delay

1.5

1.5

2.5

3.5

4.5

ns

TGCK

GCK buffer delay

1.5

1.5

1.5

2.5

3.0

ns

TGSR

GSR buffer delay

4.0

4.0

4.5

6.0

7.5

ns

TGTS

GTS buffer delay

5.0

5.0

5.5

6.0

11.0

ns

TOUT

Output buffer delay

2.0

2.0

2.5

3.0

4.5

ns

TEN

Output buffer enable/disable delay

ns

Product Term Control Delays

TPTCK

Product term clock delay

3.0

3.0

3.0

3.0

2.5

ns

TPTSR

Product term set/reset delay

1.0

1.0

2.0

2.5

3.0

ns

TPTTS

Product term 3-state delay

5.5

5.5

4.5

3.5

5.0

ns

0.5

0.5

0.5

1.0

3.0

ns

Internal Register and Combinatorial Delays

TPDI

Combinatorial logic propagation delay

TSUI

Register setup time

2.5

2.5

1.5

2.5

3.5

ns

THI

Register hold time

1.0

1.0

3.0

3.5

4.5

ns

TCOI

Register clock to output valid time

0.5

0.5

0.5

0.5

0.5

ns

TAOI

Register async. S/R to output delay

6.0

6.0

6.5

7.0

8.0

ns

TRAI

Register async. S/R recover before

clock

5.0

5.0

7.5

10.0

10.0

ns

TLOGI

Internal logic delay

1.0

1.0

2.0

2.5

3.0

ns

TLOGILP Internal low power logic delay

9.0

9.0

10.0

11.0

11.5

ns

6.0

6.0

8.0

9.5

11.0

ns

TPTA(1) Incremental product term allocator

delay

0.8

0.8

1.0

1.0

1.0

ns

TSLEW

3.5

3.5

4.0

4.5

5.0

ns

Feedback Delays

TF

FastCONNECT feedback delay

Time Adders

Slew-rate limited delay

Notes:

1. TPTA is multiplied by the span of the function as defined in the XC9500 family data sheet.

DS064 (v7.0) May 17, 2013

Product Specification

www.xilinx.com

PRODUCT OBSOLETE / UNDER OBSOLESCENCE

R

XC9536 In-System Programmable CPLD

XC9536 I/O Pins

Function

BSca

n

Function

BSca

n

Block

Macroce

ll

PC44

VQ44

CS48

Order

Block

Macroce

ll

PC44

VQ44

CS48

Order

40

D6

105

39

D7

51

41

C7

102

44

38

E5

48

5[1]

43[1]

B7[1]

99

42[1]

36[1]

E6[1]

45

42

C6

96

43

37

E7

42

6[1]

44[1]

B6[1]

93

40[1]

34[1]

F6[1]

39

33[1]

G7[1]

36

A6

90

39[1]

7[1]

1[1]

A7[1]

87

38

32

G6

33

C5

84

37

31

F5

30

11

B5

81

36

30

G5

27

10

12

A4

78

10

35

29

F4

24

11

13

B4

75

11

34

28

G4

21

12

14

A3

72

12

33

27

E3

18

13

18

12

B2

69

13

29

23

F2

15

14

19

13

B1

66

14

28

22

G1

12

15

20

14

C2

63

15

27

21

F1

16

22

16

C3

60

16

26

20

E2

17

24

18

D2

57

17

25

19

E1

18

54

18

Notes: :

1. Global control pin.

XC9536 Global, JTAG and Power Pins

Pin Type

PC44

VQ44

CS48

I/O/GCK1

43

B7

I/O/GCK2

44

B6

I/O/GCK3

A7

I/O/GTS1

42

36

E6

I/O/GTS2

40

34

F6

I/O/GSR

39

33

G7

TCK

17

11

A1

TDI

15

B3

TDO

30

24

G2

TMS

16

10

A2

VCCINT 5V

21, 41

15, 35

C1,F7

VCCIO 3.3V/5V

32

26

G3

GND

23, 10, 31

17, 4, 25

A5, D1, F3

No Connects

C4, D3, D4, E4

www.xilinx.com

DS064 (v7.0) May 17, 2013

Product Specification

PRODUCT OBSOLETE / UNDER OBSOLESCENCE

R

XC9536 In-System Programmable CPLD

Device Part Marking and Ordering Combination Information

XC95xxx

TQ144

Device Type

Package

This line not

related to device

part number

7C

Speed

Operating Range

Sample package with part marking.

Notes:

1. Due to the small size of chip scale packages, part marking on these packages does not follow the above

sample and the complete part number cannot be included in the marking. Part marking on chip scale

packages by line:

Line 1 = X (Xilinx logo), then truncated part number (no XC), i.e., 95xxx.

Line 2 = Not related to device part number.

Line 3 = Not related to device part number.

Line 4 = Package code, speed, operating temperature, three digits not related to device

part number. Package code: C1 = CS48.

Device Ordering and

Part Marking Number

XC9536-5PC44C

XC9536-5PCG44C

XC9536-5VQ44C

XC9536-5VQG44C

XC9536-5CS48C

XC9536-5CSG48C

XC9536-6PC44C

XC9536-6PCG44C

XC9536-6VQ44C

XC9536-6VQG44C

XC9536-7PC44C

XC9536-7PCG44C

XC9536-7VQ44C

XC9536-7VQG44C

XC9536-7CS48C

XC9536-7CSG48C

XC9536-7PC44I

XC9536-7PCG44I

XC9536-7VQ44I

XC9536-7VQG44I

XC9536-10PC44C

XC9536-10PCG44C

XC9536-10VQ44C

DS064 (v7.0) May 17, 2013

Product Specification

Speed

(pin-to-pin

delay)

5 ns

5 ns

5 ns

5 ns

5 ns

5 ns

6 ns

6 ns

6 ns

6 ns

7.5 ns

7.5 ns

7.5 ns

7.5 ns

7.5 ns

7.5 ns

7.5 ns

7.5 ns

7.5 ns

7.5 ns

10 ns

10 ns

10 ns

Pkg.

Symbol

PC44

PCG44

VQ44

VQG44

CS48

CSG48

PC44

PCG44

VQ44

VQG44

PC44

PCG44

VQ44

VQG44

CS48

CSG48

PC44

PCG44

VQ44

VQG44

PC44

PCG44

VQ44

No. of

Pins

44-pin

44-pin

44-pin

44-pin

48-ball

48-ball

44-pin

44-pin

44-pin

44-pin

44-pin

44-pin

44-pin

44-pin

48-ball

48-ball

44-pin

44-pin

44-pin

44-pin

44-pin

44-pin

44-pin

Package Type

Plastic Lead Chip Carrier (PLCC)

Plastic Lead Chip Carrier (PLCC); Pb-Free

Very Thin Quad Flat Pack (VQFP)

Very Thin Quad Flat Pack (VQFP); Pb-Free

Chip Scale Package (CSP)

Chip Scale Package (CSP); Pb-Free

Plastic Lead Chip Carrier (PLCC)

Plastic Lead Chip Carrier (PLCC); Pb-Free

Very Thin Quad Flat Pack (VQFP)

Very Thin Quad Flat Pack (VQFP); Pb-Free

Plastic Lead Chip Carrier (PLCC)

Plastic Lead Chip Carrier (PLCC); Pb-Free

Very Thin Quad Flat Pack (VQFP)

Very Thin Quad Flat Pack (VQFP); Pb-Free

Chip Scale Package (CSP)

Chip Scale Package (CSP); Pb-Free

Plastic Lead Chip Carrier (PLCC)

Plastic Lead Chip Carrier (PLCC); Pb-Free

Very Thin Quad Flat Pack (VQFP)

Very Thin Quad Flat Pack (VQFP); Pb-Free

Plastic Lead Chip Carrier (PLCC)

Plastic Lead Chip Carrier (PLCC); Pb-Free

Very Thin Quad Flat Pack (VQFP)

www.xilinx.com

Operating

Range(1)

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

I

I

I

I

C

C

C

7

PRODUCT OBSOLETE / UNDER OBSOLESCENCE

R

XC9536 In-System Programmable CPLD

Device Ordering and

Part Marking Number

XC9536-10VQG44C

XC9536-10CS48C

XC9536-10CSG48C

XC9536-10PC44I

XC9536-10PCG44I

XC9536-10VQ44I

XC9536-10VQG44I

XC9536-10CS48I

XC9536-10CSG48I

XC9536-15PC44C

XC9536-15PCG44C

XC9536-15VQ44C

XC9536-15VQG44C

XC9536-15PC44I

XC9536-15PCG44I

XC9536-15VQ44I

XC9536-15VQG44I

Speed

(pin-to-pin

delay)

10 ns

10 ns

10 ns

10 ns

10 ns

10 ns

10 ns

10 ns

10 ns

15 ns

15 ns

15 ns

15 ns

15 ns

15 ns

15 ns

15 ns

Pkg.

Symbol

VQG44

CS48

CSG48

PC44

PCG44

VQ44

VQG44

CS48

CSG48

PC44

PCG44

VQ44

VQG44

PC44

PCG44

VQ44

VQG44

No. of

Pins

44-pin

48-ball

48-ball

44-pin

44-pin

44-pin

44-pin

48-ball

48-ball

44-pin

44-pin

44-pin

44-pin

44-pin

44-pin

44-pin

44-pin

Package Type

Very Thin Quad Flat Pack (VQFP); Pb-Free

Chip Scale Package (CSP)

Chip Scale Package (CSP); Pb-Free

Plastic Lead Chip Carrier (PLCC)

Plastic Lead Chip Carrier (PLCC); Pb-Free

Very Thin Quad Flat Pack (VQFP)

Very Thin Quad Flat Pack (VQFP); Pb-Free

Chip Scale Package (CSP)

Chip Scale Package (CSP); Pb-Free

Plastic Lead Chip Carrier (PLCC)

Plastic Lead Chip Carrier (PLCC); Pb-Free

Very Thin Quad Flat Pack (VQFP)

Very Thin Quad Flat Pack (VQFP); Pb-Free

Plastic Lead Chip Carrier (PLCC)

Plastic Lead Chip Carrier (PLCC); Pb-Free

Very Thin Quad Flat Pack (VQFP)

Very Thin Quad Flat Pack (VQFP); Pb-Free

Operating

Range(1)

C

C

C

I

I

I

I

I

I

C

C

C

C

I

I

I

I

Notes:

1. C = Commercial: TA = 0 to +70C; I = Industrial: TA = 40 to +85C.

Warranty Disclaimer

THESE PRODUCTS ARE SUBJECT TO THE TERMS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED

AT http://www.xilinx.com/warranty.htm. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF THE

PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED ON THE

THEN-CURRENT XILINX DATA SHEET FOR THE PRODUCTS. PRODUCTS ARE NOT DESIGNED TO BE FAIL-SAFE

AND ARE NOT WARRANTED FOR USE IN APPLICATIONS THAT POSE A RISK OF PHYSICAL HARM OR LOSS OF

LIFE. USE OF PRODUCTS IN SUCH APPLICATIONS IS FULLY AT THE RISK OF CUSTOMER SUBJECT TO

APPLICABLE LAWS AND REGULATIONS.

Revision History

The following table shows the revision history for this document.

Date

Version

Revision

12/04/1998

5.0

Revised data sheet to remove PCI compliancy statement and remove TLF.

06/18/2003

6.0

Updated format.

08/21/2003

6.1

Updated Package Device Marking Pin 1 orientation.

04/15/2005

6.2

Added Asynchronous Preset Reset Pulse Width Specification (TAPRPW)

04/03/2006

6.3

Added Warranty Disclaimer. Added Pb-Free package ordering information.

05/17/2013

7.0

The products listed in this data sheet are obsolete. See XCN11010 for further information.

www.xilinx.com

DS064 (v7.0) May 17, 2013

Product Specification

Potrebbero piacerti anche

- Cummins ISX Engine Error Codes. ISM, QSM - Truck PDFDocumento35 pagineCummins ISX Engine Error Codes. ISM, QSM - Truck PDFAvs ElectronNessuna valutazione finora

- OBDII365 Technical Blog-Obdii365.Com - Free Download Cummins Insite 8.5.2 With KeygenDocumento9 pagineOBDII365 Technical Blog-Obdii365.Com - Free Download Cummins Insite 8.5.2 With KeygenAvs Electron33% (3)

- HSPY ProgrammingDocumento7 pagineHSPY ProgrammingAvs ElectronNessuna valutazione finora

- MMCX Microminiature RF Connectors - Molex - DigiKeyDocumento3 pagineMMCX Microminiature RF Connectors - Molex - DigiKeyAvs ElectronNessuna valutazione finora

- N2768A - KEYSIGHT TECHNOLOGIES - Test Accessory, Vertical Mini Probe Socket, Keysight Infiniium Series OscilloscopesDocumento1 paginaN2768A - KEYSIGHT TECHNOLOGIES - Test Accessory, Vertical Mini Probe Socket, Keysight Infiniium Series OscilloscopesAvs ElectronNessuna valutazione finora

- Multiplexing Troubleshooting: Service Bulletin Number: 4021378 Released Date: 25-Apr-2011 Multiplexing TroubleshootingDocumento8 pagineMultiplexing Troubleshooting: Service Bulletin Number: 4021378 Released Date: 25-Apr-2011 Multiplexing TroubleshootingAvs Electron100% (1)

- FAULT CODE 4176 - Aftertreatment Selective Catalyst Reduction Air Assist Valve - Voltage Above Normal or Shorted To High SourceDocumento7 pagineFAULT CODE 4176 - Aftertreatment Selective Catalyst Reduction Air Assist Valve - Voltage Above Normal or Shorted To High SourceAvs ElectronNessuna valutazione finora

- Cal Test Electronics: Revisions Descriptions RevDocumento1 paginaCal Test Electronics: Revisions Descriptions RevAvs ElectronNessuna valutazione finora

- SCR Air Assisted SystemEnglish VersionDocumento17 pagineSCR Air Assisted SystemEnglish VersionAvs ElectronNessuna valutazione finora

- The Pb-Free Bgas in SNPB Assembly Process Project (The BackwardDocumento26 pagineThe Pb-Free Bgas in SNPB Assembly Process Project (The BackwardAvs ElectronNessuna valutazione finora

- Bga Reballing SmtaDocumento18 pagineBga Reballing SmtaAvs ElectronNessuna valutazione finora

- Oscilloscope Probes and Probe AccessoriesDocumento56 pagineOscilloscope Probes and Probe AccessoriesAvs ElectronNessuna valutazione finora

- Infiniium Oscilloscope Probes and Accessories: Keysight TechnologiesDocumento59 pagineInfiniium Oscilloscope Probes and Accessories: Keysight TechnologiesAvs ElectronNessuna valutazione finora

- Molex - Connectors, Interconnects - DigiKeyDocumento3 pagineMolex - Connectors, Interconnects - DigiKeyAvs ElectronNessuna valutazione finora

- Passive probe accessoriesDocumento1 paginaPassive probe accessoriesAvs ElectronNessuna valutazione finora

- Esys Flasher User's ManualDocumento8 pagineEsys Flasher User's ManualThiago Techscan Henrique TechscanNessuna valutazione finora

- Molex - Connectors, Interconnects - DigiKeyDocumento3 pagineMolex - Connectors, Interconnects - DigiKeyAvs ElectronNessuna valutazione finora

- TEKTRONIX - Test Accessory, BNC To Probe Tip AdapterDocumento1 paginaTEKTRONIX - Test Accessory, BNC To Probe Tip AdapterAvs ElectronNessuna valutazione finora

- Usb Multilink Universal Rev C Fact SheetDocumento1 paginaUsb Multilink Universal Rev C Fact SheetEduardo FernandezNessuna valutazione finora

- Probe Tip To BNC Adapter Thread Locking: Part Number DescriptionDocumento1 paginaProbe Tip To BNC Adapter Thread Locking: Part Number DescriptionAvs ElectronNessuna valutazione finora

- Passive Voltage Probes: TPP1000 TPP0500B TPP0502 TPP0250 DatasheetDocumento4 paginePassive Voltage Probes: TPP1000 TPP0500B TPP0502 TPP0250 DatasheetAvs ElectronNessuna valutazione finora

- TEKTRONIX - Test Accessory, BNC AdapterDocumento1 paginaTEKTRONIX - Test Accessory, BNC AdapterAvs ElectronNessuna valutazione finora

- Oscilloscope Probe: BNC AdapterDocumento1 paginaOscilloscope Probe: BNC AdapterAvs ElectronNessuna valutazione finora

- Definitions and Properties of Soft FerritesDocumento13 pagineDefinitions and Properties of Soft FerritesAvs ElectronNessuna valutazione finora

- Probe AccessoriesDocumento1 paginaProbe AccessoriesAvs ElectronNessuna valutazione finora

- MCP 2200Documento44 pagineMCP 2200Anonymous XZrfuyWNessuna valutazione finora

- PE4576 - Technical Summary For Multilink Universal and Multilink Universal FXDocumento5 paginePE4576 - Technical Summary For Multilink Universal and Multilink Universal FXAvs ElectronNessuna valutazione finora

- MCP2200 Breakout Module User's Guide: 2012 Microchip Technology Inc. DS52064ADocumento24 pagineMCP2200 Breakout Module User's Guide: 2012 Microchip Technology Inc. DS52064AAvs ElectronNessuna valutazione finora

- Infrared CO2 Sensor Module (Model: MH-Z19B) : User's ManualDocumento9 pagineInfrared CO2 Sensor Module (Model: MH-Z19B) : User's ManualAvs ElectronNessuna valutazione finora

- Xensiv Pas Co2: DescriptionDocumento19 pagineXensiv Pas Co2: DescriptionAvs ElectronNessuna valutazione finora

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Arc Flash and Electrical Safety HazardsDocumento24 pagineArc Flash and Electrical Safety HazardsJulios Charl Panuncialman TagupaNessuna valutazione finora

- Aoc Le32w136 TVDocumento82 pagineAoc Le32w136 TVMarcos Jara100% (4)

- Propeller Pin Crack InspectionDocumento4 paginePropeller Pin Crack InspectionNicolás PiratovaNessuna valutazione finora

- Aranya Housing Final To Be Submitted PDFDocumento37 pagineAranya Housing Final To Be Submitted PDFsucheta100% (4)

- Fuel Pressure Regulator - Remove and InstallDocumento3 pagineFuel Pressure Regulator - Remove and InstallGerardo VelazquezNessuna valutazione finora

- Notification ACF One Range Officer RajasthanDocumento2 pagineNotification ACF One Range Officer RajasthanAshok SainiNessuna valutazione finora

- Racecar Engineering 2013 05 PDFDocumento100 pagineRacecar Engineering 2013 05 PDFfreddyonnimiNessuna valutazione finora

- HypergraphDB: A Graph-Oriented DatabaseDocumento20 pagineHypergraphDB: A Graph-Oriented DatabaseandresNessuna valutazione finora

- Management GurusDocumento44 pagineManagement GurusRouben ParmanumNessuna valutazione finora

- Indoor Multi-Wall Path Loss Model at 1.93 GHZDocumento6 pagineIndoor Multi-Wall Path Loss Model at 1.93 GHZadonniniNessuna valutazione finora

- Jsa-Wif-9 Pulling CableDocumento12 pagineJsa-Wif-9 Pulling CableY a n i. A h m e dNessuna valutazione finora

- FRP Pipe BrochureDocumento8 pagineFRP Pipe BrochurecrisjhairNessuna valutazione finora

- Laboratory Design Capacitive Displacement SensorDocumento10 pagineLaboratory Design Capacitive Displacement SensorElizabethNessuna valutazione finora

- SantuDocumento1 paginaSantuSantu sevenNessuna valutazione finora

- Resume Hemant ChaurasiaDocumento3 pagineResume Hemant Chaurasiachaurasia_hNessuna valutazione finora

- Dynamic Architecture Journal ArticleDocumento11 pagineDynamic Architecture Journal Articlesakshi soniNessuna valutazione finora

- Design & Fabrication of a Solar-Assisted Air DehumidifierDocumento17 pagineDesign & Fabrication of a Solar-Assisted Air DehumidifierSree NairNessuna valutazione finora

- Industrial Sliding DoorsDocumento40 pagineIndustrial Sliding DoorsAnonymous CPEha1db7UNessuna valutazione finora

- ME301 Mechanics of MachineryDocumento2 pagineME301 Mechanics of MachineryVishnu Mohan M SNessuna valutazione finora

- Quiz 12Documento3 pagineQuiz 12mwende faiyuuNessuna valutazione finora

- Instruction Manual - Digital Drybath - ENDocumento19 pagineInstruction Manual - Digital Drybath - ENAlain ManceraNessuna valutazione finora

- ch19 Validation VerificationDocumento43 paginech19 Validation VerificationKarthikeya HsNessuna valutazione finora

- AIR SAFETY PROCEDURES MANUAL - IndiaDocumento141 pagineAIR SAFETY PROCEDURES MANUAL - IndiaRichard R M Thodé100% (1)

- Iso Noremark 2 PDFDocumento86 pagineIso Noremark 2 PDFAkhmad MakhrusNessuna valutazione finora

- Bill of Quantities: Fifteen-Classrooms ADocumento1 paginaBill of Quantities: Fifteen-Classrooms AFritz NatividadNessuna valutazione finora

- Planning of Electrical NetworksDocumento32 paginePlanning of Electrical NetworksSerge RINAUDONessuna valutazione finora

- Eee MCQDocumento39 pagineEee MCQRoshnal BluestacksNessuna valutazione finora

- Masterful WiiFlow v4.2.3 Pack with Numerous UpdatesDocumento4 pagineMasterful WiiFlow v4.2.3 Pack with Numerous UpdatesYulianNessuna valutazione finora

- API 6D Valves Bonney Forge PDFDocumento12 pagineAPI 6D Valves Bonney Forge PDFSQUALO_122Nessuna valutazione finora

- Denison Hydraulics Goldcup Digital Hi-Iq Control: Electronic Control Card User Manual Software Version 2.2BDocumento62 pagineDenison Hydraulics Goldcup Digital Hi-Iq Control: Electronic Control Card User Manual Software Version 2.2BHassan Haghighi TajvarNessuna valutazione finora