Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Convertidor A D

Caricato da

Marcos DMTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Convertidor A D

Caricato da

Marcos DMCopyright:

Formati disponibili

MEDICIONES ELCTRICAS.

TIPOS DE CONVERTIDORES A/D

CONTENIDO

1.

Introduccin............................................................................................................................... 3

2.

Conceptos principales ............................................................................................................... 4

3.

2.1

Seales analgicas ............................................................................................................. 4

2.2

Seales digitales ................................................................................................................. 4

2.3

Teorema de muestreo ........................................................................................................ 5

2.4

Multiplexacin y Demultiplexacin ................................................................................. 7

2.5

Cuantificacin y Codificacin .......................................................................................... 8

2.5.1

Error de cuantificacin. ............................................................................................ 9

2.5.2

Codificacin de la seal cuantificada..................................................................... 10

Convertidor Analgico/Digital (ADC) ................................................................................... 10

3.1

Ventajas e inconvenientes de la conversin analgico digital. .................................... 11

3.2

Tipos de convertidores. ................................................................................................... 12

3.2.1

3.2.1.1

Resolucin y exactitud A/D..... 14

3.2.1.2

Tiempo de conversin........14

3.2.2

Convertidor A/D de Rastreo o Seguimiento.......................................................... 14

3.2.3

Convertido A/D de Aproximaciones Sucesivas. .................................................... 16

3.2.3.1

5.

Tiempo de conversin de A/D de Aproximaciones sucesivas. 18

3.2.4

Convertidor A/D con Comparador en Paralelo.................................................... 18

3.2.5

Convertidor Sigma-Delta. ....................................................................................... 20

3.2.6

Convertidores A/D con Integrador. ....................................................................... 21

3.2.6.1

Convertidor A/D de Rampa nica. .21

3.2.6.2

Convertidor A/D de Doble Rampa. .........22

3.2.7

4.

Convertidor A/D en Escalera. ................................................................................ 12

Convertidor A/D Tensin Frecuencia.................................................................... 24

Aplicaciones de los convertidores A/D................................................................................... 25

4.1

Voltmetro digital. ........................................................................................................... 25

4.2

Medicin de Resistencia, Corriente. .............................................................................. 28

4.3

Mediciones de Tensiones en CA ..................................................................................... 28

Bibliografa .............................................................................................................................. 31

Daz Moreno Marcos 7EM3

2|Pgina

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

1. Introduccin

Muchos equipos y dispositivos modernos requieren procesar las seales analgicas que

reciben y convertirlas en seales digitales para poder funcionar.

La mayor parte de informacin generada en el mundo fsico tiene un marcado carcter

analgico. Esto significa que la informacin experimenta una variacin continua, entre

ciertos lmites, a lo largo del tiempo. Por supuesto que tambin existen informaciones de

carcter digital, (todo-nada), si bien es cierto que su nmero es bastante inferior a las

informaciones analgicas.

Dada la gran sencillez tecnolgica que supone el tratamiento automtico de la informacin

digital, as como las numerosas mquinas que han surgido recientemente con dicho fin, en

muchos casos es necesario transformar la informacin analgica en otra equivalente de

carcter digital. Los sistemas que llevan a cabo esta transformacin se llaman convertidores

analgicos-digitales (A/D).

El resultado del procesamiento digital de la informacin est constituida por seales de

carcter digital, que en muchas ocasiones debern actuar y controlar cargas o actuadores

analgicos. Los sistemas encargados del cambio de la informacin digital a analgica se

denominan convertidores digitales-analgicos (D/A).

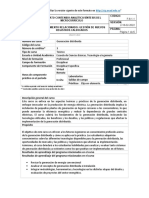

En la siguiente figura se muestra el esquema bsico del control automtico de un sistema

real. En l se puede comprobar el posicionamiento de los dos eslabones de la cadena en los

que la seal o informacin se convierte en digital y viceversa.

Figura 1. Esquema bsico de control automtico.

Daz Moreno Marcos 7EM3

3|Pgina

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

En la conversin ADC se han desarrollado y empleado muchos mtodos. Hoy en da muchos

de estos mtodos, estn disponibles como circuitos integrados en un chips o formando parte

de un sistema ms complejo, por ejemplo, un microcontrolador.

2. Conceptos principales

Para comprender la teora y mtodos que se emplean en la conversin analgica a digital,

debemos previamente conocer los principios del teorema del muestreo, el multiplexado y

demultiplexado en el tiempo, la cuantificacin, la codificacin de seales y las seales,

temas que abordaremos de manera simplificada.

2.1 Seales analgicas

Son variables elctricas que evolucionan en el tiempo en forma anloga a alguna variable

fsica. Estas variables pueden presentarse en la forma de una corriente, una tensin o una

carga elctrica. Varan en forma continua entre un lmite inferior y un lmite superior. En la

figura 2 se puede observar un ejemplo de seal analgica.

Figura 2. Ejemplo de una seal analgica.

En la figura 2 se muestra un ejemplo de seal analgica. sta corresponde a la evolucin de

la temperatura en un tiempo de 50 minutos medida por un sensor de temperatura.

2.2 Seales digitales

Son variables elctricas con dos niveles bien diferenciados que se alternan en el tiempo

transmitiendo informacin segn un cdigo previamente acordado. Cada nivel elctrico

representa uno de dos smbolos: 0 1. Los niveles especficos dependen del tipo de

dispositivos utilizado. Por ejemplo, si se emplean componentes de la familia lgica TTL

Daz Moreno Marcos 7EM3

4|Pgina

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

(transistor-transistor-logic) los niveles son 0 V y 5 V, aunque cualquier valor por debajo de

0,8 V es correctamente interpretado como un 0 y cualquier valor por encima de 2 V es

interpretado como un 1. En la figura 3 se muestra un ejemplo de seal digital.

Figura 3. Ejemplo de una seal digital.

2.3 Teorema de muestreo

Este teorema lo enunciaremos de la siguiente forma, sin demostrarlo: Si una seal continua,

S (t), en su anlisis espectral, tiene una banda de frecuencias tal que fm sea la mayor

frecuencia dentro de esa banda, la seal S(t) podr ser reconstruida sin distorsin, a partir de

muestras tomadas a una frecuencia fs, siendo fs 2. fm.

En la prxima figura, mostramos un esquema simplificado del proceso de muestreo de una

seal analgica o continua:

Figura 4. Esquema simplificado del proceso de muestreo.

Es evidente que este esquema es simplificado, y que el interruptor no ser de tipo

mecnico. En esta otra figura se observa las formas de las tres seales

principales S(t), seal a muestrear, d, seal muestreadora y S d(t) que ser la

muestreada.

Daz Moreno Marcos 7EM3

5|Pgina

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Figura 4. Seal muestreada.

Desde el punto de vista de la cuantificacin de la seal muestreada, lo ideal sera que el

tiempo en que el interruptor est cerrado, fuese prcticamente cero, ya que la seal

muestreada puede variar en dicho tiempo y hacer imprecisa su cuantificacin.

En la figura anterior vemos que S(t) es la seal analgica que se va a muestrear y est

compuesta por una suma de seales (armnicas) de varias frecuencias, siendo fm la

frecuencia mayor. d es la seal que acta sobre el interruptor electrnico y fija el muestreo

de la seal S(t) con una frecuencia fs(periodo Ts); el tiempo de muestreo vale . A la

salida del circuito de muestreo (interruptor) tenemos la seal muestreada que la

denominamos Sd(t). Esta ltima seal, en su anlisis espectral, se demuestra que sta

compuesta por una suma de varias seales de distintas frecuencias. Del conjunto de esas

frecuencias estarn las frecuencias originales de la seal a muestrear S(t) ms seales que

tienen frecuencias diferentes.

Ahora bien, si quisiramos reconstruir la seal original S(t) de la seal muestreada Sd(t),

podemos hacerlo empleando un filtro pasa bajo, que solamente deje pasar las frecuencias

originales, hasta su valor mximo fm, y rechace todas las frecuencias superior a este valor.

La funcin de transferencia del filtro, tendr que ser como muestra la siguiente figura:

Daz Moreno Marcos 7EM3

6|Pgina

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Figura 5. Empleando un filtro pasa bajo.

La respuesta del filtro debe ser plana hasta una frecuencia, como mnimo igual a fm, para caer

posteriormente de forma brusca a cero, antes de que la frecuencia alcance el valor de fs-fm.

2.4 Multiplexacin y Demultiplexacin

Mediante la aplicacin del teorema del muestreo, se pueden transmitir varias seales en el

tiempo por un mismo canal de comunicacin (canal de radiofrecuencia digital, dos

conductores elctricos, fibra ptica). Para lograrlo, es necesario muestrear varias seales

sucesivamente S1 S2.Sn y las seales muestreadas S1, S2..Sn, se las envan por el

canal de comunicacin, intercaladas en el tiempo. A este sistema de comunicacin, se le

denomina multiplexacin en el tiempo. Al otro extremo del canal, se deben separar las

distintas seales muestreadas, que fueron enviadas, proceso denominado

demultiplexacin, para luego pasarlas por un filtro pasa bajo y reconstruir las seales

originales.

La siguiente figura, nos muestra, en forma simplificada, el proceso de la multiplexacin y

demultiplexacin de seales elctricas:

Figura 6. Multiplexado y demultiplexado.

Daz Moreno Marcos 7EM3

7|Pgina

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

2.5 Cuantificacin y Codificacin

La cuantificacin de una seal consiste en la conversin de la seal, que puede tomar

cualquier valor dentro de un intervalo, en otras cuyos valores son discretos, o sea, vara a

incrementos fijos. Esto quiere decir, se asigna un mismo valor a todas las seales cuyas

magnitudes encuentre comprendida dentro de un intervalo, que constituye el escaln de

cuantificacin. Como sea que en todo proceso de cuantificacin existe una aproximacin,

tambin existir un error.

Esto debe ser as, dado que en el procedimiento de codificacin, tenemos que limitar los

niveles de tensin de la seal, dada la cantidad limitada de cdigos (estos cdigos dependern

de la cantidad de bits que se utilice).

En la prctica para cuantificar una seal, son necesarios dos procedimientos: El primero

consiste en muestrear la seal continua de la manera que se explic anteriormente,

obtenindose una seal discreta en el tiempo, con variacin continua de magnitud. Luego

esta seal debe mantenerse un cierto tiempo, dado que la cuantificacin lleva un cierto tiempo

realizarla.

El segundo procedimiento consiste en la cuantificacin propiamente dicha seguida de la

codificacin. La codificacin consiste en asignar un cierto cdigo binario, con varios bits, al

valor cuantificado.

Una funcin ideal de transferencia de un cuantificador, puede ser la representada en esta

figura 7, en la cual se debe tener en cuenta las siguientes caractersticas.

Existen unos niveles de decisin (-2,5. -1,5. -0,5. 0,5. 1,5 etc.)

A los valores comprendidos entre dos niveles consecutivos se les asigna un valor

intermedio fijo.

La distancia entre niveles consecutivos de V = cte.

Por ejemplo cuando la seal continua tiene valores de tensin comprendidos entre +1,5 y

+2,5, el cuantificador asigna un valor fijo de tensin de +2 voltios. Entre -3,5 y -2,5 se asigna

el valor -3 voltios y as sucesivamente con los otros valores intervalos de tensin.

Daz Moreno Marcos 7EM3

8|Pgina

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Figura 7. Cuantificacin de una seal.

2.5.1

Error de cuantificacin.

Para el caso donde la diferencia entre niveles de decisin es constante V= cte., el error de

cuantificacin tiene forma de diente de sierra, como lo muestra la figura anterior. El error de

cuantificacin ser tanto mayor, cuanto mayor sea el desnivel de los escalones de

cuantificacin. Por lo tanto para alcanzar un error menor, necesitamos recurrir a un elevado

nmero de niveles, con el consiguiente aumento del nmero de bits del cdigo digital de la

magnitud codificada, con la consiguiente complejidad de los circuitos.

Figura 8. Error de cuantificacin.

Daz Moreno Marcos 7EM3

9|Pgina

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

2.5.2

Codificacin de la seal cuantificada.

La relacin entre el tamao del escaln V, los niveles de cuantificacin p y la tensin

pico a pico de la seal a convertir Vpp, est dada por:

Vpp = V* p

En funcin de los niveles de cuantificacin, depender la cantidad de bits de los cdigos que

representan los niveles de tensin de la seal cuantificada. Se deber cumplir lo siguiente:

p 2N siendo N, el nmero de bits del cdigo binario.

Resumiendo, para que una seal analgica pueda ser procesada por un sistema digital, es

necesario que la seal analgica pase por las fases de muestreo, cuantificacin y codificacin.

3. Convertidor Analgico/Digital (ADC)

Los convertidores ADC son dispositivos electrnicos que establecen una relacin biunvoca

entre el valor de la seal a convertir y el cdigo (palabra) digital obtenido. Esta relacin se

obtiene en la mayora de los casos, con la ayuda de una tensin de referencia. Su fundamento

terico, como dijimos, est basado en el teorema del muestreo, la cuantificacin y la

codificacin.

Todo convertidor A/D necesita de una seal de referencia (voltaje o corriente) para su

funcionamiento con la que la entrada analgica es comparada. El cdigo digital de salida

indica que fraccin del voltaje o corriente de referencia es la seal de entrada. As pues, un

ADC puede definirse bsicamente como un divisor (entrada entre referencia) que

proporciona un resultado digital de las operaciones.

El nmero de bits utilizado por el convertidor en los cdigos digitales de salida (N) se define

como su resolucin y determina el nmero de cdigos digitales disponibles (2N) para

representar el rango de valores de entrada. La variacin mnima necesaria en la seal de

entrada que hace variar la salida digital en un solo cdigo se denomina LSB (Less Significant

Bit) y viene dado por la expresin:

LSB = FS / 2N

Dnde FS (Full Scale) representa el rango completo de valores analgicos de entrada y N la

resolucin del convertidor.

La ventaja de tratar seales digitales, es que estas son ms inmunes a ruidos y otras

interferencias que s afectan a las seales analgicas.

Daz Moreno Marcos 7EM3

10 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

3.1 Ventajas e inconvenientes de la conversin analgico digital.

Ventajas:

No introduce ruidos en la transmisin.

Se guarda y procesa mucho ms fcilmente que la analgica.

Posibilita almacenar grandes cantidades de datos en diferentes soportes

Permite detectar y corregir errores con ms facilidad.

Las grabaciones no se deterioran con el paso del tiempo como sucede con las cintas

analgicas.

Permite realizar regrabaciones sucesivas sin que se pierda ninguna generacin y, por

tanto, calidad.

Permite la compresin para reducir la capacidad de almacenamiento.

Facilita la edicin visual de las imgenes y del sonido en un ordenador o computadora

personal, utilizando programas apropiados.

No la afecta las interferencias atmosfricas (esttica) ni de otro tipo cuando se

transmite por va inalmbrica, como ocurre con las transmisiones analgicas.

Desventajas:

Para su transmisin requiere un mayor ancho de banda en comparacin con la

analgica.

La sincronizacin entre los relojes de un transmisor inalmbrico digital y el receptor

requiere que sea precisa, como ocurre con el GPS (Global Positioning System Sistema de Posicionamiento Global).

Las transmisiones de las seales digitales son incompatibles con las instalaciones

existentes para transmisiones analgicas.

Se puede decir que la seal pasa a ser digital a partir del proceso de cuantificacin y

codificacin.

Los parmetros caractersticos que definen los conversores A/D son los siguientes:

Resolucin: La resolucin de un convertidor se define como el nmero de distintos

valores digitales que se corresponden con los distintos valores analgicos de entrada.

Fondo de escala: corresponde con el mnimo valor de tensin de entrada analgica

que puede medir el conversor.

Tiempo de conversin: es el tiempo que tarda el conversor en realizar la conversin.

Rango de entrada: es el rango de tensin analgica de entrada que tolera el conversor.

Daz Moreno Marcos 7EM3

11 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Error de conversin: es el error que se induce en la medida. Al realizar la conversin,

ste error determina la precisin del conversor.

3.2 Tipos de convertidores.

Son pocos los esquemas bsicos utilizados en los convertidores A/D, aunque existen un gran

nmero de variaciones dentro de cada uno a la hora de implementarlos. La eleccin

depender de la aplicacin final del sistema, as por ejemplo en un osciloscopio digital se

necesita una gran velocidad en las conversiones mientras que en un sistema de audio lo

primordial es la resolucin de las mismas.

3.2.1

Convertidor A/D en Escalera.

A este convertidor tambin se le llama A/D de rampa digital o A/D contador. Es el

circuito ms sencillos de los convertidores A/D y consta bsicamente de los elementos

observados en la figura anterior: Reloj y circuito de control, circuito de captura y

mantenimiento (S&H), contador digital binario, conversor D/A, comparador, y circuito de

salida, consistente en basculas de retencin (LATH) y amplificadores adaptadores.

Figura 9. Convertidor A/D en Escalera.

Daz Moreno Marcos 7EM3

12 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

El funcionamiento de este convertidor, es el siguiente:

Cuando el circuito S & H ha muestreado la seal analgica (ordenado por la seal C/M

proveniente del circuito de control), el contador comienza a funcionar contando los impulsos

procedentes del reloj. La salida binaria del contador, es convertida por el DAC en una tensin

elctrica (VA/D) a medida que se va realizando la cuenta. Esta ltima tensin, tiene la forma

de una escalera y resulta proporcional a la cantidad de pulsos contados. A su vez, la tensin

de salida del DAC, es comparada con la tensin muestreada Vo en el comparador. Cuando

ambas tensiones se igualan (y la supera en una cantidad VT) la salida del comparador cambia

de valor (de o pasa a 1), detiene la cuenta del contador y el ultimo valor digital contado se

presenta en la salida completndose la conversin. Luego nuevamente se reinicia el proceso

y as sucesivamente.

Este convertidor presenta dos inconvenientes importantes que son la baja velocidad y el

tiempo de conversin es variable, en funcin del nivel de seal muestreada. El tiempo de

conversin para una determinada tensin de entrada Vi, la podemos determinar de la

siguiente forma:

t/ Tc = Vi / Vf*escala; siendo Tc el tiempo total para fondo de escala

Tc = n mx. que puede contar el contador por periodo de los pulsos reloj = (2N -1)*T

N= n de bits del contador y del cdigo convertido.

El mtodo de rampa en escalera es ms lento que el mtodo flash porque, en caso de entrada

mxima, el contador debe pasar a travs del nmero mximo de estados antes de realizar la

conversin. Para una conversin de 8 bits, esto significa un mximo de 256 estados y cado

estado consume un cierto tiempo La figura 10 ilustra una secuencia de conversin con 4 bits.

Obsrvese que, para cada muestra, el contador debe contar desde cero hasta el escaln en el

que la tensin de referencia alcanza a la tensin de entrada analgica.

Figura 10. Secuencia de conversin de 4 bits.

Daz Moreno Marcos 7EM3

13 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

3.2.1.1 Resolucin y exactitud del convertidor A/D.

Resulta interesante comprender los errores asociados cuando se llevan a cabo mediciones

con instrumentos digitales. Para ello consideraremos los errores en el convertidor de rampa

en escalera. Uno de esos errores se debe a la resolucin del DAC interno que hace que la

tensin a su salida se incremente en escalones hasta que su valor supere a la tensin Vo. Para

mejorarlo, deberamos disminuir la resolucin (escaln), pero siempre existir una diferencia

entre la cantidad real y el valor digital asignado. A esta diferencia, se le denomina error de

cuantificacin o cuantizacin.

Otro error que aparece en los ADC est relacionado est relacionado con la exactitud que

depende de la precisin de los componentes del circuito, como el comparador, las resistencias

de precisin del DAC interno, de los conmutadores de corriente, de las tensiones de

referencia, etc. Una especificacin de estos errores, se dan en relacin a la tensin de fondo

de escala. Por ejemplo una exactitud de 0,01% FS (fondo de escala), indica que la salida

puede tener un error del 0,01% de su tensin ms alta.

En general, el error de cuantificacin y la exactitud, estn dentro del mismo orden de

magnitud.

3.2.1.2 Tiempo de conversin.

Este A/D tiene un tiempo que tarda el circuito en hacer la conversin. Este tiempo depende

del valor de VIN ya que en cada caso habr que recorrer todos los estados desde 0. Si VIN

es alto, habr que recorrer muchos estados. El tiempo mximo cuando el contador recorre

todos los estados es:

=

Donde n es el nmero de bits del contador y la frecuencia del reloj. Por tanto tarda ms

cuanta ms resolucin tenga el contador y menor sea la frecuencia del reloj.

3.2.2

Convertidor A/D de Rastreo o Seguimiento.

Tambin conocido como ADC de rampa en escalera ascendente y descendente. El mtodo

de seguimiento utiliza un contador ascendente / descendente y es ms rpido que el mtodo

de rampa digital, porque el contador no se pone a cero despus de cada muestreo sino que

sigue a la entrada analgica.

En el ADC de rampa en escalera ascendente y descendente, se usa un contador ascendentedescendente para disminuir el tiempo desperdiciado. Este contador cuenta hacia arriba

cuando el comparador indique VA/D < Vo y cuenta hacia abajo, cuando VA/D > Vo. De esta

Daz Moreno Marcos 7EM3

14 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

manera la salida del DAC (VA/D) se modifica hasta que se produce el cruce con Vo donde

detiene la cuenta.

Para un nuevo valor a convertir, ahora el contador no se reestablece a cero sino que parte de

su ltima cuenta, incrementndole o decrementndose, segn sea el nuevo valor de Vo

respecto a VA/D.

De esta manera, el tiempo de conversin en este convertidor, se reduce, respecto al de

escalera ascendente, pero seguir siendo variable, en funcin del valor a convertir. Como la

salida del DAC interno sigue a la entrada Vo, a menudo se le denomina ADC de

seguimiento. La figura 11 muestra un ADC de seguimiento de 8 bits.

Figura 11. ADC tpico de seguimiento de 8 bits.

Este tipo de circuito es el que se utilizara para medir temperatura permanentemente unida a

un panel digital. La salida va variando arriba o abajo segn como sea la lectura.

A fin de reducir el error inicial de las primeras conversiones suele fijarse el contador a media

escala, es decir, en 100000.

Daz Moreno Marcos 7EM3

15 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Figura 12. Grfica de un ADC de seguimiento de 8 bits.

3.2.3

Convertido A/D de Aproximaciones Sucesivas.

En la Figura 13 se muestra el esquema de un convertidor analgico-digital de aproximaciones

sucesivas, uno de los ms utilizados en la actualidad, pues permite una considerable

velocidad de conversin (velocidades de conversin entre medias y altas del orden de algunos

microsegundos a dcimas de microsegundos) y una alta resolucin a un bajo coste. La

estructura cuenta con un registro de aproximaciones sucesivas.

Figura 13. Convertidor A/D de Aproximaciones Sucesivas.

Daz Moreno Marcos 7EM3

16 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Este convertidor ADC, es bastante similar al convertidor en escalera, desde el punto de

vista de su diagrama en bloques, con la diferencia apreciable que se sustituy el contador

digital binario por un circuito denominado de registro de aproximaciones sucesivas.

El proceso de conversin para este tipo de convertidores se basa en la realizacin de

comparaciones sucesivas de manera descendente o ascendente, hasta que se encuentra la

combinacin que iguala la tensin entregada por el D/A y la de entrada.

Como el arranque parte siempre de cero, el registro de aproximaciones sucesivas, comienza

poniendo a 1 el bit de ms peso (MSB), quedando el resto a cero, o sea, forma el valor 100

(para este ejemplo se utilizarn slo tres bits), que corresponde a la mitad de la mxima

excursin de la tensin de entrad. Este valor es transformado a seal analgica, que a su vez

se introduce en el comparador.

Si esta seal es mayor que Vi, el comparador bascula dando lugar a una seal que hace que

el registro vare su contenido, sustituyendo el 1 del bit de ms peso por un 0 y colocando en

el bit de peso inmediatamente inferior un 1, quedando inalterado el resto de los bits (010).

Por el contrario si la seal fuese menor que Vi, el registro no modifica el bit de ms peso

inmediatamente inferior a 1, dejado a 0 el resto de los bits (110).

Tanto en un caso como en otro, se efecta una nueva conversin D/A y luego se modifica el

registro con el mismo criterio. El proceso se repite hasta alcanzar el bit de menos peso (LSB).

En el figura 14, se muestra el diagrama de transiciones para 3 bits donde se indica el proceso

de bsqueda de la combinacin digital. El proceso se repetir n veces, siendo n el nmero de

bits del registro de aproximaciones sucesivas. Por lo tanto el tiempo empleado en la

conversin es independiente del valor de la seal analgica de entrada. El tiempo de

conversin de este tipo de convertidores es mucho menor que el anterior.

Figura 14. Diagrama de transicin para 3 bits.

Daz Moreno Marcos 7EM3

17 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

3.2.3.1 Tiempo de conversin del A/D de Aproximaciones Sucesivas.

Como el proceso de aproximacin se repite en la misma cantidad de pasos, cualquiera sea el

valor de la tensin analgica a convertir, entonces el tiempo de conversin es fijo. El

procesamiento de cada bit toma un ciclo reloj, de modo que el tiempo de conversin total

para N bits, resulta:

tc = N x 1 ciclo reloj

La constancia de ste valor, independiente del valor de Vo, resulta interesante cuando los

datos analgicos estn cambiando a una frecuencia relativamente rpida.

3.2.4

Convertidor A/D con Comparador en Paralelo

Es el ms rpido de los esquemas, tambin llamado instantneo o flash. Est formado

por un conjunto de N comparadores a los cuales se le introducen dos seales simultaneas,

una es la seal analgica ya muestreada y la otra una tensin de referencia distinta para cada

comparador y que se obtiene de una misma tensin de referencia (Vref.), mediante una red

de resistencias conectadas en serie. De esta manera se producen N comparaciones (7 en el

dibujo) simultaneas entre la tensin de entrada y las obtenidas desde la referencia. Las salidas

de dichos comparadores son conectadas a un circuito codificador con prioridad que produce

una salida binaria.

El tiempo de conversin completo, es del orden de los nanosegundos. Dado que la

comparacin es simultnea en todos los comparadores, a diferencia de otros convertidores,

que son secuenciales. El inconveniente principal de este convertidor es su precio dada la gran

cantidad de comparadores necesarios cuando se quiere disminuir la resolucin o escaln a

codificar.

Su principal ventaja de este comparador es su alta velocidad de muestreo que se puede

alcanzar, aunque presenta la desventaja de que se necesitan muchos comparadores para un

ADC de un nmero binario de tamao razonable. La velocidad de muestreo determina la

precisin con la que la secuencia de cdigos digitales representa la entrada analgica del

ADC. Cuando ms muestras se toman en una unidad de tiempo, ms precisa es la seal digital

que representa a la seal analgica.

Daz Moreno Marcos 7EM3

18 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Figura 15. Convertidor A/D con Comparador en Paralelo.

Aqu cabe una pregunta: Con que velocidad se debe muestrear una seal analgica, es decir

cuntas veces por unidad de tiempo es lo mnimo con que se requiere muestrear una seal

analgica? La teora propuesta por Nyquist establece que una seal de entrada variante con

el tiempo puede reproducirse con fidelidad si la velocidad de muestreo es por lo menos dos

veces tan alta como la mayor componente de la frecuencia de la seal.

Daz Moreno Marcos 7EM3

19 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Figura 16. Ilustracin de varios muestreos por ciclo.

3.2.5

Convertidor Sigma-Delta.

Estos convertidores digitalizan la seal con una muy baja resolucin (1-bit) y con un ritmo

de muestreo muy elevado (MHz). Mediante el uso de tcnicas de sobremuestreo y filtros

digitales se pueden obtener resoluciones cercanas a los 20 bits. Este tipo de convertidores

son muy adecuados para conversiones donde la resolucin es un factor muy importante y

donde la frecuencia de las seales no es muy elevada, como puede ser el caso de utilidades

de audio.

En un convertidor sigma-delta la seal analgica de entrada se conecta a un integrador cuya

salida se compara con el voltaje de masa del sistema mediante un comparador. ste ltimo

acta como una ADC de 1-bit generando una salida binaria (+V o V) dependiendo de si la

salida del integrador es positiva o negativa. La salida del comparador pasa a travs de un flipflop tipo D (con una seal de reloj de alta frecuencia) y realimenta otro canal del integrador,

conduciendo a ste en la direccin de los 0V.

Daz Moreno Marcos 7EM3

20 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Figura 17. Convertidor Sigma-Delta.

Si la salida del integrador es positiva, el comparador se satura hacia +V (lo que representa un

1 digital). En el siguiente pulso de reloj este valor se encontrar a la salida del flip-flop y por

tanto siendo la entrada del segundo comparador, el cual tiene como voltaje de referencia un

valor superior a +V. Esto provoca una saturacin positiva del mismo enviando un valor

+V al integrador, tendiendo su salida en direccin negativa. Cuando el voltaje de salida del

integrador toma un valor negativo, el lazo de realimentacin enva una seal de correccin

negativa (-V) al integrador de forma que el mismo es conducido hacia un valor positivo. El

concepto de sigma-delta se puede resumir de la siguiente manera: El primer comparador

establece una diferencia (delta) entre la salida del integrador y 0V. El integrador suma

(sigma) la salida del comparador con la salida analgica de entrada.

3.2.6

Convertidores A/D con Integrador.

Estos convertidores son ms sencillos que los anteriores ya que no utilizan DAC interno. Se

emplean en aquellos casos en que no se requieren gran velocidad, pero en los que es

importante conseguir buena linealidad. Se usan frecuentemente en voltmetros digitales.

Existen dos tipos a saber: el de rampa nica y el de doble rampa.

3.2.6.1 Convertidor A/D de Rampa nica.

Como muestra la figura 18, tiene un integrador, un comparador, un generador de impulsos y

los circuitos de salida. En la puesta en marcha el integrador y el contador son puestos a cero

por el circuito de control. A partir de este momento, el integrador genera una rampa con una

pendiente determinada por los valores de C y R. Simultneamente el contador comienza a

contar los pulsos provenientes del reloj, que pasan por una puerta Y. Para este caso, la salida

Daz Moreno Marcos 7EM3

21 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

del comparador, deber estar en uno lgico (1), para permitir que los pulsos lleguen al

contador. En el comparador se realiza la comparacin entre la seal de entrada (seal

muestreada) y la rampa generada en el integrador. Cuando el nivel de la rampa supera a la

seal de entrada, el comparador bascula colocando un cero lgico en la puerta AND,

deteniendo el paso de pulsos hacia el contador. El valor contado hasta este momento,

corresponde con la salida digital del valor de la tensin de entrada muestreada.

Figura 18. Convertidor A/D de Rampa nica.

El principal problema que presenta este tipo de convertidores es que la salida depende de

muchos factores, como: Vref, R, C y T. Por ello Vref y T deben ser muy estables en el tiempo

para que la conversin sea correcta. Los valores de RC no afectan mucho ya que su

contribucin puede dar errores de ganancia fcilmente subsanables. La dependencia con el

reloj, a travs de T, es ms importante ya que la estabilidad del mismo debe ser siempre la

misma "de por vida". Por ello, esta estructura es muy simple y barata si prescindimos de las

caractersticas extremas que necesitamos para el reloj, esto hace que no se utilice esta

estructura.

3.2.6.2 Convertidor A/D de Doble Rampa.

Este convertidor se ha diseado para resolver los inconvenientes del de rampa nica

(variabilidad de C, R y f). El funcionamiento comienza integrando la seal muestreada de

entrada durante un tiempo T1 fijo para cualquier nivel de tensin. Esto da lugar a una rampa

negativa hasta alcanzar el nivel de tensin - VA1 (- VA2 corresponde para otro nivel de

Daz Moreno Marcos 7EM3

22 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

tensin de entrada). A continuacin se cambia de posicin el conmutador C2 y se pasa a

integrar una tensin negativa de referencia (-Vref.), dando lugar a una rampa positiva, que

comienza desde -VA. El tiempo de integracin de esta rampa, hasta que la tensin se haga

cero, como se observa en la figura 19, depende de la tensin alcanzada cuando se gener la

rampa negativa. Durante este tiempo, el contador cuenta los pulsos provenientes del reloj.

Al pasar la rampa por el nivel cero, detectado por el comparador, termina la cuenta,

tenindose una salida digital, proporcional al nivel de tensin de entrada.

Figura 19. Convertidor A/D de Doble Rampa.

Los convertidores de este tipo son lentos: unas 30-40 conversiones por segundo, es decir de

30-40 ms lo cual permite que el oscilador sea muy sencillo del tipo RC.

Este convertidor es til ya que adems de tener una dependencia baja de la salida con la

entrada, permite conseguir alta resolucin (24 bits o algo ms). Sin embargo esta alta

Daz Moreno Marcos 7EM3

23 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

resolucin puede presentar problemas de deriva offset que se resuelva mediante una tercera

rampa. Su idea bsica es medir la deriva en la primera fase poniendo la entrada a cero y

aadiendo esta deriva mediante un sumador en el resto del circuito. Se aade, por tanto, un

tiempo previo al primero que es un ajuste de cero del A/D.

Otra ventaja de este circuito es el bajo consumo por estar fabricado en tecnologa CMOS.

Son tambin bastante inmunes al ruido sobre todo al de alta frecuencia. Si, por ejemplo, se

quiere convertir una seal continua, si se observa sta detenidamente se ver que no tiene un

nico valor sino que oscila dentro de una banda de valores (tiene ruido).

Con un convertidor de integracin la conversin no es instantnea (del orden de 30 c/s), por

ello al integrar en el tiempo est promediando el valor de la seal. Si el perodo de conversin

es un mltiplo de la seal de ruido, conseguiremos que el valor obtenido coincida con el valor

de la seal constante y por tanto sin ruido, ya que la contribucin de los semiperiodos

positivos del ruido es la misma que la de los semiperiodos negativos.

3.2.7

Convertidor A/D Tensin Frecuencia.

En este tipo de convertidor se realiza una conversin de la seal analgica de entrada a

frecuencia, midindose despus el valor de la misma (antes la convertamos en tiempo). Este

circuito, por tanto, tendr dos partes bien distintas: la primera convierte la seal a frecuencia

y la segunda mide esa frecuencia.

Este convertidor es ms simple porque no necesita un DAC interno. En lugar de este, utiliza

un oscilador lineal controlado por voltaje, denominado tambin VCO, que produce una

frecuencia de salida proporcional a su voltaje de entrada. Para el caso del convertidor A / D,

el voltaje de entrada del VCO es la seal analgica. Esta ltima modifica la frecuencia de

salida del VCO. Esta frecuencia alimenta a un contador que cuenta durante un intervalo de

tiempo fijo. El conteo final resulta proporcional al valor del voltaje analgico.

Una de las aplicaciones principales para este tipo de convertidor es en los entornos

industriales ruidosos donde se deben transmitir seales analgicas de pequea magnitud,

provenientes de los transductores, hacia las computadoras de control. El ruido elctrico puede

afectar de manera adversa las seales analgicas si se transmiten directamente, a travs de

conductores, a las computadoras. Una solucin, es alimentar un VCO con la seal analgica

y transmitir la variacin de esta frecuencia que prcticamente no se ver afectada. La

computadora, por medio de sus circuitos internos y programa correspondiente, contara los

pulsos digitales durante un tiempo fijo y convertir este conteo en el equivalente valor digital

de la seal analgica.

Una de las principales ventajas que presenta este convertidor es que posee una alta capacidad

de aislamiento, debido a que la salida ya es digital y con un optoacoplador, se consigue un

aislamiento completo y total. Por ello, si colocamos a la salida de nuestro conversor tensinfrecuencia un optoacoplador obtendremos un convertidor A/D con aislamiento.

Daz Moreno Marcos 7EM3

24 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

4. Aplicaciones de los convertidores A/D.

Los conversores analgico-digital tienen una gran cantidad de aplicaciones. Estn presentes

en todo tipo de sistemas como pueden ser sistemas de telecomunicaciones, sistemas de

control, medidas, etc.

Tambin tiene aplicaciones en sistemas donde es necesario medir seales analgicas, como

pueden ser sensores de temperatura, proximidad o en sistemas donde hay que realizar el

procesamiento y/o almacenamiento de audio o cualquier otro tipo de informacin. Como

estas seales no pueden ser analizadas directamente por un procesador, es necesaria la

utilizacin de conversores A/D.

La eleccin del convertidor est directamente relacionado con la velocidad a la que cambia

la seal analgica que se quiere modular, es decir, la frecuencia de la misma, por ejemplo,

para muestrear la temperatura no ser necesario el uso de un convertidor con una frecuencia

de muestreo alta ya que la temperatura no vara con rapidez en el tiempo, por otra parte, ser

necesario un conversor de gran rapidez cuando se requiera muestrear una seal de alta

frecuencia como puede ser la seal de telecomunicaciones.

4.1 Voltmetro digital.

Los voltmetros digitales convierten los voltajes analgicos a su representacin en cdigo

BCD (decimal codificado en binario), el cual se decodifica y se presenta la informacin a

travs de visualizadores, normalmente de 7 segmentos.

Analizaremos el principio de funcionamiento de un voltmetro digital que utiliza como

conversor una rampa digital. Para ello realizaremos un esquema en bloques de un DVM

(medidor de voltaje digital) de tres dgitos. En este caso, el contador est compuesto por tres

contadores de dcadas que cuentan hasta 999, para luego pasar a cero y volver a contar. La

salida de los contadores es convertida a analgica por el ADC interno, que tiene una

resolucin de 10 mV. Al final de la cuenta (999), nos va a dar un valor mximo de la tensin

de salida Vo, de 9,99 voltios.(valor mximo tambin de la tensin analgica a medir).

La salida de los contadores tambin alimenta a tres registros del tipo paralelo que guardan

transitoriamente la ltima informacin obtenida en la conversin, hasta que se complete la

nueva conversin. Estos registros son basculas (LATH) del tipo D, donde la informacin se

transfiere a la salida despus que se le aplica un pulso reloj. De esta manera mientras los

contadores estn contando, esta informacin no se transfiere a los elementos visualizadores,

sino que mantienen la cuenta anterior en su salida. De esta manera en los elementos

visualizadores, mientras se realiza la nueva lectura, mantienen el valor numrico anterior.

Cuando la ltima cuenta finaliza, los registros actualizan su salida, transfiriendo a estas

ltimas, la nueva informacin que tienen en sus entradas.

Daz Moreno Marcos 7EM3

25 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

A su vez la salida de los registros acta como entrada de decodificadores BCD/excitadores

de 7 segmentos que excitan finalmente los elementos visualizadores. La siguiente figura, nos

muestra el diagrama en bloques de las partes ms importantes del voltmetro digital:

Figura 20. Esquema de bloques de un medidor de tensin digital.

Daz Moreno Marcos 7EM3

26 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Analizando el diagrama de bloques, cuando Vo < Vi la salida del comparador Vc, permanece

en alto (1), permitiendo que pasen por la compuerta AND los pulsos reloj hacia el contador.

A medida que este se incrementa, la seal a la salida del DAC interno Vo se incrementa,

tambin a razn de 10 mV por pulso contado. A partir de un nmero de cuenta, resulta Vo >

Vi; para esta situacin, la salida del comparador pasa a bajo (0), inhabilitando la compuerta

AND, y con esto, deteniendo la cuenta, con lo que se termina la conversin. Por otra parte,

el flanco de bajada de la tensin Vc, provoca el disparo del multivibrador monoestable n1

que genera en su salida, un pulso temporizado de 1 s. . Este pulso activa los registros

(basculas) que transfieren el ultimo valor de la cuenta del contador, a su salida, haciendo

cambiar o no, la presentacin decimal en los visualizadores.

Cuando cae el pulso del MV1, la informacin queda retenida en los registros, y por otro lado

activa al MV2, que genera otro pulso que restablece los contadores a cero. Para esta ltima

situacin Vo cae a cero haciendo que Vo < Vi, el comparador entonces pasa a alto,

habilitando nuevamente la compuerta AND y permitiendo que los pulsos reloj sean contados

nuevamente, iniciando un nuevo ciclo de conversin.

La siguiente figura muestra las formas de ondas de las diferentes seales que intervienen en

la conversin del DVM.

Figura 21. Formas de onda de diferentes seales.

Daz Moreno Marcos 7EM3

27 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

4.2 Medicin de Resistencia, Corriente.

El DVM se puede convertir en un multmetro (DMM). Por ejemplo para medir corrientes, se

hace pasar la corriente desconocida a travs de una resistencia fija de referencia para producir

un voltaje. A los efectos de que esta resistencia no modifique prcticamente el circuito de

medicin, se la hace pasar por un amplificador operacional realimentado de tal forma que la

fuente de corriente desconocida vea en la entrada del multmetro un cortocircuito virtual.

Veamos el circuito bsico para convertir corriente en tensin:

Figura 22. Circuito para medir corriente.

Para medir resistencia, se hace pasar por la resistencia a medir, una corriente fija de referencia

(fuente de corriente constante). Esta corriente conocida, convierte la resistencia desconocida

en una tensin elctrica que luego es convertida a digital.

Figura 23. Circuito para medir resistencia.

En ambos casos, medicin de corrientes y resistencias, previo a la conversin A/D, se puede

colocar un amplificador o atenuador para obtener distintas escalas de medicin.

4.3 Mediciones de Tensiones en CA

Los voltajes de CA se pueden medir en este DVM, previa su conversin a un voltaje de CC.

En estos casos la conversin de CA a CC no resulta conveniente realizarla con rectificadores

no controlados, debido a los errores provocados por las cadas de tensin en los diodos

(especialmente para mediciones de pequeas seales). Una solucin, es recurrir a los

Daz Moreno Marcos 7EM3

28 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

denominados rectificadores de presicin de onda completa. Tenemos varios circuitos

denominados convertidores de ca a cc o tambin llamados circuito de valor medio

absoluto (MAV). El MAV de una onda de voltaje, sea sinodal, triangular o cuadrada, es

aproximadamente igual a su valor medio cuadrtica (MAV) o valor eficaz. Por lo tanto, un

circuito de bajo costo MAV puede utilizarse como sustituto de un circuito de clculo de

verdadero valor eficaz que es mucho ms caro. Veamos a continuacin un circuito MAV

realizado con amplificadores operacionales:

Figura 24. Circuito para medir tensin en CA.

En este circuito, cuando la tensin de entrada Vi es positiva, el diodo D2 esta polarizado

en directo y D1 en inverso. Por R1 circula una corriente I1=Vi/R1 y lo hace tambin por R2.

Como R1=R2=R (AO1 acta como inversor realimentado), entonces en el puntoA, la

tensin vale -Vi. Por otra parte, el AO2 acta como sumador inversor con seales que

ingresan por R3 y R4 que valen +Vi y -Vi respectivamente. La tensin a la salida de

AO2 vale: Vo= - ((R5/R4)*Vi + (R5/R3)*(-Vi)) = - (Vi + 2*(-Vi) ) = +Vi (salida para Vi

positivo) Cuando Vi es negativa, el diodo D2 no conduce y el diodo D1 conduce, dado que

aparece una tensin positiva a la salida de AO1 (+0,7 volt). Esto sucede as aun con una muy

pequea amplitud de la tensin de entrada, dada la gran ganancia de amplificador

operacional. En este caso, la tensin del punto A vale cero volt por estar D2 bloqueado. La

tensin de salida de AO2 vale:

Vo= - ((R5/R4)*(-Vi) + (R5/R3)*(0)) = - R5/R4*(-Vi) = +Vi (salida para Vi negativo)

Como vemos, en ambos casos, Vi positiva o negativa, la tensin de salida resulta siempre

positiva. Sin el capacitor C, tenemos a la salida de AO2 la seal de entrada rectificada en

onda completa, con exactitud y sin prdida de seal, como sera el caso de utilizar los

rectificadores con diodos.

Daz Moreno Marcos 7EM3

29 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

Figura 25. Formas de onda para la tensin.

Si le aadimos un capacitor de alto valor y de bajas fugas (10 F de tantalio), el circuito acta

como integrador, haciendo que Vo sea el valor promedio rectificado de Vi. Para DVM de

precisin, se utilizan circuitos que convierten el valor rms de una seal alterna pura u otra, a

un valor de CC (el circuito es ms complejo).

Daz Moreno Marcos 7EM3

30 | P g i n a

MEDICIONES ELCTRICAS. TIPOS DE CONVERTIDORES A/D

5. Bibliografa

http://www.geocities.ws/pnavar2/convert/index.html

http://www.asifunciona.com/electronica/af_conv_ad/conv_ad_5.htm

https://www.academia.edu/13456174/Unidad_3_Convertidores_Principios_el%C3

%A9ctricos_y_Aplicaciones_digitales

http://bibing.us.es/proyectos/abreproy/11932/fichero/2.MARCO+TEORICO.pdf

Daz Moreno Marcos 7EM3

31 | P g i n a

Potrebbero piacerti anche

- Catalogo de Claves Responsables Del Ipn ActualDocumento48 pagineCatalogo de Claves Responsables Del Ipn ActualSofia FelizNessuna valutazione finora

- Antología Lengua Que Vive 2014 PDFDocumento48 pagineAntología Lengua Que Vive 2014 PDFMarcos DMNessuna valutazione finora

- Ejemplos Sistema PUDocumento16 pagineEjemplos Sistema PUIsa Eliana Moy LNessuna valutazione finora

- Definición de Paas - ExpoDocumento5 pagineDefinición de Paas - ExpoMarcos DMNessuna valutazione finora

- Iec 60502 2 EspañolDocumento13 pagineIec 60502 2 Españolmartin100% (4)

- Generación DistribuidaDocumento6 pagineGeneración DistribuidaDaniel SalazarNessuna valutazione finora

- Preguntas Tipo TEST LibroDocumento24 paginePreguntas Tipo TEST LibroMANUEL YERAILNessuna valutazione finora

- Manual Isis Sipel PDFDocumento86 pagineManual Isis Sipel PDFClemente EstèNessuna valutazione finora

- PROPUESTA SUBESTACION CASETA-ModelDocumento1 paginaPROPUESTA SUBESTACION CASETA-ModelElmer SeguraNessuna valutazione finora

- FISIDocumento14 pagineFISIIrvin ChicasNessuna valutazione finora

- 153-Texto Del Artículo-371-2-10-20170420Documento3 pagine153-Texto Del Artículo-371-2-10-20170420Oscar OmarNessuna valutazione finora

- Wa0005 PDFDocumento65 pagineWa0005 PDFGodoyNessuna valutazione finora

- Silabo Fisica III 2015Documento10 pagineSilabo Fisica III 2015Cesar Samir MezaNessuna valutazione finora

- Laboratorio SemaforosDocumento10 pagineLaboratorio SemaforosCristian Alexis Angarita RodríguezNessuna valutazione finora

- Distribucion NeplanDocumento44 pagineDistribucion NeplanAlejandro Montoya100% (3)

- ACTIVIDADESFisicaDocumento5 pagineACTIVIDADESFisicaDulce Solis SanchezNessuna valutazione finora

- QATRO Politica, Presentacion, Actividades y Equipos de Prueba (010820)Documento40 pagineQATRO Politica, Presentacion, Actividades y Equipos de Prueba (010820)QATRO-ELEC-ISEI S.L.Nessuna valutazione finora

- Aplicación de La Soldadura Orbital Mig Aplicado en Aceros Inoxidables para La Empresa Consorcios Mmefa SacDocumento151 pagineAplicación de La Soldadura Orbital Mig Aplicado en Aceros Inoxidables para La Empresa Consorcios Mmefa SacAlberto OrihuelaNessuna valutazione finora

- Laboratorio #1 Circuitos Electronicos I - DiodosDocumento7 pagineLaboratorio #1 Circuitos Electronicos I - DiodosrikudousenninNessuna valutazione finora

- HGCII CarolinaMochaDocumento448 pagineHGCII CarolinaMochaivanNessuna valutazione finora

- 555 TimerDocumento17 pagine555 Timerjrm123Nessuna valutazione finora

- Ejercicios Con Circuitos en Serie y Paralelo Hernando Elvis Gutierrez GomezDocumento5 pagineEjercicios Con Circuitos en Serie y Paralelo Hernando Elvis Gutierrez GomezElvis Gutierrez100% (1)

- Informe #4 Laboratorio Circuitos IIIDocumento16 pagineInforme #4 Laboratorio Circuitos IIIPABLO ANTONIO SANDOVAL URIONANessuna valutazione finora

- Catalogo Componentes Electronicos LedvanceDocumento18 pagineCatalogo Componentes Electronicos LedvanceMaxidiano Isidro Céspedes GonzalesNessuna valutazione finora

- Generador Con Derivación DC Con Autoexcitación EXPODocumento24 pagineGenerador Con Derivación DC Con Autoexcitación EXPOJuan Manuel Maravilla OsorioNessuna valutazione finora

- Introduccion A SimulinkDocumento5 pagineIntroduccion A Simulinkalberto pazkual100% (1)

- 19 2020 Trabajo de RedesDocumento10 pagine19 2020 Trabajo de RedesJuan David Collazos Delgado0% (1)

- Circuito de Disparo Con UJTDocumento3 pagineCircuito de Disparo Con UJTDiego ValleNessuna valutazione finora

- Catalogo CatalogoDocumento98 pagineCatalogo Catalogothiago_gomes7953Nessuna valutazione finora

- Ondas ElectromagneticasDocumento27 pagineOndas ElectromagneticasJuan Carlos Leon MartinezNessuna valutazione finora

- Curva Caracteristica y Parametros Del UJTDocumento12 pagineCurva Caracteristica y Parametros Del UJTCésar Augusto Núñez Donado0% (3)

- Club Saber Electronica Numero 10Documento98 pagineClub Saber Electronica Numero 10CODE0303456100% (6)

- Centros de Control de MotoresDocumento19 pagineCentros de Control de MotoresJackson Nomar Perez SanchezNessuna valutazione finora

- 36478-6 MID 144 SID 243 Interruptor de Ajuste, Programador de Velocidad, ControlDocumento4 pagine36478-6 MID 144 SID 243 Interruptor de Ajuste, Programador de Velocidad, Controlluis sandovalNessuna valutazione finora