Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

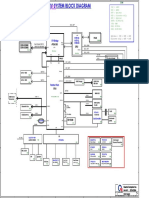

Acer Aspire One AO751H Sequence Atom

Caricato da

Moh HamCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Acer Aspire One AO751H Sequence Atom

Caricato da

Moh HamCopyright:

Formati disponibili

A

+5VPCU +3VPCU

SYS_HWPG(PCU)

From AC,Battery VIN

SUSON

MAINON

+5V +3V +2.5V +1.8V +1.5V +1.05V

HWPG_1.5V HWPG_1.05V

VRON

+VCC_CORE

From EC

From PWM

From EC

From PWM

STPCPU#

STPCLK#

CPUSLP#

DPSLP#

DPRSTP#

DPRSLPVR

RSTWARN

PLTRST#

CPU_PWRGD

CPURST#

From SCH

From SCH

From SCH

From SCH

From SCH

From SCH

From EC

From EC

From SCH

From SCH

ECPWROK

From EC

HWPG

CPU_COREPG

SLPRDY#(H Level)

From SCH

VRON

20us

100us

>5ms

>5ms

SLPMODE(L Level)

From SCH

MAINON

RSTRDY#(H Level)

From SCH

HWPG_1.8V (SUS)

+3VSUS +1.8VSUS +SMDDR_VREF +SMDDR_VTERM

>5ms

SUSON

From PWM

RSMRST#

From EC

+5V_S5

+3V_S5

NBSWON#

S5_ON

ZA3 Power On Sequence

From EC

From EC

From Power Button

From PWM

2ms

FAN Module

MOS CKT

Power Plane

+3VPCU

Battery

PWM FAN

Stuff

+3V

Date:

Size

Sunday, March 08, 2009

Sheet

PROJECT : ZA3

of

34

Rev

1A

Quanta Computer Inc.

Reserve

Power Sequence/ BOM Rule

Document Number

+3VPCU

CPU thermal Sensor EC EEPROM

Reserve

+3VSUS

Mini Card (3G)

Jmicron JMH330

+3V

Marvell 88SE8040

Description

Mini Card (WLAN/WMAX)

EC SMBUS Table

EC775 SDA2 / SCL2 (+3VPCU)

MOS CKT

+3V

RAM

Reserve Reserve

+3V

CLK GEN

EC775 SDA1 / SCL1 (+3VPCU)

Power Plane

FAN_PWM@

3G@

330@

8040@

Name

Poulsbo SCH SMBUS Table

(SMB_DATA) / (SMB_CLK) (+3V)

3G Module

PATA TO SATA BRIDGE

PATA TO SATA BRIDGE

Function

Items

BOM naming rule

Potrebbero piacerti anche

- Compal La-A971p r0.3 Schematics PDFDocumento53 pagineCompal La-A971p r0.3 Schematics PDFMoh HamNessuna valutazione finora

- Acer Aspire E1-431 E1-431G E1-471G ZQSA - ZQTA MB - Reve Unlock PDFDocumento44 pagineAcer Aspire E1-431 E1-431G E1-471G ZQSA - ZQTA MB - Reve Unlock PDFMoh HamNessuna valutazione finora

- h81h3-mv v1 PDFDocumento32 pagineh81h3-mv v1 PDFMoh HamNessuna valutazione finora

- Lenovo Yoga 3 14 LCFC NM-A381 Rev1.0Documento45 pagineLenovo Yoga 3 14 LCFC NM-A381 Rev1.0Moh HamNessuna valutazione finora

- LP141WX3 TLB1Documento27 pagineLP141WX3 TLB1Moh HamNessuna valutazione finora

- n91 MV d3h 0322Documento58 paginen91 MV d3h 0322Moh HamNessuna valutazione finora

- Sualaptop365.Edu - VN - Asus Pegatron H46Y Rev. 1.1 0401 LGDocumento60 pagineSualaptop365.Edu - VN - Asus Pegatron H46Y Rev. 1.1 0401 LGMoh HamNessuna valutazione finora

- Bremen 10G: MP Build (A02)Documento63 pagineBremen 10G: MP Build (A02)Moh HamNessuna valutazione finora

- Sw12e1ev XSTDocumento33 pagineSw12e1ev XSTMoh HamNessuna valutazione finora

- LG WF-T6600PP - SvcMnls Ipul PDFDocumento56 pagineLG WF-T6600PP - SvcMnls Ipul PDFMoh HamNessuna valutazione finora

- Quanta ZHK R3a 20140630 SchematicsDocumento34 pagineQuanta ZHK R3a 20140630 SchematicsAnonymous rePyCistNessuna valutazione finora

- Fujitsu S2110Documento99 pagineFujitsu S2110Moh HamNessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)