Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

CMOS Tech-2UP (12 - 11 - 03)

Caricato da

Mountsinai CscTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

CMOS Tech-2UP (12 - 11 - 03)

Caricato da

Mountsinai CscCopyright:

Formati disponibili

ECE 4420 CMOS Technology (12/11/03)

Page 1

CMOS TECHNOLOGY

INTRODUCTION

Classification of Silicon Technology

Silicon IC Technologies

Bipolar

Junction

Isolated

Dielectric

Isolated

Silicon031211-01 Germanium

Bipolar/CMOS

Oxide

isolated

Silicon

MOS

PMOS

(Aluminum

Gate)

CMOS

Aluminum

gate

Silicon

gate

NMOS

Aluminum

gate

Digital Integrated Circuit Design

Silicon

gate

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 2

Components of a Modern CMOS Technology

Illustration of a modern CMOS process:

Metal Layers

0.8m

M8

NMOS

PMOS

M7

Transistor

Transistor

M6

M5 7m

Polycide 0.3m

Polycide

Sidewall Spacers

M4

Salicide

Salicide

M3

Salicide

M2

M1

STI

n+

n+

Source/drain

extensions

Deep p-well

STI

p+

p+

Source/drain

STI

extensions

Deep n-well

p-substrate

031211-02

In addition to NMOS and PMOS transistors, the technology provides:

1.) A deep n-well that can be utilized to reduce substrate noise coupling.

2.) A MOS varactor that can serve in VCOs

3.) At least 6 levels of metal that can form many useful structures such as inductors,

capacitors, and transmission lines.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 3

CMOS Components Transistors

fT as a function of gate-source overdrive, VGS-VT (0.13m):

Typical, 25C

70

60

NMOS

Slow, 70C

fT (GHz)

50

Typical, 25C

40

30

Slow, 70C

PMOS

20

10

0

100

200

300

|VGS-VT| (mV)

400

500

030901-07

The upper frequency limit is probably around 40 GHz for NMOS with an fT in the vicinity

of 60GHz with an overdrive of 0.5V and at the slow-high temperature corner.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 4

FUNDAMENTAL PROCESSING STEPS

Basic steps

Oxide growth

Thermal diffusion

Ion implantation

Deposition

Etching

Epitaxy

Photolithography

Photolithography is the means by which the above steps are applied to selected areas of

the silicon wafer.

Silicon wafer

125-200 mm

(5"-8")

n-type: 3-5 -cm

p-type: 14-16 -cm

Digital Integrated Circuit Design

0.5-0.8mm

Fig. 2.1-1r

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 5

Oxidation

Description:

Oxidation is the process by which a layer of silicon dioxide is grown on the surface of a

silicon wafer.

Original silicon surface

tox

Silicon dioxide

0.44 tox

Silicon substrate

Fig. 2.1-2

Uses:

Protect the underlying material from contamination

Provide isolation between two layers.

Very thin oxides (100 to 1000) are grown using dry oxidation techniques. Thicker

oxides (>1000) are grown using wet oxidation techniques.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 6

Diffusion

Diffusion is the movement of impurity atoms at the surface of the silicon into the bulk of

the silicon.

Always in the direction from higher concentration to lower concentration.

Low

Concentration

High

Concentration

Fig. 150-04

Diffusion is typically done at high temperatures: 800 to 1400C

N0

Gaussian

ERFC

N(x)

N0

t1 < t2 < t3

N(x)

t 1 < t2 < t3

NB

NB

t1

t2

t3

Depth (x)

Infinite source of impurities at the surface.

t1

t2

t3

Depth (x)

Finite source of impurities at the surface.

Fig. 150-05

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 7

Ion Implantation

Ion implantation is the process by which

impurity ions are accelerated to a high

velocity and physically lodged into the

target material.

Path of

impurity

atom

Fixed Atom

Fixed Atom

Annealing is required to activate the

impurity atoms and repair the physical

Impurity Atom

damage to the crystal lattice. This step

final resting place

is done at 500 to 800C.

Ion implantation is a lower temperature

process compared to diffusion.

N(x)

Can implant through surface layers, thus it is

useful for field-threshold adjustment.

Can achieve unique doping profile such as

buried concentration peak.

N

Fixed Atom

Fig. 150-06

Concentration peak

Digital Integrated Circuit Design

ECE 4420 CMOS Technology (12/11/03)

Depth (x)

Fig. 150-07

P.E. Allen - 2003

Page 8

Deposition

Deposition is the means by which various materials are deposited on the silicon wafer.

Examples:

Silicon nitride (Si3N4)

Silicon dioxide (SiO2)

Aluminum

Copper

Polysilicon

There are various ways to deposit a material on a substrate:

Chemical-vapor deposition (CVD)

Low-pressure chemical-vapor deposition (LPCVD)

Plasma-assisted chemical-vapor deposition (PECVD)

Sputter deposition

Material that is being deposited using these techniques covers the entire wafer.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 9

Etching

Mask

Film

Etching is the process of selectively

removing a layer of material.

When etching is performed, the etchant

may remove portions or all of:

The desired material

The underlying layer

The masking layer

Underlying layer

(a) Portion of the top layer ready for etching.

a Selectivity

Mask

Film

c

b

Selectivity

Anisotropy

Underlying layer

Important considerations:

(b) Horizontal etching and etching of underlying layer.

Fig. 150-08

Anisotropy of the etch is defined as,

A = 1-(lateral etch rate/vertical etch rate)

Selectivity of the etch (film to mask and film to substrate) is defined as,

film etch rate

Sfilm-mask = mask etch rate

A = 1 and Sfilm-mask = are desired.

There are basically two types of etches:

Wet etch which uses chemicals

Dry etch which uses chemically active ionized gases.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 10

Epitaxy

Epitaxial growth consists of the formation of a layer of single-crystal silicon on the

surface of the silicon material so that the crystal structure of the silicon is continuous

across the interfaces.

It is done externally to the material as opposed to diffusion which is internal

The epitaxial layer (epi) can be doped differently, even oppositely, of the material on

which it grown

It accomplished at high temperatures using a chemical reaction at the surface

The epi layer can be any thickness, typically 1-20 microns

Gaseous cloud containing SiCL4 or SiH4

Si +

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

- Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Fig. 150-09

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 11

Photolithography

Components

Photoresist material

Mask

Material to be patterned (e.g., oxide)

Positive photoresist

Areas exposed to UV light are soluble in the developer

Negative photoresist

Areas not exposed to UV light are soluble in the developer

Steps

1. Apply photoresist

2. Soft bake (drives off solvents in the photoresist)

3. Expose the photoresist to UV light through a mask

4. Develop (remove unwanted photoresist using solvents)

5. Hard bake ( 100C)

6. Remove photoresist (solvents)

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 12

Illustration of Photolithography - Exposure

The process of exposing

Photomask

selective areas to light

through a photo-mask is

called printing.

Types of printing include:

Contact printing

Proximity printing

Projection printing

UV Light

Photomask

Photoresist

Polysilicon

Fig. 150-10

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 13

Illustration of Photolithography - Positive Photoresist

Develop

Polysilicon

Photoresist

Etch

Photoresist

Polysilicon

Remove

photoresist

Polysilicon

Fig. 150-11

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 14

Illustration of Photolithography - Negative Photoresist

(Not used much any more)

Photoresist

Underlying Layer

Photoresist

SiO2

Underlying Layer

SiO2

SiO2

Underlying Layer

Digital Integrated Circuit Design

Fig. 150-12

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 15

TYPICAL DSM CMOS FABRICATION PROCESS

Major Fabrication Steps for a DSM CMOS Process

1.) p and n wells

2.) Shallow trench isolation

3.) Threshold shift

4.) Thin oxide and gate polysilicon

5.) Lightly doped drains and sources

6.) Sidewall spacer

7.) Heavily doped drains and sources

8.) Siliciding (Salicide and Polycide)

9.) Bottom metal, tungsten plugs, and oxide

10.) Higher level metals, tungsten plugs/vias, and oxide

11.) Top level metal, vias and protective oxide

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 16

Step 1 Starting Material

The substrate should be highly doped to act like a good conductor.

yy

;;

Gate Ox

Oxide

Substrate

p+

Digital Integrated Circuit Design

p-

n-

n+

Poly

Salicide Polycide

Metal

031231-13

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 17

Step 2 - n and p wells

These are the areas where the transistors will be fabricated - NMOS in the p-well and

PMOS in the n-well.

Done by implantation followed by a deep diffusion.

n well implant and diffusion

yy

;;

Gate Ox

Oxide

p well implant and diffusion

n-well

p-well

Substrate

p+

p-

n-

n+

Poly

Salicide Polycide

Digital Integrated Circuit Design

Metal

031231-12

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 18

Step 3 Shallow Trench Isolation

The shallow trench isolation (STI) electrically isolates one region/transistor from another.

Shallow

Trench

Isolation

yy

;;

Gate Ox

Oxide

Shallow

Trench

Isolation

n-well

Shallow

Trench

Isolation

p-well

Substrate

p+

Digital Integrated Circuit Design

p-

n-

n+

Poly

Salicide Polycide

Metal

031231-11

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 19

Step 4 Threshold Shift and Anti-Punch Through Implants

The natural thresholds of the NMOS is about 0V and of the PMOS is about 1.2V. An nimplant is used to make the NMOS harder to invert and the PMOS easier resulting in

threshold voltages balanced around zero volts.

Also an implant can be applied to create a higher-doped region beneath the channels to

prevent punch-through from the drain depletion region extending to source depletion

region.

n+ anti-punch through implant

p+ anti-punch through implant

n threshold implant

n threshold implant

Shallow

Trench

Isolation

yy

;;

Gate Ox

Oxide

Shallow

Trench

Isolation

n-well

Shallow

Trench

Isolation

p-well

Substrate

p+

p-

n-

n+

Poly

Salicide Polycide

Digital Integrated Circuit Design

Metal

031231-10

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 20

; ;

Step 5 Thin Oxide and Polysilicon Gates

A thin oxide is deposited followed by polysilicon. These layers are removed where they

are not wanted.

Thin Oxide

Shallow

Trench

Isolation

yy

;;

Gate Ox

Oxide

Shallow

Trench

Isolation

n-well

Shallow

Trench

Isolation

p-well

Substrate

p+

Digital Integrated Circuit Design

p-

n-

n+

Poly

Salicide Polycide

Metal

031231-09

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 21

; ;

Step 6 Lightly Doped Drains and Sources

A lightly-doped implant is used to create a lightly-doped source and drain next to the

channel of the MOSFETs.

Shallow pImplant

Shallow

Trench

Isolation

yy

;;

Gate Ox

Oxide

Shallow pImplant

Shallow nImplant

Shallow nImplant

Shallow

Trench

Isolation

n-well

Shallow

Trench

Isolation

p-well

Substrate

p+

p-

n-

n+

Poly

Salicide Polycide

Digital Integrated Circuit Design

Metal

031231-08

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 22

Step 7 Sidewall Spacers

A layer of dielectric is deposited on the surface and removed in such a way as to leave

sidewall spacers next to the thin-oxide-polysilicon-polycide sandwich. These sidewall

spacers will prevent the part of the source and drain next to the channel from becoming

heavily doped.

; ;

Sidewall

Spacers

Shallow

Trench

Isolation

yy

;;

Gate Ox

Oxide

Sidewall

Spacers

Shallow

Trench

Isolation

n-well

Shallow

Trench

Isolation

p-well

Substrate

p+

Digital Integrated Circuit Design

p-

n-

n+

Poly

Salicide Polycide

Metal

031231-07

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 23

; ;

Step 8 Implantation of the Heavily Doped Sources and Drains

Note that not only does this step provide the completed sources and drains but allows for

ohmic contact into the wells and substrate.

p+

implant

n+

implant

p+

n+

Sidewall

p+ Spacers

p+

implant

implant

yy

;;

Gate Ox

Oxide

n+

implant

p+

implant

n+

n+

p+

p+

p+

Shallow

Trench

Isolation

n+

implant

Shallow

Trench

Isolation

n-well

Shallow

Trench

Isolation

p-well

Substrate

p+

p-

n-

n+

Poly

Salicide Polycide

Digital Integrated Circuit Design

Metal

031231-06

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 24

Step 9 Siliciding

Siliciding and polyciding is used to reduce interconnect resistivity by placing a lowresistance silicide such as TiSi2, WSi2, TaSi2, etc. on top of the diffusions.

; ;

Sidewall

Spacers

Salicide

Salicide

p+

n+

yy

;;

Gate Ox

Oxide

Salicide

p+

p+

Shallow

Trench

Isolation

Polycide

Salicide

n+

n+

p+

Shallow

Trench

Isolation

n-well

Shallow

Trench

Isolation

p-well

Substrate

p+

Digital Integrated Circuit Design

p-

n-

n+

Poly

Salicide Polycide

Metal

031231-05

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 25

Step 10 Intermediate Oxide Layer

An oxide layer is used to cover the transistors and to planarize the surface.

Intermediate

Oxide

Layer

Salicide

Salicide

p+

n+

yy

;;

Oxide

Polycide

Salicide

p+

p+

Shallow

Trench

Isolation

Gate Ox

; ;

Sidewall

Spacers

Salicide

n+

n+

p+

Shallow

Trench

Isolation

n-well

Shallow

Trench

Isolation

p-well

Substrate

p+

p-

n-

n+

Salicide Polycide

Poly

Digital Integrated Circuit Design

Metal

031231-04

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 26

Step 11- First-Level Metal

Tungsten plugs are built through the lower intermediate oxide layer to provide contact

between the devices, wells and substrate to the first-level metal.

Intermediate

Oxide

Layers

Tungsten

Plugs

Salicide

p+

Salicide

n+

yy

;;

Oxide

Polycide

Salicide

p+

p+

Shallow

Trench

Isolation

Gate Ox

; ;

Sidewall

Spacers

Tungsten

Plug

Salicide

n+

n+

p+

Shallow

Trench

Isolation

n-well

First

Level

Metal

Shallow

Trench

Isolation

p-well

Substrate

p+

Digital Integrated Circuit Design

p-

n-

n+

Poly

Salicide Polycide

Metal

031231-03

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 27

Step 12 Second-Level Metal

The previous step is repeated to from the second-level metal.

Intermediate

Oxide

Layers

Tungsten

Plugs

Tungsten

Plugs

Salicide

p+

Salicide

n+

yy

;;

Oxide

Salicide

Tungsten

Plug

Salicide

p+

p+

Shallow

Trench

Isolation

Gate Ox

; ;

Tungsten Plugs

Polycide

Sidewall

Spacers

n+

n+

p+

Shallow

Trench

Isolation

n-well

Second

Level

Metal

First

Level

Metal

Shallow

Trench

Isolation

p-well

Substrate

p+

p-

n-

n+

Poly

Salicide Polycide

Metal

Digital Integrated Circuit Design

031231-02

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 28

Completed Fabrication

After multiple levels of metal are applied, the fabrication is completed with a thicker toplevel metal and a protective layer to hermetically seal the circuit from the environment.

Note that metal is used for the upper level metal vias. The chip is electrically connected

by removing the protective layer over large bonding pads.

; ;

Protective Insulator Layer

Metal Vias

Intermediate

Oxide

Layers

Tungsten

Plugs

Tungsten

Plugs

Salicide

p+

Metal Via

Tungsten Plugs

Polycide

Sidewall

Spacers

Salicide

n+

Salicide

p+

p+

Shallow

Trench

Isolation

Top

Metal

Tungsten

Plug

Salicide

n+

n+

p+

Shallow

Trench

Isolation

n-well

Second

Level

Metal

First

Level

Metal

Shallow

Trench

Isolation

p-well

Substrate

Gate Ox

Oxide

p+

Digital Integrated Circuit Design

p-

n-

n+

Poly

Salicide Polycide

Metal

031231-01

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 29

Scanning Electron Microscope of a MOSFET Cross-section

Tungsten Plug

TEOS

SOG

Polycide

Sidewall

Spacer

TEOS/BPSG

Poly

Gate

Fig. 2.8-20

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 30

Scanning Electron Microscope Showing Metal Levels and Interconnect

Metal 3

Aluminim

Vias

Metal 2

Tungsten

Plugs

Metal 1

Transistors

Digital Integrated Circuit Design

Fig.180-11

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 31

SUMMARY

Fabrication is the means by which the circuit components, both active and passive, are

built as an integrated circuit.

Basic process steps include:

1.) Oxide growth

2.) Thermal diffusion

3.) Ion implantation

4.) Deposition

5.) Etching

6.) Epitaxy

The complexity of a process can be measured in the terms of the number of masking

steps or masks required to implement the process.

Major Processing Steps for DSM CMOS:

1.) p and n wells

2.) Shallow trench isolation

3.) Threshold shift

4.) Thin oxide and gate polysilicon

5.) Lightly doped drains and sources

6.) Sidewall spacer

7.) Heavily doped drains and sources

8.) Siliciding (Salicide and Polycide)

9.) Bottom metal, tungsten plugs, and oxide

10.) Higher level metals, tungsten plugs/vias, and oxide

11.) Top level metal, vias and protective oxide

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 32

INTEGRATED CIRCUIT LAYOUT

MOS Transistor Layout

Example of the layout of a single MOS

transistor:

Metal

FOX

Active area

drain/source

Contact

Cut

FOX

;;

;;

;;

;;

;;

Polysilicon

gate

L

Active area

drain/source

Metal 1

Fig. 2.6-04

Comments:

Make sure to contact the source and drain with multiple contacts to evenly distribute

the current flow under the gate.

Minimize the area of the source and drain to reduce bulk-source/drain capacitance.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 33

Resistor Layout

Direction of current flow

W

T

Area, A

L

Fig. 2.6-15

Resistance of a conductive sheet is expressed in terms of

L L

R = A = W T ()

where

= resistivity in -m

Ohms/square:

L

L

R = T W = S W ()

where

S is a sheet resistivity and has the units of ohms/square

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 34

Example of Resistor Layouts

Metal

Metal

FOX

FOX

FOX

Substrate

Active area (diffusion)

FOX

Active area (diffusion) Well diffusion

Active area

Contact

FOX

Substrate

Active area or Polysilicon W

Well diffusion

Contact

Cut

Cut

L

Metal 1

Diffusion or polysilicon resistor

Metal 1

Well resistor

Fig. 2.6-16

Corner corrections:

0.5

1.45

1.25

Fig. 2.6-16B

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 35

Example 1 - Resistance Calculation

Given a polysilicon resistor like that drawn above with W=0.8m and L=20m, calculate

s (in /), the number of squares of resistance, and the resistance value. Assume that

for polysilicon is 9 10-4 -cm and polysilicon is 3000 thick. Ignore any contact

resistance.

Solution

First calculate s.

9 10-4 -cm

s = T = 3000 10-8 cm = 30 /

The number of squares of resistance, N, is

20m

L

N = W = 0.8m = 25

giving the total resistance as

R = s = 30 25 = 750

Digital Integrated Circuit Design

ECE 4420 CMOS Technology (12/11/03)

P.E. Allen - 2003

Page 36

Design Rules

Design rules are geometrical constraints that guarantee the proper operation of a circuit

implemented by a given CMOS process.

These rules are necessary to avoid problems such as device misalignment, metal

fracturing, lack of continuity, etc.

Design rules are expressed in terms of minimum dimensions such as minimum values of:

- Widths

- Separations

- Extensions

- Overlaps

Design rules typically use a minimum feature dimension called lambda. Lambda is

usually equal to the minimum channel length.

Minimum resolution of the design rules is typically half lambda.

In most processes, lambda can be scaled or reduced as the process matures.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 37

Example of the Physical Design Process

CIRCUIT

n+

p+

+5V

Ground

M2

vout

(2.5V)

M1

M2

vin

(2.5V)

White

Metal Poly p-well n-substrate

vout

;;

;;;

;;

;;

yy

yy

;;

FABRICATION

LAYOUT

Blue Green Black Red Orange

;;;;;;;;;

;;;

;;;;;;;;;

;;

;

;;;

;;;;;;;;;

;;

;;

;;

;

;;

;;;

;;;;;;;;;

;;

;;

;;

;;

;;

;;

;;

;;;

p+

M1

p+

n+

n+

p-well

n-substr

ate

031113-01

5V

vin

Digital Integrated Circuit Design

-s

a

tr

te

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 38

BiCMOS TECHNOLOGY

Typical 0.5m BiCMOS Technology

Masking Sequence:

13. PMOS lightly doped drain

1. Buried n+ layer

2. Buried p+ layer

14. n+ source/drain

3. Collector tub

15. p+ source/drain

4. Active area

16. Silicide protection

5. Collector sinker

17. Contacts

6. n-well

18. Metal 1

7. p-well

19. Via 1

8. Emitter window

20. Metal 2

9. Base oxide/implant

21. Via 2

10. Emitter implant

22. Metal 3

11. Poly 1

23. Nitride passivation

12. NMOS lightly doped drain

Notation:

BSPG = Boron and Phosphorus doped Silicate Glass (oxide)

Kooi Nitride = A thin layer of silicon nitride on the silicon surface as a result of the

reaction of silicon with the HN3 generated, during the field oxidation.

TEOS = Tetro-Ethyl-Ortho-Silicate. A chemical compound used to deposit conformal

oxide films.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 39

n+ and p+ Buried Layers

Starting Substrate:

1m

p-substrate

BiCMOS-01

5m

n+ and p+ Buried Layers:

NPN Transistor

n+ buried layer

p+ buried

layer

PMOS Transistor

NMOS Transistor

n+ buried layer

p+ buried layer

1m

p-substrate

BiCMOS-02

5m

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 40

Epitaxial Growth

NPN Transistor

n-well

p-well

n+ buried layer

p+ buried

layer

PMOS Transistor

NMOS Transistor

n-well

p-well

n+ buried layer

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-03

5m

Comment:

As the epi layer grows vertically, it assumes the doping level of the substrate beneath it.

In addition, the high temperature of the epitaxial process causes the buried layers to

diffuse upward and downward.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 41

Collector Tub

NPN Transistor

Original Area of

CollectorTub Implant

PMOS Transistor

Collector Tub

n+ buried layer

p-well

p+ buried

layer

n-well

n+ buried layer

NMOS Transistor

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-04

5m

Comment:

The collector area is developed by an initial implant followed by a drive-in diffusion to

form the collector tub.

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 42

Active Area Definition

NPN Transistor

PMOS Transistor

NMOS Transistor

Nitride

-Silicon

Collector Tub

n+ buried layer

p-well

p+ buried

layer

n-well

n+ buried layer

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-05

5m

Comment:

The silicon nitride is use to impede the growth of the thick oxide which allows contact

to the substrate

-silicon is used for stress relief and to minimize the birds beak encroachment

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 43

Field Oxide

FOX

NPN Transistor

FOX

PMOS Transistor

Field Oxide

Collector Tub

p-well

n+ buried layer

p+ buried

layer

NMOS Transistor

Field Oxide

n-well

Field Oxide

p-type

Epitaxial

Silicon

p-well

n+ buried layer

p+ buried layer

1m

p-substrate

BiCMOS-06

5m

Comments:

The field oxide is used to isolate surface structures (i.e. metal) from the substrate

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 44

Collector Sink and n-Well and p-Well Definitions

FOX

NPN Transistor

Collector Sink

FOX

Collector Tub

n+ buried layer

PMOS Transistor

Anti-Punch Through

Threshold Adjust

Field Oxide

Field Oxide

Field Oxide

n-well

p-well

p+ buried

layer

NMOS Transistor

Anti-Punch Through

Threshold Adjust

n+ buried layer

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-07

Digital Integrated Circuit Design

5m

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 45

Base Definition

FOX

NPN Transistor

FOX

PMOS Transistor

Field Oxide

Collector Tub

Field Oxide

p+ buried

layer

Field Oxide

n-well

p-well

n+ buried layer

NMOS Transistor

p-well

n+ buried layer

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-08

5m

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 46

Definition of the Emitter Window and Sub-Collector Implant

NPN Transistor

PMOS Transistor

NMOS Transistor

FOX

FOX

Sacrifical Oxide

Field Oxide

Field Oxide

Field Oxide

n-well

p-well

p-well

Sub-Collector

n+ buried layer

p+ buried

layer

n+ buried layer

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-09

Digital Integrated Circuit Design

5m

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 47

Emitter Implant

FOX

NPN Transistor

Emitter Implant

FOX

PMOS Transistor

Field Oxide

Collector Tub

NMOS Transistor

Field Oxide

Field Oxide

n-well

p-well

p-well

Sub-Collector

n+ buried layer

p+ buried

layer

n+ buried layer

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-10

5m

Comments:

The polysilicon above the base is implanted with n-type carriers

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 48

Emitter Diffusion

FOX

FOX

NPN Transistor

PMOS Transistor

Field Oxide

NMOS Transistor

Field Oxide

Field Oxide

n-well

p-well

p-well

Emitter

n+ buried layer

p+ buried

layer

n+ buried layer

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-11

5m

Comments:

The polysilicon not over the emitter window is removed and the n-type carriers diffuse

into the base forming the emitter

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 49

Formation of the MOS Gates and LD Drains/Sources

FOX

NPN Transistor

FOX

PMOS Transistor

Field Oxide

Field Oxide

p+ buried

layer

Field Oxide

n-well

p-well

n+ buried layer

NMOS Transistor

n+ buried layer

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-12

5m

Comments:

The surface of the region where the MOSFETs are to be built is cleared and a thin gate

oxide is deposited with a polysilicon layer on top of the thin oxide

The polysilicon is removed over the source and drain areas

A light source/drain diffusion is done for the NMOS and PMOS (separately)

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 50

Heavily Doped Source/Drain

FOX

FOX

NPN Transistor

PMOS Transistor

Field Oxide

Field Oxide

p+ buried

layer

Field Oxide

n-well

p-well

n+ buried layer

NMOS Transistor

n+ buried layer

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-13

5m

Comments:

The sidewall spacers prevent the heavy source/drain doping from being near the

channel of the MOSFET

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 51

Siliciding

FOX

NPN Transistor

Silicide TiSi2

FOX

PMOS Transistor

Silicide TiSi2

Field Oxide

Field Oxide

p+ buried

layer

Field Oxide

n-well

p-well

n+ buried layer

NMOS Transistor

Silicide TiSi2

n+ buried layer

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-14

5m

Comments:

Siliciding is used to reduce the resistance of the polysilicon and to provide ohmic

contacts to the base, emitter, collector, sources and drains

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 52

Contacts

Tungsten Plugs

FOX

FOX

Tungsten Plugs

TEOS/BPSG/SOG

Field Oxide

Field Oxide

p+ buried

layer

n+ buried layer

TEOS/BPSG/SOG

Field

FieldOxide

Oxide

n-well

p-well

n+ buried layer

Tungsten Plugs

TEOS/BPSG/SOG

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-15

5m

Comments:

A dielectric is deposited over the entire wafer

One of the purposes of the dielectric is to smooth out the surface

Tungsten plugs are used to make electrical contact between the transistors and metal1

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 53

Metal1

FOX

Metal1

FOX

Metal1

TEOS/BPSG/SOG

TEOS/BPSG/SOG

Field Oxide

Field Oxide

p+ buried

layer

n+ buried layer

TEOS/BPSG/SOG

Field

FieldOxide

Oxide

n-well

p-well

n+ buried layer

Metal1

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-16

5m

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 54

Metal1-Metal2 Vias

FOX

FOX

Tungsten Plugs

TEOS/BPSG/SOG

TEOS/BPSG/SOG

Field Oxide

Field Oxide

p+ buried

layer

n+ buried layer

TEOS/BPSG/SOG

Field

FieldOxide

Oxide

n-well

p-well

n+ buried layer

Oxide/

SOG/

Oxide

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-17

Digital Integrated Circuit Design

5m

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 55

Metal2

Metal 2

FOX

FOX

Oxide/

SOG/

Oxide

TEOS/BPSG/SOG

TEOS/BPSG/SOG

Field Oxide

Field Oxide

n+ buried layer

p+ buried

layer

Field

FieldOxide

Oxide

n-well

p-well

n+ buried layer

TEOS/BPSG/SOG

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-18

5m

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 56

Metal2-Metal3 Vias

TEOS/

BPSG/

SOG

FOX

FOX

Oxide/

SOG/

Oxide

TEOS/BPSG/SOG

TEOS/BPSG/SOG

Field Oxide

Field Oxide

n+ buried layer

p+ buried

layer

Field

FieldOxide

Oxide

n-well

p-well

n+ buried layer

TEOS/BPSG/SOG

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-19

5m

Comments:

The metal2-metal3 vias will be filled with metal3 as opposed to tungsten plugs

Digital Integrated Circuit Design

P.E. Allen - 2003

ECE 4420 CMOS Technology (12/11/03)

Page 57

Completed Wafer

Nitride (Hermetically seals the wafer)

Oxide/SOG/Oxide

Metal3

Metal3

Vias

TEOS/

BPSG/

SOG

Oxide/

SOG/

Oxide

TEOS/BPSG/SOG

Field Oxide

Field Oxide

FOX

FOX

TEOS/BPSG/SOG

n+ buried layer

p+ buried

layer

Field

FieldOxide

Oxide

n-well

p-well

n+ buried layer

TEOS/BPSG/SOG

p-well

p-type

Epitaxial

Silicon

p+ buried layer

1m

p-substrate

BiCMOS-20

Digital Integrated Circuit Design

ECE 4420 CMOS Technology (12/11/03)

5m

P.E. Allen - 2003

Page 58

SUMMARY

This section has illustrated the major process steps for a 0.5micron BiCMOS

technology.

The performance of the active devices are:

npn bipolar junction transistor:

F = 100-140

BVCEO = 7V

fT = 12GHz,

n-channel FET:

K = 127A/V2

VT = 0.64V

N 0.060

p-channel FET:

VT = -0.63V

P 0.072

K = 34A/V2

Although todays state of the art is 0.25m to 0.13m BiCMOS, the processing steps

illustrated above approximate that which is done in a smaller geometry.

Digital Integrated Circuit Design

P.E. Allen - 2003

Potrebbero piacerti anche

- Thermal Oxidation Process BasicsDocumento104 pagineThermal Oxidation Process BasicsBalamurugan Velayutham100% (1)

- 2CMOSFabricationMNIT (DEc2006)Documento46 pagine2CMOSFabricationMNIT (DEc2006)Arjun YadavNessuna valutazione finora

- Automotive Control SystemsDocumento406 pagineAutomotive Control SystemsDenis Martins Dantas100% (3)

- Magoosh IELTS Vocabulary PDFDocumento37 pagineMagoosh IELTS Vocabulary PDFOmidNessuna valutazione finora

- Unit - IDocumento69 pagineUnit - IsaravananNessuna valutazione finora

- OxidationDocumento58 pagineOxidationDonnie SenomioNessuna valutazione finora

- Understand Centrifugal CompressorDocumento16 pagineUnderstand Centrifugal Compressorramanathan72-1100% (2)

- Lecture 030 - Deep Submicron (DSM) Cmos TechnologyDocumento14 pagineLecture 030 - Deep Submicron (DSM) Cmos TechnologywatelzbuddyNessuna valutazione finora

- Plasma Etching Processes for Interconnect Realization in VLSIDa EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeNessuna valutazione finora

- BS 5896 2010Documento33 pagineBS 5896 2010shashiresh50% (2)

- Ic FabricationDocumento7 pagineIc FabricationphooolNessuna valutazione finora

- Nmos and Cmos FabricationDocumento33 pagineNmos and Cmos FabricationmannsloveNessuna valutazione finora

- IC Manufacturing SMT Process FlowDocumento41 pagineIC Manufacturing SMT Process FlowAnirban KarNessuna valutazione finora

- Ic FabricationDocumento31 pagineIc FabricationMukesh Nexus100% (1)

- SOI TechnologyDocumento12 pagineSOI Technologycomputer48Nessuna valutazione finora

- 2.2 Basic Integrated Circuit Processes: ObjectiveDocumento15 pagine2.2 Basic Integrated Circuit Processes: Objectivetutul_kNessuna valutazione finora

- 2.2 Basic Integrated Circuit Processes: ObjectiveDocumento15 pagine2.2 Basic Integrated Circuit Processes: ObjectiveLalit BurrakNessuna valutazione finora

- Dasar Design CMOS TransistorDocumento49 pagineDasar Design CMOS Transistormaqbulloh darojatiNessuna valutazione finora

- CMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AnDocumento18 pagineCMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AntmdmurthyNessuna valutazione finora

- Midterm Exam 1Documento9 pagineMidterm Exam 1Hemal ShahporiaNessuna valutazione finora

- Basic Cmos Technology: Not ShownDocumento20 pagineBasic Cmos Technology: Not ShownajaykumarnotomNessuna valutazione finora

- C-1 CMOS Processing FlowDocumento76 pagineC-1 CMOS Processing FlowKu Ble YanNessuna valutazione finora

- 3 Thermal Oxidation PDFDocumento37 pagine3 Thermal Oxidation PDFGaurav SumanNessuna valutazione finora

- CMOS TechnologiesDocumento27 pagineCMOS TechnologiesDebela TesfayeNessuna valutazione finora

- CMOS Fabrication: (With Extended Comments)Documento26 pagineCMOS Fabrication: (With Extended Comments)srivardhana7Nessuna valutazione finora

- MEMS Design Chap 2-MEMS ProcessesDocumento31 pagineMEMS Design Chap 2-MEMS ProcessesvuonglupNessuna valutazione finora

- Chapter 3. CMOS Processing Technology - VLSI - CAD LaboratoryDocumento45 pagineChapter 3. CMOS Processing Technology - VLSI - CAD LaboratoryYidnekachwe MekuriaNessuna valutazione finora

- SedraSmith6e Appendix ADocumento17 pagineSedraSmith6e Appendix Anehalem650Nessuna valutazione finora

- Silicon Nitride Films Deposited by RF Sputtering For Microstructure Fabrication in MEMSDocumento11 pagineSilicon Nitride Films Deposited by RF Sputtering For Microstructure Fabrication in MEMSbehzadjaziNessuna valutazione finora

- Unit 2Documento33 pagineUnit 2Venky VellankiNessuna valutazione finora

- CH 03 CMOS Fabrication Part 01Documento18 pagineCH 03 CMOS Fabrication Part 01muneeb.abrarNessuna valutazione finora

- Unit 1Documento66 pagineUnit 1srgperumalNessuna valutazione finora

- How Semicon WorksDocumento15 pagineHow Semicon WorkskrisNessuna valutazione finora

- CMOS Fabrication Process and Layout Design Rules Lecture 10Documento4 pagineCMOS Fabrication Process and Layout Design Rules Lecture 10lomash acharyaNessuna valutazione finora

- Semiconductor Device Fabrication ProcessDocumento13 pagineSemiconductor Device Fabrication ProcessHasi De RustafariNessuna valutazione finora

- CH 02 FabricationDocumento55 pagineCH 02 FabricationUPADHYAY SHIVANSHNessuna valutazione finora

- NMOS Fabrication: Step 1: Processing The SubstrateDocumento5 pagineNMOS Fabrication: Step 1: Processing The Substratechinthala santhosh srkNessuna valutazione finora

- VLSI Unit 2 Technology - SDocumento52 pagineVLSI Unit 2 Technology - SIndrajeet GautamNessuna valutazione finora

- M Group: Linear Integrated Circuits (Ec1313) IC FabricationDocumento17 pagineM Group: Linear Integrated Circuits (Ec1313) IC Fabricationscribdm100% (1)

- EC1313 Two Marks Linear Integrated CircuitsDocumento11 pagineEC1313 Two Marks Linear Integrated Circuitsmoney_kandan2004Nessuna valutazione finora

- IC FabricationDocumento27 pagineIC FabricationJohn PaulNessuna valutazione finora

- Presentation 1 LicDocumento28 paginePresentation 1 LicreporterrajiniNessuna valutazione finora

- Chapter 3 Fabrication of Cmos Integrated Circuits Jin Fu Li Department of Electrical Engineering National Central University Jhongli TaiwanDocumento37 pagineChapter 3 Fabrication of Cmos Integrated Circuits Jin Fu Li Department of Electrical Engineering National Central University Jhongli TaiwanYusra AmeenNessuna valutazione finora

- Analog Digital VLSI Design TechniquesDocumento78 pagineAnalog Digital VLSI Design TechniqueshkajaiNessuna valutazione finora

- Chapter 4fabricationofICDocumento20 pagineChapter 4fabricationofICManikandan RadhakrishnanNessuna valutazione finora

- Introduction To MOS TechnologiesDocumento15 pagineIntroduction To MOS TechnologieslokeshwarrvrjcNessuna valutazione finora

- T2 VLSI FabricationDocumento24 pagineT2 VLSI FabricationM. Bilal NoorNessuna valutazione finora

- Fabrikasi ICDocumento47 pagineFabrikasi ICNanamaliamNessuna valutazione finora

- Tec CmosDocumento27 pagineTec Cmosgovind01Nessuna valutazione finora

- CMOS Fabrication Technologies and Process Design RulesDocumento14 pagineCMOS Fabrication Technologies and Process Design RulesPrashant SinghNessuna valutazione finora

- Microfabrication: Yash V. Kankal Roll No.Documento31 pagineMicrofabrication: Yash V. Kankal Roll No.yogesh_lonkarNessuna valutazione finora

- Cmos Process FlowDocumento29 pagineCmos Process FlowPushparaj Karu100% (1)

- Technology Brief 7: Integrated Circuit Fabrication Process: Semiconductor Processing BasicsDocumento4 pagineTechnology Brief 7: Integrated Circuit Fabrication Process: Semiconductor Processing BasicsAshima PatleyNessuna valutazione finora

- CMOS Fabrication Processes OverviewDocumento30 pagineCMOS Fabrication Processes OverviewJames Hyun Wook ParkNessuna valutazione finora

- Vlsi FabDocumento8 pagineVlsi FabhaheNessuna valutazione finora

- Ee2254 Lica QBDocumento0 pagineEe2254 Lica QBnjparNessuna valutazione finora

- MANUFACTURING: MODERN CMOS PROCESS TECHNOLOGIESDocumento6 pagineMANUFACTURING: MODERN CMOS PROCESS TECHNOLOGIESBoyella NagendraNessuna valutazione finora

- Cmos Metal GateDocumento56 pagineCmos Metal GateSubin AlexNessuna valutazione finora

- 3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyDocumento1 pagina3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNessuna valutazione finora

- VLSI DesignDocumento181 pagineVLSI Designprabhug22Nessuna valutazione finora

- Compendium of Atomic Alkali Resistant Optical Thin Films, Diffusion and Electrical Mobility in Diode Pumped Alkali Lasers (DPALs)Da EverandCompendium of Atomic Alkali Resistant Optical Thin Films, Diffusion and Electrical Mobility in Diode Pumped Alkali Lasers (DPALs)Nessuna valutazione finora

- Ceramic Materials for Energy Applications VIDa EverandCeramic Materials for Energy Applications VIHua-Tay LinNessuna valutazione finora

- Silicon Carbide One-dimensional NanostructuresDa EverandSilicon Carbide One-dimensional NanostructuresNessuna valutazione finora

- Amalambika Convent English School student project on chemistryDocumento2 pagineAmalambika Convent English School student project on chemistryMountsinai CscNessuna valutazione finora

- 16PGAD0242 Athira SasiDocumento5 pagine16PGAD0242 Athira SasiMountsinai CscNessuna valutazione finora

- Preliminary Agreement SignedDocumento4 paginePreliminary Agreement SignedMountsinai CscNessuna valutazione finora

- Penchal Reddy High School: Welcome's You To Ruther Ford Model of An Atom Power Point PresentationDocumento14 paginePenchal Reddy High School: Welcome's You To Ruther Ford Model of An Atom Power Point PresentationMountsinai CscNessuna valutazione finora

- Preliminary Agreement SignedDocumento4 paginePreliminary Agreement SignedMountsinai CscNessuna valutazione finora

- HHRS170728-Thilip SoftDocumento23 pagineHHRS170728-Thilip SoftMountsinai CscNessuna valutazione finora

- Asca Registration Form DateDocumento1 paginaAsca Registration Form DateMountsinai CscNessuna valutazione finora

- AntonyDocumento3 pagineAntonyMountsinai CscNessuna valutazione finora

- Preliminary Agreement SignedDocumento4 paginePreliminary Agreement SignedMountsinai CscNessuna valutazione finora

- Labour Welfare - Meaning and Definition of Labour WelfareDocumento2 pagineLabour Welfare - Meaning and Definition of Labour WelfareMountsinai CscNessuna valutazione finora

- Preliminary Agreement SignedDocumento4 paginePreliminary Agreement SignedMountsinai CscNessuna valutazione finora

- CurriculumDocumento3 pagineCurriculumMountsinai CscNessuna valutazione finora

- Medical CertificateDocumento1 paginaMedical CertificateMountsinai CscNessuna valutazione finora

- Chapter 1Documento16 pagineChapter 1Mountsinai CscNessuna valutazione finora

- M.A.M Bethany Public School Kumily: Particulers Rs Ps Particulers Rs PsDocumento1 paginaM.A.M Bethany Public School Kumily: Particulers Rs Ps Particulers Rs PsMountsinai CscNessuna valutazione finora

- 1.INTRODUCTION A voice browser is a “device which interprets a (voice) markup language and is capable of generating voice output and/or interpreting voice input,and possibly other input/output modalities." The definition of a voice browser, above, is a broad one.The fact that the system deals with speech is obvious given the first word of the name,but what makes a software system that interacts with the user via speech a "browser"?The information that the system uses (for either domain data or dialog flow) is dynamic and comes somewhere from the Internet. From an end-user's perspective, the impetus is to provide a service similar to what graphical browsers of HTML and related technologies do today, but on devices that are not equipped with full-browsers or even the screens to support them. This situation is only exacerbated by the fact that much of today's content depends on the ability to run scripting languages and 3rd-party plDocumento24 pagine1.INTRODUCTION A voice browser is a “device which interprets a (voice) markup language and is capable of generating voice output and/or interpreting voice input,and possibly other input/output modalities." The definition of a voice browser, above, is a broad one.The fact that the system deals with speech is obvious given the first word of the name,but what makes a software system that interacts with the user via speech a "browser"?The information that the system uses (for either domain data or dialog flow) is dynamic and comes somewhere from the Internet. From an end-user's perspective, the impetus is to provide a service similar to what graphical browsers of HTML and related technologies do today, but on devices that are not equipped with full-browsers or even the screens to support them. This situation is only exacerbated by the fact that much of today's content depends on the ability to run scripting languages and 3rd-party plPooja ReddyNessuna valutazione finora

- Rony Biodata 1Documento2 pagineRony Biodata 1Mountsinai CscNessuna valutazione finora

- Bryophyta to Chordata Key OrganismsDocumento18 pagineBryophyta to Chordata Key OrganismsMountsinai CscNessuna valutazione finora

- Li-Fi: The Future of Wireless CommunicationDocumento2 pagineLi-Fi: The Future of Wireless CommunicationMountsinai CscNessuna valutazione finora

- Li FiDocumento24 pagineLi FiMountsinai CscNessuna valutazione finora

- Li - Fi Department of Computer ScienceDocumento23 pagineLi - Fi Department of Computer ScienceMountsinai Csc0% (1)

- OneRoof CyberCafePro ClientManualDocumento43 pagineOneRoof CyberCafePro ClientManualAnna Size100% (3)

- Li - Fi Department of Computer ScienceDocumento23 pagineLi - Fi Department of Computer ScienceMountsinai Csc0% (1)

- ObjectiveDocumento1 paginaObjectiveMountsinai CscNessuna valutazione finora

- CV Summary for IT Position Seeking Recent GraduateDocumento5 pagineCV Summary for IT Position Seeking Recent Graduateeang barangNessuna valutazione finora

- Daily DAWN News Vocabulary With Urdu Meaning (05 April 2020) PDFDocumento6 pagineDaily DAWN News Vocabulary With Urdu Meaning (05 April 2020) PDFAEO Begowala100% (2)

- Axial Shortening of Column in Tall Structure.Documento9 pagineAxial Shortening of Column in Tall Structure.P.K.Mallick100% (1)

- Transient and Random VibrationDocumento19 pagineTransient and Random VibrationAman SharmaNessuna valutazione finora

- Analytic DeviceDocumento4 pagineAnalytic DeviceuiuiuiuNessuna valutazione finora

- CHEST Workout Structure and Training Log PREVIEWDocumento3 pagineCHEST Workout Structure and Training Log PREVIEWgaurav singhNessuna valutazione finora

- Aikah ProfileDocumento20 pagineAikah ProfileMohammad ZeeshanNessuna valutazione finora

- A134 PDFDocumento4 pagineA134 PDFJarbas MoraesNessuna valutazione finora

- Steam and Brine Gathering System DesignDocumento32 pagineSteam and Brine Gathering System Designbogdan_chivulescuNessuna valutazione finora

- NETWORK ANALYSIS Chap.8 TWO PORT NETWORK & NETWORK FUNCTIONS PDFDocumento34 pagineNETWORK ANALYSIS Chap.8 TWO PORT NETWORK & NETWORK FUNCTIONS PDFsudarshan poojaryNessuna valutazione finora

- Player Alex's SEO-Optimized Character Sheet for Antero VipunenDocumento2 paginePlayer Alex's SEO-Optimized Character Sheet for Antero VipunenAlex AntiaNessuna valutazione finora

- The Future of Smart Cities and RegionsDocumento20 pagineThe Future of Smart Cities and RegionsChristianNessuna valutazione finora

- Digital Logic and Microprocessor Design With Interfacing 2nd Edition Hwang Solutions ManualDocumento27 pagineDigital Logic and Microprocessor Design With Interfacing 2nd Edition Hwang Solutions Manualdacdonaldnxv1zq100% (27)

- OceanPixel Abundo Marine Renewable Energy An Emerging OptionDocumento96 pagineOceanPixel Abundo Marine Renewable Energy An Emerging OptionjopaypagasNessuna valutazione finora

- Library Management System Project ReportDocumento50 pagineLibrary Management System Project ReportSURAJ GAMINGNessuna valutazione finora

- Gysmi-Note UC3845BDGDocumento1 paginaGysmi-Note UC3845BDGfrance locatelNessuna valutazione finora

- Design of A 120 In.-Diameter Steel Bifurcation With A Small Acute Angle For A High-Pressure PenstockDocumento10 pagineDesign of A 120 In.-Diameter Steel Bifurcation With A Small Acute Angle For A High-Pressure PenstockStalynMEcNessuna valutazione finora

- Holux M-1000C Bluetooth GPS Logger Manual GuideDocumento22 pagineHolux M-1000C Bluetooth GPS Logger Manual Guidenabiloo2003Nessuna valutazione finora

- PMO ProceduresDocumento21 paginePMO ProceduresTariq JamalNessuna valutazione finora

- P8B WS Memory Qualified Vendors List (QVL)Documento3 pagineP8B WS Memory Qualified Vendors List (QVL)bolpensmaierNessuna valutazione finora

- The Five Generations of Computers: AssignmentDocumento10 pagineThe Five Generations of Computers: Assignmentjismon_kjNessuna valutazione finora

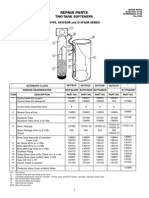

- Star S07FS32DR Water Softener Repair PartsDocumento1 paginaStar S07FS32DR Water Softener Repair PartsBillNessuna valutazione finora

- Siemens 1LE1 PDFDocumento308 pagineSiemens 1LE1 PDFharold100% (1)

- AMG ActuatorsDocumento12 pagineAMG ActuatorsMohan ArumugavallalNessuna valutazione finora

- Allcargo Corporate BrochureDocumento12 pagineAllcargo Corporate BrochureallinonecargologisticsNessuna valutazione finora

- The Causes of Shear Cracking in Prestressed Concrete Box Girder BridgesDocumento10 pagineThe Causes of Shear Cracking in Prestressed Concrete Box Girder BridgesVipin Kumar ParasharNessuna valutazione finora