Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Altera Cyclone V Soc Development & Education Board (De1-Soc)

Caricato da

Johanes Patrick STitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Altera Cyclone V Soc Development & Education Board (De1-Soc)

Caricato da

Johanes Patrick SCopyright:

Formati disponibili

5

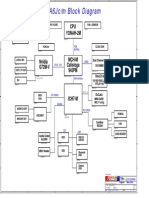

ALTERA Cyclone V SoC Development & Education Board (DE1-SoC)

D

PAGE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

CONTENT

Cover Page

Block Diagram

FPGA BANK 3, BANK 4

FPGA BANK 5, BANK 6

FPGA BANK 7, BANK 8

FPGA Clocks, GND

FPGA Configuration

FPGA Decoupling

FPGA Power

USB Blaster II

JTAG Chain

GPIO 0

GPIO 1

SDRAM, HPS QSPI Flash

HPS DDR3 SDRAM

PAGE

CONTENT

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

ADV7123 VGA

ADV7180 Video Decoder

Audio CODEC

7-Segment Display, LED

FPGA BUTTON, Switch

ADC, PS2, IR Tx, IR Rx

2-port USB Host

1 Gagabit Ethernet

UART to USB, SD CARD

Accelerometer, LTC Connector

I2C Multiplexer, HPS BUTTON, HPS LED

Power - 1.1V

Power - 5V, 3.3V

Power - 9V, 2.5V, 1.5V

Power - 1.2V, 1.8V, DDR3 VREF, DDR3 VTT

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

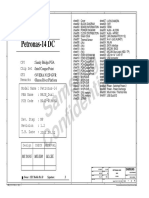

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

Cover Page

Thursday, November 20, 2014

Rev

F

Sheet

1

of

30

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

Block Diagram

Friday, December 19, 2014

Rev

F

Sheet

1

of

30

DRAM_ADDR[12..0] 6,14

D

SW[9..0]

DRAM_DQ[15..0]

7,20

USB_B2_DATA[7..0]

7,10

KEY[3..0]

14

6,20

GPIO_0[35..0]

6,12

GPIO_1[35..0]

6,13

LEDR[9..0]

4,19

U20-9

Bank 3A

USB_B2_CLK

10

USB_EMPTY

10

SW2

USB_SCL

10

USB_SDA

10

USB_RESET_n 10

USB_B2_DATA7

USB_B2_DATA4

FAN_CTRL

7

SW0

USB_OE_n

10

USB_RD_n

10

USB_FULL

10

USB_WR_n

10

USB_B2_DATA3

USB_B2_DATA2

SW1

SW5

USB_B2_DATA6

USB_B2_DATA1

AF4

AF5

AF9

AG8

AF8

AG7

AG1

AH2

AA12

AB12

AF6

AG6

AG5

AH5

AJ1

AJ2

AC12

AD12

AG2

AH3

Bank 3 VCCIO = 3.3V

Bank 3B

U20-10

IO_3B/DIFFIO_TX_B17P/DQ3B

IO_3B/DIFFIO_TX_B17N

IO_3B/DIFFIO_RX_B18P/DQ3B

IO_3A/PR_ERROR/DIFFIO_RX_B7P

IO_3B/DIFFIO_RX_B18N/DQ3B

IO_3A/PR_DONE/DIFFIO_RX_B7N

IO_3B/DIFFIO_RX_B19P/DQS3B

IO_3A/DIFFIO_TX_B8P/DQ1B

IO_3B/DIFFIO_RX_B19N/DQSN3B

IO_3A/PR_READY/DIFFIO_TX_B8N/DQ1B

IO_3B/DIFFIO_TX_B20P

IO_3A/DIFFIO_TX_B9P/DQ2B

IO_3B/DIFFIO_TX_B20N/DQ3B

IO_3A/DIFFIO_TX_B9N

IO_3B/DIFFIO_TX_B21P/DQ3B

IO_3A/DIFFIO_RX_B10P/DQ2B

IO_3B/DIFFIO_TX_B21N/DQ3B

IO_3A/DIFFIO_RX_B10N/DQ2B

IO_3B/DIFFIO_RX_B22P/DQ3B

IO_3A/DIFFIO_RX_B11P/DQS2B

IO_3B/DIFFIO_RX_B22N/DQ3B

IO_3A/DIFFIO_RX_B11N/DQSN2B

IO_3B/DIFFIO_RX_B23P

IO_3A/DIFFIO_TX_B12P

IO_3B/DIFFIO_RX_B23N

IO_3A/DIFFIO_TX_B12N/DQ2B

IO_3B/DIFFIO_TX_B24P/DQ3B

IO_3A/DIFFIO_TX_B13P/DQ2B

IO_3B/DIFFIO_TX_B24N/DQ3B

IO_3A/DIFFIO_TX_B13N/DQ2B

IO_3B/DIFFIO_TX_B25P/DQ4B/B_WEN

IO_3A/DIFFIO_RX_B14P/DQ2B

IO_3B/DIFFIO_TX_B25N/GND

IO_3A/DIFFIO_RX_B14N/DQ2B

IO_3B/DIFFIO_RX_B26P/DQ4B/B_A_14

IO_3A/DIFFIO_RX_B15P

IO_3B/DIFFIO_RX_B26N/DQ4B/B_A_15

IO_3A/DIFFIO_RX_B15N

IO_3B/DIFFIO_RX_B27P/DQS4B/B_CSN_0

IO_3A/DIFFIO_TX_B16P/DQ2B

IO_3B/DIFFIO_RX_B27N/DQSN4B/B_CSN_1

IO_3A/DIFFIO_TX_B16N/DQ2B

IO_3B/DIFFIO_TX_B28P/B_A_12

IO_3B/DIFFIO_TX_B28N/DQ4B/B_A_13

IO_3B/DIFFIO_TX_B29P/DQ4B/B_A_10

IO_3B/DIFFIO_TX_B29N/DQ4B/B_A_11

IO_3B/DIFFIO_RX_B30P/DQ4B/B_A_8

IO_3B/DIFFIO_RX_B30N/DQ4B/B_A_9

IO_3B/DIFFIO_TX_B32P/DQ4B/B_CASN

IO_3B/DIFFIO_TX_B32N/DQ4B/B_RASN

IO_3B/DIFFIO_TX_B33P/DQ5B/B_BA_0

IO_3B/DIFFIO_TX_B33N/GND

IO_3B/DIFFIO_RX_B34P/DQ5B/B_BA_1

IO_3B/DIFFIO_RX_B34N/DQ5B/B_BA_2

IO_3B/DIFFIO_RX_B35P/DQS5B/B_CK

IO_3B/DIFFIO_RX_B35N/DQSN5B/B_CKN

IO_3B/DIFFIO_TX_B36P/B_A_6

IO_3B/DIFFIO_TX_B36N/DQ5B/B_A_7

IO_3B/DIFFIO_RX_B38P/DQ5B/B_A_4

IO_3B/DIFFIO_RX_B38N/DQ5B/B_A_5

IO_3B/DIFFIO_TX_B40P/DQ5B/B_A_0

IO_3B/DIFFIO_TX_B40N/DQ5B/B_A_1

AG10

AH9

AF11 14

AG11 14

AA13 14

AB13 14

AK2 21

AK3 21

AJ4 21

AK4 21

AE13 14

AF13 14

AD14

AE14

AJ5

AK6

AJ6

AJ7

AG12

AG13

AB15

AC14

AK7

AK8

AJ9

AK9

AH13

AH14

AH7

AH8

AH10

AJ10

AJ11

AK11

AA14

AA15

AK12 14

AK13 14

AG15

AH15

AJ14

AK14

Bank 4A VCCIO

DRAM_DQ5

DRAM_DQ11

DRAM_CAS_N

DRAM_CS_N

DRAM_WE_N

DRAM_LDQM

ADC_SCLK

ADC_DOUT

ADC_CONVST

ADC_DIN

DRAM_RAS_N

DRAM_BA0

DRAM_ADDR6

DRAM_ADDR3

DRAM_DQ15

DRAM_DQ0

DRAM_DQ14

DRAM_DQ1

DRAM_ADDR10

DRAM_ADDR9

DRAM_ADDR4

DRAM_ADDR5

DRAM_DQ2

DRAM_DQ3

DRAM_DQ10

DRAM_DQ4

DRAM_ADDR11

DRAM_ADDR1

DRAM_DQ13

DRAM_DQ12

DRAM_DQ8

DRAM_DQ9

DRAM_DQ7

DRAM_DQ6

KEY0

KEY1

DRAM_UDQM

DRAM_CKE

DRAM_ADDR2

DRAM_ADDR8

DRAM_ADDR12

DRAM_ADDR0

GPIO_012

GPIO_015

GPIO_018

GPIO_032

LEDR0

LEDR1

GPIO_013

GPIO_014

GPIO_09

GPIO_04

GPIO_031

GPIO_022

GPIO_011

GPIO_010

GPIO_034

GPIO_020

GPIO_08

GPIO_05

LEDR2

LEDR4

GPIO_07

GPIO_06

GPIO_021

GPIO_035

GPIO_030

GPIO_033

GPIO_123

GPIO_111

GPIO_129

GPIO_128

GPIO_026

GPIO_027

GPIO_01

GPIO_016

GPIO_023

GPIO_126

GPIO_125

GPIO_127

AG16

AG17

AE17

AF18

V16

W16

AE16

AF16

AJ16

AK16

AG21

AH20

AH17

AH18

AG18

AH19

AJ17

AK18

V17

W17

AJ19

AK19

AJ20

AJ21

AF19

AG20

AG23

AH24

AG22

AH22

AE18

AE19

Y17

AA18

AK21

AK22

AH23

AJ22

= 3.3V

IO_4A/DIFFIO_TX_B41P/DQ6B/B_DQ_2

IO_4A/DIFFIO_RX_B62P/DQ8B/B_DQ_21

IO_4A/RZQ_0/DIFFIO_TX_B41N

IO_4A/DIFFIO_RX_B62N/DQ8B/B_DQ_20

IO_4A/DIFFIO_RX_B42P/DQ6B/B_DQ_1

IO_4A/DIFFIO_RX_B63P/GND

IO_4A/DIFFIO_RX_B42N/DQ6B/B_DQ_0

IO_4A/DIFFIO_RX_B63N/GND

IO_4A/DIFFIO_RX_B43P/DQS6B/B_DQS_0

IO_4A/DIFFIO_TX_B64P/DQ8B/B_DM_2

IO_4A/DIFFIO_RX_B43N/DQSN6B/B_DQSN_0

IO_4A/DIFFIO_TX_B64N/DQ8B/B_DQ_23

IO_4A/DIFFIO_TX_B44P/B_ODT_0

IO_4A/DIFFIO_TX_B65P/DQ9B/B_DQ_26

IO_4A/DIFFIO_TX_B44N/DQ6B/B_DQ_3

IO_4A/DIFFIO_TX_B65N/GND

IO_4A/DIFFIO_TX_B45P/DQ6B/B_DQ_6

IO_4A/DIFFIO_RX_B66P/DQ9B/B_DQ_25

IO_4A/DIFFIO_TX_B45N/DQ6B/B_ODT_1

IO_4A/DIFFIO_RX_B66N/DQ9B/B_DQ_24

IO_4A/DIFFIO_RX_B46P/DQ6B/B_DQ_5

IO_4A/DIFFIO_RX_B67P/DQS9B/B_DQS_3

IO_4A/DIFFIO_RX_B46N/DQ6B/B_DQ_4

IO_4A/DIFFIO_RX_B67N/DQSN9B/B_DQSN_3

IO_4A/DIFFIO_TX_B48P/DQ6B/B_DM_0

IO_4A/DIFFIO_TX_B68P/GND

IO_4A/DIFFIO_TX_B48N/DQ6B/B_DQ_7

IO_4A/DIFFIO_TX_B68N/DQ9B/B_DQ_27

IO_4A/DIFFIO_TX_B49P/DQ7B/B_DQ_10

IO_4A/DIFFIO_TX_B69P/DQ9B/B_DQ_30

IO_4A/DIFFIO_TX_B49N/GND

IO_4A/DIFFIO_TX_B69N/DQ9B/GND

IO_4A/DIFFIO_RX_B50P/DQ7B/B_DQ_9

IO_4A/DIFFIO_RX_B70P/DQ9B/B_DQ_29

IO_4A/DIFFIO_RX_B50N/DQ7B/B_DQ_8

IO_4A/DIFFIO_RX_B70N/DQ9B/B_DQ_28

IO_4A/DIFFIO_RX_B51P/DQS7B/B_DQS_1

IO_4A/DIFFIO_RX_B71P/GND

IO_4A/DIFFIO_RX_B51N/DQSN7B/B_DQSN_1

IO_4A/DIFFIO_RX_B71N/GND

IO_4A/DIFFIO_TX_B52P/B_CKE_1

IO_4A/DIFFIO_TX_B72P/DQ9B/B_DM_3

IO_4A/DIFFIO_TX_B52N/DQ7B/B_DQ_11

IO_4A/DIFFIO_TX_B72N/DQ9B/B_DQ_31

IO_4A/DIFFIO_TX_B53P/DQ7B/B_DQ_14

IO_4A/DIFFIO_TX_B73P/DQ10B/B_DQ_34

IO_4A/DIFFIO_TX_B53N/DQ7B/B_CKE_0

IO_4A/DIFFIO_TX_B73N/GND

IO_4A/DIFFIO_RX_B54P/DQ7B/B_DQ_13

IO_4A/DIFFIO_RX_B74P/DQ10B/B_DQ_33

IO_4A/DIFFIO_RX_B54N/DQ7B/B_DQ_12

IO_4A/DIFFIO_RX_B74N/DQ10B/B_DQ_32

IO_4A/DIFFIO_TX_B56P/DQ7B/B_DM_1

IO_4A/DIFFIO_RX_B75P/DQS10B/B_DQS_4

IO_4A/DIFFIO_TX_B56N/DQ7B/B_DQ_15

IO_4A/DIFFIO_RX_B75N/DQSN10B/B_DQSN_4

IO_4A/DIFFIO_TX_B57P/DQ8B/B_DQ_18

IO_4A/DIFFIO_TX_B76P/GND

IO_4A/DIFFIO_TX_B57N/GND

IO_4A/DIFFIO_TX_B76N/DQ10B/B_DQ_35

IO_4A/DIFFIO_RX_B58P/DQ8B/B_DQ_17

IO_4A/DIFFIO_TX_B77P/DQ10B/B_DQ_38

IO_4A/DIFFIO_RX_B58N/DQ8B/B_DQ_16

IO_4A/DIFFIO_TX_B77N/DQ10B/GND

IO_4A/DIFFIO_RX_B59P/DQS8B/B_DQS_2

IO_4A/DIFFIO_RX_B78P/DQ10B/B_DQ_37

IO_4A/DIFFIO_RX_B59N/DQSN8B/B_DQSN_2

IO_4A/DIFFIO_RX_B78N/DQ10B/B_DQ_36

IO_4A/DIFFIO_TX_B60P/B_RESETN

IO_4A/DIFFIO_RX_B79P/GND

IO_4A/DIFFIO_TX_B60N/DQ8B/B_DQ_19

IO_4A/DIFFIO_RX_B79N/GND

IO_4A/DIFFIO_TX_B61P/DQ8B/B_DQ_22

IO_4A/DIFFIO_TX_B80P/DQ10B/B_DM_4

IO_4A/DIFFIO_TX_B61N/DQ8B/GND

IO_4A/DIFFIO_TX_B80N/DQ10B/B_DQ_39

GPIO_028

GPIO_029

GPIO_03

GPIO_017

GPIO_124

GPIO_122

GPIO_121

GPIO_120

GPIO_131

GPIO_130

GPIO_019

GPIO_024

GPIO_117

GPIO_118

GPIO_19

GPIO_119

GPIO_132

GPIO_15

LEDR3

LEDR5

GPIO_113

GPIO_116

GPIO_115

GPIO_114

GPIO_025

GPIO_133

LEDR6

GPIO_134

GPIO_110

GPIO_112

GPIO_17

GPIO_18

GPIO_135

GPIO_13

GPIO_11

GPIO_12

GPIO_14

GPIO_16

AF20

AF21

Y18

AA19

AK23

AK24

AJ24

AJ25

AF23

AF24

AC20

AD19

AJ26

AK26

AG25

AH25

AE22

AE23

V18

W19

AJ27

AK27

AK28

AK29

AD20

AD21

Y19

AA20

AG26

AH27

AF25

AF26

AC22

AC23

AA21

AB21

AD24

AE24

5CSEMA5F31

5CSEMA5F31

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

FPGA BANK 3, BANK 4

Thursday, November 20, 2014

Rev

F

Sheet

1

of

30

LEDR[9..0]

3,19

HEX0[6..0]

HEX1[6..0]

HEX2[6..0]

HEX3[6..0]

HEX4[6..0]

HEX5[6..0]

7,19

7,19

6,19

7,19

19

6,19

Bank 5A

VCCIO = 3.3V

AG27

AH28

W20

Y21

AH29

W21

W22

AA25

AB26

AB22

AB23

AA24

AB25

AE27

AE28

Y23

Y24

AG28

AF28

V23

W24

AF29

AF30

AD26

AC27

AH30

AG30

IO_5A/RZQ_1/DIFFIO_TX_R1P/DQ1R

IO_5A/PR_REQUEST/DIFFIO_TX_R1N/DQ1R

IO_5A/DIFFIO_RX_R4P/DQ1R

IO_5A/DIFFIO_RX_R4N/DQ1R

IO_5A/CVP_CONFDONE/DIFFIO_TX_R3N/DQ1R

IO_5A/DIFFIO_RX_R6P/DQS1R

IO_5A/DIFFIO_RX_R6N/DQSN1R

IO_5A/DIFFIO_TX_R7P/DQ1R

IO_5A/DIFFIO_TX_R7N

IO_5A/DIFFIO_RX_R8P/DQ1R

IO_5A/DIFFIO_RX_R8N/DQ1R

IO_5A/DIFFIO_RX_R9P

IO_5A/DIFFIO_RX_R9N

IO_5A/DIFFIO_TX_R10P/DQ2R

IO_5A/DIFFIO_TX_R10N/DQ2R

IO_5A/DIFFIO_RX_R11P/DQ2R

IO_5A/DIFFIO_RX_R11N/DQ2R

IO_5A/DIFFIO_TX_R12P/DQ2R

IO_5A/DIFFIO_TX_R12N/DQ2R

IO_5A/DIFFIO_RX_R13P/DQS2R

IO_5A/DIFFIO_RX_R13N/DQSN2R

IO_5A/DIFFIO_TX_R14P

IO_5A/DIFFIO_TX_R14N/DQ2R

IO_5A/DIFFIO_RX_R15P/DQ2R

IO_5A/DIFFIO_RX_R15N/DQ2R

IO_5A/DIFFIO_TX_R16P/DQ2R

IO_5A/DIFFIO_TX_R16N

Bank 6

Bank 6B VCCIO

HPS_DDR3_ADDR[14..0] 15

HPS_DDR3_BA[2..0]

15

HPS_DDR3_DM[3..0]

15

HPS_DDR3_DQ[31..0]

Bank 5

U20-12

U20-11

HEX03

HEX06

LEDR7

LEDR9

HEX11

LEDR8

HEX43

HEX56

HEX54

HEX36

HEX20

HEX40

HEX35

HEX01

HEX02

HEX41

HEX42

HEX05

HEX04

HEX45

HEX44

HEX14

HEX15

HEX30

HEX31

HEX12

HEX13

Y29

V27

U25

T25

V28

U27

R24

W26

W27

T24

T23

15

VCCIO = 3.3V

HPS_DDR3_DQS_P[3..0]

15

Bank 5B

HPS_DDR3_DQS_N[3..0]

15

VCCIO = 3.3V

IO_5B/DIFFIO_RX_R17P

IO_5B/DIFFIO_RX_R17N

IO_5B/DIFFIO_TX_R18P/DQ3R

IO_5B/DIFFIO_TX_R18N/DQ3R

IO_5B/DIFFIO_RX_R19P/DQ3R

IO_5B/DIFFIO_RX_R19N/DQ3R

IO_5B/DIFFIO_TX_R20P/DQ3R

IO_5B/DIFFIO_TX_R20N/DQ3R

IO_5B/DIFFIO_TX_R24P/DQ3R

IO_5B/RZQ_2/DIFFIO_TX_R24N

W25

V25

AC28

AC29

AB30 21

AA30 21

AB28

AA28

AD30

AC30

HPS_DDR3_DQ31

HPS_DDR3_DQ30

HPS_DDR3_DQ29

HPS_DDR3_DQ28

HPS_DDR3_DQ27

HPS_DDR3_DQ26

HPS_DDR3_DQ25

HPS_DDR3_DQ24

HPS_DDR3_DM3

HPS_DDR3_DQS_P3

HPS_DDR3_DQS_N3

HEX46

HEX50

HEX23

HEX25

IRDA_TXD

IRDA_RXD

HEX34

HEX51

HEX24

HEX26

W29

V30

R26

R27

T28

T29

P25

P24

W30

R22

R21

15

P30

HPS_DDR3_ADDR14

HPS_DDR3_ADDR13

HPS_DDR3_ADDR12

HPS_DDR3_ADDR11

HPS_DDR3_ADDR10

HPS_DDR3_ADDR9

HPS_DDR3_ADDR8

HPS_DDR3_ADDR7

HPS_DDR3_ADDR6

HPS_DDR3_ADDR5

HPS_DDR3_ADDR4

HPS_DDR3_ADDR3

HPS_DDR3_ADDR2

HPS_DDR3_ADDR1

HPS_DDR3_ADDR0

G25

H25

C29

B30

C30

D29

G26

H27

E28

F29

J27

J25

F30

F28

G30

F26

HPS_DDR3_RESET_N

HPS_DDR/HPS_DQ_39

HPS_DDR/HPS_DQ_38

HPS_DDR/HPS_DQ_37

HPS_DDR/HPS_DQ_36

HPS_DDR/HPS_DQ_35

HPS_DDR/HPS_DQ_34

HPS_DDR/HPS_DQ_33

HPS_DDR/HPS_DQ_32

HPS_DDR/HPS_DM_4

HPS_DDR/HPS_DQS_4

HPS_DDR/HPS_DQSN_4

HPS_GPI13

HPS_GPI12

HPS_GPI11

HPS_GPI10

HPS_GPI9

HPS_GPI8

HPS_GPI7

HPS_GPI6

HPS_GPI5

HPS_GPI4

HPS_DDR/HPS_DQ_31

HPS_DDR/HPS_DQ_30

HPS_DDR/HPS_DQ_29

HPS_DDR/HPS_DQ_28

HPS_DDR/HPS_DQ_27

HPS_DDR/HPS_DQ_26

HPS_DDR/HPS_DQ_25

HPS_DDR/HPS_DQ_24

HPS_DDR/HPS_DM_3

HPS_DDR/HPS_DQS_3

HPS_DDR/HPS_DQSN_3

HPS_DDR/HPS_DQ_23

HPS_DDR/HPS_DQ_22

HPS_DDR/HPS_DQ_21

HPS_DDR/HPS_DQ_20

HPS_DDR/HPS_DQ_19

HPS_DDR/HPS_DQ_18

HPS_DDR/HPS_DQ_17

HPS_DDR/HPS_DQ_16

HPS_DDR/HPS_DM_2

HPS_DDR/HPS_DQS_2

HPS_DDR/HPS_DQSN_2

HPS_DDR3_CK_P

HPS_DDR3_CK_N

15

15

M23

L23

HPS_DDR3_CAS_N

HPS_DDR3_RAS_N

15

15

E27

D30

HPS_DDR3_BA2

HPS_DDR3_BA1

HPS_DDR3_BA0

R236

J23

J24

E29

HPS_DDR3_CS_N

15

H24

K21

HPS_DDR3_WE_N

15

C28

100

HPS_DDR3_RZQ

D27

Y28

V29

U20

T21

U28

T30

V20

P22

P29

N30

R29

N27

P27

P26

N28

N29

T26

U26

R28

R19

R18

HPS_DDR3_DQ23

HPS_DDR3_DQ22

HPS_DDR3_DQ21

HPS_DDR3_DQ20

HPS_DDR3_DQ19

HPS_DDR3_DQ18

HPS_DDR3_DQ17

HPS_DDR3_DQ16

HPS_DDR3_DM2

HPS_DDR3_DQS_P2

HPS_DDR3_DQS_N2

HPS_DDR/HPS_RESETN

Bank 6A VCCIO

5CSEMA5F31

= 1.5V

HPS_DDR/HPS_A_15

HPS_DDR/HPS_A_14

HPS_DDR/HPS_A_13

HPS_DDR/HPS_A_12

HPS_DDR/HPS_A_11

HPS_DDR/HPS_A_10

HPS_DDR/HPS_A_9

HPS_DDR/HPS_A_8

HPS_DDR/HPS_A_7

HPS_DDR/HPS_A_6

HPS_DDR/HPS_A_5

HPS_DDR/HPS_A_4

HPS_DDR/HPS_A_3

HPS_DDR/HPS_A_2

HPS_DDR/HPS_A_1

HPS_DDR/HPS_A_0

= 1.5V

HPS_GPI3

HPS_GPI2

HPS_GPI1

HPS_GPI0

HPS_DDR/HPS_DQ_15

HPS_DDR/HPS_DQ_14

HPS_DDR/HPS_DQ_13

HPS_DDR/HPS_DQ_12

HPS_DDR/HPS_DQ_11

HPS_DDR/HPS_DQ_10

HPS_DDR/HPS_DQ_9

HPS_DDR/HPS_DQ_8

HPS_DDR/HPS_DM_1

HPS_DDR/HPS_DQS_1

HPS_DDR/HPS_DQSN_1

HPS_DDR/HPS_CK

HPS_DDR/HPS_CKN

HPS_DDR/HPS_DQ_7

HPS_DDR/HPS_DQ_6

HPS_DDR/HPS_DQ_5

HPS_DDR/HPS_DQ_4

HPS_DDR/HPS_DQ_3

HPS_DDR/HPS_DQ_2

HPS_DDR/HPS_DQ_1

HPS_DDR/HPS_DQ_0

HPS_DDR/HPS_DM_0

HPS_DDR/HPS_DQS_0

HPS_DDR/HPS_DQSN_0

HPS_DDR/HPS_CASN

HPS_DDR/HPS_RASN

HPS_DDR/HPS_BA_2

HPS_DDR/HPS_BA_1

HPS_DDR/HPS_BA_0

HPS_DDR/HPS_CSN_0

HPS_DDR/HPS_CSN_1

HPS_DDR/HPS_ODT_0

HPS_DDR/HPS_ODT_1

HPS_DDR/HPS_WEN

HPS_RZQ_0

HPS_DDR/HPS_CKE_0

HPS_DDR/HPS_CKE_1

GND

M22

N23

J26

M25

M30

L28

M27

M26

K27

K29

L26

K26

M28

N25

N24

HPS_DDR3_DQ15

HPS_DDR3_DQ14

HPS_DDR3_DQ13

HPS_DDR3_DQ12

HPS_DDR3_DQ11

HPS_DDR3_DQ10

HPS_DDR3_DQ9

HPS_DDR3_DQ8

HPS_DDR3_DM1

HPS_DDR3_DQS_P1

HPS_DDR3_DQS_N1

J29

J30

L24

L25

G28

H30

K22

K23

K28

N18

M19

HPS_DDR3_DQ7

HPS_DDR3_DQ6

HPS_DDR3_DQ5

HPS_DDR3_DQ4

HPS_DDR3_DQ3

HPS_DDR3_DQ2

HPS_DDR3_DQ1

HPS_DDR3_DQ0

HPS_DDR3_DM0

HPS_DDR3_DQS_P0

HPS_DDR3_DQS_N0

H28

H29

15

HPS_DDR3_ODT

L29

L30

15

HPS_DDR3_CKE

5CSEMA5F31

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

FPGA BANK 5, BANK 6

Thursday, November 20, 2014

Rev

F

Sheet

1

of

30

HPS_ENET_RX_DATA[3..0]

23

23

HPS_ENET_TX_DATA[3..0]

TD_DATA[7..0]

VGA_G[7..0] 16

HPS_USB_DATA[7..0]

17

22

VGA_B[7..0]

HPS_FLASH_DATA[3..0]

VGA_R[7..0] 16

6,16

14

U20-14

Bank 8A VCCIO

U20-13

D

HPS_CLK_25

10,11,26

HPS_WARM_RST_N C27

HPS_RESET_N 10,26 F23 HPS_NRST

HPS_NPOR

HPS_CLOCK1_25 D25

HPS_CLK_25

HPS_CLOCK2_25 F25 HPS_CLK1

HPS_CLK2

10,11

JTAG_TRST

A28

R234

4.7K

VCC3P3

F24 HPS_TRST

R237

4.7K

HPS_PORSEL

HPS_TDO

HPS_TDI

HPS_TCK

HPS_TMS

11

11

11

11

B28

B27

H22

A29

HPS_TDO

HPS_TDI

HPS_TCK

HPS_TMS

Bank 7

Bank 7A

CAN0_TX,CLKSEL0/CAN0_TX/UART0_TX/SPIM1_SS0/HPS_GPIO66

CAN0_RX/UART0_RX/SPIM1_MISO/HPS_GPIO65

I2C0_SCL/UART1_TX/SPIM1_MOSI/HPS_GPIO64

I2C0_SDA/UART1_RX/SPIM1_CLK/HPS_GPIO63

UART0_TX,CLKSEL1/UART0_TX/CAN0_TX/SPIM1_SS1/HPS_GPIO62

UART0_RX/CAN0_RX/SPIM0_SS1/HPS_GPIO61

SPIM0_SS0,BOOTSEL0/SPIM0_SS0/CAN1_TX/UART1_RTS/HPS_GPIO60

SPIM0_MISO/CAN1_RX/UART1_CTS/HPS_GPIO59

SPIM0_MOSI/I2C1_SCL/UART0_RTS/HPS_GPIO58

SPIM0_CLK/I2C1_SDA/UART0_CTS/HPS_GPIO57

TRACE_D7/SPIS1_MISO/I2C0_SCL/HPS_GPIO56

TRACE_D6/SPIS1_SS0/I2C0_SDA/HPS_GPIO55

TRACE_D5/SPIS1_MOSI/CAN1_TX/HPS_GPIO54

TRACE_D4/SPIS1_CLK/CAN1_RX/HPS_GPIO53

TRACE_D3/SPIS0_SS0/I2C1_SCL/HPS_GPIO52

TRACE_D2/SPIS0_MISO/I2C1_SDA/HPS_GPIO51

TRACE_D1/SPIS0_MOSI/UART0_TX/HPS_GPIO50

TRACE_D0/SPIS0_CLK/UART0_RX/HPS_GPIO49

TRACE_CLK/HPS_GPIO48

Bank 7B

HPS_ENET_GTX_CLK 23 H19

HPS_ENET_TX_DATA0 F20

HPS_ENET_TX_DATA1 J19

HPS_ENET_TX_DATA2 F21

HPS_ENET_TX_DATA3 F19

HPS_ENET_RX_DATA0 A21

HPS_ENET_MDIO 23 E21

HPS_ENET_MDC 23 B21

HPS_ENET_RX_DV 23 K17

HPS_ENET_TX_EN 23 A20

HPS_ENET_RX_CLK 23 G20

HPS_ENET_RX_DATA1 B20

HPS_ENET_RX_DATA2 B18

HPS_ENET_RX_DATA3 D21

HPS_BOOTSEL2

D20

NAND_ALE/RGMII1_TX_CLK/QSPI_SS3/HPS_GPIO14

NAND_CE/RGMII1_TXD0/USB1_D0/HPS_GPIO15

NAND_CLE/RGMII1_TXD1/USB1_D1/HPS_GPIO16

NAND_RE/RGMII1_TXD2/USB1_D2/HPS_GPIO17

NAND_RB/RGMII1_TXD3/USB1_D3/HPS_GPIO18

NAND_DQ0/RGMII1_RXD0/HPS_GPIO19

NAND_DQ1/RGMII1_MDIO/I2C3_SDA/HPS_GPIO20

NAND_DQ2/RGMII1_MDC/I2C3_SCL/HPS_GPIO21

NAND_DQ3/RGMII1_RX_CTL/USB1_D4/HPS_GPIO22

NAND_DQ4/RGMII1_TX_CTL/USB1_D5/HPS_GPIO23

NAND_DQ5/RGMII1_RX_CLK/USB1_D6/HPS_GPIO24

NAND_DQ6/RGMII1_RXD1/USB1_D7/HPS_GPIO25

NAND_DQ7/RGMII1_RXD2/HPS_GPIO26

NAND_WP/RGMII1_RXD3/QSPI_SS2/HPS_GPIO27

NAND_WE,BOOTSEL2/NAND_WE/QSPI_SS1/HPS_GPIO28

Bank 7C

HPS_SD_CMD

B

24

HPS_SD_DATA0

HPS_SD_DATA1

HPS_LTC_GPIO

24

24

25

F18

B17

G18

C17

H17

C18

SDMMC_CMD/USB0_D0/HPS_GPIO36

SDMMC_PWREN/USB0_D1/HPS_GPIO37

SDMMC_D0/USB0_D2/HPS_GPIO38

SDMMC_D1/USB0_D3/HPS_GPIO39

SDMMC_D4/USB0_D4/HPS_GPIO40

SDMMC_D5/USB0_D5/HPS_GPIO41

A15

C15

E14

A14

RGMII0_TXD0/USB1_D0/HPS_GPIO1

RGMII0_TXD1/USB1_D1/HPS_GPIO2

RGMII0_TXD2/USB1_D2/HPS_GPIO3

RGMII0_TXD3/USB1_D3/HPS_GPIO4

D5

C4

VGA_G6

F11

VGA_G7

E11

E8

D7

J7 18 AUD_DACDAT

AUD_BCLK

H7 18

TD_DATA3

B2

TD_DATA1

B1

B6

B5

C3

TD_DATA7

B3

K1226 FPGA_I2C_SDAT

J12 26 FPGA_I2C_SCLK

TD_DATA0

D2

TD_DATA6

C2

VGA_G5

G12

VGA_G4

G11

E4

D4

AUD_ADCDAT

K7 18

K8 18 AUD_ADCLRCK

E3

TD_DATA2

E2

VGA_G3

G10

F10 16 VGA_BLANK_N

TD_DATA5

E1

TD_DATA4

D1

VGA_G1

J10

VGA_G0

J9

E7

E6

F9

F8

G7 18 AUD_XCK

F6 17 TD_RESET_N

5CSEMA5F31

VCCIO = 3.3V

B16 24 HPS_SD_DATA3

D17 24 HPS_SD_DATA2

A16 24 HPS_SD_CLK

E17

E18

R87

DNI 0 23,26 HPS_ENET_RESET_N

G17

R85

DNI 0 22

HPS_USB_RESET

Default Setting: BOOTSEL[2:0]=101 (Boot from SD CARD)

CLKSEL[1:0]=0

VCCIO = 3.3V

VCC3P3

RGMII0_TX_CLK/HPS_GPIO0

RGMII0_RX_CLK/USB1_CLK/HPS_GPIO10

RGMII0_RX_CTL/USB1_D7/HPS_GPIO8

RGMII0_RXD0/USB1_D4/HPS_GPIO5

RGMII0_RXD1/USB1_STP/HPS_GPIO11

RGMII0_RXD2/USB1_DIR/HPS_GPIO12

RGMII0_RXD3/USB1_NXT/HPS_GPIO13

C19 23 HPS_ENET_INT_N

D19 14 HPS_FLASH_DCLK

A18 14 HPS_FLASH_NCSO

HPS_FLASH_DATA3

E19

HPS_FLASH_DATA2

A19

HPS_FLASH_DATA1

H18

HPS_FLASH_DATA0

C20

= 3.3V

IO_8A/DIFFIO_TX_T2P/DQ1T

IO_8A/DIFFIO_TX_T22P

IO_8A/DIFFIO_TX_T2N/DQ1T

IO_8A/DIFFIO_TX_T22N/DQ3T

IO_8A/DIFFIO_RX_T3P/DQ1T

IO_8A/DIFFIO_RX_T23P/DQ3T

IO_8A/DIFFIO_RX_T3N/DQ1T

IO_8A/DIFFIO_RX_T23N/DQ3T

IO_8A/DIFFIO_RX_T5P/DQS1T

IO_8A/DIFFIO_TX_T24P/DQ3T

IO_8A/DIFFIO_RX_T5N/DQSN1T

IO_8A/DIFFIO_TX_T24N

IO_8A/DIFFIO_TX_T6P

IO_8A/DIFFIO_RX_T25P

IO_8A/DIFFIO_TX_T6N/DQ1T

IO_8A/DIFFIO_RX_T25N

IO_8A/DIFFIO_RX_T7P/DQ1T

IO_8A/DIFFIO_TX_T26P/DQ4T

IO_8A/DIFFIO_RX_T7N/DQ1T

IO_8A/DIFFIO_TX_T26N/DQ4T

IO_8A/DIFFIO_TX_T8P/DQ1T

IO_8A/DIFFIO_RX_T27P/DQ4T

IO_8A/DIFFIO_TX_T8N

IO_8A/DIFFIO_RX_T27N/DQ4T

IO_8A/DIFFIO_TX_T10P/DQ2T

IO_8A/DIFFIO_TX_T28P/DQ4T

IO_8A/DIFFIO_TX_T10N/DQ2T

IO_8A/DIFFIO_TX_T28N/DQ4T

IO_8A/DIFFIO_RX_T11P/DQ2T

IO_8A/DIFFIO_RX_T29P/DQS4T

IO_8A/DIFFIO_RX_T11N/DQ2T

IO_8A/DIFFIO_RX_T29N/DQSN4T

IO_8A/DIFFIO_TX_T12P/DQ2T

IO_8A/DIFFIO_TX_T30P

IO_8A/DIFFIO_TX_T12N/DQ2T

IO_8A/DIFFIO_TX_T30N/DQ4T

IO_8A/DIFFIO_RX_T13P/DQS2T

IO_8A/DIFFIO_RX_T31P/DQ4T

IO_8A/DIFFIO_RX_T13N/DQSN2T

IO_8A/DIFFIO_RX_T31N/DQ4T

IO_8A/DIFFIO_TX_T14P

IO_8A/DIFFIO_TX_T32P/DQ4T

IO_8A/DIFFIO_TX_T14N/DQ2T

IO_8A/DIFFIO_TX_T32N

IO_8A/DIFFIO_RX_T15P/DQ2T

IO_8A/DIFFIO_RX_T33P

IO_8A/DIFFIO_RX_T15N/DQ2T

IO_8A/DIFFIO_RX_T33N

IO_8A/DIFFIO_TX_T16P/DQ2T

IO_8A/DIFFIO_TX_T34P/DQ5T

IO_8A/DIFFIO_TX_T16N

IO_8A/DIFFIO_TX_T34N/DQ5T

IO_8A/DIFFIO_RX_T17P

IO_8A/DIFFIO_RX_T35P/DQ5T

IO_8A/DIFFIO_RX_T17N

IO_8A/DIFFIO_RX_T35N/DQ5T

IO_8A/DIFFIO_TX_T18P/DQ3T

IO_8A/DIFFIO_TX_T36P/DQ5T

IO_8A/DIFFIO_TX_T18N/DQ3T

IO_8A/DIFFIO_TX_T36N/DQ5T

IO_8A/DIFFIO_RX_T19P/DQ3T

IO_8A/DIFFIO_RX_T37P/DQS5T

IO_8A/DIFFIO_RX_T19N/DQ3T

IO_8A/DIFFIO_RX_T37N/DQSN5T

IO_8A/DIFFIO_TX_T20P/DQ3T

IO_8A/DIFFIO_TX_T38P

IO_8A/DIFFIO_TX_T20N/DQ3T

IO_8A/DIFFIO_TX_T38N/DQ5T

IO_8A/DIFFIO_RX_T21P/DQS3T

IO_8A/DIFFIO_RX_T39P/DQ5T

IO_8A/DIFFIO_RX_T21N/DQSN3T

IO_8A/DIFFIO_RX_T39N/DQ5T

IO_8A/DIFFIO_TX_T40P/DQ5T

IO_8A/DIFFIO_TX_T40N

RGMII0_TX_CTL/HPS_GPIO9

RGMII0_MDC/USB1_D6/I2C2_SCL/HPS_GPIO7

RGMII0_MDIO/USB1_D5/I2C2_SDA/HPS_GPIO6

F16

N16

SW16 DNI

22

HPS_USB_CLKOUT

24

HPS_CONV_USB_N

HPS_USB_DATA7

M17

B15

R105

R104

R103

R96

R95

1K

1K

1K

1K

1K

HPS_USB_DATA6

HPS_USB_DATA5

D15

C14

1

2

3

4

5

6

ON

HPS_USB_DATA4

HPS_USB_STP

22

HPS_USB_DIR

22

HPS_USB_NXT

22

QSPI_SS1/HPS_GPIO35

QSPI_CLK/HPS_GPIO34

QSPI_SS0,BOOTSEL1/QSPI_SS0/HPS_GPIO33

QSPI_IO3/USB1_NXT/HPS_GPIO32

QSPI_IO2/USB1_DIR/HPS_GPIO31

QSPI_IO1/USB1_STP/HPS_GPIO30

QSPI_IO0/USB1_CLK/HPS_GPIO29

B13

A13

C13

B12

F15

F14

C12

16 B11

16 D11

D10

A9

A8

C7

B7

E9

D9

C8

B8

VGA_B4

H14

VGA_B1

G13

VGA_SYNC_N 16 C10

C9

VGA_R7

F13

VGA_R2

E13

A6

TD_HS

17 A5

AUD_DACLRCK 18 H8

G8

A4

TD_VS

17 A3

VGA_R6

E12

VGA_R5

D12

D6

C5

VGA_B2

H13

VGA_G2

H12

12

11

10

9

8

7

E16

G16

D16

D14

D24 25 HPS_SPIM_SS

E24 25 HPS_SPIM_MISO

D22 25 HPS_SPIM_MOSI

C23 25 HPS_SPIM_CLK

G22 HPS_CLOCKSEL1

B22 25 HPS_GSENSOR_INT

H20 HPS_BOOTSEL0

B23

C22

A23

E23 25,26 HPS_I2C1_SCLK

C24 25,26 HPS_I2C1_SDAT

G21

26

HPS_KEY

A24

26 HPS_LED

H23 25 HPS_I2C2_SCLK

A25 25 HPS_I2C2_SDAT

C25 24 HPS_UART_TX

B25 24 HPS_UART_RX

B26 26 HPS_I2C_CONTROL

VCCIO = 3.3V

SDMMC_D3/USB0_NXT/HPS_GPIO47

SDMMC_D2/USB0_DIR/HPS_GPIO46

SDMMC_CCLK_OUT/USB0_STP/HPS_GPIO45

SDMMC_FB_CLK_IN/USB0_CLK/HPS_GPIO44

SDMMC_D7/USB0_D7/HPS_GPIO43

SDMMC_D6/USB0_D6/HPS_GPIO42

Bank 7D

HPS_USB_DATA0

HPS_USB_DATA1

HPS_USB_DATA2

HPS_USB_DATA3

VCCIO = 3.3V

VGA_B0

VGA_R0

VGA_R1

VGA_R3

VGA_B5

VGA_B3

VGA_R4

VGA_HS

VGA_VS

HPS_BOOTSEL0

HPS_FLASH_NCSO

HPS_BOOTSEL2

HPS_SPIM_SS

HPS_CLOCKSEL1

(BOOTSEL0) R108

(BOOTSEL1) R107

(BOOTSEL2) R106

(CLOCKSEL0)R98

(CLOCKSEL1)R97

HPS_BOOTSEL0

HPS_FLASH_NCSO

HPS_BOOTSEL2

HPS_SPIM_SS

HPS_CLOCKSEL1

(BOOTSEL0)

(BOOTSEL1)

(BOOTSEL2)

(CLOCKSEL0)

(CLOCKSEL1)

10K

10K DNI

10K

10K DNI

10K DNI

SW-DIP12

DNI R111

R110

DNI R109

R100

R99

5CSEMA5F31

1K

1K

1K

1K

1K

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

FPGA BANK 7, BANK 8

Thursday, November 20, 2014

Rev

F

Sheet

1

of

30

U20-7

U20-6

J22

D26

A26

J6

J2

J1

L2

L1

N2

N1

P9

P8

T8

T9

R2

R1

U2

U1

W2

W1

AA2

AA1

AC2

AC1

AE2

AE1

W8

W7

A12

A17

A2

A22

A27

AA11

AA22

AA3

AA4

AA6

AA9

AB1

AB19

AB2

AB29

AB5

AB7

AC16

AC26

AC3

AC4

AC6

AC8

AD1

AD2

AD23

AD5

AE10

AE20

AE3

AE4

AF1

AF12

U20-2

Clocks

D

CLOCK_50

AF14

DRAM_ADDR7 AF15

W15

KEY2

Y16

KEY3

CLOCK2_50

GPIO_10

GPIO_00

GPIO_02

AA16

AB17

AC18

AD17

CLOCK3_50

HEX52

HEX55

HEX53

Y26

Y27

AA26

AB27

CLOCK4_50

VGA_B7

TD_CLK27

VGA_B6

K14

J14

17 H15

G15

Bank 3B VCCIO = 3.3V

IO_3B/CLK0P,FPLL_BL_FBP/DIFFIO_RX_B31P

IO_3B/CLK0N,FPLL_BL_FBN/DIFFIO_RX_B31N

IO_3B/CLK1P/DIFFIO_RX_B39P

IO_3B/CLK1N/DIFFIO_RX_B39N

IO_3B/FPLL_BL_CLKOUT0,FPLL_BL_CLKOUTP,FPLL_BL_FB/DIFFIO_TX_B37P/DQ5B/B_A_2

IO_3B/FPLL_BL_CLKOUT1,FPLL_BL_CLKOUTN/DIFFIO_TX_B37N/DQ5B/B_A_3

AH12

AJ12

14 DRAM_CLK

14 DRAM_BA1

Bank 4A VCCIO = 3.3V

IO_4A/CLK2P/DIFFIO_RX_B47P

IO_4A/CLK2N/DIFFIO_RX_B47N

IO_4A/CLK3P/DIFFIO_RX_B55P

IO_4A/CLK3N/DIFFIO_RX_B55N

Bank 5B VCCIO = 3.3V

IO_5B/CLK4P,FPLL_BR_FBP/DIFFIO_RX_R23P/DQ3R

IO_5B/CLK4N,FPLL_BR_FBN/DIFFIO_RX_R23N/DQ3R

IO_5B/CLK5P/DIFFIO_RX_R21P/DQS3R

IO_5B/CLK5N/DIFFIO_RX_R21N/DQSN3R

IO_5B/FPLL_BR_CLKOUT0,FPLL_BR_CLKOUTP,FPLL_BR_FB/DIFFIO_TX_R22P

IO_5B/FPLL_BR_CLKOUT1,FPLL_BR_CLKOUTN/DIFFIO_TX_R22N/DQ3R

Bank 8A VCCIO = 3.3V

IO_8A/CLK6P,FPLL_TL_FBP/DIFFIO_RX_T9P

IO_8A/CLK6N,FPLL_TL_FBN/DIFFIO_RX_T9N

IO_8A/CLK7P/DIFFIO_RX_T1P

IO_8A/CLK7N/DIFFIO_RX_T1N

IO_8A/FPLL_TL_CLKOUT0,FPLL_TL_CLKOUTP,FPLL_TL_FB/DIFFIO_TX_T4P/DQ1T

IO_8A/FPLL_TL_CLKOUT1,FPLL_TL_CLKOUTN/DIFFIO_TX_T4N/DQ1T

AE29

AD29

A11

A10

HEX21

HEX22

16

VGA_CLK

5CSEMA5F31

VGA_B[7..0]

5,16

DRAM_ADDR[12..0] 3,14

3,20

3,12

GPIO_1[35..0]

3,13

HEX2[6..0]

HEX5[6..0]

4,19

4,19

VCC3P3

VDDOA

VDDOB

VDDOC

VDDOD

VDD

U12

11

10

18

14

20

GPIO_0[35..0]

VCC3P3

C53

3

4

5

7

Y2

1

0.1u

2

EN

VCC

GND

OUT

4

3

R60

25.00MHz

CLK2

CLK3

CLK4

CLK5

CLKIN

XA

XB

21

CLK0

CLK1

GND

GND

GND

GND

GND_EP

KEY[3..0]

CLK6

CLK7

CLOCK_50

CLOCK2_50

13

12

9

8

19

17

23

ENET_CLK_25

CLOCK3_50

16

15

22

22

USBPHY_CLK_24

USBHUB_CLK_24

HPS_CLK_25

CLOCK4_50

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AF17

AF2

AF27

AF3

AG14

AG24

AG9

AH1

AH11

AH21

AH6

AJ18

AJ28

AJ3

AJ30

AK15

AK25

AK5

B14

B19

B24

B29

B9

C1

C16

C21

C26

C6

D13

D23

D3

E10

E25

E30

F17

F2

F27

F5

F7

G24

G3

G4

H1

H11

H2

H5

J18

J28

J3

J4

J8

K1

K10

K15

K2

K20

K25

K5

L11

L13

L15

L17

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

L19

L22

L3

L4

L6

M1

M10

M12

M14

M16

M18

M2

M20

M29

M5

M7

M8

N11

N13

N15

N17

N19

N26

N3

N4

N6

N8

N9

P1

P10

P12

P14

P16

P18

P2

P20

P5

P7

R11

R13

R15

R17

R3

R30

R4

R6

R8

R9

T1

T10

T12

T14

T15

T16

T2

T20

T27

T5

T7

U11

U13

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DNU_1

DNU_2

DNU_3

DNU_4

DNU_5

DNU_6

DNU_7

DNU_8

DNU_9

DNU_10

DNU_11

DNU_12

DNU_13

DNU_14

DNU_15

DNU_16

DNU_17

DNU_18

DNU_19

DNU_20

DNU_21

DNU_22

DNU_23

DNU_24

GND

5CSEMA5F31

U15

U17

U24

U29

U3

U4

U6

U9

V1

V10

V12

V14

V19

V2

V21

V5

V7

W11

W13

W18

W28

W3

W4

W6

W9

Y1

Y10

Y12

Y14

Y15

Y2

Y20

Y25

Y30

Y5

Y7

Y8

U22

T18

F1

G2

H3

H4

K3

K4

M3

M4

P3

P4

T3

T4

V3

V4

Y3

Y4

AB3

AB4

AD3

AD4

AA7

AD15

E26

J15

5CSEMA5F31

Si5350C-B02330-GM

U20-8

Reference pin

RREF_TL

G1

VCC3P3

5CSEMA5F31

C179

C187

C186

C173

C185

0.47u

0.47u

0.47u

0.47u

0.47u

R240

2K

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

FPGA Clocks & GND

Thursday, November 20, 2014

Rev

F

Sheet

1

of

30

USB Blaster

11

11

11

11

VCC12

HEX0[6..0]

HEX1[6..0]

HEX3[6..0]

R142

1K

U20-1

VCC3P3

Configuration

Design Note:

Optional termination resistor

for DCLK

R147

CAD Note:

Place near FPGA DCLK pin

C82

12p

50V

DNI

R146

10K

DNI

0

DNI

R145

1K

DNI

AC5

V9

AB9

U8

U7

EPCQ_AS_DATA0

AE6

EPCQ_AS_DATA1

AE5

EPCQ_AS_DATA2

AE8

EPCQ_AS_DATA3

AC7

EPCQ_NCSO

AB8

PS2_DAT2

21 AE9

AE12

SW9

PS2_CLK2

21 AD9

AD11

SW4

AF10

SW3

AD10

SW8

AE11

SW6

AC9

SW7

USB_B2_DATA0

AH4

PS2_DAT

21 AE7

USB_B2_DATA5

AG3

PS2_CLK

21 AD7

10K FPGA_CONF_DONE F3

F4

10K FPGA_NSTATUS

J5

10K FPGA_NCONFIG

G5

Bank 3A VCCIO = 3.3V

TCK

TMS

TDO

TDI

DCLK

3

D99

IO_5A/INIT_DONE/DIFFIO_RX_R2P

IO_5A/CRC_ERROR/DIFFIO_RX_R2N

AS_DATA0,ASDO/DATA0

AS_DATA1/DATA1

AS_DATA2/DATA2

AS_DATA3/DATA3

NCSO/DATA4

IO_3A/DATA5/DIFFIO_TX_B2N

IO_3A/DATA6/DIFFIO_RX_B1N/DQ1B

IO_3A/DATA7/DIFFIO_TX_B2P/DQ1B

IO_3A/DATA8/DIFFIO_RX_B1P/DQ1B

IO_3A/DATA9/DIFFIO_TX_B4N/DQ1B

IO_3A/DATA10/DIFFIO_RX_B3N/DQSN1B

IO_3A/DATA11/DIFFIO_TX_B4P

IO_3A/DATA12/DIFFIO_RX_B3P/DQS1B

IO_3A/DATA13/DIFFIO_TX_B6N/DQ1B

IO_3A/DATA14/DIFFIO_RX_B5N/DQ1B

IO_3A/DATA15/DIFFIO_TX_B6P/DQ1B

IO_3A/CLKUSR/DIFFIO_RX_B5P/DQ1B

CONF_DONE

NSTATUS

NCONFIG

NCE

FAN_CTRL

Bank 5A VCCIO = 3.3V

IO_5A/DEV_OE/DIFFIO_TX_R5P

IO_5A/NCEO/DIFFIO_TX_R3P/DQ1R

IO_5A/DEV_CLRN/DIFFIO_TX_R5N/DQ1R

AD25

Power - FAN

Q5

FDV305N

DNI

HEX32

AC25

HEX33

AE26

HEX00

AJ29

HEX10

AD27

HEX16

SM2T3V3A 3.3V

200W

DNI

Fix MSEL[4:0]=10010 in AS Fast Mode

VCC3P3_PGM

SW10

Bank 9A

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

10

L8

K6

G6

L7

L9

1

2

3

4

5

6

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

ON

R118

R117

R119

JTAG_TCK

JTAG_TMS

FPGA_TDO

FPGA_TDI

EPCQ_DCLK

VCC3P3_PGM

FPGA_NCONFIG

J16 DNI

3

2

1

3

C73

33p

50V

DNI

JTAG_TCK

0

DNI

R141

4,19

4,19

4,19

FPGA_TDI

JTAG_TMS

JTAG_TCK

FPGA_TDO

12

11

10

9

8

7

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

R136

R135

R122

R121

R120

1K

1K

1K

1K

1K

SW-DIP12

R138

R137

R125

R124

R123

5CSEMA5F31

FPGA_CONF_DONE 10

0

0

0

0

0

DNI

DNI

DNI

DNI

DNI

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

USB_B2_DATA[7..0] 3,10

B

SW[9..0]

3,20

VCC

NC01

NC02

NC03

NC04

NC05

NC06

NC07

NC08

10

C105

0.1u

10V

3

4

5

6

11

12

13

14

GND

U40

VCC3P3

VCC3P3

DATA0

DATA1

DATA2

DATA3

DCLK

nCS

EPCQ_AS_DATA0

EPCQ_AS_DATA1

EPCQ_AS_DATA2

EPCQ_AS_DATA3

EPCQ_DCLK

EPCQ_NCSO

15

8

9

1

16

7

S25FL128SAGMFI011

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

FPGA Configuration

Thursday, November 20, 2014

Rev

F

Sheet

1

of

30

FPGA VCCINT

VCCINT_FPGA

C310

C340

C344

C274

C339

C321

C346

C348

0.01u

0.01u

0.01u

0.01u

0.01u

0.01u

0.01u

0.01u

C383

C264

C239

C350

C205

C240

C294

C293

C276

C343

C334

C289

C285

C318

100u

6.3V

1u

0.47u

0.1u

47n

22n

0.01u

0.01u

0.01u

0.01u

0.01u

4.7n

4.7n

4.7n

HPS VCC3P3(BANK 7)

VCC3P3

Panasonic

6TPE100MPB

VCCINT_FPGA

C322

C278

0.01u

C341

0.01u

C320

0.01u

C284

0.01u

0.01u

C292

C272

0.01u

0.01u

C200

C199

C257

C256

C238

C255

100u

6.3V

1u

0.1u

22n

0.01u

0.1u

VCCA_FPLL

0.01u

C337

C288

C282

C295

C290

C338

C347

0.01u

0.01u

0.01u

0.01u

0.01u

0.01u

0.01u

0.01u

VCC3P3

Panasonic

6TPE100MPB

C316

C313

C315

C312

C287

C277

C280

C279

4.7n

4.7n

4.7n

4.7n

4.7n

4.7n

4.7n

4.7n

C283

C311

C281

C336

C275

C314

C291

C317

4.7n

4.7n

4.7n

4.7n

4.7n

4.7n

4.7n

4.7n

C377

C367

C365

C259

C364

C260

C369

C362

C332

100u

6.3V

2.2u

0.47u

0.22u

0.1u

47n

22n

0.01u

4.7n

4.7n

C371

C359

C196

C331

C330

C195

C361

C270

C253

C268

C273

C308

100u

6.3V

4.7u

0.47u

0.1u

47n

22n

22n

0.01u

0.01u

0.01u

4.7n

4.7n

VCCINT_FPGA

C386

C384

C351

C203

C385

C381

C202

C204

C379

4.7n

4.7n

4.7n

4.7n

4.7n

22n

22n

22n

22n

22n

22n

VCCINT_FPGA

VCCINT_FPGA

C210 C201 C375 C211 C387

C208 C209 C380 C372 C376 C227 C226 C370 C388

47n

0.1u

47n

0.1u

0.1u

C258 C333

C368

0.1u

22n

4.7n

0.1u

0.1u

VCC_AUX

C198 C197

C366

C363

C271

4.7u

1u

0.01u

0.1u

1u

HPS 1.5V(BANK 6)

C262

47n

C261

0.01u

HPS VCC2P5(BANK 6)

C349

47n

C319

4.7n

VCC2P5

Panasonic

6TPE100MPB

VCCINT_FPGA

47n

C345

VCC_AUX_SHARED

C378

VCCINT_FPGA

VCCINT_FPGA

VCC3P3_PGM

Place C394 close to J20/G23 pin

FPGA VCC3P3(BANK 3, 4, 5, 8)

C286

VCCBAT

C342

VCCINT_FPGA

VCC1P1_HPS

Panasonic

6TPE100MPB

0.22u 0.22u 0.47u 1u

VCC1P5_DDR3

Panasonic

2R5TPE330MAZB

C360

330u

2.5V

C328

C329

C267

C305

C269

4.7u

0.47u

0.22u

0.1u

47n

C237

C251

C307

C252

C306

0.01u

0.01u

0.01u

0.01u

0.01u

2.2u

C335

C254

C265

C309

C304

C266

4.7n

4.7n

4.7n

4.7n

22n

22n

VCCINT_FPGA

Panasonic

6TPE100MPB

C373 C207 C389 C296 C382 C263 C206

100u

6.3V

100u

6.3V

100u

6.3V

100u

6.3V

10u

10u

10u

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

FPGA Decoupling

Wednesday, May 27, 2015

Rev

F

Sheet

1

of

30

U20-4

Power

VCCINT_FPGA

VCC3P3

0

VCC2P5

L24

VCC3P3_PGM

R246

VCCBAT

M11

M13

M9

N10

N12

N14

P11

P13

R10

R12

R14

T11

T13

U10

U12

U14

V11

V13

V15

W10

W12

W14

Y11

Y13

Y9

L5

R5

W5

AA5

M6

N5

T6

U5

U21

Y6

J11

AA23

AB10

BEAD

H9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCPGM

VCCPGM

VCCPGM

U20-5

VCCPD3A

VCCPD3A

VCCPD3B4A

VCCPD3B4A

VCCPD3B4A

VCCPD3B4A

VCCPD3B4A

VCCPD3B4A

VCCPD3B4A

VCCPD3B4A

VCCPD5A

VCCPD5A

VCCPD5B

VCCPD8A

VCCPD8A

VCCPD8A

VCCPD8A

VCCPD8A

VCCA_FPLL

VCCA_FPLL

VCCA_FPLL

VCCA_FPLL

VCCA_FPLL

VCCA_FPLL

VCCA_FPLL

VCCA_FPLL

VCCA_FPLL

VCC_AUX

VCC_AUX

VCC_AUX

VCC_AUX

VCC_AUX

VCC_AUX_SHARED

AA10

AC10

Power - VCCIO

VCC3P3

VCC3P3

AC15

AB18

AC13

AB20

AC17

AC19

AD16

AE21

AC11

AD8

AF7

AG4

AD6

AB14

AD13

AE15

AJ13

AJ8

AK10

V22

V24

U23

AJ15

K11

K13

L10

L12

L14

VCCA_FPLL

N7

R7

V8

AA8

K9

Y22

AB6

P6

V6

AB11

AB16

AD22

H10

J16

L26

AA17

AC21

AD18

AE25

AF22

AG19

AH16

AH26

AK20

AJ23

AK17

VCC2P5

BEAD

VCC_AUX

W23

AG29

AD28

AB24

VCC2P5

L25

BEAD

AC24

VCC_AUX_SHARED

VCCIO3A

VCCIO3A

VCCIO3A

VCCIO3A

VCCIO5B

VCCIO5B

VREFB5BN0

VREFB3AN0

VCCIO8A

VCCIO8A

VCCIO8A

VCCIO8A

VCCIO8A

VCCIO8A

VCCIO8A

VCCIO8A

VCCIO8A

VCCIO8A

VCCIO3B

VCCIO3B

VCCIO3B

VCCIO3B

VCCIO3B

VCCIO3B

VREFB3BN0

VCCIO4A

VCCIO4A

VCCIO4A

VCCIO4A

VCCIO4A

VCCIO4A

VCCIO4A

VCCIO4A

VCCIO4A

VCCIO4A

VREFB4AN0

VREFB8AN0

AA27

AE30

VCC3P3

AA29

D

A7

B4

C11

D8

E5

F12

G14

G9

H6

J13

B10

VCCIO5A

VCCIO5A

VCCIO5A

VCCIO5A

VREFB5AN0

VCC2P5

5CSEMA5F31

J21

L23

BEAD

VCCBAT

5CSEMA5F31

U20-3

HPS Power

VCC1P1_HPS

B

VCC1P5_DDR3

DDR3_VREF_HPS

U16

T19

T17

R16

P19

P17

P15

N20

M15

L20

L18

L16

U18

D28

G29

H26

K24

K30

L27

M24

N21

G27

P23

P28

R25

T22

U19

V26

U30

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCC_HPS

VCCIO6A_HPS

VCCIO6A_HPS

VCCIO6A_HPS

VCCIO6A_HPS

VCCIO6A_HPS

VCCIO6A_HPS

VCCIO6A_HPS

VCCIO6A_HPS

VREFB6AN0_HPS

VCCIO6B_HPS

VCCIO6B_HPS

VCCIO6B_HPS

VCCIO6B_HPS

VCCIO6B_HPS

VCCIO6B_HPS

VREFB6BN0_HPS

VCCIO7A_HPS

VCCIO7A_HPS

VCCIO7B_HPS

VCCIO7B_HPS

VCCIO7C_HPS

VCCIO7D_HPS

VCCIO7D_HPS

VREFB7A7B7C7DN0_HPS

VCCPD6A6B_HPS

VCCPD6A6B_HPS

VCCPD6A6B_HPS

VCCPD6A6B_HPS

VCCPD6A6B_HPS

VCCPD7A_HPS

VCCPD7B_HPS

VCCPD7C_HPS

VCCPD7D_HPS

H21

F22

G19

E20

D18

H16

E15

E22

VCC3P3

M21

N22

P21

R20

R23

VCC2P5

K19

K18

J17

K16

VCC3P3

VCC_AUX

VCCPLL_HPS

VCCRSTCLK_HPS

VCCRSTCLK_HPS

L21

VCC3P3

G23

J20

A

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

5CSEMA5F31

Size

B

Date:

5

Document Number

FPGA Power

Thursday, November 20, 2014

Rev

F

Sheet

1

of

30

U17D

FX2_SDA

J13

FX2_D_P

FX2_D_N

3

2

VBUS_VCC5

1

4

C67

D-

R116

MAX_SDA

J7

C_USB_MAX_TDI

C_USB_MAX_TCK

C_USB_MAX_TMS

C_USB_MAX_TDO

H2

H3

J1

J2

D+

VCC3P3

USB B-TYPE

C192

0.1u

0.1u

3

1M

D+

D-

GND

1

2

FX2_RESETn R229

MR_n RST_n

C_USB_MAX_TCK

C_USB_MAX_TDI

C_USB_MAX_TDO

C_USB_MAX_TMS

100K

U16

D1

D2

VCC3P3

G1

A5

B5

C5

E7

E8

4.7n

C66

R112

1K

0.1u

E1

E2

Y3

1

OE/FS

VDD

4

USB_B2_CLK

GND

CLK

CLK_24M

OSC_24MHz

VBUS_VCC5 R93

FX2_PA1

FX2_PA2

FX2_PA3

FX2_PA4

FX2_PA5

FX2_PA6

FX2_PA7

FX2_WAKEUP

10K

R92

20K

C61

0.1u

G2

C1

C2

G8

G6

F8

F7

F6

C8

C7

C6

H2

F1

F2

VCC3P3

R232

120

D5

2

LEDG

1

JTAG_RX

R233

120

D4

2

LEDG

1

JTAG_TX

R230

DNI

120

D7 DNI

2

LEDG

1

SC_RX

R231

DNI

120

D6 DNI

2

LEDG

1

SC_TX

JTAG INTERFACE

CLK_24M

JTAG_Blaster_TCK

JTAG_Blaster_TMS

JTAG_Blaster_TDO

JTAG_Blaster_TDI

11

11

11

11

R80

R77

R78

R79

0

0

0

0

FX2_PD0

FX2_PD2

FX2_PD3

FX2_PD1

ADM6711SAKSZ

VCC3P3

TPD2EUSB30

C60

FX2_RESETn

GND

U39

R91

GCLK0p

GCLK1p

GCLK2p

GCLK3p

K9

USB_B2_CLK

E2

FX2_PB7

E1

F8

R285

E10

DNI

EPM570GF100C5N

VCC

FX2_D_N

FX2_D_P

DEV_CLRn

TDI

TCK

TMS

TDO

VBUS GND

U14

D

DEV_OE

MAX_SDA

H1

A4

B4

C4

D7

D8

U17B

VCC3P3

AVCC

AVCC

RESET

SCL

SDA

VCC

VCC

VCC

VCC

VCC

VCC

WAKEUP

CTL0

CTL1

CTL2

DMINUS

DPLUS

RDY0

RDY1

IFCLK

XTALIN

XTALOUT

CLKOUT

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

RESERVED

AGND

AGND

GND

GND

GND

GND

GND

GND

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

B8

F3

G3

FX2_RESETn

FX2_SCL

FX2_SDA

B7

FX2_WAKEUP

H7

G7

H8

FX2_FLAGA

FX2_FLAGB

FX2_FLAGC

A1

B1

FX2_SLRDn

FX2_SLWRn

R114

R115

2K

2K

FX2_PA2

FX2_FLAGC

FX2_PA7

FX2_FLAGA

FX2_PA3

FX2_PA4

FX2_PB4

FX2_PA6

FX2_PB2

FX2_FLAGB

FX2_PB0

FX2_PA1

FX2_PB5

USB_DISABLE_n

FX2_PB6

B2

FX2_PB0

FX2_PB1

FX2_PB2

FX2_PB3

FX2_PB4

FX2_PB5

FX2_PB6

FX2_PB7

H3

F4

H4

G4

H5

G5

F5

H6

IO_B1_H8

IO_B1_J3

IO_B1_J4

IO_B1_J5

IO_B1_J6

IO_B1_J8

IO_B1_J9

IO_B1_K1

IO_B1_K2

IO_B1_K3

IO_B1_K4

IO_B1_K5

IO_B1_K6

IO_B1_K7

IO_B1_K8

IO_B1_K10

H8

J3

J4

J5

J6

J8

J9

K1

K2

K3

K4

K5

K6

K7

K8

K10

FX2_PB1

FX2_PB3

FX2_SCL

FX2_PD6

FX2_PD4

11

USB_RESET_n

USB_OE_n

USB_RD_n

USB_WR_n

SC_RX

SC_TX

USB_B2_DATA0

USB_B2_DATA1

USB_B2_DATA2

USB_B2_DATA3

USB_B2_DATA4

A1

A2

A3

A4

A7

B8

D10

D9

A9

A10

B2

B3

B4

B5

B9

C9

C8

B7

C7

USB_DISABLE_n

VCC1P8

FX2_SLWRn

FX2_SLRDn

FX2_PD7

FX2_PD5

FX2_PA5

JTAG_Blaster_TDO

JTAG_Blaster_TMS

JTAG_Blaster_TDI

JTAG_Blaster_TCK

R130

0

U17A

C5

E6

F5

H5

D5

D7

E5

F6

G5

G7

GNDINT

GNDINT

GNDINT

GNDINT

VCCINT

VCCINT

VCCINT

VCCINT

GNDIO

GNDIO

GNDIO

GNDIO

GNDIO

GNDIO

VCCIO1

VCCIO1

VCCIO1

VCCIO2

VCCIO2

VCCIO2

C6

E7

F4

H6

VCC3P3

C

E4

G4

G6

VCC3P3

D4

D6

F7

EPM570GF100C5N

U17C

JTAG_TX

JTAG_RX

FX2_PD0

FX2_PD1

FX2_PD2

FX2_PD3

FX2_PD4

FX2_PD5

FX2_PD6

FX2_PD7

A8

A7

B6

A6

B3

A3

C3

A2

JTAG Control for USB Blaster II

IO_B1_B1

IO_B1_C1

IO_B1_C2

IO_B1_D1

IO_B1_D2

IO_B1_D3

IO_B1_E3

IO_B1_F1

IO_B1_F2

IO_B1_F3

IO_B1_G1

IO_B1_G2

IO_B1_G3

IO_B1_H1

IO_B1_H4

IO_B1_H7

EPM570GF100C5N

CY7C68013A-56BAXC

VCC3P3

B1

C1

C2

D1

D2

D3

E3

F1

F2

F3

G1

G2

G3

H1

H4

H7

IO_B2_A1

IO_B2_A2

IO_B2_A3

IO_B2_A4

IO_B2_A7

IO_B2_B8

IO_B2_D10

IO_B2_D9

IO_B2_A9

IO_B2_A10

IO_B2_B2

IO_B2_B3

IO_B2_B4

IO_B2_B5

IO_B2_B9

IO_B2_C9

IO_B2_C8

IO_B2_B7

IO_B2_C7

IO_B2_C3

IO_B2_C4

IO_B2_A6

IO_B2_F10

IO_B2_F9

IO_B2_B10

IO_B2_E8

IO_B2_C10

IO_B2_D8

IO_B2_B6

IO_B2_E9

IO_B2_A8

IO_B2_A5

IO_B2_G8

IO_B2_G9

IO_B2_G10

IO_B2_H9

IO_B2_H10

IO_B2_J10

C3

C4

5,11,26

USB_B2_DATA7

A6

USB_B2_DATA5

F10

USB_B2_DATA6

F9

B10

R94

0

E8

0

DNI R297

C10

DNI

USB_FULL

D8

USB_EMPTY

B6

E9

USB_SCL

A8

USB_SDA

A5

FPGA_NCONFIG

G8 DNI R286

0

FPGA_CONF_DONE

G9 DNI R287

0

G10

HPS_RESET_N

H9

R288

0

H10

QSPI_RESET_N

J10

R289

0

HPS_WARM_RST_N

5,11

JTAG_TRST

FPGA_NCONFIG

FPGA_CONF_DONE

5,26

HPS_RESET_N

14

QSPI_RESET_N

EPM570GF100C5N

Place Near CY7C68013A

Place near MAX II

USB_B2_CLK

VCC3P3

C214

0.1u

USB_B2_CLK

USB_RESET_n

USB_OE_n

USB_RD_n

USB_WR_n

A

USB_SCL

USB_FULL

USB_EMPTY

USB_SDA

3

3

3

3

3

USB_B2_DATA[7..0]

C231

0.1u

C229

0.1u

C230

0.1u

C213

0.1u

C215

0.1u

C212

0.1u

CLK_24M

R102

VCC3P3

VCC3P3

R113

0

DNI

C243

0.1u

C245

0.1u

C242

0.1u

C244

0.1u

C241

0.1u

C228

0.1u

VCC3P3

2K

2K

2K

2K

J18

R75

1K

R76

1K

C_USB_MAX_TCK

C_USB_MAX_TDO

C_USB_MAX_TMS

C_USB_MAX_TDI

3,7

1

3

5

7

9

2

4

6

8

10

C68

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

33p

DNI

Title

DE1-SoC Board

DNI CPLD ISP

Size

B

CPLD ISP

Date:

5

VCC1P8

0

DNI

R133

R132

R131

R134

3

3

3

3

C232

0.1u

VCC3P3

Document Number

USB Blaster II

Thursday, November 20, 2014

Rev

F

Sheet

1

10

of

30

DNI

JTAG_Blaster_TDO R126

USB Blaster

JTAG_Blaster_TCK

JTAG_Blaster_TMS

JTAG_Blaster_TDO

JTAG_Blaster_TDI

10

10

10

10

FPGA_TDI

JTAG_Blaster_TMS R127

JTAG_TMS

JTAG_Blaster_TCK

R129

JTAG_TCK

JTAG_Blaster_TDI

R128

JTAG_TDI

FPGA_TDI

R294

JTAG_TDI

R243

JTAG_TCK

JTAG_TMS

FPGA_TDO

DNI

FPGA JTAG INTERFACE

FPGA_TDI

JTAG_TMS

JTAG_TCK

FPGA_TDO

7

7

7

7

VCC3P3

VCC3P3

VCC3P3

JTAG_Blaster_TDI

R6

1K

HPS JTAG INTERFACE

HPS_TCK

HPS_TMS

HPS_TDI

HPS_TDO

R7

1K

JTAG_TCK

JTAG_Blaster_TDI

JTAG_TMS

HPS_TDO

R242

HPS_TCK

R244

HPS_TMS

R241

HPS_TDI

DNI

DNI

1

3

5

7

9

JTAG_Blaster_TDO

0

DNI

JTAG_Blaster_TDO R296

R1

10K

J5

5

5

5

5

R295

2

4

6

8

10

USB_DISABLE_n

R2

0

R298 0

5,10,26

HPS_WARM_RST_N

JTAG_TRST

5,10

DNI

JTAG Header

C

10

USB_DISABLE_n

JTAG Chain

B

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

JTAG Chain

Thursday, November 20, 2014

Rev

F

Sheet

1

11

of

30

VCC3P3

VCC3P3

VCC3P3

D8

1

3

2

D30

GPIO_0_D16

VCC3P3

D77

GPIO_0_D12

VCC3P3

D73

GPIO_0_D8

VCC3P3

D20

GPIO_0_D4

VCC3P3

D61

GPIO_0_D0

VCC3P3

D58

1

3

3

2

D90

GPIO_0_D20

GPIO_0_D24

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

D54

D57

D17

D70

D74

D27

D86

GPIO_0_D1

GPIO_0_D5

GPIO_0_D9

GPIO_0_D13

GPIO_0_D17

3

2

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

D53

D15

D65

D69

D25

D81

D85

GPIO_0_D6

GPIO_0_D10

GPIO_0_D14

GPIO_0_D18

3

2

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

D12

D62

D66

D22

D78

D82

D33

GPIO_0_D3

2

BAT54S

GPIO_0_D7

2

BAT54S

GPIO_0_D11

3

2

BAT54S

GPIO_0_D15

3

2

BAT54S

GPIO_0_D19

3

2

BAT54S

D94

1

GPIO_0_D27

2

BAT54S

BAT54S

GPIO_0_D23

GPIO_0_D31

2

BAT54S

GPIO_0_D35

D49

3

GPIO_0_D30

BAT54S

1

D36

1

GPIO_0_D26

GPIO_0_D34

BAT54S

GPIO_0_D22

BAT54S

GPIO_0_D2

GPIO_0_D29

D50

3

GPIO_0_D33

D91

3

BAT54S

1

GPIO_0_D25

GPIO_0_D32

BAT54S

GPIO_0_D21

3

2

D46

3

GPIO_0_D28

BAT54S

1

VCC3P3

D10

2

BAT54S

BAT54S

GPIO 0

GPIO_0[35..0]

3,6

GPIO 0

RN2

GPIO_00

GPIO_01

GPIO_02

GPIO_03

1

2

3

4

GPIO_04

GPIO_05

GPIO_06

GPIO_07

1

2

3

4

8

7

6

5

GPIO_0_D0

GPIO_0_D1

GPIO_0_D2

GPIO_0_D3

8

7

6

5

GPIO_0_D4

GPIO_0_D5

GPIO_0_D6

GPIO_0_D7

JP1

Clock_in

Clock_in

47

RN4

RN13

GPIO_020

GPIO_021

GPIO_022

GPIO_023

1

2

3

4

47

RN7

GPIO_08

GPIO_09

GPIO_010

GPIO_011

1

2

3

4

8

7

6

5

1

2

3

4

GPIO_0_D8

GPIO_0_D9

GPIO_0_D10

GPIO_0_D11

GPIO_024

GPIO_025

GPIO_026

GPIO_027

1

2

3

4

8

7

6

5

1

2

3

4

8

7

6

5

GPIO_0_D24

GPIO_0_D25

GPIO_0_D26

GPIO_0_D27

8

7

6

5

GPIO_0_D28

GPIO_0_D29

GPIO_0_D30

GPIO_0_D31

8

7

6

5

GPIO_0_D32

GPIO_0_D33

GPIO_0_D34

GPIO_0_D35

47

RN16

GPIO_0_D12

GPIO_0_D13

GPIO_0_D14

GPIO_0_D15

GPIO_028

GPIO_029

GPIO_030

GPIO_031

1

2

3

4

47

RN11

GPIO_016

GPIO_017

GPIO_018

GPIO_019

GPIO_0_D20

GPIO_0_D21

GPIO_0_D22

GPIO_0_D23

VCC5

47

RN15

47

RN9

GPIO_012

GPIO_013

GPIO_014

GPIO_015

8

7

6

5

VCC3P3

GPIO_0_D0

GPIO_0_D2

GPIO_0_D4

GPIO_0_D6

GPIO_0_D8

GPIO_0_D10

GPIO_0_D12

GPIO_0_D14

GPIO_0_D16

GPIO_0_D18

GPIO_0_D20

GPIO_0_D22

GPIO_0_D24

GPIO_0_D26

GPIO_0_D28

GPIO_0_D30

GPIO_0_D32

GPIO_0_D34

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

GPIO_0_D1

GPIO_0_D3

GPIO_0_D5

GPIO_0_D7

GPIO_0_D9

GPIO_0_D11

GPIO_0_D13

GPIO_0_D15

GPIO_0_D17

GPIO_0_D19

GPIO_0_D21

GPIO_0_D23

GPIO_0_D25

GPIO_0_D27

GPIO_0_D29

GPIO_0_D31

GPIO_0_D33

GPIO_0_D35

BOX Header 2X20M

47

RN18

8

7

6

5

GPIO_0_D16

GPIO_0_D17

GPIO_0_D18

GPIO_0_D19

47

GPIO_032

GPIO_033

GPIO_034

GPIO_035

1

2

3

4

47

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

GPIO 0

Thursday, November 20, 2014

Rev

F

Sheet

1

12

of

30

VCC3P3

VCC3P3

VCC3P3

D9

1

3

2

D31

GPIO_1_D16

VCC3P3

D75

GPIO_1_D12

VCC3P3

D72

GPIO_1_D8

VCC3P3

D21

GPIO_1_D4

VCC3P3

D59

GPIO_1_D0

VCC3P3

D56

1

3

3

2

D88

GPIO_1_D20

GPIO_1_D24

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

D52

D55

D18

D68

D71

D28

D84

GPIO_1_D1

GPIO_1_D5

GPIO_1_D9

GPIO_1_D13

GPIO_1_D17

3

2

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

D51

D16

D64

D67

D26

D79

D83

GPIO_1_D6

GPIO_1_D10

GPIO_1_D14

GPIO_1_D18

3

2

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

D13

D60

D63

D23

D76

D80

D34

GPIO_1_D3

2

BAT54S

GPIO_1_D7

2

BAT54S

GPIO_1_D11

3

2

BAT54S

GPIO_1_D15

3

2

BAT54S

GPIO_1_D19

3

2

BAT54S

D93

1

GPIO_1_D27

2

BAT54S

BAT54S

GPIO_1_D23

GPIO_1_D31

2

BAT54S

GPIO_1_D35

D47

3

GPIO_1_D30

BAT54S

1

D37

1

GPIO_1_D26

GPIO_1_D34

BAT54S

GPIO_1_D22

BAT54S

GPIO_1_D2

GPIO_1_D29

D48

3

GPIO_1_D33

D89

3

BAT54S

1

GPIO_1_D25

GPIO_1_D32

BAT54S

GPIO_1_D21

3

2

D45

3

GPIO_1_D28

BAT54S

1

VCC3P3

D11

2

BAT54S

BAT54S

GPIO 1

GPIO_1[35..0]

3,6

GPIO 1

RN3

GPIO_10

GPIO_11

GPIO_12

GPIO_13

1

2

3

4

GPIO_14

GPIO_15

GPIO_16

GPIO_17

1

2

3

4

8

7

6

5

GPIO_1_D0

GPIO_1_D1

GPIO_1_D2

GPIO_1_D3

8

7

6

5

GPIO_1_D4

GPIO_1_D5

GPIO_1_D6

GPIO_1_D7

JP2

Clock_in

47

RN5

RN12

GPIO_120

GPIO_121

GPIO_122

GPIO_123

1

2

3

4

47

RN6

GPIO_18

GPIO_19

GPIO_110

GPIO_111

1

2

3

4

8

7

6

5

1

2

3

4

GPIO_1_D8

GPIO_1_D9

GPIO_1_D10

GPIO_1_D11

GPIO_124

GPIO_125

GPIO_126

GPIO_127

1

2

3

4

8

7

6

5

1

2

3

4

8

7

6

5

GPIO_1_D24

GPIO_1_D25

GPIO_1_D26

GPIO_1_D27

8

7

6

5

GPIO_1_D28

GPIO_1_D29

GPIO_1_D30

GPIO_1_D31

8

7

6

5

GPIO_1_D32

GPIO_1_D33

GPIO_1_D34

GPIO_1_D35

47

RN17

GPIO_1_D12

GPIO_1_D13

GPIO_1_D14

GPIO_1_D15

GPIO_128

GPIO_129

GPIO_130

GPIO_131

1

2

3

4

47

RN10

GPIO_116

GPIO_117

GPIO_118

GPIO_119

GPIO_1_D20

GPIO_1_D21

GPIO_1_D22

GPIO_1_D23

VCC5

47

RN14

47

RN8

GPIO_112

GPIO_113

GPIO_114

GPIO_115

8

7

6

5

VCC3P3

GPIO_1_D0

GPIO_1_D2

GPIO_1_D4

GPIO_1_D6

GPIO_1_D8

GPIO_1_D10

GPIO_1_D12

GPIO_1_D14

GPIO_1_D16

GPIO_1_D18

GPIO_1_D20

GPIO_1_D22

GPIO_1_D24

GPIO_1_D26

GPIO_1_D28

GPIO_1_D30

GPIO_1_D32

GPIO_1_D34

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

GPIO_1_D1

GPIO_1_D3

GPIO_1_D5

GPIO_1_D7

GPIO_1_D9

GPIO_1_D11

GPIO_1_D13

GPIO_1_D15

GPIO_1_D17

GPIO_1_D19

GPIO_1_D21

GPIO_1_D23

GPIO_1_D25

GPIO_1_D27

GPIO_1_D29

GPIO_1_D31

GPIO_1_D33

GPIO_1_D35

BOX Header 2X20M

47

RN19

8

7

6

5

GPIO_1_D16

GPIO_1_D17

GPIO_1_D18

GPIO_1_D19

47

GPIO_132

GPIO_133

GPIO_134

GPIO_135

1

2

3

4

47

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE1-SoC Board

Size

B

Date:

5

Document Number

GPIO 1

Thursday, November 20, 2014

Rev

F

Sheet

1

13

of

30

DRAM_DQ[15..0]

DRAM_ADDR[12..0] 3,6

D

3

9

43

49

VDDQ

VDDQ

VDDQ

VDDQ

16

17

18

19

20

21

3

3

3

3

3

6

A0

D0

A1

D1

A2

D2

A3

D3

A4

D4

A5

D5

A6

D6

A7

D7

A8

D8

A9

D9

A10

D10

A11 SDRAM 32Mx16 D11

A12

D12

CLK

D13

CKE

D14

LDQM

D15

UDQM

nWE

nCAS

nRAS

nCS

BA0

BA1

HPS_FLASH_DCLK

HPS_FLASH_NCSO

5

5

5

R290

2K

VCC3P3

U13

HPS_FLASH_DATA31

2

VCC3P3

3

4

5

6

HPS_FLASH_NCSO 7

HPS_FLASH_DATA18

QSPI_RESET_N

C184

0.1u

DNI

HOLD_n/DQ3

C

VCC

DQ0

RESET

DNU_8

DNU_2

DNU_7

DNU_3

DNU_6

DNU_4

DNU_5

S_n

VSS

DQ1

W_n/Vpp/DQ2

VCC3P3

R225

330

DNI

VCC3P3

R170

DR_VCC3P3

HPS_FLASH_DCLK

HPS_FLASH_DATA0

C

HPS_FLASH_DATA2

HPS_FLASH_NCSO

R220

DNI

HPS_FLASH_DATA0

R257

4.7K DRAM_WE_N

R224

DNI

HPS_FLASH_DATA1

R256

4.7K DRAM_CAS_N

R61

DNI

HPS_FLASH_DATA2

R255

4.7K DRAM_RAS_N

R226

DNI

HPS_FLASH_DATA3

R254

4.7K DRAM_CS_N

R251

4.7K DRAM_CKE

R221 10K

HPS_FLASH_DCLK

Note: place a pull down resistor on the FLASH_DCLK wire at

16

15

14

13

12

11

10

9

N25Q512A83GSF40F

DR_VCC3P3

28

41

54

10

VCC3P3

VSSQ

VSSQ

VSSQ

VSSQ

DRAM_WE_N

DRAM_CAS_N

DRAM_RAS_N

DRAM_CS_N

DRAM_BA0

DRAM_BA1

QSPI_RESET_N

HPS_FLASH_DATA[3..0]

DRAM_DQ0

DRAM_DQ1

DRAM_DQ2

DRAM_DQ3

DRAM_DQ4

DRAM_DQ5

DRAM_DQ6

DRAM_DQ7

DRAM_DQ8

DRAM_DQ9

DRAM_DQ10

DRAM_DQ11

DRAM_DQ12

DRAM_DQ13

DRAM_DQ14

DRAM_DQ15

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

6

12

46

52

23

24

25

26

29

30

31

32

33

34

22

35

36

38

37

15

39

VSS

VSS

VSS

DRAM_ADDR0

DRAM_ADDR1

DRAM_ADDR2

DRAM_ADDR3

DRAM_ADDR4

DRAM_ADDR5

DRAM_ADDR6

DRAM_ADDR7